Изобретение относится к радиосвязи и может найти применение в системах связи с широкополосными сигналами.

Известны устройства поиска ШПС, недостатком которых является низкая помехоустойчивость к взаимным (структурным) помехам.

Наиболее близким к предлагаемому является устройство, содержащее n корреляторов 1, входы которых объединены и являются входом устройства. Вторые входы корреляторов 1 соединены с выходами генератора копий 3, а выходы корреляторов 1 соединены с входами решающего устройства 2. Выход решающего устройства 2 соединен с входом порогового устройства 4, выход которого является выходом устройства.

Цель изобретения - повышение помехоустойчивости к структурными помехам.

Для достижения этой цели в устройство, содержащее n корреляторов, первые входы которых объединены, вторые соединены с выходами генератора копий, а выходы соединены с входами решающего устройства, введены блок управления, два коммутатора, первый и второй элементы задержки, последовательно соединенные первый перемножитель, режекторный фильтр, второй перемножитель, причем вход первого элемента задержки и первого перемножителя объединены и соединены с входом устройства, выход первого элемента задержки и выход второго перемножителя соединены с соответствующими входами первого коммутатора, третий вход которого соединен с выходом блока управления, а выход - с объединенными входами корреляторов, один вход второго коммутатора соединен с выходом решающего устройства, n входов второго коммутатора соединены с n выходами генератора копий, а выход коммутатора соединен с первым перемножителем и через второй элемент задержки - с вторым перемножителем, кроме того, один вход блока управления соединен с выходом решающего устройства, другой вход - с тактовым выходом генератора копий.

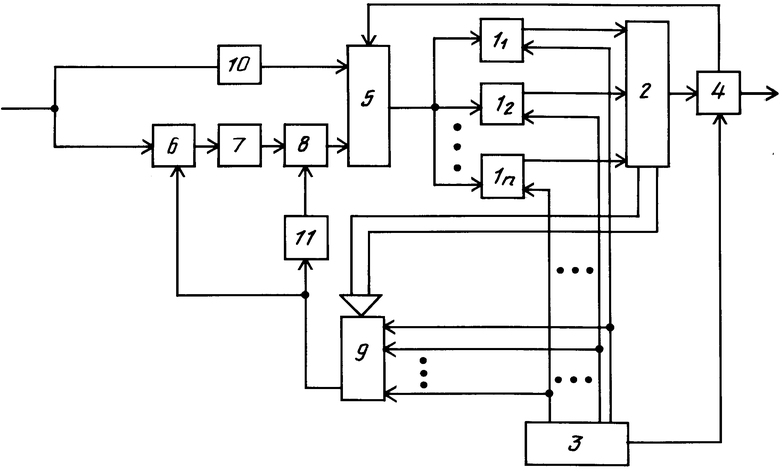

На чертеже приведена структурная схема предлагаемого устройства.

Оно содержит корреляторы 11...1n, решающее устройство 2, генератор копий 3, блок управления 4, первый коммутатор 5, первый и второй перемножители 6 и 8, режекторный фильтр 7, второй коммутатор 9, первый и второй элементы задержки 10 и 11.

Вход устройства соединен с первым коммутатором 5 через две ветви; одна ветвь содержит элемент задержки 10, другая - последовательно соединенные первый перемножитель 6, режекторный фильтр 7, второй перемножитель 8. Выход коммутатора 5 соединен с объединенными входами n 11...1n корреляторов, выходы которых соединены с входами решающего устройства 2, один выход которого соединен с входом блока управления 4, а другой - с входом второго коммутатора 9. Вторые входы корреляторов 11...1n соединены с выходами генератора копий 3, эти же выходы генератора копий 3 соединены с входами второго коммутатора 9, выход которого соединен с входом первого перемножителя 6 и через элемент задержки 11 - с входом второго перемножителя 8. Тактовый выход генератора копий 3 соединен с вторым входом блока управления 4, один выход которого соединен с входом первого коммутатора 5, другой является выходом устройства.

Работает устройство следующим образом.

В исходном режиме работы вход устройства через элемент задержки 10 и коммутатор 5 подключается к входам корреляторов 11...1n, с выходов которых сигнал поступает на решающее устройство 2, где выбирается максимальный отклик, который подается на блок управления 4, а также определяется номер канала с максимальным откликом, который подается на коммутатор 9. В блоке управления 4 осуществляется сравнение отклика с первым порогом П1. Если порог П1 не превышен, то режим сохраняется неизменным. При превышении П1 команда с первого выхода блока управления 4 подается на коммутатор 5, который подключает к входам корреляторов 11...1n блоки 6-8. В качестве опорного сигнала на перемножители 6, 8 подается ПСП, формируемая генератором 3, при этом коммутатор 9 подключает к перемножителям 6 и 8 опорную ПСП канала с максимальным откликом. Путем перемножения с ПСП, синхронной с приходящей ШПС, в перемножителе 6 осуществляется свертка ШПС с узкополосный сигнал, который режектируется в режекторном фильтре 7. Помехи, несинхронные с опорной ПСП, подаваемой на перемножитель 6, получают дополнительную манипуляцию. При этом спектр их расширяется и часть спектра, попадающая в фильтр 7, режектируется.

В перемножителе 8 помехи повторно перемножаются с той же ПСП синхронной с ними, в результате чего дополнительная манипуляция, наложенная на помехи в перемножителе 6 снимается и они возвращаются к своему первоначальному виду и подаются на корреляторы 11...1n и затем на решающее устройство 2, где происходит их корреляционная обработки и выбор максимального отклика, который подается на блок управления 4, где сравнивается с порогом П2, причем П2 < П1. Если порог П2 на втором этапе не превышен, выносится решение ("1" на выходе блока 4) о правильной синхронизации за полезный сигнал на первом этапе поиска. При этом командой, подаваемой с блока управления 4 на коммутатор 5, устройство возвращается в исходное состояние, т.е. вход устройства через элемент задержки 10 и коммутатор 5 подключается к корреляторам 11... 1n. Если порог П2 превышен, то принимается решение о том, что на первом этапе превышение порога П1 было вызвано помехой и решение об окончании поиска не выносится ("0" на выходе 2 блока управления 4), а устройство возвращается в исходное состояние.

Элементы задержки 10 и 11 компенсируют задержки сигнала при прохождении трактов с целью обеспечения синхронности входного и опорного сигналов.

Докажем достижение поставленной цели.

Устройство-прототип принимает решение об обнаружении сигнала при первом превышении порога П1. При этом оно не различает случаи воздействия сигнала и структурной помехи, а также случай превышения порога неосновным выбросом автокорреляционной функции сигнала. При этом вероятность правильного обнаружения Д составляет Д = 0,5.

Предложенное устройство отличает случаи превышения порога сигналом и помехой. Действительно, на первом этапе, если П1 превышен откликом сигнала, то на втором этапе обнаружения сигнал сворачивается и полностью режектируется. Это означает, что превышение порога П2 может быть обусловлено только помехой. Решения об окончании поиска в этом случае не выносится, устройство возвращается в исходное состояние и производит повторную попытку синхронизации и т.д. до тех пор, пока не будет принято правильное решение.

Вероятность правильного обнаружения в этом случае

Д = 1 - (0,5)К, где К - число попыток;

К - Т/Тн, Т - время работы устройства, Тн - время накопления в корреляторах.

Так при К = 3Д = 0,875 > 0,5.

Аналогично за счет выбора соотношений между П1 и П2 можно обнаружить случай превышения порога неосновным максимумом. Эта возможность основана на том, что при синхронизации за главный лепесток сигнал режектируется полностью и в этом случае вероятность превышения порога П2 мала, а при синхронизации за боковой выброс режектируется не весь сигнал, а только часть его, т. е. превышение П2 свидетельствует также о синхронизации за боковой выброс при отсутствии помех.

Изобретение относится к радиосвязи и может найти применение в системах связи с широкополосными сигналами. Цель изобретения: уменьшение вероятности ложного обнаружения при воздействии мощной помехи. Устройство обнаружения широкополосных сигналов содержит корреляторы 11-1n , блок выбора максимума 2, генератор 3 псевдослучайной последовательности, пороговый блок 4, первый коммутатор 5, первый и второй перемножители 6, 8, рефлекторный фильтр 7, второй коммутатор 9 и первый и второй элементы задержки 10, 11. 1 ил.

УСТРОЙСТВО ОБНАРУЖЕНИЯ ШИРОКОПОЛОСНЫХ СИГНАЛОВ, содержащее K параллельно соединенных по информационным входам корреляторов, опорные входы которых соединены с соответствующими выходами генератора псевдослучайной последовательности, а выходы - с соответствующими входами блока выбора максимума, выход которого соединен с информационным входом порогового блока, отличающееся тем, что, с целью уменьшения вероятности ложного обнаружения при воздействии мощной помехи, в него введены последовательно соединенные первый перемножитель, режекторный фильтр, второй перемножитель и первый коммутатор, а также второй коммутатор, выход которого соединен с опорным входом первого перемножителя и через первый элемент задержки - с опорным входом второго перемножителя, информационные входы второго коммутатора соединены с соответствующими опорными входами корреляторов, а адресный вход - с адресным выходом блока выбора максимума, второй информационный вход первого коммутатора через второй элемент задержки соединен с информационным входом первого перемножителя, управляющий вход первого коммутатора соединен с выходом порогового блока, тактовый вход которого соединен с соответствующим выходом генератора псевдослучайной последовательности, а выход первого коммутатора соединен с соединенными между собой информационными входами K корреляторов.

| Пестряков В.В | |||

| Шумоподобные сигналы в системах передачи информации | |||

| М.: Сов.радио, 1973, с.154, рис.5.2.1. |

Авторы

Даты

1994-09-30—Публикация

1990-01-29—Подача