Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных машинах и устройствах, функционирующих в системе остаточных классов.

Известно устройство (аналог) [1], содержащее два дешифратора, шифратор, блоки элементов И, блок элементов ИЛИ, группу элементов ИЛИ, схему сравнения, элементы запрета, элементы И, кольцевой сдвигающий регистр. Недостаток устройства - низкое быстродействие выполнения модульных операций сложения и вычитания.

Известно также устройство (аналог) [2], содержащее дешифраторы, группы элементов И и ИЛИ, группу блоков элементов И, схему сравнения, блок элементов ИЛИ, счетчик, элементы ИЛИ, шифратор, элементы запрета и И, умножитель частоты, кольцевой регистр сдвига. Недостаток устройства - низкое быстродействие выполнения модульных операций сложения и вычитания.

Наиболее близким по технической сущности (прототип) к предлагаемому изобретению является устройство [3], содержащее два суммирующих счетчика, схему сравнения, вычитатель по модулю, блоки элементов И, элемент запрета, элементы И, кольцевой регистр сдвига и шифратор. Максимальное время выполнения модульной операции сложения (вычитания) составляет m-тактов (m - модуль устройства), что обуславливает основной его недостаток. Недостаток прототипа - низкое быстродействие выполнения модульных операций сложения и вычитания, ввиду того, что максимальный цикл устройства составляет m-тактов.

Задача, на решение которой направлено заявляемое изобретение, состоит в повышении производительности перспективных образцов вычислительной техники.

Технический результат выражается в повышении быстродействия выполнения модульных операций сложения и вычитания за счет уменьшения длительности арифметической операции.

Технический результат достигается тем, что в устройство, содержащее два счетчика, первый элемент запрета, с первого по третий блоки элементов И, первый блок элементов ИЛИ, первый преобразователь кода и шифратор, причем входы задания сложения и вычитания устройства соединены соответственно с первыми входами первого и второго блоков элементов И, выходы которых соединены соответственно с входом первого преобразователя кода и вторым входом первого блока элементов ИЛИ, первый вход которого соединен с выходом первого преобразователя кода, а выход - с информационным входом второго счетчика, выход шифратора соединен с вторыми входами третьего блока элементов И, выходы которого являются выходом устройства, введены третий и четвертый счетчик, четыре элемента ИЛИ-НЕ, второй элемент запрета, с четвертого по девятый блоки элементов И, с второго по восьмой преобразователь кода, с второго по четвертый блоки элементов ИЛИ, два элемента ИЛИ, элемент И и дешифратор, причем первый информационный вход устройства соединен с входами второго и третьего преобразователей кода, выходы которых соединены с информационными входами соответственно первого и третьего счетчиков, выходы разрядов которых соединены с соответствующими входами соответственно первого и второго элементов ИЛИ-НЕ, второй информационный вход устройства соединен с входами четвертого и пятого преобразователей кода, выход четвертого преобразователя кода соединен с вторыми входами первого и второго блоков элементов И, выход пятого преобразователя кода соединен с вторыми входами четвертого и пятого блоков элементов И, первые входы которых соединены соответственно с входами задания сложения и вычитания устройства, а выходы которых соединены соответственно с входом шестого преобразователя кода и вторым входом второго блока элементов ИЛИ, первый вход которого соединен с выходом шестого преобразователя кода, а выход - с информационным входом четвертого счетчика.

Выходы разрядов второго и четвертого счетчиков соединены с соответствующими входами соответственно третьего и четвертого элементов ИЛИ-НЕ, выходы которых соединены с вторыми входами соответственно первого и второго элементов ИЛИ, первые входы которых соединены соответственно с выходами первого и второго элементов ИЛИ-НЕ, а выходы - с управляющими входами соответственно первого и второго элементов запрета, информационные входы которых соединены с тактовым входом устройства, а выход первого элемента запрета соединен с вычитающими входами первого и второго счетчика, выход второго элемента запрета соединен с вычитающими входами третьего и четвертого счетчиков, выходы разрядов первого, второго, третьего и четвертого счетчиков соединены соответственно с первыми входами шестого, седьмого, восьмого и девятого блоков элементов И, вторые входы которых соединены соответственно с выходами третьего, первого, четвертого и второго элементов ИЛИ-НЕ.

Выходы шестого и седьмого блоков элементов И соединены соответственно с первым входом третьего блока элементов ИЛИ и с входом седьмого преобразователя кода, выход которого соединен с вторым входом третьего блока элементов ИЛИ, выходы восьмого и девятого блоков элементов И соединены соответственно с первым входом четвертого блока элементов ИЛИ и с входом восьмого преобразователя кода, выход которого соединен с вторым входом четвертого блока элементов ИЛИ, выходы третьего и четвертого блоков элементов ИЛИ соединены с соответствующими входами дешифратора, выход которого соединен с входом шифратора, выходы первого и второго элементов ИЛИ соединены соответственно с первым и вторым входами элемента И, выход которого соединен с первым входом третьего блока элементов И.

Сущность изобретения состоит в разложении первого А и второго В операндов по частным модулям m1 и m2 (m1˙ m2 ≥ m), где m - модуль операции с одновременным проведении операции модульного сложения (вычитания) по каждому частному модулю, корректируя при необходимости промежуточный результат, с последующим его преобразованием в результате операции по модулю m. Рассмотрим алгоритм проведения операции модульного вычитания, ввиду того, что

(А + В)modm = A - (m - B)modm,

(m - B)modm = [(m1 - B1); (m2 - B2)],

B = (B1; B2) - разложение числа В по частным модулям m1 и m2 (m1˙ m2 ≥ m).

Следовательно, алгоритм операции (A-B)modm следующий:

1) представляем исходные операнды А и В в виде А = (А1, А2) и В = (В1, В2), где А1, В1 и А2, В2 - соответственно остатки исходных операндов по частным модулям m1 и m2;

2) производим последовательное вычитание единицы со всех остатков, при этом, как только остаток одного из операндов по данному частному модулю станет равен нулю, то операция по данному частному модулю прекращается;

3) завершением модульной операции вычитания будет момент, когда по одному из остатков каждого частного модуля одного из операндов (А или В) результат будет равен нулю, при этом возможны четыре варианта:

а) представим результат операции (А-В)modm = Xmodm = (X1, X2), где X1, X2 - остатки по частным модулям m1 и m2, если А1 > А2 и В1 > В2, то получим сразу окончательный результат;

б) если А1 < А2 и В1 > В2, то (А-В)modm = (m1 -  , X2);

, X2);

в) если А1 > А2 и В1 < В2, то (А-В)modm = (X1, m2 -  );

);

г) при А1 < А2 и В1 < В2; (А-В)modm = (m1 -  , m2 -

, m2 -  ) = (X1, X2), т. е. , если соответствующий остаток уменьшаемого А по данному частному модулю (или обоим) меньше соответствующего остатка вычитаемого по данному частному модулю (или обоим), то результат операции модульного вычитания инвертируется по данному частному модулю (или обоим).

) = (X1, X2), т. е. , если соответствующий остаток уменьшаемого А по данному частному модулю (или обоим) меньше соответствующего остатка вычитаемого по данному частному модулю (или обоим), то результат операции модульного вычитания инвертируется по данному частному модулю (или обоим).

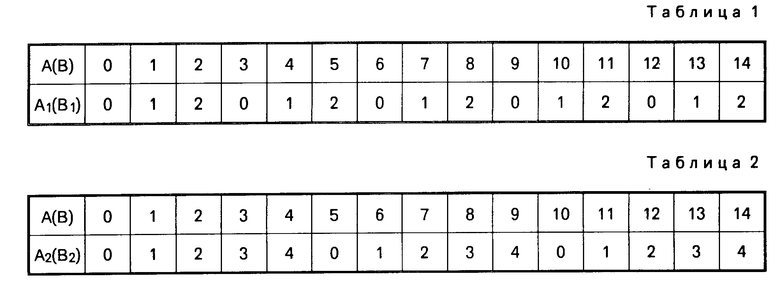

Преобразователи кода 2, 4 и 3, 5 производят нахождение остатка операндов А и В соответственно по частным модулям m1 и m2, а преобразователи кода 1, 7 и 6, 8 производят инверсию чисел по частным модулям соответственно m1 и m2. Рассмотрим подробнее построение устройства при m1 = 3, m2 = 5 и m = 15. Табл. 1 отображает работу преобразователей кода 2 и 4.

Табл. 2 отражает работу преобразователей кода 3 и 5.

Табл. 3 отображает работу преобразователей кода 1 и 7.

Табл. 4 отображает работу преобразователей кода 6 и 8.

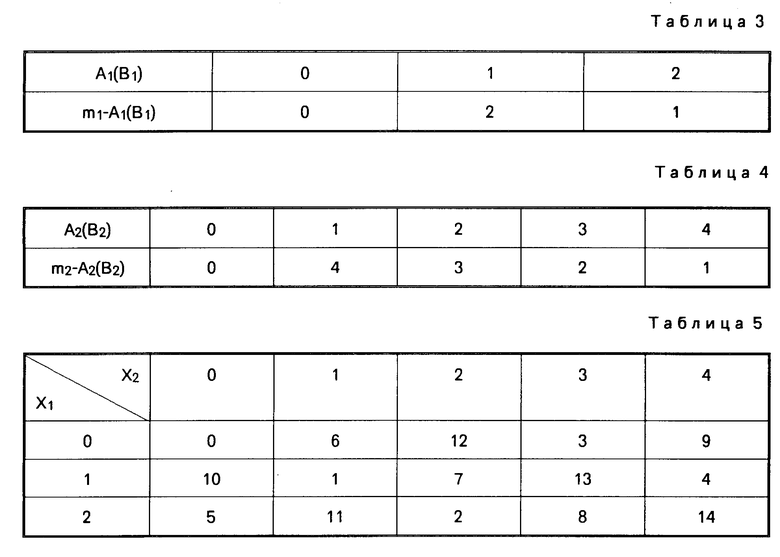

Первый и второй счетчики состоят из двух двоичных разрядов, а третий и четвертый - из трех двоичных разрядов. Максимальная длительность модульных операций составляет 4 такта, вместо 15 в прототипе.

Дешифратор совместно с шифратором реализуют обратное преобразование результата модульной операции в код по модулю m = 15 согласно табл. 5.

Дешифратор имеет 8 входов, используется 15 выходов с нулевого по четырнадцатый. Шифратор имеет 16 входов и 4 выхода для двоичного представления результата модульной операции сложения (вычитания).

Возможность достижения положительного эффекта от использования данного изобретения состоит в повышении быстродействия работы устройства, в виду уменьшения количества сдвигов для получения результатов, а также выбора минимального остатка в двух операндах (А и В) по каждому частному модулю.

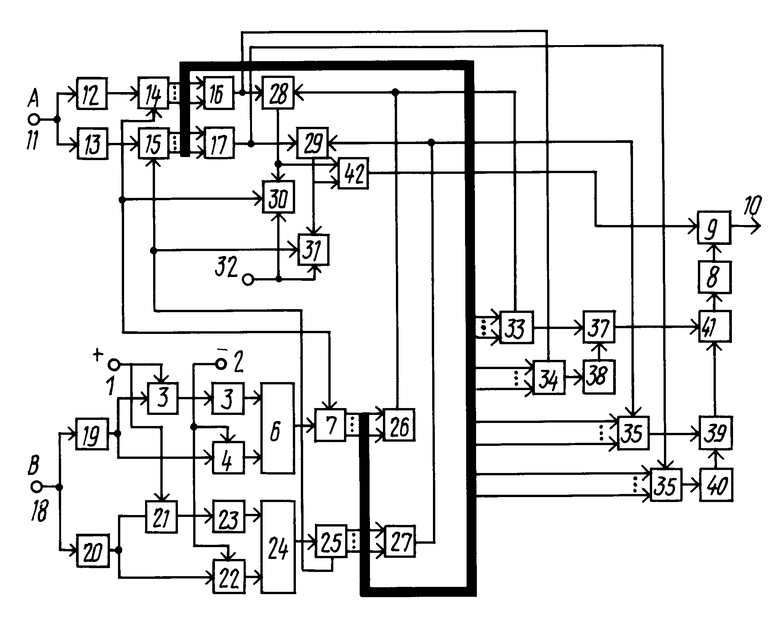

На чертеже представлена структурная схема устройства, где 1 - вход задания сложения устройства, 2 - вход задания вычитания устройства, 3 - первый блок элементов И, 4 - второй блок элементов И, 5 - первый преобразователь кода, 6 - первый блок элементов ИЛИ, 7 - второй счетчик, 8 - шифратор, 9 - третий блок элементов И, 10 - выход устройства, 11 - первый информационный вход устройства, 12 - второй преобразователь кода, 13 - третий преобразователь кода, 14 - первый счетчик, 15 - третий счетчик, 16 - первый элемент ИЛИ-НЕ, 17 - второй элемент ИЛИ-НЕ, 18 - второй информационный вход устройства, 19 - четвертый преобразователь кода, 20 - пятый преобразователь кода, 21 - четвертый блок элементов И, 22 - пятый блок элементов И, 23 - шестой преобразователь кода, 24 - второй блок элементов ИЛИ, 25 - четвертый счетчик, 26 - третий элемент ИЛИ-НЕ, 27 - четвертый элемент ИЛИ-НЕ, 28 - первый элемент ИЛИ, 29 - второй элемент ИЛИ, 30 - первый элемент запрета, 31 - второй элемент запрета, 32 - тактовый вход устройства, 33 - шестой блок элементов И, 34 -седьмой блок элементов И, 35 - восьмой блок элементов И, 36 - девятый блок элементов И, 37 - третий блок элементов ИЛИ, 38 - седьмой преобразователь кода, 39 - четвертый блок элементов ИЛИ, 40 - восьмой преобразователь кода, 41 - дешифратор, 42 - элемент И.

Входы задания сложения 1 и вычитания 2 устройства соединены соответственно с первыми входами первого 3 и второго 4 блоков элементов И, выходы которых соединены соответственно с входом первого 5 преобразователя кода и вторым входом первого 6 блока элементов ИЛИ, первый вход которого соединен с выходом первого 5 преобразователя кода, а выход - с информационным входом второго 7 счетчика, выход шифратора 8 соединен с вторыми входами третьего 9 блока элементов И, выходы которого являются входом 10 устройства, первый 11 информационный вход устройства соединен с входами второго 12 и третьего 13 преобразователей кода, выходы которых соединены с информационными входами соответственно первого 14 и третьего 15 счетчиков, выходы разрядов которых соединены с соответствующими входами соответственно первого 16 и второго 17 элементов ИЛИ-НЕ, второй 18 информационный вход устройства соединен с входами четвертого 19 и пятого 20 преобразователей кода, выход четвертого 19 преобразователя кода соединен с вторыми входами первого 3 и второго 4 блоков элементов И, выход пятого 20 преобразователя кода соединен с вторыми входами четвертого 21 и пятого 22 блоков элементов И, первые входы которых соединены соответственно с входами задания сложения 1 и вычитания 2 устройства, а выходы которых соединены с входом шестого 23 преобразователя кода и вторым входом второго 24 блока элементов ИЛИ, первый вход которого соединен с выходом шестого 23 преобразователя кода, а выход с информационным входом четвертого 25 счетчика.

Выходы разрядов второго 7 и четвертого 25 счетчиков соединены с соответствующими входами соответственно третьего 26 и четвертого 27 элементов ИЛИ-НЕ, выходы которых соединены с вторыми входами соответственно первого 28 и второго 29 элементов ИЛИ, первые входы которых соединены соответственно с выходами первого 16 и второго 17 элементов ИЛИ-НЕ, а выходы с управляющими входами соответственно первого 30 и второго 31 элементов запрета, информационные входы которых соединены с тактовым входом 32 устройства, выход первого 30 элемента запрета соединен с вычитающими входами первого 14 и второго 7 счетчиков, выход второго 31 элемента запрета соединен с вычитающими входами третьего 15 и четвертого 25 счетчиков, выходы разрядов первого 14, второго 7, третьего 15 и четвертого 25 счетчиков соединены соответственно с первыми входами шестого 33, седьмого 34, восьмого 35 и девятого 36 блоков элементов И, вторые входы которых соединены соответственно с выходами третьего 26, первого 16, четвертого 27 и второго 17 элементов ИЛИ-НЕ, выходы шестого 33 и седьмого 34 блоков элементов И соединены соответственно с первым входом третьего 37 блока элементов ИЛИ и с входом седьмого 38 преобразователя кода, выход которого соединен со вторым входом третьего 37 блока элементов ИЛИ, выходы восьмого 36 и девятого 36 блоков элементов И соединены соответственно с первым входом четвертого 39 блока элементов ИЛИ и с входом восьмого 40 преобразователя кода, выход которого соединен с вторым входом четвертого 39 блока элементов ИЛИ, выходы третьего 37 и четвертого 39 блоков элементов ИЛИ соединены с соответствующими входами дешифратора 41, выход которого соединен с входом шифратора 8, выходы первого 28 и второго 29 элементов ИЛИ соединены соответственно с первым и вторым входами элемента И 42, выход которого соединен с первым входом третьего 9 блока элементов И.

Работу устройства удобно рассматривать в двух режимах:

1) режим определения результата операции модульного вычитания;

2) режим определения результата операции модульного сложения.

Исходное состояние счетчиков - нули во всех разрядах. Сигналы на выходе элементов ИЛИ-НЕ появляются в том случае, когда на всех выходах соответствующих счетчиков будут нули. При проведении операции модульного вычитания операнды А и В поступают на входы соответственно преобразователей кода 12, 13 и 19, 20. На выходе преобразователей кода 12 и 19 получаем остатки входных операндов А1 и В1 по частному модулю m1, а на выходе преобразователей кода 13 и 20 - остатки входных операндов по частному модулю m2. Операнд А = (А1, А2) поступает на информационные входы соответствующих счетчиков 14 и 15. Операнд В = (В1, В2) через соответствующие открытые блоки элементов И 4, 22 (сигнал на входе 2 присутствует) на информационные входы соответствующих счетчиков 7 и 25 через соответствующие блоки элементов ИЛИ 6, 24. С тактового входа 32 устройства на вычитающие входы счетчиков 14, 7 и 15, 25 через соответствующие первый 30 и второй 31 элементы запрета поступают тактовые импульсы, которые уменьшают содержимое счетчиков 14, 7 и 15, 25. Если содержимое счетчика 14 (7) станет равно нулю, то с выхода элемента ИЛИ-НЕ 16 (26) поступает сигнал на соответствующий вход первого 28 элемента ИЛИ, с выхода которого поступает сигнал на управляющий вход первого элемента запрета 30, прекращая подачу тактовых импульсов на вычитающие входы счетчиков 14 и 7.

Аналогично, если содержимое счетчика 15 (25) станет равно нулю, то с выхода элемента ИЛИ-НЕ 17 (27) поступает сигнал на соответствующий вход второго 29 элемента ИЛИ, с выхода которого поступает сигнал на управляющий вход второго 31 элемента запрета, прекращают подачу импульсов на вычитающие входы счетчиков 15 и 25. Если сначала сигнал поступит с выхода третьего 26 элемента ИЛИ-НЕ, то открывается шестой 33 блок элементов И и результат операции X1 по частному модулю m1 с выходов первого 14 счетчика через шестой 33 блок элементов И поступает на первый вход третьего 37 блока элементов ИЛИ, но если сначала сигнал поступит с выхода первого 16 элемента ИЛИ-НЕ, то открывается седьмой 34 блок элементов И и промежуточный результат операции  по частному модулю m1с выходов второго 7 счетчика поступает на вход седьмого 34 блока элементов И, с выхода которого

по частному модулю m1с выходов второго 7 счетчика поступает на вход седьмого 34 блока элементов И, с выхода которого  поступает на вход седьмого 38 преобразователя кода, с выхода которого результат операции X1 = m1 -

поступает на вход седьмого 38 преобразователя кода, с выхода которого результат операции X1 = m1 -  по частному модулю m1 поступает на второй вход третьего 37 блока элементов ИЛИ. Аналогичная картина происходит в тракте по частному модулю m2. Следовательно, на выходах третьего 37 и четвертого 39 блоков элементов ИЛИ имеем результат модульной операции в виде X = (X1, X2). Когда сигналы поступят с выходов первого 28 и второго 29 элементов ИЛИ на оба входа элемента И 42, то сигнал с его выхода (сигнал окончания модульной операции вычитания) открывает третий блок 9 элементов И и результат операции, преобразованный в дешифраторе 41 и шифраторе 8 к виду Xmodm в двоичном коде через третий блок 9 элементов И поступает на выход 10 устройства.

по частному модулю m1 поступает на второй вход третьего 37 блока элементов ИЛИ. Аналогичная картина происходит в тракте по частному модулю m2. Следовательно, на выходах третьего 37 и четвертого 39 блоков элементов ИЛИ имеем результат модульной операции в виде X = (X1, X2). Когда сигналы поступят с выходов первого 28 и второго 29 элементов ИЛИ на оба входа элемента И 42, то сигнал с его выхода (сигнал окончания модульной операции вычитания) открывает третий блок 9 элементов И и результат операции, преобразованный в дешифраторе 41 и шифраторе 8 к виду Xmodm в двоичном коде через третий блок 9 элементов И поступает на выход 10 устройства.

Работа устройства при выполнении операции модульного сложения отличается от предыдущего режима только тем, что второй операнд при помощи первого 1 и шестого 23 преобразователей кода представляется в виде (m - B)modm = (m1 - B1, m2 - B2).

Рассмотрим примеры конкретного выполнения операций модульного вычитания и сложения для m = 15 (m1 = 3, m2 = 5).

П р и м е р 1. Пусть необходимо определить результат операции модульного вычитания для А = 7, В = 11 (А и В - операнды). Присутствует сигнал на шине 2. Операнд А = 7 в двоичном коде поступает на входы второго 12 и третьего 13 преобразователей кода. На выходе второго 12 преобразователя кода получаем число А1 = 1, а на выходе третьего 13 преобразователя кода - число А2 = 2 (табл. 1 и 2). Следовательно, в первом 14 и третьем 15 счетчиках установятся соответственно числа А1 = 1 и А2 = 2 в двоичном коде. Операнд В = 11 поступает на входы четвертого 19 и пятого 20 преобразователей кода, на выходах которых имеем соответственно В1 = 2, В2 = 1 (табл. 1 и 2). Эти числа через открытые блоки элементов И соответственно 4 и 22 и далее через соответственно первый 6 и второй 24 блоки элементов ИЛИ поступает на информационные входы соответствующих счетчиков 7 и 25. С тактового входа 32 через первый 30 элемент запрета поступает один импульс на вычитающие входы первого 14 и второго 7 счетчиков.

Одновременно один импульс поступает через второй 31 элемент запрета на вычитающие входы третьего 15 и четвертого 25 счетчиков. После прохождения первого импульса состояние первого 14 счетчика станет равно 0, второго 7 счетчика - 1, третьего 15 счетчика - 1, четвертого 25 счетчика - 0. Следовательно, операция модульного вычитания закончилась через один такт (в прототипе нужно было 11 тактов). С выхода первого 16 элемента ИЛИ-НЕ через первый 28 элемент ИЛИ на управляющий вход первого 30 элемента запрета поступает сигнал, запрещающий прохождение тактовых импульсов на вычитающие входы счетчиков 14 и 7. Одновременно с выхода четвертого 27 элемента ИЛИ-НЕ поступает сигнал через второй 29 элемент ИЛИ на управляющий вход второго 31 элемента запрета, который запрещает прохождение тактовых импульсов на вычитающие входы счетчиков 15 и 25. Эти сигналы поступают также на первый и второй входы элемента И 42, выходной сигнал которого открывает третий 9 блок элементов И. Сигнал с выхода первого 16 элемента ИЛИ-НЕ открывает седьмой 34 блок элементов И, обеспечивая прохождение содержимого второго 7 счетчика, равного 1, на вход седьмого 38 преобразователя кода, с выхода которого число 2 (табл. 3) через третий 37 блок, элементов ИЛИ поступает на первый вход дешифратора 41. Сигнал с выхода четвертого 27 элемента ИЛИ-НЕ открывает восьмой 35 блок элементов И, обеспечивая прохождение содержимого третьего 15 счетчика, равного 1, через четвертый 39 блок элементов ИЛИ на второй вход дешифратора 41. На входах дешифратора 41 имеет собственно число 2 и 1. Согласно таблице на выходе шифратора 8 будет число 11 в двоичном коде, которое поступает на выход 10 устройства. Это и будет результат модульной операции вычитания. Проверка: (7-11)mod 15 = 11mod 15.

П р и м е р 2. Пусть необходимо определить результат операции модульного сложения для А = 7, В = 11 (А и В - операнды). Присутствует сигнал на шине 1. Операнд А (аналогично первому примеру) поступает на информационные входы первого 14 и третьего 15 счетчиков, однако остатки операнда В по первому m1 = 3 и второму m2 = 5 частным модулям проходят через соответствующие первый 5 и шестой 23 преобразователи кода и во втором 7 и четвертом 25 счетчиках устанавливаются значения соответственно 1 и 4 (табл. 3 и 4). После прохождения первого тактового импульса состояние первого 14 счетчика будет равно нулю, второго 7 счетчика - 0, третьего 15 счетчика - 1, четвертого 25 счетчика - 3. Сигналом с выхода первого 28 элемента ИЛИ закрывается тракт прохождения тактовых импульсов на вычитающие входы первого 14 и второго 7 счетчиков. На вычитающие входы третьего 15 и четвертого 25 счетчиков поступает еще один тактовый импульс, который переводит третий 15 счетчик в состояние ноль, а содержимое четвертого 25 счетчика станет равно 2. Следовательно, операция модульного сложения закончилась через два такта. Аналогичным образом, как и в первом примере, происходит открытие третьего 9 блока элементов И. Сигнал с выхода второго 17 элемента ИЛИ-НЕ открывает девятый 36 блок элементов И, обеспечивая прохождение содержимого четвертого 25 счетчика, равное 2, в виде числа 3 (табл. 4) через четвертый 39 блок элементов ИЛИ на второй вход дешифратора 41 (на его первом входе будет число 0). Согласно табл. 5 на выходе шифратора 8 будет число 3, которое поступает на выход 10 устройства. Это и будет результат модульной операции сложения.

Проверка: (7+11)mod 15 = 3mod 15.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1991 |

|

RU2018935C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1991 |

|

RU2018936C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1998 |

|

RU2145112C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1995 |

|

RU2109326C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1992 |

|

RU2023290C1 |

| Арифметическое устройство по модулю | 1991 |

|

SU1775721A1 |

| Устройство для сложения и вычитания чисел по модулю | 1988 |

|

SU1683011A1 |

| Арифметическое устройство по модулю | 1989 |

|

SU1756881A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1998 |

|

RU2143723C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ | 1999 |

|

RU2156998C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных машинах и устройствах, функционирующих в системе остаточных классов. Цель изобретения - повышение быстродействия. Цель достигается путем введения третьего 15 и четвертого 25 счетчиков, четырех элементов ИЛИ - НЕ, второго 31 элемента запрета, с четвертого по девятый блоков элементов И, с второго по восьмой преобразователей кода, с второго по четвертый блоков элементов ИЛИ, двух элементов ИЛИ, элемента И 42, дешифратора 41. Сущность изобретения состоит в разложении первого А и второго В операндов по частным модулям m1 и m2 ( (m1·m2≥ m , где m - модуль операции) с одновременным проведением операции модульного сложения (вычитания) по каждому частному модулю, корректируя при необходимости промежуточный результат, с последующим его преобразованием в результат операции по модулю m. 1 ил., 5 табл.

УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ, содержащее два счетчика, первый элемент запрета, с первого по третий блоки элементов И, первый блок элементов ИЛИ, первый блок определения дополнительного кода остатка по первому частному модулю и шифратор, причем входы задания сложения и вычитания устройства соединены с первыми входами первого и второго блоков элементов И, выходы которых соединены соответственно с входом первого блока определения дополнительного кода остатка по первому частному модулю и вторым входом первого блока элементов ИЛИ, первый вход которого соединен с выходом первого блока определения дополнительного кода остатка по первому частному модулю, а выход - с информационным входом второго счетчика, выход шифратора соединен с вторым входом третьего блока элементов И, выход которого является выходом устройства, отличающееся тем, что оно содержит третий и четвертый счетчики, четыре элемента ИЛИ - НЕ, второй элемент запрета, с четвертого по девятый блоки элементов И, с второго по четвертый блоки элементов ИЛИ, два элемента ИЛИ, элемент И, дешифратор, второй блок определения дополнительного кода остатка по первому частному модулю, два блока определения дополнительного кода остатка по второму частному модулю, два блока определения кода остатка по первому частному модулю и два блока определения кода остатка по второму частному модулю, причем первый информационный вход устройства соединен с входами первого блока определения кода остатка по первому частному модулю и первого блока определения кода остатка по второму частному модулю, выходы которых соединены с информационными входами соответственно первого и третьего счетчиков, выходы разрядов которых соединены с соответствующими входами соответственно первого и второго элементов ИЛИ - НЕ, второй информационный вход устройства соединен с входами второго блока определения кода остатка по первому частному модулю и второго блока определения кода остатка по второму частному модулю, выход второго блока определения кода остатка по первому частному модулю соединен с вторыми входами первого и второго блоков элементов И, выход второго блока определения кода остатка по второму частному модулю соединен с вторыми входами четвертого и пятого блоков элементов И, первые входы которых соединены соответственно с входами задания сложения и вычитания устройства, а выходы соединены соответственно с входом первого блока определения дополнительного кода остатка по второму частному модулю и вторым входом второго блока элементов ИЛИ, первый вход которого соединен с выходом первого блока определения дополнительного кода остатка по второму частному модулю, а выход - с информационным входом четвертого счетчика, выходы разрядов второго и четвертого счетчиков соединены с соответствующими входами соответственно третьего и четвертого элементов ИЛИ - НЕ, выходы которых соединены с вторыми входами соответственно первого и второго элементов ИЛИ, первые входы которых соединены с выходами соответственно первого и второго элементов ИЛИ - НЕ, а выходы - с управляющими входами соответственно первого и второго элементов запрета, информационные входы которых соединены с тактовым входом устройства, выход первого элемента запрета соединен с вычитающими входами первого и второго счетчиков, выход второго элемента запрета соединен с вычитающими входами третьего и четвертого счетчиков, выходы разрядов первого, второго, третьего и четвертого счетчиков соединены с первыми входами соответственно шестого, седьмого, восьмого и девятого блоков элементов И, вторые входы которых соединены с выходами соответственно третьего, первого, четвертого и второго элементов ИЛИ - НЕ, выходы шестого и седьмого блоков элементов И соединены соответственно с первым входом третьего блока элементов ИЛИ и входом второго блока определения дополнительного кода остатка по первому частному модулю, выход которого соединен с вторым входом третьего блока элементов ИЛИ, выходы восьмого и девятого блоков элементов И соединены соответственно с первым входом четвертого блока элементов ИЛИ и входом второго блока определения дополнительного кода остатка по второму частному модулю, выход которого соединен с вторым входом четвертого блока элементов ИЛИ, выходы третьего и четвертого блоков элементов ИЛИ соединены с соответствующими входами дешифратора, выход которого соединен с входом шифратора, выходы первого и второго элементов ИЛИ соединены соответственно с первым и вторым входами элемента И, выход которого соединен с первым входом третьего блока элементов И.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для сложения и вычитания чисел по модулю | 1989 |

|

SU1633399A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-11-15—Публикация

1991-10-31—Подача