Изобретение относится к испытательной технике, предназначено для испытания изделий на импульсные нагрузки на вибростендах электродинамического типа.

Известно устройство для регулирования колебаний, содержащее последовательно соединенные генератор периодических сигналов, регулятор амплитуды, усилитель мощности, вибратор, вибропреобразователь, согласующий усилитель, выпрямитель, фильтр нижних частот, блок сравнения, на второй вход которого подается постоянное опорное напряжение, а выход подключен к управляющему входу регулятора амплитуды.

Недостаток известного устройства - ограниченная область применения, обусловленная отсутствием возможности воспроизведения широкого класса импульсных сигналов.

Наиболее близким по технической сущности и достигаемому результату является устройство для регулирования колебаний, содержащее генератор периодических сигналов, выход которого соединен с первым входом регулятора амплитуды, выход которого подключен через последовательно соединенные ключ, усилитель мощности, вибратор, вибропреобразователь, согласующий усилитель, измеритель пикового значения и первый блок памяти, выходом подключенный к первому входу блока сравнения, выходом подключенного к управляющему входу регулятора амплитуды, последовательно соединенные формирователь прямоугольных сигналов и первый дифференцирующий блок, последовательно соединенные инвертор и второй дифференцирующий блок, выход которого подключен к R-входу триггера, прямой выход которого подключен к управляющему входу ключа и управляющему входу блока памяти, входы инвертора и первого дифференцирующего блока объединены и подключены к выходу формирователя прямоугольных сигналов, первый счетчик импульсов, элемент И.

Недостаток известного устройства - ограниченные функциональные возможности, обусловленные отсутствием возможности программирования количества импульсов в каждой пачке, амплитудных значений импульсов и периода повторения за счет построения структурной схемы, в которой запрограммировано только суммарное количество импульсов за счет введения задатчика числа импульсов, без разделения по пачкам, стабилизации амплитудных значений всех импульсов на одном и том же уровне, равном уровню опорного напряжения, и неизменности периода повторения импульсов, обусловленного применением счетчика с неизменным коэффициентом пересчета.

Предлагаемое изобретение направлено на расширение функциональных возможностей за счет обеспечения возможности программирования количества импульсов в каждой пачке амплитудных значений и периода повторения.

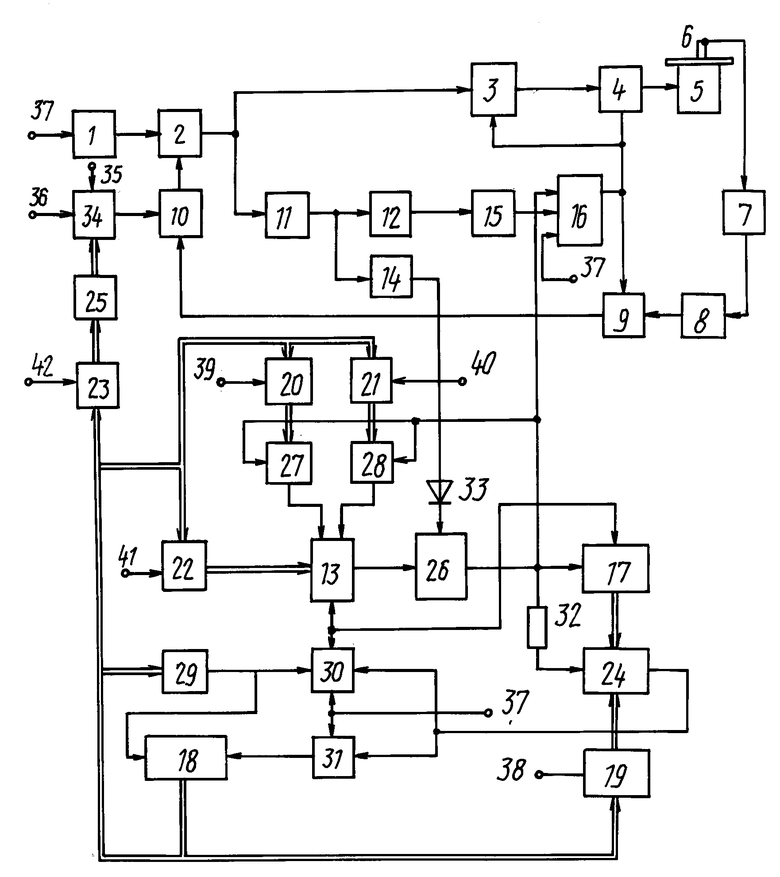

На чертеже изображена структурная схема предложенного устройства для регулирования колебаний.

Устройство содержит последовательно соединенные генератор 1 периодических сигналов, регулятор 2 амплитуды, ключ 3, усилитель 4 мощности, вибратор 5, вибропреобразователь 6, согласующий усилитель 7, измеритель 8 пикового значения, первый блок 9 памяти, блок 10 сравнения, а также формирователь 11 прямоугольных сигналов, инвертор 12, первый счетчик 13 импульсов, первый и второй дифференцирующие блоки 14, 15 соответственно, триггер 16, второй счетчик 17 импульсов, третий счетчик 18 импульсов, второй-шестой блоки 19-23 памяти соответственно, цифровой компаратор 24, цифроаналоговый преобразователь 25, управляемый делитель 26 частоты следования импульсов, элементы И 27, 28, 29, элементы ИЛИ 30, 31, элемент задержки 32, выпрямительный диод 33, коммутатор 34, выход 35 источника опорного напряжения Uоп, шину 36 управления, вход "Запуск" 37, шины 38, 39, 40, 41, 42 записи соответствующих блоков памяти.

Блоки и элементы устройства соединены следующим образом.

Выход генератора 1 периодических сигналов через последовательно соединенные регулятор 2 амплитуды, ключ 3, усилитель 4 мощности, вибратор 5, вибропреобразователь 6, согласующий усилитель 7, измеритель пикового значения 8 и первый блок 9 памяти подключен к первому входу блока 10 сравнения, выход которого подключен к управляющему входу регулятора 2 амплитуды.

Выход регулятора 2 амплитуды через последовательно соединенные формирователь 11 прямоугольных сигналов, инвертор 12 и второй дифференцирующий блок 15 подключен к R-входу триггера 16, прямой выход которого подключен к объединенным управляющему входу ключа 3 и управляющему входу блока 9 памяти.

Выход формирователя 11 прямоугольных сигналов через последовательно соединенные первый дифференцирующий блок 14 и диод 33 в прямом включении подключен к сигнальному входу управляемого делителя 26 частоты следования импульсов, выход которого подключен к счетному входу второго счетчика 17 импульсов, объединенному с S-входом триггера 16 непосредственно, а через элемент 32 задержки - к входу цифрового компаратора 24, сигнальные группы входов которого подключены к прямым выходам разрядов счетчика 17 и второго блока 19 памяти. Выход цифрового компаратора 24 подключен к объединенным входам элементов ИЛИ 30, 31, вторые объединенные входы которых подключены к внешнему входу "Запуск" 37.

Выход второго элемента ИЛИ 31 подключен к счетному входу третьего счетчика 18 импульсов, прямые выходы разрядов которого подключены к адресным входам блоков 19, 20, 21, 22, 23 памяти и входам элемента И 29.

Выходы блоков 20, 21 памяти через элементы И 27, 28 соответственно подключены к суммирующему и вычитающему входам реверсивного счетчика 13 импульсов, выход которого подключен к входу управляемого делителя 26 частоты следования импульсов.

Выход элемента И 29 подключен к входу "Сброс" счетчика 18 импульсов и третьему входу первого элемента ИЛИ 30, выход которого подключен к входу "Прием" счетчика 13 и входу "Сброс" счетчика 17.

Выход блока 23 памяти подключен к входам цифроаналового преобразователя 25, выходом подключенного к второму входу коммутатора 34, первый вход которого подключен к выходу 35 источника опорного напряжения Uоп, а выход - к второму входу блока 10 сравнения. Вторые входы элементов И 27, 28 подключены к выходу делителя 26 частоты следования импульсов.

В исходном состоянии триггер 16 установлен в нуль, содержимое счетчиков 13, 17, 18 равно нулю. Информация, записанная в конкретные ячейки блоков 19, 20, 21, 22, 23 памяти является командой на выполнение в устройствах определенных функций.

В ячейках блока 19 памяти запрограммировано количество импульсов в каждой пачке импульсов. Информация в ячейках блоков 20, 21 памяти (в виде логических единиц и нулей) определяет совместно с элементами И 27, 28 и счетчиком 13 увеличение или уменьшение периода повторения импульсов в каждой пачке импульсов относительно его первоначального значения То, заданного коэффициентом деления No, записанным в соответствующей ячейке блока 22 памяти.

При этом число ячеек блока 22 памяти до номера ячейки с командой "Стоп" определяет число формируемых пачек импульсов. В ячейках блока 23 памяти запрограммировано амплитудное значение каждого формируемого для воспроизведения вибратором 5 импульса.

Счетчик 18 осуществляет считывание информации для каждой пачки импульсов из ячеек блоков 19, 20, 21, 22, 23 памяти, обеспечивая формирование каждой пачки импульсов с заранее заданным периодом повторения импульсов, числом импульсов в пачке, увеличением или уменьшением в пределах каждой пачки периода повторения импульсов, а также амплитудных значений импульсов формируемой импульсной последовательности.

Устройство работает следующим образом.

По команде "Старт", поступающей в форме импульса запуска на вход 37, включается генератор 1 периодических сигналов и устанавливается в исходное положение счетчик 18 импульсов. Импульс запуска через элемент ИЛИ 30 проходит также на входы установки начального значения счетчика 13 импульсов и на вход "Сброс" счетчика 17 импульсов, в результате чего в счетчик 13 записывается число Nо, хранящееся в нулевой ячейке блока 22 памяти. Число No определяет начальный коэффициент деления делителя 26 частоты следования импульсов.

Генератор 1 периодических сигналов формирует на своем выходе сигнал 1 переменного напряжения, в частности синусоидальное напряжение, которое через регулятор 2 амплитуды поступает на вход ключа 3.

В исходном состоянии триггер 16 находится в нуле, ключ 3 разомкнут и в обмотку подвижной катушки вибратора 5 сигналы не поступают. Подвижная система вибратора 5 находится в положении равновесия.

На выходе формирователя 11 прямоугольных сигналов формируются прямоугольные импульсы, соответствующие положительным полупериодам синусоидального напряжения, которое дифференцируется первым дифференцирующим блоком 14.

Одновременно инвертированные инвертором 12 импульсы дифференцируются вторым дифференцирующим блоком 15 и поступают на R-вход триггера 16, подтверждая его нулевое состояние.

Сигналы с выхода дифференцирующего блока 14 после прохождения через диод 33 и соответствующие переднему фронту прямоугольного сигнала с выхода формирователя 11 прямоугольных сигналов поступают на вход делителя 26 частоты следования импульсов, коэффициент деления которого определяется содержимым счетчика 13, определяемым содержимым нулевой ячейки блока 22 памяти.

Первый импульс проходящей на выход делителя 26 частоты следования импульсов поступает на счетный вход счетчика 17 непосредственно, а через элемент 32 задержки - на вход цифрового компаратора 24.

При достижении равенства содержимого счетчика 17 импульсов содержимому нулевой ячейки блока 19 памяти цифровой компаратор 24 вырабатывает на выходе импульс, который через элемент ИЛИ 30 устанавливает счетчик 17 в нуль, а через элемент ИЛИ 31 поступает на счетный вход счетчика 18, в результате чего счетчик 18 в следующем цикле адресует следующие ячейки блоков 19, 20, 21, 22, 23 памяти. Одновременно этот же импульс через элемент ИЛИ 30 поступает на вход "Прием" счетчика 13, в результате в него записывается число N1 - содержимое первой ячейки блока 22 памяти.

Первый же импульс, возникающий на выходе делителя 26 частоты следования импульсов, поступает на S-вход триггера 16, устанавливая его в единицу. При этом ключ 3 замыкается и импульсный сигнал поступает в обмотку подвижной системы вибратора 5, вызывая его перемещение по траектории, определенной формой сигнала, поступающего в обмотку подвижной части вибратора 5.

Одновременно сигнал с прямого выхода триггера 16 поступает на управляющий вход блока 9 памяти и подготавливает его к запоминанию пикового значения сигнала на выходе согласующего усилителя 7 и фиксируемого измерителем пикового значения 8 и поступающего с выхода вибропреобразователя 6.

В режиме стабилизации пиковых значений импульсных сигналов, формируемых вибратором 5, на управляющий вход 36 коммутатора 34 поступает нулевой сигнал, благодаря чему на выход коммутатора 34 поступает сигнал Uоп.

Зафиксированное в блоке 9 памяти значение сигнала в момент паузы сравнивается с опорным Uоп в блоке 10 сравнения и подается на управляющий вход регулятора 2 амплитуды, подстраивая амплитуду импульсных сигналов до заданного значения.

В момент окончания рабочего импульса на R - вход триггера 16 через инвертор 12 и дифференцирующий блок 15 поступает импульс, устанавливающий триггер 16 в нуль, благодаря чему размыкается ключ 3. Таким образом, формируются импульсные сигналы, поступающие в обмотку подвижной системы вибратора 5.

В ячейках блока 22 памяти записаны коэффициенты деления частоты, определяющие начальный период повторения импульсов в пачке, количество импульсов в каждой пачке зафиксировано в ячейках блока 19 памяти, адреса ячеек которого определяются изменяющимся содержанием счетчика 18, на счетный вход которого поступает очередной импульс, формируемый на выходе цифрового компаратора 24 при воспроизведении очередной серии импульсов. Число ячеек блока 22 памяти до номера ячейки с запрограммированной командой "Стоп" определяет число формируемых пачек импульсов. Содержимое ячеек блоков 20 и 21 памяти (записанное в виде логических сигналов единица - нуль) определяет с элементами И 27, И 28 соответственно и счетчиком 13 импульсов увеличение или уменьшение периода повторения импульсов в каждой пачке импульсов относительно его начального значения, заданного коэффициентом деления, записанным в соответствующей ячейке блока 22 памяти.

Изменение периода следования импульсов в каждой формируемой пачке происходит следующим образом.

При поступлении импульса на вход "Запуск" 37 нулевое содержимое счетчика 18 импульсов изменяется на единицу младшего разряда и определяет адреса ячеек блоков 20 и 21 памяти, условно назовем их нулевыми ячейками.

Если в нулевых ячейках блоков 20 и 21 памяти записаны логические нули, то элементы И 27, И 28 закрыты по первым входам, поэтому содержимое счетчика 13 остается равным No и на выходе делителя 26 частоты следования импульсов формируются импульсы постоянной частоты в No раз меньше частоты следования импульсов, поступающих через диод 33 с выхода блока 14 дифференцирования на вход делителя 26 частоты.

Если в нулевой ячейке блока 20 памяти записана логическая единица, а в нулевой ячейке блока 21 памяти - логический нуль, то элемент И 27 по первому ходу открыт, а элемент И 28 закрыт, то каждый импульс, возникающий на выходе делителя 26 частоты, проходит через элемент И 27 на суммирующий вход счетчика 13, содержимое которого увеличивается на единицу младшего разряда, а значит и увеличивается коэффициент деления делителя 26 частоты следования импульсов.

Таким образом, на выходе делителя 26 частоты, на счетном входе счетчика 17 и на выходе ключа 3 формируется пачка импульсов с уменьшающейся во времени частотой следования.

Если в нулевой ячейке блока 20 памяти записан логический нуль, а в нулевой ячейке блока 21 памяти записана логическая единица, то элемент И 27 закрыт по первому входу, а элемент И 28 открыт по первому входу, то каждый импульс формируется на выходе делителя 26 частоты, проходит через элемент И 28 на вычитающий вход счетчика 13, содержимое которого уменьшается на единицу младшего разряда, а значит и уменьшается коэффициент деления делителя 26 частоты следования импульсов. При этом на выходе делителя 26 частоты следования импульсов, на счетном входе счетчика 17 и на выходе ключа 3 формируется пачка импульсов с увеличивающейся во времени частотой следования.

При заранее заданном содержимом счетчика 18, определяемом формированием сигнала на выходе элемента И 29, счетчик 18 сбрасывается в нуль, а в счетчик 13 заносится нулевое содержимое ячейки, адрес которой соответствует формированию импульса на выходе элемента И 29.

При поступлении импульса запуска происходит также адресация нулевой ячейки блока 23 памяти благодаря считыванию информации с помощью кода счетчика 18.

При поступлении каждого очередного импульса на счетный вход счетчика 18 происходит считывание информации из соответствующих ячеек блока 23 памяти, благодаря чему на выходе ЦАП 25 формируется сигнал, поступающий на второй вход коммутатора 34 и определяющий амплитудное значение на выходе регулятора 2 амплитуды. В этом режиме на управляющий вход 36 коммутатора 34 поступает единичный сигнал.

По сравнению с прототипом предложенное устройство обеспечивает более широкую область применения за счет обеспечения возможности программирования количества импульсов в каждой пачке, амплитудного значения каждого импульса и переменного периода повторения (скважности импульсной последовательности).

Изобретение относится к испытательной технике и предназначено для испытания изделий на импульсные нагрузки. В устройстве расширены функциональные возможности за счет обеспечения возможности программирования количества импульсов в каждой пачке амплитудных значений и периода повторения. Устройство содержит последовательно соединенные генератор 1 периодических сигналов, регулятор 2 амплитуды, ключ 3, усилитель 4 мощности, вибратор 5, вибропреобразователь 6, согласующий усилитель 7, измеритель 8 пикового значения, первый блок 9 памяти, блок 10 сравнения, а также формирователь 11 прямоугольных сигналов, инвертор 12, первый счетчик 13 импульсов, первый и второй дифференцирующие блоки 14, 15 соответственно, триггер 16. Новым является введение в устройство второго счетчика 17 импульсов, третьего счетчика 18 импульсов, второго - шестого блоков 19 - 23 памяти соответственно, цифрового компаратора 24, цифроаналогового преобразователя 25, управляемого делителя 26 частоты следования импульсов, элементов ИЛИ 30, 31, элемента задержки 32, диода 33, коммутатора 34, а также связи между ними. 1 ил.

УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ КОЛЕБАНИЙ, содержащее генератор периодических сигналов, выход которого соединен с информационным входом регулятора амплитуды, выход которого подключен через последовательно соединенные ключ, усилитель мощности, вибратор, вибропреобразователь, согласующий усилитель, измеритель пикового значения к информационному входу первого блока памяти, выходом подключенного к первому входу блока сравнения, выходом подключенного к управляющему входу регулятора амплитуды, последовательно соединенные формирователь прямоугольных сигналов и первый дифференцирующий блок, последовательно соединенные инвертор и второй дифференцирующий блок, выход которого подключен к R-входу триггера, прямой выход которого подключен к управляющему входу ключа и управляющему входу первого блока памяти, входы инвертора и первого дифференцирующего блока объединены и подключены к выходу формирователя прямоугольных сигналов, а также первый счетчик импульсов и элемент И, отличающееся тем, что оно содержит второй и третий счетчики импульсов, второй, третий, четвертый, пятый и шестой блоки памяти, цифровой компаратор, цифроаналоговый преобразователь, управляемый делитель частоты следования импульсов, второй и третий элементы И, первый и второй элементы ИЛИ, элемент задержки, выпрямительный диод, коммутатор, а первый счетчик импульсов выполнен реверсивным, причем выход первого дифференцирующего блока подключен через последовательно соединенные выпрямительный диод и делитель частоты следования импульсов к счетному входу второго счетчика импульсов непосредственно, а через элемент задержки - к входу цифрового компаратора, первая и вторая группы входов которого подключены соответственно к разрядным выходам второго счетчика импульсов и второго блока памяти, выход цифрового компаратора подключен к вторым объединенным входам первого и второго элементов ИЛИ, первые входы элементов ИЛИ объединены и подключены к внешнему входу "Запуск", выход второго элемента ИЛИ подключен к счетному входу третьего счетчика импульсов, прямые выходы разрядов которого подключены через третий элемент И к третьему входу первого элемента ИЛИ, объединенному с входом "Сброс" третьего счетчика импульсов, прямые выходы разрядов третьего счетчика импульсов подключены к адресным входам блоков памяти с второго по шестой, выходы третьего и четвертого блоков памяти через первый и второй элементы И соответственно подключены к суммирующему и вычитающему входам первого счетчика импульсов, выходы пятого блока памяти подключены к входам прямых разрядов первого счетчика импульсов, прямые выходы разрядов которого подключены к управляющим входам управляемого делителя частоты следования импульсов, вход "Установка начального состояния" первого счетчика импульсов объединен с входом "Сброс" второго счетчика импульсов и подключен к выходу первого элемента ИЛИ, выход управляемого делителя частоты следования импульсов подключен к объединенным вторым входам первого и второго элементов И и S-входу триггера, выходы шестого блока памяти подключены к входам цифроаналогового преобразователя, выход которого подключен к второму входу коммутатора, первый вход которого подключен к выходу источника опорного напряжения, а выход - к второму входу блока сравнения.

| Устройство для регулирования колебаний | 1982 |

|

SU1068905A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1994-12-15—Публикация

1991-10-23—Подача