Изобретение относится к испытательной технике и может быть использовано в машиностроении и приборостроении.

Известен способ определения рассеяния энергии и собственной частоты механической колебательной системы, заключающийся в том, что возбуждают затухающие колебания исследуемой системы, фиксируют моменты прохождения положения равновесия и момент равенства нулю скорости колебаний.

Известное устройство для определения рассеяния энергии и собственной частоты механической системы содержит вибропреобразователь, устанавливаемый на испытуемом объекте, два ключа, два регистра, генератор сигналов, интегратор, два знакочувствительные элемента, элемент И, два дифференцирующих элемента, четыре диода, два инвертора, два триггера, два счетчика импульсов, два цифроаналоговых преобразователя, элемент задержки, блок деления, три блока умножения и два преобразователя, в качестве генератора сигналов использован генератор импульсов, а вибропреобразователь представляет собой преобразователь скорости, выход которого подключен к входам первого знакочувствительного элемента и интегратора, выход которого подключен к входу второго знакочувствительного элемента, выход которого подключен к первому входу элемента И, к второму входу которого подключен выход первого знакочувствительного элемента, выход элемента И подключен к входу первого дифференцирующего элемента, выход которого подключен через первый диод в прямом направлении к единичному входу первого триггера, обнуляющий вход которого подключен к выходу первого инвертора, выход второго знакочувствительного элемента подключен к входу второго дифференцирующего элемента, выход которого через второй диод в прямом направлении подключен к единичному входу второго триггера, обнуляющий вход которого подключен к выходу второго инвертора, выход первого дифференцирующего элемента подключен через третий диод в обратном направлении к входу первого инвертора, выход второго дифференцирующего элемента через четвертый диод в обратном направлении подключен к входу второго инвертора, выход которого подключен к входу элемента задержки и к управляющим входам первого и второго регистров, выход элемента задержки подключен к установочным входам первого и второго счетчиков, входы которых соответственно подключены к выходам первого и второго ключей, входы которых подключены к выходу генератора импульсов, управляющие входы - соответственно к выходам первого и второго триггеров, выходы первого и второго счетчиков импульсов подключены соответственно к входам первого и второго регистров, выходы которых подключены соответственно к входам первого и второго цифроаналоговых преобразователей, выход первого цифроаналогового преобразователя подключен к первому входу первого блока умножения, выход которого подключен к входам первого и второго преобразователей, выход второго цифроаналогового преобразователя подключен к входу "Делитель" блока деления, вход "Делимое" которого предназначен для подключения к источнику напряжения величиной π, а выход - к второму входу первого блока умножения, выходы первого и второго преобразователей подключены соответственно к вторым входам второго и третьего блоков умножения, выходы которых являются соответственно первым и вторым выходами устройства.

Недостаток известных способов определения рассеяния энергии и собственной частоты механической колебательной системы и устройства для его осуществления - отсутствие возможности определения параметров колебаний нелинейной механической колебательной системы, что сужает область использования.

Цель изобретения - расширение области использования за счет определения рассеяния энергии и собственной частоты также и нелинейной механической колебательной системы.

Это достигается тем, что при способе определения рассеяния энергии и собственной частоты механической колебательной системы возбуждают затухающие колебания исследуемой системы, фиксируют моменты прохождения положения равновесия и момент равенства нулю скорости колебаний, измеряют первый интервал Δ1 времени между первым моментом t1 прохождения положения равновесия и моментом t2 равенства нулю скорости колебаний и второй интервал Δ2 времени между первым и вторым моментами t1 и t3прохождения равновесия и параметр h рассеяния энергии и собственную частоту ωол колебаний линейной механической системы определяют из условий

h =  ctg

ctg ,

,

ωол=

измеряют третий интервал Δ3 времени между третьим и четвертым t4, t5моментами прохождения положения равновесия, а также амплитудные значения а1, а2 во втором и третьем интервалах времени и параметр α2рассеяния энергии и собственную частоту ωон колебаний нелинейной механической системы определяют из условий

измеряют третий интервал Δ3 времени между третьим и четвертым t4, t5моментами прохождения положения равновесия, а также амплитудные значения а1, а2 во втором и третьем интервалах времени и параметр α2рассеяния энергии и собственную частоту ωон колебаний нелинейной механической системы определяют из условий

α2=

·

·  , ωон=

, ωон=

Кроме того, устройство для определения рассеяния энергии и собственной частоты механической системы, содержащее вибропреобразователь в виде преобразователя скорости, устанавливаемый на испытуемый объект, два ключа, два регистра, генератор сигналов в виде генератора импульсов, интегратор, два знакочувствительных элемента, элемент И, два дифференцирующих элемента, четыре диода, два инвертора, два триггера, два счетчика импульсов, два цифроаналоговых преобразователя, элемент задержки, блок деления, три блока умножения и два преобразователя, выход преобразователя скорости подключен к входам первого знакочувствительного элемента и интегратора, выход которого подключен к входу второго знакочувствительного элемента, выход которого подключен к первому входу элемента И, к второму входу которого подключен выход первого знакочувствительного элемента, выход элемента И подключен к входу первого дифференцирующего элемента, выход которого подключен через первый диод в прямом направлении к единичному входу первого триггера, обнуляющий вход которого подключен к выходу первого инвертора, выход второго знакочувствительного элемента подключен к входу второго дифференцирующего элемента, выход которого через второй диод в прямом направлении подключен к единичному входу второго триггера, обнуляющий вход которого подключен к выходу второго инвертора, выход первого дифференцирующего элемента подключен через третий диод в обратном направлении к входу первого инвертора, выход второго дифференцирующего элемента через четвертый диод в обратном направлении подключен к входу второго инвертора, выход которого подключен к входу элемента задержки и управляющим входам первого и второго регистров, выход элемента задержки подключен к установочным входам первого и второго счетчиков, входы которых соответственно подключены к выходам первого и второго ключей, входы которых подключены к выходу генератора импульсов, а управляющие входы - соответственно к выходам первого и второго триггеров, выходы первого и второго счетчиков импульсов подключены соответственно к входам первого и второго регистров, выходы которых подключены соответственно к входам первого и второго цифроаналоговых преобразователей, выход первого цифроаналогового преобразователя подключен к первому входу первого блока умножения, выход которого подключен к входам первого и второго преобразователей, выход второго цифроаналогового преобразователя подключен к входу "Делитель" блока деления, вход "Делимое" которого предназначен для подключения к источнику напряжения величиной π, а выход - к второму входу первого блока умножения, выходы первого и второго преобразователей подключены соответственно к вторым входам второго и третьего блоков умножения, выходы которых являются соответственно первым и вторым выходами устройства, снабжено третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым ключами, первым и вторым элементами ИЛИ, вторым элементом И, элементом НЕ, третьим и четвертым счетчиками импульсов, первым и вторым дешифраторами, третьим триггером, таймером, первым и вторым коммутаторами, вычислительным блоком, регистратором, причем выход второго знакочувствительного элемента подключен к входу второго дифференцирующего элемента через шестой ключ, а выход первого элемента И подключен к входу первого дифференцирующего элемента через седьмой ключ, прямой выход первого триггера подключен к управляющему входу первого ключа через последовательно соединенные третий ключ и первый элемент ИЛИ, второй вход которого подключен к прямому выходу второго триггера через четвертый ключ, прямой выход второго триггера подключен к управляющему входу второго ключа через пятый ключ, единичный и нулевой входы второго триггера подключены к входу второго элемента ИЛИ, выход которого подключен к входу третьего счетчика импульсов, разрядные выходы которого подключены к входам первого дешифратора, выходом подключенного через элемент НЕ к объединенным управляющим входам шестого и седьмого ключей и к второму входу второго элемента И, первый вход которого подключен к источнику управляющего напряжения, а выход - к управляющему входу третьего ключа, выход второго инвертора подключен к входу таймера непосредственно, а к единичному входу третьего триггера - через девятый ключ, выход таймера подключен к входу "Сброс" третьего счетчика непосредственно, а через восьмой ключ - к входу четвертого счетчика импульсов, разрядные выходы которого подключены к входам второго дешифратора, прямой и инверсный выходы третьего триггера подключены к управляющим входам четвертого и пятого ключей соответственно, выход первого цифроаналогового преобразователя подключен к первому входу первого блока умножения через первый коммутатор, выход второго цифроаналогового преобразователя подключен к входу первого блока деления через второй коммутатор, первый и второй выходы вычислительного блока подключены к третьему и четвертому входам регистратора соответственно, первый и второй входы которого подключены к выходам второго и третьего блоков умножения соответственно.

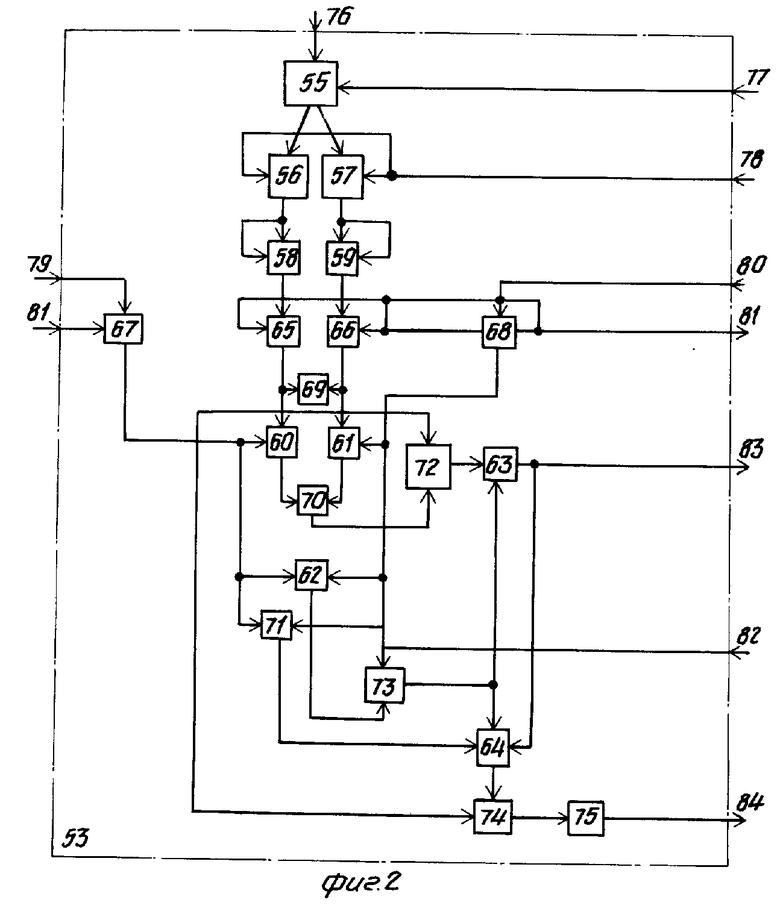

Кроме того, вычислительный блок содержит коммутатор, первый и второй пиковые детекторы, первый, второй, третий, четвертый, пятый, шестой седьмой блоки умножения, первый, второй, третий, четвертый ключи, первый, второй и третий сумматоры, первый, второй и третий блоки деления, усилитель, причем вход коммутатора объединен с первым входом вычислительного блока, первый выход коммутатора подключен через последовательно соединенные первый пиковый детектор, первый блок умножения, первый ключ и третий блок умножения к суммирующему входу второго сумматора, вычитающий вход которого подключен к второму выходу коммутатора через последовательно соединенные второй пиковый детектор, второй блок умножения, второй ключ и четвертый блок умножения, выходы первого и второго ключей подключены к суммирующему и вычитающему входам первого сумматора соответственно, выходы первого и второго сумматоров подключены к входам "Делитель" и "Делимое" соответственно первого блока деления, выход которого через седьмой блок умножения подключен к первому выходу вычислительного блока, вторые входы третьего и пятого блоков умножения и вычитающий вход третьего сумматора объединены и подключены к выходу третьего ключа, второй вход четвертого блока умножения, первый вход пятого блока умножения и суммирующий вход пятого сумматора объединены и подключены к выходу четвертого ключа, выход пятого блока умножения подключен к входу "Делитель" второго блока деления, к входу "Делимое" которого подключен выход источника напряжения величиной π, выход третьего блока деления подключен к второму входу шестого блока умножения, объединенному с первым входом седьмого блока умножения, второй вход которого подключен к выходу шестого блока умножения, а третий вход - к выходу третьего сумматора, выход седьмого блока умножения подключен к входу "Делимое" третьего блока деления, вход "Делитель" которого подключен к выходу первого сумматора, а выход через усилитель - к второму выходу вычислительного блока, первый вход вычислительного блока подключен к выходу интегратора, управляющий вход коммутатора подключен к второму входу вычислительного блока, объединенному с выходом третьего триггера, третий вход вычислительного блока подключен к входу "Сброс", четвертый вход вычислительного блока объединен с входом третьего ключа и подключен к выходу второго коммутатора, пятый вход вычислительного блока объединен с входом четвертого ключа и подключен к выходу первого коммутатора, шестой вход вычислительного блока объединен с управляющими входами первого, второго, третьего и четвертого ключей и подключен к выходу второго дешифратора, седьмой вход вычислительного блока подключен к выходу источника напряжения величиной π.

При жесткой характеристике восстанавливающей силы дифференциальное уравнение свободных колебаний консервативной системы можно представить в виде +ω

+ω

где ω , α2=

, α2=  , c > 0, c1> 0 Для мягкой характеристики дифференциальное уравнение свободных колебаний имеет вид

, c > 0, c1> 0 Для мягкой характеристики дифференциальное уравнение свободных колебаний имеет вид +ω

+ω (2) Для систем, описываемых уравнениями (1), (2), уравнение скелетной кривой (зависимость частоты ωо свободных колебаний от амплитуды) при учете лишь двух первых членов разложения нелинейной части имеет вид соответственно

(2) Для систем, описываемых уравнениями (1), (2), уравнение скелетной кривой (зависимость частоты ωо свободных колебаний от амплитуды) при учете лишь двух первых членов разложения нелинейной части имеет вид соответственно

ω =  1 -

1 -

a

a

(3) или

ω =  1 -

1 -

a

a ,

,

(3а)

ω =  1 +

1 +

a

a

(4) или

ω =  1 +

1 +

a

a ,

,

(4а)

где а - полуразмах колебаний.

Таким образом, скелетная кривая нелинейной колебательной системы содержит информацию о параметрах ωо, α2 или ωо, С, С1.

Рассмотрим для определенности соотношение (4а)

ω =  1 +

1 +

a

a При полуразмахах а1, а2 колебаний из уравнения (4а) получим два уравнения относительно неизвестных ωо=Х-1 и С1С1=Y

При полуразмахах а1, а2 колебаний из уравнения (4а) получим два уравнения относительно неизвестных ωо=Х-1 и С1С1=Y

ω1= X 1 +

1 +  Ya

Ya ,

,

(5)

ω2= X 1 +

1 +  Ya

Ya ,

,

(5a) Преобразуем уравнения (5) и (5а)

(6) Решим систему уравнений (6) матричным методом (по методу Крамера)

Δ=

=

= ,

,

(7)

Δ1=

=

=

(8)

Δ2=

=

=

(9) Определим неизвестные Х/ ωо-1/, Y  .

.

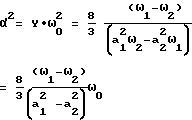

X = ω =

=  , ω0=

, ω0=

(10) или ωо=ω2 K1-ω1 K2, (10a) где

K1=  =

=  ,

,

K2=  =

=

(11)

Y =  C′=

C′=  =

=

Но так как ωо2=Сm-1, C=m ωо2, то при определении любым методом С и m (например, методом пробных масс) из уравнения (11) можно определить коэффициент С1

Но так как ωо2=Сm-1, C=m ωо2, то при определении любым методом С и m (например, методом пробных масс) из уравнения (11) можно определить коэффициент С1

C1= C ·

(11а) Из уравнения (11) также следует

Y =  =

=  =

=

(11б) Из выражений (10), (11б) определим · ω

· ω

=

=

(12) Таким образом, на основании выражений (10) и (12) можно определить ωо и α2.

Для определения ωо и α2 необходимо зафиксировать значения а1, ω1 и а2, ω2.

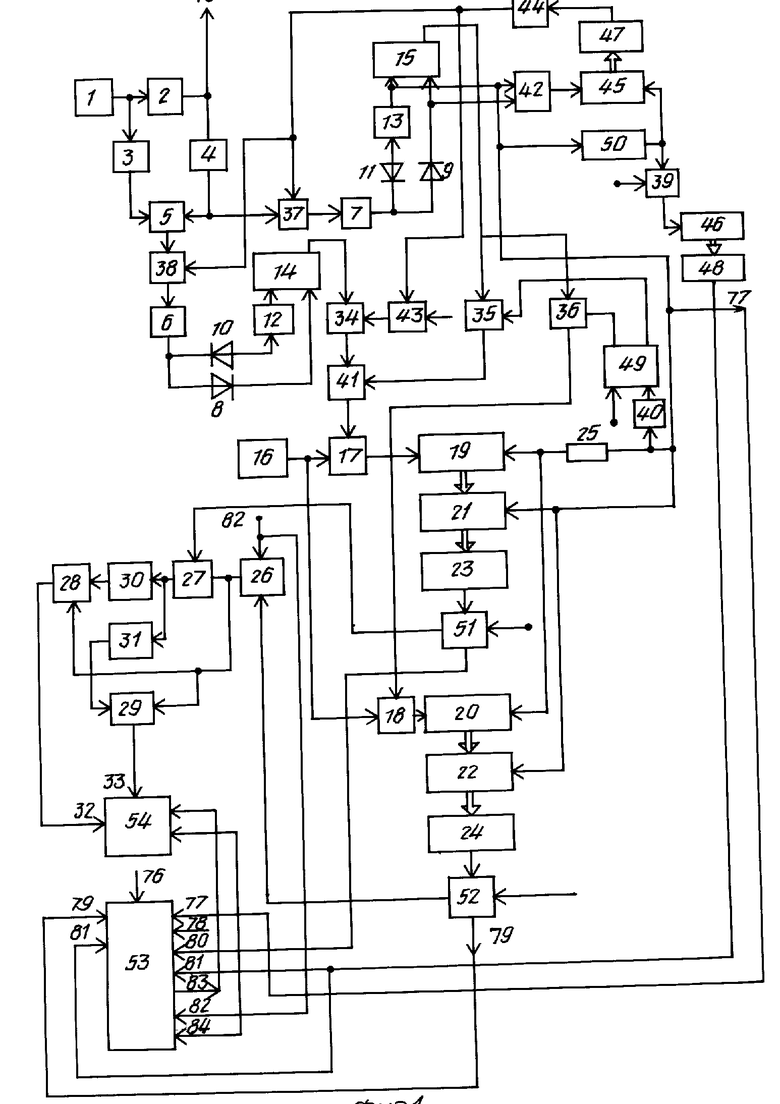

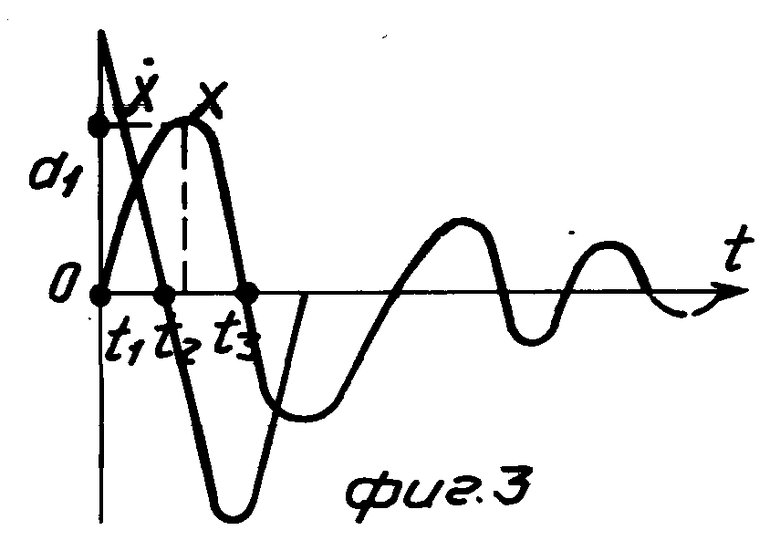

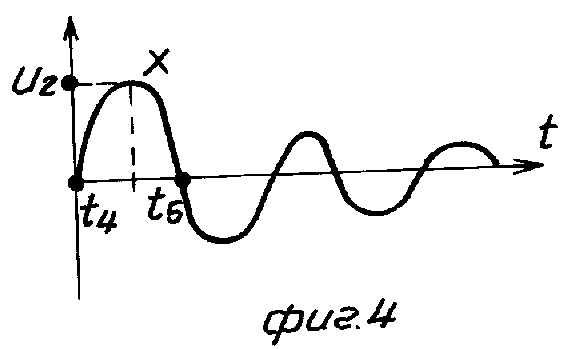

На фиг. 1 представлена структурная схема устройства для определения рассеяния и собственной частоты механической системы; на фиг.2 - структурная схема вычислительного блока; на фиг.3 - эпюра затухающих колебаний перемещения Х и скорости  при внешнем воздействии с амплитудой β1; на фиг. 4 - эпюра затухающих колебаний перемещения Х при внешнем воздействии с амплитудой β2.

при внешнем воздействии с амплитудой β1; на фиг. 4 - эпюра затухающих колебаний перемещения Х при внешнем воздействии с амплитудой β2.

Способ осуществляется следующим образом.

Исследуемая механическая колебательная система возбуждается коротким импульсом калиброванной амплитуды β1, а затем после установления режима устойчивого равновесия - коротким импульсом другой калиброванной амплитуды β2.

Свободные колебания в каждом случае представляют собой затухающие колебания.

Фиксируют сигнал, равны промежутку времени Δ2 между соседними моментами положения равновесия и амплитудное значение а1 в первом полупериоде при возбуждении системы импульсом с амплитудным значением β1, а затем после установления системы в положение устойчивого равновесия фиксируют сигнал, равный промежутку времени Δ3 между соседними моментами положения равновесия, и амплитудное значение а2 в первом полупериоде колебаний при возбуждении системы импульсом с амплитудным значением β2.

Как следует из теоретических исследований (соотношения 10 и 12), значения коэффициентов ωо и α2 определяют в результате функционального преобразования ω1, ω2, а1, а2; ω1, ω2 связаны с Δ2, Δ3 известными соотношениями

ω1= π Δ2-1,ω2=π Δ3-1 (13) Тогда соотношение (10) при учете выражения (13) принимает вид ω0=  ·

·  ,

,

(14) а соотношение (12) принимает вид

α2=  ·

·

(15) или

α2=  ·

·

ω0

ω0

(16)

Таким образом, для определения коэффициентов ωо и α2 необходимо провести измерения Δ2, а1, Δ3, а2 и выполнить функциональные преобразования по соотношениям (14) и (15).

Устройство содержит измерительный преобразователь 1 скорости  , интегратор 2, первый 3 и второй 4 знакочувствительные элементы, элемент И5, первый 6 и второй 7 дифференцирующие элементы, первый 8, второй 9, третий 10 и четвертый 11 диоды, первый 12 и второй 13 инверторы, первый 14 и второй 15 триггеры, генератор 16 импульсов, первый 17 и второй 18ключи, первый 19 и второй 20 счетчики импульсов, первый 21 и второй 22 регистры, первый 23 и второй 24 цифроаналоговые преобразователи (ЦАП), элемент 25 задержки, блок 26 деления, первый 27, второй 28 и третий 29 блоки умножения, первый 30 и второй 31 преобразователи, первый 32 и второй 33 выходы устройства, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый ключи 34-40 соответственно, элементы ИЛИ 41, 42, второй элемент И 43, элемент НЕ 44, третий и четвертый счетчики 45, 46 импульсов, первый и второй дешифраторы 47, 48, третий триггер 49, таймер 50, первый и второй коммутаторы 51, 52 соответственно, вычислительный блок 53, регистратор 54.

, интегратор 2, первый 3 и второй 4 знакочувствительные элементы, элемент И5, первый 6 и второй 7 дифференцирующие элементы, первый 8, второй 9, третий 10 и четвертый 11 диоды, первый 12 и второй 13 инверторы, первый 14 и второй 15 триггеры, генератор 16 импульсов, первый 17 и второй 18ключи, первый 19 и второй 20 счетчики импульсов, первый 21 и второй 22 регистры, первый 23 и второй 24 цифроаналоговые преобразователи (ЦАП), элемент 25 задержки, блок 26 деления, первый 27, второй 28 и третий 29 блоки умножения, первый 30 и второй 31 преобразователи, первый 32 и второй 33 выходы устройства, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый ключи 34-40 соответственно, элементы ИЛИ 41, 42, второй элемент И 43, элемент НЕ 44, третий и четвертый счетчики 45, 46 импульсов, первый и второй дешифраторы 47, 48, третий триггер 49, таймер 50, первый и второй коммутаторы 51, 52 соответственно, вычислительный блок 53, регистратор 54.

Вычислительный блок 53 содержит коммутатор 55, первый и второй пиковые детекторы 56, 57 соответственно, блоки 58-64 умножения, ключи 65-68, сумматоры 69-71, блоки 72-74 деления, усилитель 75, информационный вход 76, первый управляющий вход 77, вход "Сброс" 78, второй и третий информационные входы 79, 80 соответственно, второй управляющий вход 81, четвертый информационный вход 82, первый и второй выходы 83, 84 соответственно.

Элементы и блоки устройства соединены следующим образом.

Выход преобразователя 1 скорости подключен к объединенным входам интегратора 2 и первого знакочувствительного элемента 3, выход интегратор 2 подключен к входу второго знакочувствительного элемента 4, выход которого подключен к первому входу элемента И5 непосредственно, а к единичному входу второго триггера 15 - через последовательно соединенные ключ 37, второй дифференцирующий элемент 7 и второй диод 9 в прямом направлении.

Нулевой вход триггера 15 подключен к выходу второго дифференцирующего элемента 7 через последовательно соединенные четвертый диод 11 и второй инвертор 13.

Выход первого знакочувствительного элемента 3 подключен к второму входу элемента И5, выход которого через последовательно соединенные ключ 38, первый дифференцирующий элемент 6 и первый диод 8, включенный в прямом направлении, подключен к единичному входу первого триггера 14, нулевой вход которого подключен к выходу первого дифференцирующего элемента 6 через последовательно соединенные третий диод 10, включенный в обратном направлении, и первый инвертор 12. Единичный выход триггера 14 подключен через последовательно соединенные ключ 34 и элемент ИЛИ 41 к управляющему входу ключа 17. Единичный выход триггера 15 подключен через ключ 35 к второму входу элемента ИЛИ 41 а через ключ 36 - к управляющему входу ключа 18. Информационные входы ключей 17, 18 объединены и подключены к выходу генератора 16 импульсов.

Выходы первого и второго ключей 17, 18 подключены к входам первого и второго счетчиков 19, 20 импульсов соответственно.

Выходы разрядов первого и второго счетчиков 19, 20 подключены к разрядным входам первого и второго регистров 21, 22 соответственно. Выходы регистров 21, 22 через первый и второй цифроаналоговые преобразователи 23, 24 подключены к входам коммутаторов 51, 52 соответственно.

Первые выходы коммутаторов 51, 52 подключены соответственно к первому входу блока 27 умножения и входу "Делитель" блока 26 деления, к входу "Делимое" которого подключен выход источник напряжения величиной π (выход 82).

Выход блок 26 деления подключен к объединенным первым входам первого, второго и третьего блоков 27, 28, 29 умножения соответственно. Выход первого блока 27 умножения подключен к объединенным входам первого и второго преобразователей 30, 31, выходы которых подключены к вторым входам блоков 28, 29 умножения соответственно, выходы которых подключены к первому и второму входам 32, 33 соответственно регистратора 54.

Выход второго инвертора 13 подключен к управляющим входам первого и второго регистров 21, 22 непосредственно и входу 77 блока 53, а к установочным входам первого и второго счетчиков 19, 20 - через элемент 25 задержки. Выход инвертора 13 и катод диода 9 подключены к входам элемента ИЛИ 42, выход которого подключен к счетному входу счетчика 45 импульсов, разрядные выходы которого подключены к входам дешифратора 47, выход которого подключен к управляющему входу ключа 37, объединенному с управляющим входом ключа 38 и вторым входом элемента И 43 через элемент НЕ 44.

Выход инвертора 13 подключен к входу таймера 50, выход которого подключен к входу "Сброс" счетчика 45 импульсов непосредственно, а через ключ 39 - к счетному входу счетчика 46 импульсов, разрядные выходы которого подключены к входам дешифратора 48. Единичный вход триггера 49 подключен к выходу инвертора 13 через ключ 40, единичный и нулевой выходы триггера 49 подключены к управляющим входам ключей 35, 36 соответственно.

Выход интегратора 2 подключен к входу 76 вычислительного блока 53, объединенному с входом коммутатора 55, выходы которого подключены к входам первого и второго пиковых детекторов 56, 57, к входам сброса которых подключен вход "Сброс" 78.

Выходы пиковых детекторов 56, 57 подключены к объединенным входам блоков 58, 59 умножения соответственно, выход первого из которых через ключ 65, а выход второго через ключ 66 подключены к первым входам блоков 60, 61 умножения соответственно.

Выходы блоков 60, 61 умножения подключены к суммирующему и вычитающему входам соответственно сумматора 70. Выходы ключей 65, 66 подключены к суммирующему и вычитающему входам сумматора 69. Выходы сумматоров 69, 70 подключены к входам "Делитель" и "Делимое" блока 72 деления. Выход блока 72 деления подключен к второму входу блока 63 умножения, первый вход которого подключен к выходу блока 73 деления, вход "Делимое" которого подключен к входу 82, на который поступает сигнал, равный π, а вход "Делитель" подключен к выходу блока 62 умножения, входы которого объединены с вторыми входами блоков 60, 61 умножения соответственно.

Выход блока 63 умножения подключен к первому входу блока 64 умножения, второй вход которого подключен к выходу блока 73 деления,з а третий вход - к выходу сумматора 71, вычитающий вход которого подключен к второму входу блока 60 умножения, а суммирующий вход - к второму входу блока 61 умножения. Выход блока 64 умножения подключен к входу "Делимое" блока 74 деления, вход "Делитель" которого подключен к выходу сумматора 69.

Второй вход блока 60 умножения через ключ 67 подключен к входу 79, подключенному к второму выходу коммутатора 52.

Второй вход блока 61 умножения через ключ 68 подключен к входу 80, подключенному к второму выходу коммутатора 51. Управляющие входы ключей 65-68 подключены к входу 81, подключенному к выходу дешифратора 48.

Выход блока 63 умножения подключен к выходу 83, соединенному с третьим входом регистратора 54. Выход блока 74 деления через усилитель 75 подключен к выходу 84, соединенному с четвертым входом регистратора 54.

Устройство работает следующим образом.

Режим А. В исходном состоянии на первом входе элемента И 43 установлен единичный сигнал, на втором входе элемента И 43 также единичный сигнал, так как на выходе дешифратора 47 - нулевой сигнал, а на выходе элемента НЕ 44 - единичный сигнал. Ключи 34, 37, 38 замкнуты, ключи 39, 40 разомкнуты. Триггер 49 установлен в нуль, ключ 36 замкнут, ключ 35 разомкнут.

На управляющих входах коммутаторов 51, 52 нулевые сигналы.

Импульс, проходящий через диод 9, поступает также через элемент ИЛИ 42 на счетный вход счетчика 45, устанавливая его в состояние 01/счетчик двухразрядный, единица устанавливается в младшем разряде/. Сигнал на выходе дешифратора 47 не изменяется и остается равным нулю.

При нулевых сигналах на управляющих входах коммутаторов 51, 52 сигналы с их входов поступают на их первые выходы.

Измерительный преобразователь 1 скорости формирует на выходе напряжение  , а на выходе интегратора 2 формируется напряжение, пропорциональное перемещению Х. На выходе первого 3 и второго 4 знакочувствительных элементов формируются сигналы в течение положительных полупериодов входных сигналов

, а на выходе интегратора 2 формируется напряжение, пропорциональное перемещению Х. На выходе первого 3 и второго 4 знакочувствительных элементов формируются сигналы в течение положительных полупериодов входных сигналов  , Х соответственно.

, Х соответственно.

На выходе элемента И 5 формируется сигнал при совпадении положительных значений Х и  в каждом полупериоде.

в каждом полупериоде.

В момент t1 формирования сигнал на выходе элемента И 5 первый триггер 14 устанавливается в единичное состояние импульсом с выхода первого диода 8.

При этом первый ключ 17 замыкается и на вход первого счетчика 19 поступают импульсы с выхода генератора 16 импульсов.

В тот же момент t1 времени второй триггер 15 устанавливается в единичное состояние импульсом с выхода второго дифференцирующего элемента 7. При этом замыкается второй ключ 18 и импульсы с выхода генератора 16 импульсов поступают на вход второго счетчика 20.

Первый триггер 14 устанавливается в нулевое состояние импульсом с выхода первого дифференцирующего элемента 6, соответствующим заднему фронту импульса с элемента И 5 (момент t2).

Начиная с момента t2, содержимое первого счетчика 19 остается без изменения.

В момент t3 соответствующий заднему фронту импульса с второго знакочувствительного элемента 4 второй триггер 15 устанавливается в нулевое состояние, при этом второй ключ 18 размыкается и содержимое второго счетчика 20 больше не изменяется. Кроме того, импульс, формируемый в момент t3 времени, поступает на входы первого 21 и второго 22 регистров, в результате чего содержимое первого счетчика 19 переносится в первый регистр 21, а содержимое второго счетчика 20 - во второй регистр 22. Тот же импульс, задержанный элементом 25 задержки, поступает на установочные входы первого 19 и второго 20 счетчиков, устанавливая их в нулевое состояние.

Сигнал Δ2 с выхода второго ЦАП 24 поступает на вход "Делитель" блока 26 деления, на вход "Делимое" которого поступает сигнал, равный π. Сигнал, равный π/Δ2, поступает на первый вход первого блока 27 умножения, на второй вход которого поступает сигнал Δ1 с выхода первого ЦАП 23. Сигнал с выхода первого блока 27 умножения, равный  , поступает на входы первого 30 и второго 31 преобразователей, на выходе первого из которых формируется сигнал, равный ctg

, поступает на входы первого 30 и второго 31 преобразователей, на выходе первого из которых формируется сигнал, равный ctg , а на выходе второго - сигнал, равный sin-1

, а на выходе второго - сигнал, равный sin-1 .

.

Сигнал с выхода первого 30 и второго 31 преобразователей поступают на первые входы второго 28 и третьего 29 блоков умножения соответственно, на вторые входы которых поступает сигнал с выхода блока 26 деления.

На выходе второго блока 28 умножения формируется сигнал, равный h, на выходе третьего блока 29 умножения формируется сигнал, равный ωо.

Сигналы, соответствующие значениям h, ωo, поступают на выходы 32, 33 регистратора 54 соответственно.

Режим Б. На первом входе элемента И 43 нулевой сигнал, поэтому независимо от сигнала на втором входе элемента И 43 ключ 34 разомкнут. Исходное состояние триггера 49 - нулевое, поэтому ключ 35 разомкнут, ключ 36 замкнут, ключ 37 замкнут, так как на выходе элемента НЕ 44, на управляющих входах ключей 39, 40 единичные сигналы, поэтому ключи замкнуты. На выходе дешифраторов 47, 48 нулевые сигналы.

На управляющих входах коммутаторов 51, 52 единичные сигналы, поэтому сигналы с их входов поступают на их вторые входы, а значит, и на входы 80, 79 вычислительного блока 53.

В момент t4 (см. фиг.4) импульс с выхода второго дифференцирующего элемента 7 поступает через диод 9 на единичный вход триггера 15, устанавливая его в единицу. При этом замыкается ключ 18 и на вход счетчика 20 поступают импульсы с выхода генератора 16 импульсов. Одновременно импульс с выхода диода 9 через элемент ИЛИ 42 поступает на счетный вход счетчика 45, увеличивая его содержимое на единицу младшего разряда.

В момент t3 импульс, соответствующий заднему фронту импульса с выхода второго знакочувствительного элемента 4, устанавливает второй триггер 15 в нуль, при этом второй ключ 18 размыкается. Тот же импульс через элемент ИЛИ 42 поступает на счетный вход счетчика 45 импульсов, который устанавливается в состояние "10" (счетчик двухразрядный - единица в старшем разряде).

На выходе дешифратора 47 формируется сигнал, ключ 37 размыкается вследствие отсутствия сигнала на выходе элемента НЕ 44.

Импульс с выхода инвертора 13 поступает на единичный вход триггера 49, устанавливая его в единицу. При этом ключ 36 размыкается, а ключ 35 замыкается. Импульс, формируемый в момент t3, поступает на входы первого и второго 21 и 22 регистров, в результате чего содержимое счетчика 19 переносится в регистр 21, а содержимое счетчика 20 - в регистр 22. Тот же импульс, задержанный элементом 25 задержки, поступает на установочные входы счетчиков 19, 20, устанавливая счетчик 20 в нуль и подтверждая нулевое состояние счетчика 19. Так происходит формирование временного интервала Δ2 при калиброванном входном сигнале величиной β1. Через промежуток времени, определяемый временем срабатывания таймера 50 и достаточный для установления системы в состояние устойчивого равновесия, на его выходе формируется сигнал, по которому счетчик 45 устанавливается в нуль, а содержимое счетчика 46 увеличивается на единицу младшего разряда.

При установлении счетчика 45 в нуль ключ 37 снова замыкается. Ударный механизм в момент времени t4 коротким импульсом калиброванной амплитуды β2 возбуждает снова свободные колебания в нелинейной механической колебательной системе.

В момент времени t4 второй триггер 15 снова устанавливается в единицу импульсом с выхода диода 9.

При этом замыкается ключ 17 и импульсы с выхода генератора 16 поступают на вход счетчика 19.

В момент времени t5 формируется импульс, поступающий на нулевой вход триггера 15, устанавливая его в нуль. При этом ключ 17 размыкается. Начиная с момента времени t5, содержимое счетчика 19 остается без изменения и равно Δ3.

Тот же импульс поступает на входы регистров 21, 22, в результате чего содержимое счетчика 19 переносится в регистр 21, находящийся в нуле, а содержимое счетчика 20, равное нулю, переносится в регистр 22. Тот же импульс, задержанный элементом 25 задержки, поступает на установочные входы счетчиков 19, 20, устанавливая их в нуль. Импульс, поступающий в момент t5 на нулевой вход триггера 15 поступает, на вход счетчика 45, устанавливая его в состояние "10". При этом ключ 37 снова размыкается, а на выходе таймера 50 через промежуток времени, необходимый для установления системы в положение устойчивого равновесия, формируется импульс, устанавливающий счетчик 45 в нуль.

Импульс с выхода таймера 50 поступает также на вход счетчика 46, устанавливая его в состояние "10" (единица в старшем разряде двухразрядного счетчика 46 импульсов). При этом на выходе дешифратора 48 формируется сигнал, поступающий на вход 81 вычислительного блока 53.

Вычислительный блок 53 работает следующим образом.

Сигнал, поступающий на вход 76, проходит на первый выход коммутатора 55 и далее на вход пикового детектора 56, предварительно установленный в нуль сигналом по входу "Сброс" 78.

Блок 56 фиксирует амплитудное значение а1.

При установлении триггера 49 в единицу сигнал, поступающий на вход коммутатора 55, проходит на вход пикового детектора 57, который фиксирует амплитудное значение а2.

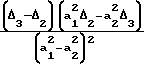

После фиксации величин Δ2, а1,Δ3, а2 срабатывает дешифратор 48, благодаря чему замыкаются ключи 65-68. На выходе сумматора 69 формируется сигнал /a12-a22/, а на выходе сумматора 70 - сигнал /a12Δ2--a22 Δ3/. На выходе блока 73 деления формируется сигнал  , а на выходе 83 блока 63 умножения - сигнал ω0=

, а на выходе 83 блока 63 умножения - сигнал ω0=

, поступающий на третий вход блока 54 регистрации.

, поступающий на третий вход блока 54 регистрации.

На выходе сумматора 71 формируется сигнал / Δ3- Δ2/, на выходе блока 64 умножения - сигнал  (Δ3-Δ2), а на выходе блока 74 деления - сигнал

(Δ3-Δ2), а на выходе блока 74 деления - сигнал  (Δ3-Δ2)

(Δ3-Δ2) , который после прохождения через усилитель 75 с коэффициентом усиления 8/3 на основании соотношения (16) равен параметру α2.

, который после прохождения через усилитель 75 с коэффициентом усиления 8/3 на основании соотношения (16) равен параметру α2.

Изобретение относится к испытательной технике. Цель изобретения - расширение области использования за счет определения рассеяния энергии и собственной частоты также и нелинейной колебательной системы, достигается благодаря тому, что возбуждают затухающие колебания исследуемой системы, измеряют первый интервал времени между соседними моментами положения равновесия и амплитудное значение при внешнем возбуждении импульсом калибровки амплитуды одного значения, измеряют второй интервал времени между соседними моментами положения равновесия и амплитудное значение при внешнем возбуждении импульсом калиброванной амплитуды другого значения и по предложенным соотношениям определяют параметры, характеризующие нелинейную механическую колебательную систему. В устройство введены ключи, элементы ИЛИ, элемент И, элемент НЕ, счетчики импульсов, дешифраторы, триггер, таймер, коммутаторы вычислительного блока и регистратор. 2 с. и 1 з.п. ф-лы, 4 ил.

h =  ctg

ctg ;

;

ωол=

,

,

отличающийся тем, что, с целью расширения области использования за счет определения рассеяния энергии и собственной частоты также и нелинейной механической колебательной системы, измеряют третий интервал Δ3 времени между третьим t4 и четвертым t5 моментами прохождения положения равновесия, а также амплитудные значения a1 и a2 во втором и третьем интервалах времени и параметр α2 рассеяния энергии и собственную частоту ωoн колебаний нелинейной механической системы определяют из условий

α2=

·

·  ;

;

ωон=

.

.

| Способ определения рассеяния энергии и собственной частоты механической колебательной системы и устройство для его осуществления | 1988 |

|

SU1583778A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1994-12-30—Публикация

1991-06-17—Подача