Изобретение относится к области моделирования функциональных свойств нервной системы, а именно для построения нейронных сетей, и может быть использовано в качестве элемента нейроподобных сетей для моделирования сложных биологических процессов, в частности при изучении адаптивных процессов памяти в нейрофизиологических экспериментах.

Известно устройство интеллектуальный решатель СФИНКС, содержащее в блоке памяти, соединенном с рецепторными и эффекторными терминалами, главную базу данных (ГБД) и модельную базу данных (МБД). МБД содержит "знания" системы о предметной области в виде совокупности объектов как терминальных, так и являющихся описаниями объектов МБД. МБД заполняется программистом, формализующим объектные сведения, являющимся, следовательно, неотъемлемым звеном системы в процессе образования адаптивных связей.

Недостаток функционирующей системы обусловлен ее ограниченным приложением и определяется обязательным участием программиста - системного аналитика, осуществляющего свою деятельность при помощи терминала системного программиста, что обусловливает недостаточное быстродействие для работы в реальном масштабе времени, ограниченные функциональные возможности создаваемой базы данных из-за ограничения поступающих данных об объектной области при вводе через терминал системного программиста и недостаточную достоверность образующихся адаптивных связей вследствие трудности процесса формализации знаний.

Цель изобретения - расширение функциональных возможностей моделирования путем повышения достоверности образования адаптивных связей в реальном масштабе времени воздействия факторов среды и обеспечения самоорганизации образования адаптивных связей.

Поставленная цель достигается тем, что в устройство для моделирования адаптивных связей, содержащее блок памяти с рецепторными и эффекторными терминалами, согласно изобретению, введен блок активации памяти, состоящий из узла детекторов нового, первого и второго модуляторов, узла детекторов положительной значимости и узла детекторов отрицательной значимости, к которым подключены терминал рецепторов значимости, а блок памяти выполнен в виде N/N 1, последовательно соединенных модулей памяти. При этом выходы модулей памяти и подключенный к входам узла детекторов положительной и отрицательной значимости выход рецепторного терминала соединены с входами узла детекторов нового, первый вход каждого из модулей - с выходом первого модулятора, второй - с выходом второго модулятора, третий - с выходом узла детекторов нового и с первыми входами первого и второго модуляторов, четвертый - с выходом узла детекторов положительной значимости и с вторым входом первого модулятора, пятый - с выходом узла детекторов отрицательной значимости и с вторым входом второго модулятора. Кроме того, модули памяти, узлы детекторов нового и значимости и блоки модуляторов системы выполнены из однотипных элементов-нейристоров, состоящих из порогового усилителя, связанного входами с выходами двух синаптических коммутаторов. При этом пороговый усилитель выполнен, например, по схеме последовательно соединенных инвертирующих масштабных усилителей, имеющих суммирующие входы, а каждый из синаптических коммутаторов состоит из N/N > 1 ячеек, имеющих N сигнальных входов по числу первых входов ячеек, первый вход управления (УПР1), объединяющий вторые входы ячеек, второй вход управления (УПР2), объединяющий третьи входы ячеек, и выход, объединяющий выходы ячеек, причем ячейка синаптического коммутатора выполнена, например, в виде электролитического элемента, соединенного первым выводом с первым входом ячейки, вторым выводом через последовательно соединенные развязывающий резистор и первый управляемый ключ с вторым и третьим входами ячейки, а через второй ключ - с выходом ячейки.

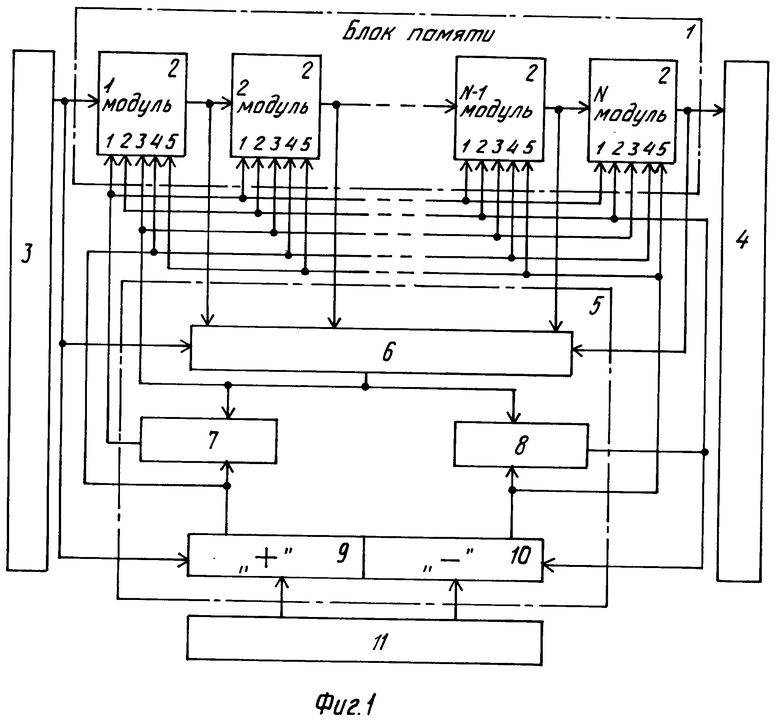

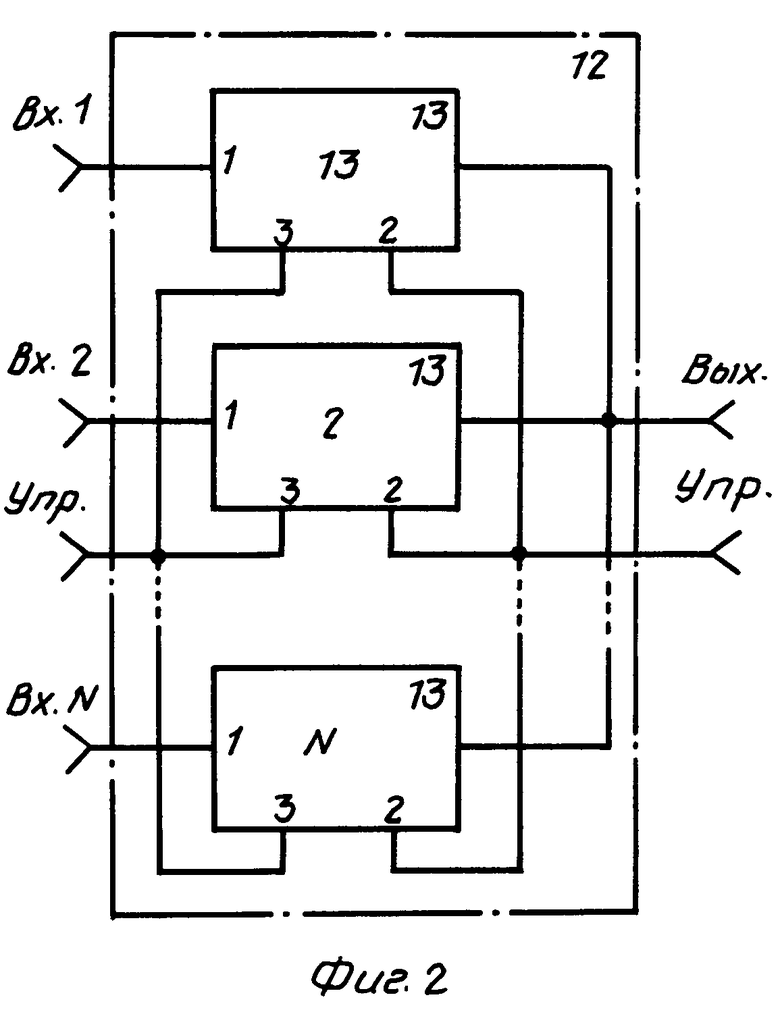

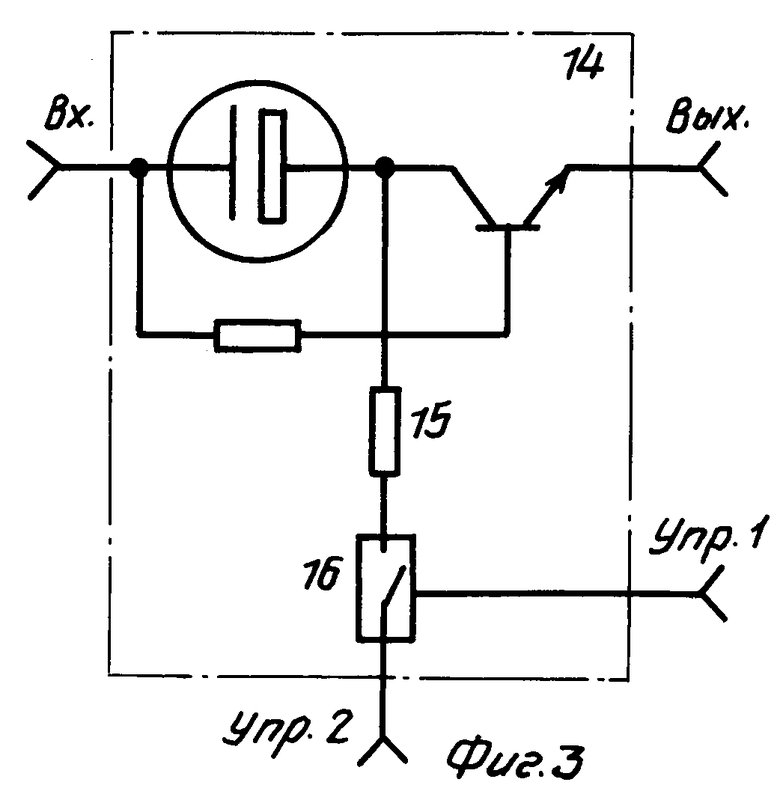

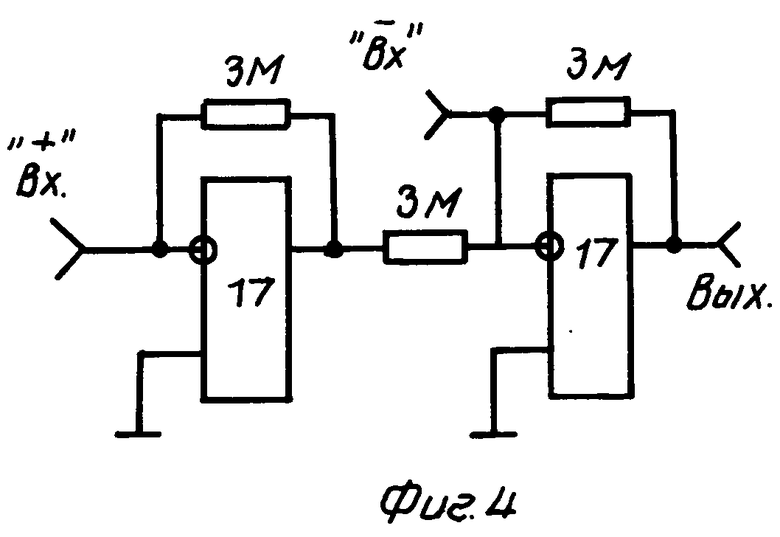

На фиг. 1 приведена возможная блок-схема устройства; на фиг.2 - блок-схема синаптического коммутатора; на фиг.3 - возможная блок-схема ячейки синаптического коммутатора; на фиг. 4 - возможная блок-схема порогового усилителя.

Устройство для моделирования адаптивных связей содержит блок памяти 1, состоящий из N/N > 1 последовательно включенных модулей памяти 2, вход первого из которых соединен с выходом рецепторного терминала 3, а выход последнего - с входом эффекторного терминала 4. Посредством магистралей связи блок памяти 1 подключен к блоку активации памяти 5, состоящему из узла детекторов нового 6, первого 7 и второго 8 модуляторов и узлов детекторов значимости, включающих узел детекторов положительной значимости 9, отмеченный значком "+" и узел детекторов отрицательной значимости 10, отмеченный значком "-". К последним названным узлам подключены терминалы рецепторов значимости 11.

Каждый из модулей 2 блока памяти 1 соединен с блоком активации памяти 5 следующими связями: выходом - с одним из входов узла детекторов нового 6, первым входом - с выходом первого модулятора 7, вторым входом - с выходом второго модулятора 8, третьим входом - с выходом узла детекторов нового 6 и с первыми входами первого 7 и второго 8 модуляторов, четвертым входом - с выходом узла детекторов положительной значимости 9 и с вторым входом первого модулятора 7, пятым входом - с выходом узла детекторов отрицательной значимости 10 и с вторым входом второго модулятора 8. Выход рецепторного терминала 3 подключен также к одному из входов (свободному) узла детекторов нового 6 и к входам (свободным) узлов детекторов положительной и отрицательной 10 значимости.

Основной конструктивный элемент, из которого выполнены все блоки системы - нейристор, состоящий из порогового усилителя, связанного входами с выходами двух синаптических коммутаторов, состоящих, в свою очередь, из N (N > 1) однотипных ячеек. Синаптический коммутатор 12 (фиг.2) имеет N сигнальных входов по числу содержащихся в нем ячеек 13, выход, объединяющий выходы всех ячеек, и два входа управления: УПР1- объединяющий вторые входы ячеек и УПР2- объединяющий третьи входы ячеек. Ячейка синаптического коммутатора 13 (фиг. 3) может быть выполнена, например, в виде электролитического элемента 14, первым выводом соединенного с входом ячейки, а вторым выводом - через развязывающий резистор 15 и первый управляемый ключ 16 - с входами ячейки УПР1 и УПР2 и через второй ключ - с выходом ячейки.

В качестве порогового усилителя может использоваться, например, устройство, приведенное на фиг.4. Оно выполнено на базе интегральных усилителей 17 (например, на микросхеме КР14ОУД1208), включенных по схеме последовательно соединенных инвертирующих масштабных усилителей, имеет два входа: "возбуждающий" ("+" вх) и "тормозной/"-" вх/ с приоритетом у тормозного (вследствие конечного значения питающих напряжений). К каждому входу может быть подведено неограниченное количество входных цепей через проводимости (например, резисторы), определяющие коэффициент передачи каждой данной сигнальной цепи. Конструктивно предполагается подключение к каждому из входов по одному синаптическому коммутатору, имеющему около 1000 входных электродов для адаптивного образования возбуждающих и тормозных связей. Установка связей в том или ином коммутаторе определяется созданием названных условий образования связей при наличии "неспецифического подкрепления" - сигнала от соответствующего модулятора 7(8). Порог усилителей определяется наличием установившихся тормозных связей и уровнями сигналов, приложенных к ним.

Синаптический коммутатор 12 может быть выполнен в виде любого устройства, реализующего описанные условия образования связей, но реально должен быть выполнен в виде элемента, функционирующего за счет свойств своей молекулярной (или другого уровня) структуры, так как на уровне классической схемотехнической реализации или на уровне программных средств построение схемы на 1000 входов, выполняющей условия образования связей, реально не представляется возможным. В одном из вариантов реализации, предложенном на фиг. 3, единичная проводимость в ячейке коммутатора образована электролитическим элементом 14, подключенным между выходом предшествующего (рецепторного) порогового усилителя и входом порогового усилителя данного коммутатора. Если ячейка уже обладает проводимостью (имеет ионные носители в канале) то связь функционирует по схеме масштабного усилителя. Если в канале нет носителей, то ячейка заперта. Чтобы вызвать появление носителей в канале, необходимо провести гальванический процесс в прямом направлении. Условия для этого возникают (фиг.3), когда на входе ячейки присутствует достаточный уровень входного сигнала, на вход управления УПР1 поступает высокий уровень (с выхода порогового усилителя данного нейристора, возбужденного по каким-либо своим цепям), который открывает ключ 16 и присутствует сигнал УПР2 "неспецифического подкрепления" достаточно низкого уровня (с выхода модулятора). При этом, в электролитическом элементе начинают накапливаться ионные носители, концентрация которых затем и определит проводимость ячейки коммутатора. Транзистор в данной схеме выполняет роль автоматического ключа, препятствующего спонтанному гальваническому процессу при отсутствии сигнала УПР2 (так как вход порогового усилителя всегда имеет потенциал виртуального нуля), при этом предполагается, что проводимость резистора в цепи базы транзистора сама по себе определяет пренебрежимо малый коэффициент передачи ячейки коммутатора.

Обладающий высокой чувствительностью нейристор с синаптическими коммутаторами без установившихся связей может спонтанно "возбуждаться" от наводок. Более того, для приближения протекающих процессов к реально происходящим уровень этих наводок должен задаваться достаточным для обеспечения такого спонтанного генерирования (например, специальными излучателями, расположенными вблизи модулей 2 памяти, на фиг.1 не показанными). Выходные сигналы спонтанно генерирующего нейристора используются в качестве управляющих (УПР1) для выполнения условий образования самых первых адаптивных связей.

Блок памяти системы сообщен с объектной средой посредством рецепторного терминала 3 (специализированных датчиков) и эффекторного терминала 4 (специализированных исполнительных устройств).

В каждом из N модулей 2 памяти блока памяти 1 должно находиться достаточное для выполнения планируемой адаптивной функции количество нейристоров, расположенных слоями.

Узел детекторов нового 6 устройства активации памяти представляет собой наборы рецепторов, образующих за формирования адаптивных связей "маски восприятия" по известному механизму (Соколов Е.Н. Нейронные механизмы памяти и обучения. М.: Наука, 1981). Если в последующем восприятии область установившихся связей не перекрывается "маской", то на выходе детекторов нового появляется сигнал, пропорциональный новизне.

Узлы детекторов значимости 9, 10 представляют собой наборы рецепторов, сигнализирующих о благоприятных и неблагоприятных воздействиях внешней и внутренней среды, и являются селективными датчиками воздействия.

Модуляторы 7, 8 представляют собой наборы нейристоров, которые за счет определенной организации связей обеспечивают функцию перемножения уровней сигналов детекторов значимости 9, 10 и детекторов нового 6 (в соответствии с известной функцией модулятора сигналов одной полярности).

Устройство реализует функцию образования адаптивных связей следующим образом.

Функциональное назначение узла детектора нового 6, модуляторов 7, 8 и узла детекторов значимости 9, 10, предопределяемое спецификой связей, задается изначально ("наследственно"), что способствует ускорению общего процесса развития основных адаптивных функций в условиях определенной объектной среды и делает более определенным планируемый результат, хотя при этом затруднит образование адаптивных связей в случае достаточно резкого изменения условий объектной среды.

В рецепторном терминале 3 и модулях 2 памяти и блока 1 памяти связи изначально не установлены. В соответствии с приведенными условиями образования связей сначала будут образовываться связи между рецепторным терминалом 3, где произошло возбуждение рецепторов объектной средой, узлами детекторов нового 6, блоками детекторов положительной 9 и отрицательной 10 значимости, а также со всеми нейристорами тех модулей 2 памяти, где из-за отсутствия связей и за счет достаточного уровня наведенных помех возникают спонтанные генерации. При этом для оптимизации адаптивных функций в блоке 1 памяти необходимо обеспечить строго поочередное образование адаптивных связей от слоя к слою (например, путем поочередного включения питания слоев памяти): сначала в процесс вовлекаются рецепторный терминал 3 и первый модуль памяти, а также эффекторный терминал 4 и N-й модуль памяти, затем добавляются 2 модуль памяти и N-1 модуль памяти и т.д. При этом время образования связей в каждом последующем слое должно значительно превышать время образования адаптивных связей в предыдущем слое.

Связи, образующиеся в результате описанного процесса, ставят в зависимость реакцию системы (ее эффекторную реакцию) от рецепции объектной среды, а также от результатов оценки ее новизны и значимости, т.е. образующиеся связи являются адаптивными.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения контура изображения | 1990 |

|

SU1755306A1 |

| Ячейка ассоциативной классифицирующей среды | 1987 |

|

SU1522191A1 |

| СПОСОБ АДАПТАЦИИ РЕЖИМОВ ПЕРЕДАЧИ ИНФОРМАЦИИ ПО СПУТНИКОВЫМ КАНАЛАМ СВЯЗИ В УСЛОВИЯХ ВОЗДЕЙСТВИЯ АТМОСФЕРНЫХ ВОЗМУЩЕНИЙ И УСТРОЙСТВО ЕГО РЕАЛИЗУЮЩЕЕ | 2015 |

|

RU2611606C1 |

| Система связи | 1989 |

|

SU1815802A1 |

| Устройство для фильтрации изображения | 1989 |

|

SU1661806A1 |

| Адаптивный коммутатор телеизмерительной системы | 1990 |

|

SU1785020A1 |

| СИСТЕМА СТИМУЛЯЦИИ ФУНКЦИОНИРОВАНИЯ ОРГАНОВ | 2009 |

|

RU2401137C1 |

| АДАПТИВНЫЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ НЕПРЕРЫВНЫХ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2007 |

|

RU2349923C1 |

| Устройство для моделирования условных рефлексов | 1975 |

|

SU612259A1 |

| СТАНЦИЯ СПУТНИКОВОЙ СВЯЗИ КОНТЕЙНЕРНОГО ИСПОЛНЕНИЯ | 2011 |

|

RU2455769C1 |

Использование: изобретение относится к области моделирования функциональных свойств нервной системы и может быть использовано в нейрофизиологических экспериментах и их планировании при изучении адаптивных процессов памяти. Сущность: в устройство, содержащее блок памяти с рецепторными и эффекторными терминалами, введен блок активации памяти, состоящий из узлов детекторов нового, детекторов значимости с терминалами рецепторов значимости и модуляторов, а блок памяти выполнен в виде последовательно соединенных модулей памяти, причем в качестве основного конструктивного элемента названных блоков модулей применен нейристор, состоящий из порогового усилителя и двух синаптических коммутаторов. 4 з.п. ф-лы, 4 ил.

| Брябрин В.М | |||

| Диалоговая информационно-логическая система | |||

| Труды Международной конференции по искуственному интеллекту | |||

| Ленинград-Репино. |

Авторы

Даты

1995-01-20—Публикация

1991-01-03—Подача