Изобретение относится к радиотехнике и предназначено для использования в радиосвязи для передачи аналоговых сообщений,

Цель изобретения - повышение помехоустойчивости передачи сообщений в пороговой области.,

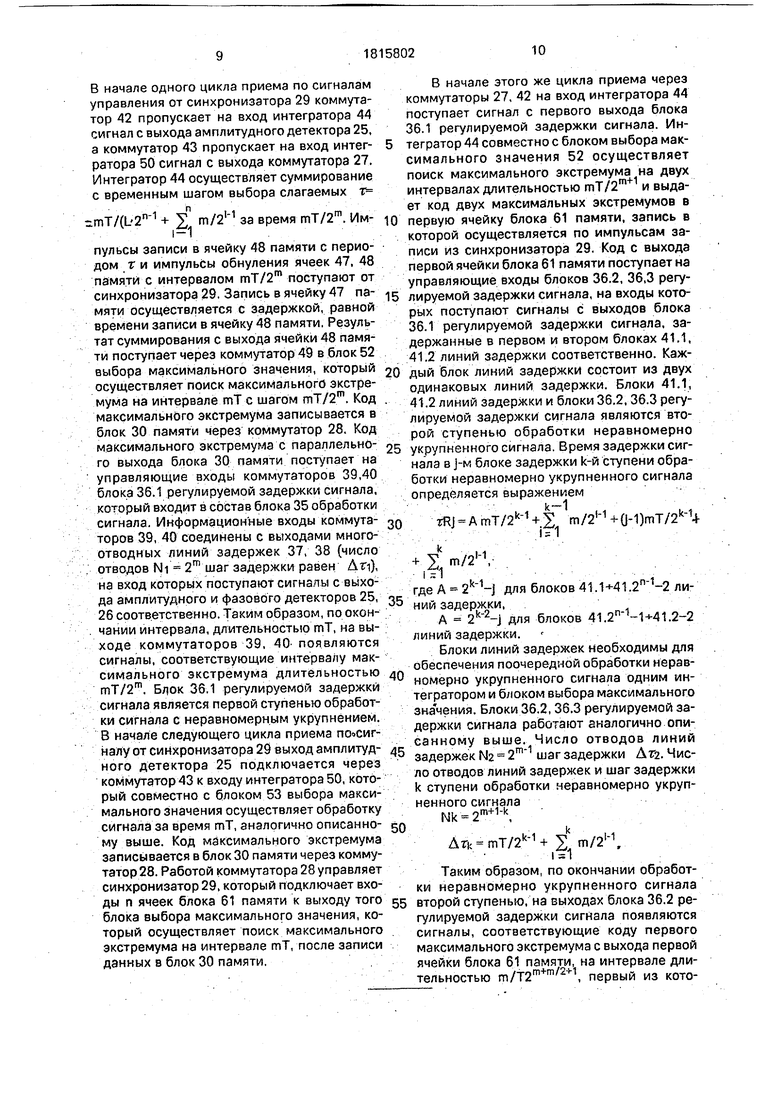

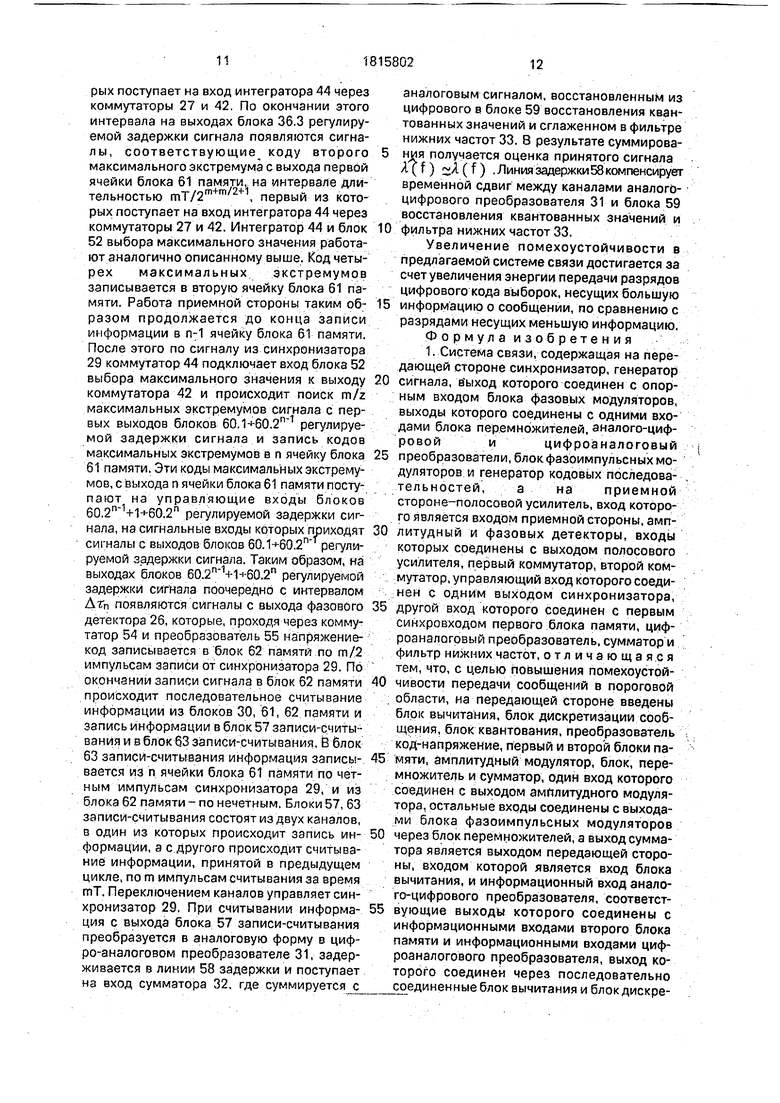

На фиг. 1,2 представлены функциональные схемы передающей и приемной сторон системы связи.

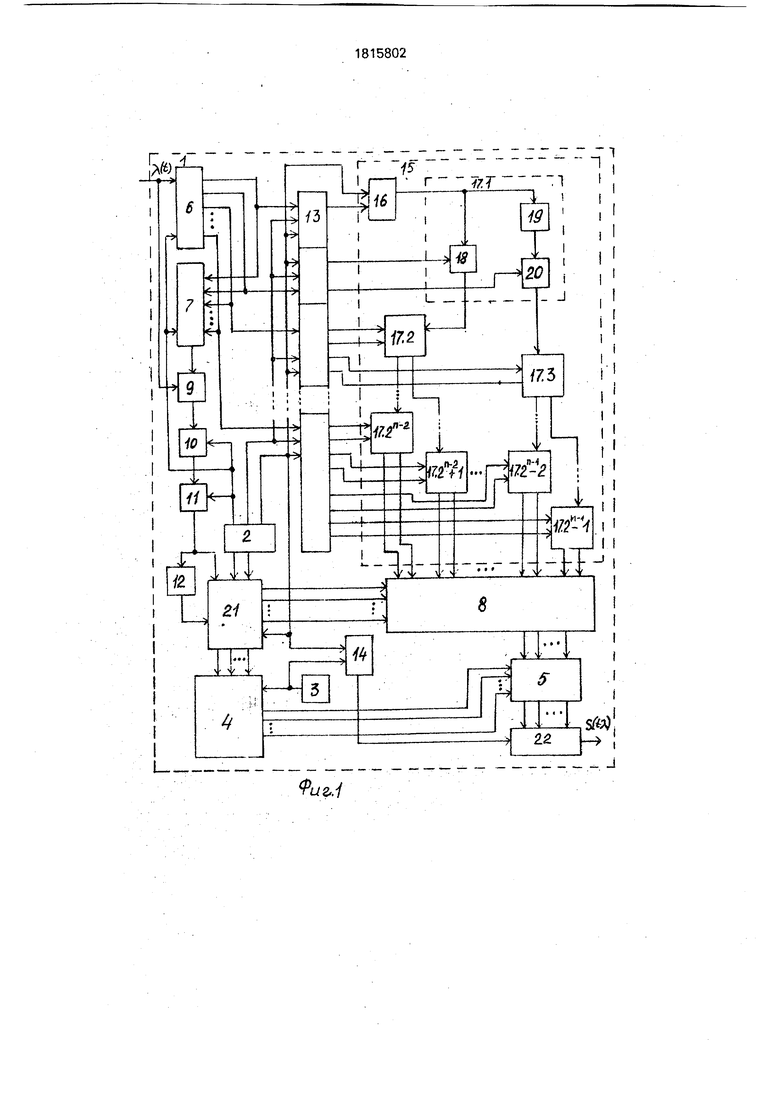

Система связи с неравномерным укрупнением сигнала содержит на передающей стороне 1 (фиг. 1) синхронизатор 2, генератор сигнала 3, блок 4 фазовых модуляторов, блок 5 перемножителей, аналого-цифровой преобразователь 6, цифроаналоговый преобразователь 7, блок 8 фазоимпульсных модуляторов, блок 9 вычитания, блок 1.0 дискретизации, блок 11 квантования, преобразователь 12 код-напряжение, блок 13 памяти, амплитудный модулятор 14, генератор 15 кодовых последовательностей, фазо- импульсный модулятор 16, блоки 17,1-17.

регулируемой задержки импульса, фазоимпульсный модулятор 18, линию 19 задержки, фазоимпульсный модулятор 20, блдк 21 памяти и сумматор 22, один вход которого соединен с выходом амплитудного модулятора 14, один вход которого соединен с выходом генератора си гнала 3 и одним входом блока 4 фазовых модуляторов, выходы которого соединены с одними входами блока 5 перемножителей, другие входы которого соединены с выходами генератора 15 кодовых последовательностей через блок 8 фазоимпульсных модуляторов, а выходы блока 5 перемножителей подключены к остальным входам сумматора 22, выход которого является выходом приемной стороны 1, входом которой является вход блока 9 вычитания, соединенный с информационным входом аналого-цифрового преобразователя 6, соответствующие выходы которого соединены с информационными входами п ячеек блока 13 памяти и информационными

00

ел

00

о

ю

входами цифйоаиалогового преобразователя 7, выход которого соединен через блок 9 вычитания и блок 10 дискретизации с входом блока 11 квантования, выход которого соединен с одним информационным входом блока 21 памяти, одни выходы которого соединены с входами блока 8 фазоимпульсных модуляторов, и через преобразователь 12 код - напряжение с другим информационным входом блока 21 памяти, другие выходы которого соединены с сигнальными входами блока 4 фазовых модуляторов, а первые синхронизированные входы п ячеек блока памяти соединены между собой с первым синхронизационным входом блока 21 памяти, с опорным входом генератора 15 кодовых последовательностей, вторым входом амплитудного модулятора 14 и одним выходом синхронизатора 2, соответствующие выходы которого подключены к тактовым входам аналого-цифрового и цифроаналого- вого преобразователей 6,7, блока 10 дисре- тизации и блока 11 квантования, к вторым синхронизационным входам первой: п блока 13 памяти, ячеек к двум синхронизационным входам блока 21 памяти, выходы блока 13 памяти соединены с входами генератора 15 кодовых последовательностей, а в приемной части 23 (фиг. 2) - полосовой усилитель 24, амплитудный детектор 25, фазовый детектор 26, коммутаторы 27, 28, синхронизатор 29, блок 30 памяти, цифроаналоговый преобразователь 31, сумматор 32, фильтр 33 нижних частот, синхронизируемый генератор 34, блок 35 обработки сигнала, блоки 36.1-К36.2п-1 регулируемой задержки сигнала, линии 37, 38 задержек, коммутаторы 39, 40, блоки 41.1+41.2п-2 линий задержек, коммутаторы 42, 43, интегратор 44, сумматор 45, линию 46 задержки, ячейки 47, 48 памяти, коммутатор 49, интегратор 50, блок 51 регулируемой задержки, блоки 52,53 выбора максимального значения, коммутатор 54, преобразователь 55 напряжение-код, коммутатор 56, блок 57 записи-считывания, линию 58 задержки, блок 59 восстановления квантовых значений, блоки 6,. 1+60.2 регулируемой задержки сигнала, ячейки 61 блока памяти, блок 62 памяти, блок 63 записи-считывания, выход которого соединен через блок 59 восстановления квантованных значений и фильтр 33 нижних.частот к первому входу сумматора 32, выход которого является выходом приемной стороны 23, а второй вход сумматора 32 соединен через линию 58 задержки и цифро-аналоговый преобразователь 31 с выходом блока 57 записи-считывания, соответствующие информационные входы которого соединены с последовательными выходами блока 30 памяти и первой + п-1 ячеек блока 61 памяти, а управляющий и первый тактовый входы соединены с управляющим и первым тактовым входами блока 63 записи-считывания

соответственно и выходами синхронизатора 29, вход которого подключен к выходу амплитудного детектора 25, первому сигнальному входу блока 35 обработки сигнала и первым информационным входом комму0 таторов 42, 43, а соответствующие выходы синхронизатора 29 подключены к управляющему входу коммутатора 43, второй информационный вход которого соединен с вторым информационным входом коммута5 тора 42 и выходом коммутатора 27, к управляющему входу коммутатора 42, к управляющему и первому тактовому входам интегратора 50, к управляющему и первому тактовому входам интегратора 44, к первому

0 тактовому входу блока 52 выбора максимального значения и второму тактовому входу интегратора 44, к синхронизационному и второму тактовому входам блока 52 выбора максимального значения, выход ко5 торого соединен с первым информационным входом коммутатора 28, к первому тактовому входу блока 53 выбора максимального значения и к второму тактовому входу интегратора 50, к синхронизационно0 му и второму тактовому входам блока 53 выбора максимального значения, выход которого соединен со вторым информационным входом коммутатора 28, выход которого соединен с информационными

5 входами блока 30 памяти и п ячеек блока 61 памяти, к управляющему входу коммутатора 28, к первому синхронизационному входу блока 30 памяти, к первому синхронизаци- оннному входу п ячеек блока 61 памяти, к

0 первому синхронизационному входу блока 62 памяти, к второму тактовому входу блоков 57,63 записи-считывания и вторым синхронизационным входам блока 30 памяти, п ячейкам блока 61 памяти, причем разрядные

5 выходы блока 30 памяти и первой п-2 ячейки блока 61 памяти соединены с управляющими входами блока 35 обработки сигнала, одни выходы которого подключены к одним входам коммутатора 27, другие входы кото0 рого подключены к сигнальным выходам - блока 51 регулируемой задержки, сигнальные входы которого подключены к вторым выходам блока 35 обработки сигнала, а управляющие входы блока 51 регулируемой

5 задержки соединены с разрядными выходами п-1 и п ячеек блока 61 памяти, к второму синхронизационному входу блока 62 памяти и к управляющему входу коммутатора 56, информационные входы и выход которого соединены с последовательным выходом п

чейки блока 61 памяти и блока 62 памяти и входом блока 63 записи-считывания соответственно, к управляющему входу коммуатора 54, информационные входы которого оединены с выходами блока 51 регулируе- 5 мой задержки, а выход соединен с информационным входом блока 62 памяти через преобразователь 55 напряжение-код, к управляющему входу коммутатора 27, к первому входу синхронизируемого генератора 34, 10 второй вход которого подключен к входам мплитудного и фазового детекторов 25, 26 и к выходу полосового усилителя 24, вход которого является входом приемной стороны 23, а выход синхронизируемого гёнера- 15 ора 34 соединен с вторым входом фазового етектора 26, выход которого соединен со вторым сигнальным входом блока 35 обработки сигнала.

Генератор 15 кодовых последовательно- 20 стей (фиг.1) содержит фазоимпульсный модулятор 16 и блоки 17.1-17. регулируемой задержки импульса, информационные входы которых, информационный вход фазоимпуль- сного модулятора 16 и опорный вход фа- 25 зоимпульсного модулятора 16 являются информационными и опорным входами генератора 15 кодовых последовательностей оответственно, выходами которого являются выходы блоков 17.2 2-«-17.2п 1-1 регу- 30 ируемой задержки импульса, причем выход фазоимпульсного модулятора 16 подключен к опорному входу блока 17.1 регулируемой задержки импульса, а каждый из вух выходов каждого блока регулируемой 35 задержки импульса, из числа блоков 17.1-Н7. регулируемой задержки импульса, соединен с опорным входом другого блока регулируемой задержки импульса.

Каждый блок 17 регулируемой задерж- 40 ки импульса (фиг. 1) содержит фазоимпуль- сный модулятор 18 и последовательно включенные линию 19 задержки и фазоим- пульсный модулятор 20, информационный вход и выход которого и информационный 45 вход и выход фазоимпульсного модулятора 19 являются информационными входами и выходами блока 11 регулируемой задержки импульса, опорным входом которого являются соединенные входы фазоимпульсного 50 модулятора 18 и лии 19 задержки.

Блок 35 обработки сигнала (фиг.2) содержит блоки 36.1+36. регулируемой задержки сигнала и блоки 41.1+41.2п-2 линий задержек, причем управляющие входы бло- 55 ков 36.1-«-36. регулируемой задержки сигнала являются управляющими входами блока 35 обработки сигнала, а первые выхоы блоков 36.1 . регулируемой задержки сигнала являются одними выходами

блока 35 обработки сигнала, другими выходами которого являются первый и второй выходы блоков 41.2п 1-1+41.2п-2 линий задержек, входы которых соединены с выходами блоков 36..2п-1 регулируемой задержки сигнала соответственно, причем первый и второй сигнальные входы блока 36.1 регулируемой задержки сигнала являются первым и вторым сигнальными входами блока 35 обработки сигнала, а первый и второй выходы каждого блока регулируемой задержки сигнала, из числа блоков SG.I-KJe 1- регулируемой задержки сигнала, соединены с первым и вторым входами двух блоков линий задержек, а первый и второй выходы каждого блока линий задержек, из числа блоков 41., линий задержек, подключены к первому и второму сигнальным входам блока регулируемой задержки сигнала.

Каждый блок 36 регулируемой задержки сигнала (фиг. 2) содержит линии 37, 38 задержек и коммутаторы 39, 40, информационные входы которых соединены с выходами линий 37, 38 задержек соответственно, а управляющие входы, соединенные вместе, и выходы коммутаторов 39, 40 являются управляющим входом и выходами блока 36 регулируемой задержки сигнала, первым и вторым сигнальными входами которого являются входы линий 37,38 задержек соответственно.

Интегратор 44,50 (фиг.2) содержит сумматор 45, линию 46 задержки, ячейки 47,48 памяти и коммутатор 49, управляющий входи выход которого являются управляющим входом и выходом интегратора 44, 50, сигнальным входом которого являются соединенные первые входы сумматора 45 и коммутатора 49, а соединенные вход линии 46 задержки, выход которой соединен с первым тактовым вхсСдом ячейки 47 памяти, и первый тактовый вход ячейки 47 памяти и соединенные вторые тактовые входы ячеек 47, 48 памяти являются первым и вторым тактовыми входами интегратора 44,50, причем выход сумматора 45 соединен со вторым входом коммутатора 49 через ячейку 48 памяти, выход которой соединен со вторым входом сумматора 45 через ячейку 47 памяти.

Блок 5.1 регулируемой задержки содержит блоки 60.1+60.2 регулируемой задержки сигнала, причем входы блоков 60.1+60. регулируемой задержки сигнала являются сигнальными входами блока 51 регулируемой задержки, одни выходы блоков 60.1+60. регулируемой задержки сигнала являются сигнальными выходами блока 51 регулируемой задержки, а другие выходы соединены с входами блоков 60.2 т+

-ь 1гС0.2 регулируемой задержки сигнала, выходы которых являются информационны- JHH выходами блока 51 регулируемой задержки, управляющими входами которого являются управляющие входы блоков 60.1+60.2 регулируемой задержки сигнала. Система связи с неравномерным укрупнением сигнала работает следующим образом. Сообщение Л(т) преобразуется в цифровую форму в аналого-цифровом пре- образователе 6с частотой джискретизации f 1 /Т (в соответствии с теоремой Котель- никова Т 1/2 тв), причем каждая выборка отображается в п двоичных разрядов, где п

- степень укрупнения, целое положитель- ное число больше единицы. Число выборок, передаваемых с помощью неравномерного укрупнения, равно m 2П. Запись п разрядов двоичного кода в блоки памяти происходит по m импульсам записи из синхронизатора 2, Параллельный код выборки поступает также на вход цифро-аналоговогопреобразователя 7. Восстановленный сигнал вычитается из сообщения A{f) в блоке 9 вычитания, в резуль- тате чего получается ошибка квантования, которая преобразуется в блоке 10 дискретизации в ступенчатой кусочно-постоянный сигнал с длительностью ступеньки равной Т; далее сигнал квантуется в блоке 11 кван- тования с L уровнями квантования (1 2+9). Двоичный код квантованного значения поступает на вход блока 21 памяти, в ячейки которого записывается код четных выборок по т/2 импульсам записи синхрониза- тора 2, и на вход преобразователя 12 код-напряжение. Значения напряжения нечетных выборок записываются в ячейки памяти блока 21 памяти по т/2 импульсам записи из синхронизатора 2. Информация из входных ячеек памяти блоков 13 и 21 памяти переписывается в выходные по сигналу Конец цикла с периодом Т из синхро- низатора 2. Выходной сигнал блока 21 памяти модулирует фазу генератора 3 несу- щего колебания в блоке 4 фазовых модуляторов, который состоит из т/2 фазовых модуляторов. Выходные сигналы блока 13 памяти поступают на информационные входы генератора 15 кодовых последователь- ностей. Сигнал Конец цикла поступает на опорный вход фазоимпульсного модулятора 16, который формирует задержанный импульс (с дискретой задержки Дп mT/2m) по отношению к сигналу Конец цикла. Be- личина задержки определяется кодом с выхода блока 13 памяти. Фазоимпульсный модулятор 16 является первой ступенью неравномерного укрупнения. Второй ступенью неравномерного укрупнения является блок 17.1 регулируемой задержки импульса, состоящий из двух фазоимпульсных модуляторов 18 и 20, причем на фазоим- пульсный модулятор 20 входной импульс приходит с задержкой tz mT/2m+1. Дискрета задержки импульса во второй ступени неравномерного укрупнения Ата mT/2m+ т/ . Величина задержек фазоимпульсных модуляторов 18, 20 определяется кодом первых т/2 разрядов и кодом вторых т/2 разрядов блока 13 памяти соответственно. Третья ступень неравномерного укрупнения содержит блоки 17.2, 17.3 регулируемой задержки импульса, причем t3 тТ/2т (-П1/2+2 и Дгз mT/2m+m/2+rn/.....n

ступень неравномерного укрупнения содержит блоки 17.. регулируемой задержки импульса,tn mT/2n 1+ ,Дтп

| --

mT/2n 1+ 2Пщ/2и.. I-1

Выходные сигналы генератора 15 кодовых последовательностей поступают на опорные входы блока 8 фазоимпульсных модуляторов, который состоит из т/2 фазоимпульсныхмодуляторов, на информационные входы которого поступают т/2 выходных сигнала блока 21 памяти. Выходные сигналы блока 8 фазоимпульсных модуляторов перемножаются в блоке 5 перемножителей, который состоит из т/2 пере- множителей, с сигналами с выхода блока 4 фазовых модуляторов. Выходные сигналы блока 5 перемножителей поступают на сумматор 22, который формирует из прямоугольных радиоимпульсов колоколообразные и передает последние в канал связи. На сумматор 22 поступает также пилот-сигнал-напряжение генератора 3 несущей частоты, промодулированное сигналом Конец цикла в амплитудном модуляторе 14, причем длительность сигнала Конец цикла не менее, чем в 2+3 раза больше длительности импульсов с выхода блока 5 перемножителей.

На приемной стороне 23 сигнал фильтруется и усиливается в пЪлосовом усилителе 24, детектируется в амплитудном и фазовом детекторах 25,26, причем опорной фазой для фазового детектора 26 является фаза с выхода синхронизируемого генератора 34, который подстраивается по сигналу от полосового усилителя 24 во время передачи пилот-сигнала. Эти моменты времени определяет синхронизатор 29, который осуществляет подстройку циклов по сигналу с выхода амплитудного детектора 25.

начале одного цикла приема по сигналам правления от синхронизатора 29 коммутаор 42 пропускает на вход интегратора 44 игнал с выхода амплитудного детектора 25, коммутатор 43 пропускает на вход интег- 5 ратора 50 сигнал с выхода коммутатора 27. Интегратор 44 осуществляет суммирование временным шагом выбора слагаемых т

mT/( + 2 за время mT/2m. Им- 10

пульсы записи в ячейку 48 памяти с периодом г и импульсы обнуления ячеек 47, 48 памяти с интервалом mT/2m поступают от синхронизатора 29. Запись в ячейку 47 па- jg мяти осуществляется с задержкой, равной времени записи в ячейку 48 памяти, Резульат суммирования с выхода ячейки 48 памяи поступает через коммутатор 49 в блок 52 выбора максимального значения, который 2Q осуществляет поиск максимального экстремума на интервале тТ с шагом m T/2 n. Код максимального экстремума записывается в блок 30 памяти через коммутатор 28. Код максимального экстремума с параллельно- 25 го выхода блока 30 памяти поступает на управляющие входы коммутаторов 39,40 блока 36.1 регулируемой задержки сигнала, который входит в состав блока 35 обработки сигнала. Информационные входы коммута- OQ торов 39, 40 соединены с выходами многоотводных линий задержек 37, 38 (число отводов NI 2m шаг задержки равен Ari), на вход которых поступают сигналы с выхода амплитудного и фазового детекторов 25, gg 26 соответственно. Таким образом, по окон- . чании интервала, длительностью тТ, на выоде коммутаторов 39, 40 появляются сигналы, соответствующие интервалу максимального экстремума длительностью 40 mT/2m. Блок 36.1 регулируемой задержки сигнала является первой ступенью обработки сигнала с неравномерным укрупнением. В начале следующего цикла приема налу от синхронизатора 29 выход амплитуд- 45 ного детектора 25 подключается через коммутатор 43 к входу интегратора 50, который совместно с блоком 53 выбора максимального значения осуществляет обработку сигнала за время тТ, аналогично описание- gn му выше. Код максимального экстремума записывается в блок 30 памяти через коммутатор 28. Работой коммутатора 28 управляет синхронизатор 29, который подключает входы п ячеек блока 61 памяти к выходу того gg блока выбора максимального значения, который осуществляет поиск максимального экстремума на интервале тТ, после записи данных в блок 30 памяти.

В начале этого же цикла приема через коммутаторы 27, 42 на вход интегратора 44 поступает сигнал с первого выхода блока 36.1 регулируемой задержки сигнала. Интегратор 44 совместно с блоком выбора максимального значения 52 осуществляет поиск максимального экстремума на двух интервалах длительностью mT/2m+ и выдает код двух максимальных экстремумов в первую ячейку блока 61 памяти, запись в которой осуществляется по импульсам записи из синхронизатора 29. Код с выхода первой ячейки блока 61 памяти поступает на управляющие входы блоков 36.2, 36,3 регулируемой задержки сигнала, на входы которых поступают сигналы с выходов блока 36.1 регулируемой задержки сигнала, задержанные в первом и втором блоках 41,1, 41.2 линий задержки соответственно. Каждый блок линий задержки состоит из двух одинаковых линий задержки. Блоки 41.1, 41.2 линий задержки и блоки 36.2,36.3 регулируемой задержки сигнала являются второй ступенью обработки неравномерно укрупненного сигнала. Время задержки сигнала в j-м блоке задержки k-й ступени обработки неравномерно укрупненного сигнала определяется выражением k-1

1-1

k-1

TRj A mW1+ ; -)mJ/2

JT1

m/2

1-1

где А для блоков 41.1 +41. линий задержки,

A для блоков 41..2-2 линий задержки. ....

Блоки линий задержек необходимы для обеспечения поочередной обработки неравномерно укрупненного сигнала одним интегратором и блоком выбора максимального значения. Блоки 36.2,36.3 регулируемой задержки сигнала работают аналогично описанному выше. Число отводов линий задержек N2 шаг задержки Аг2. Число отводов линий задержек и шаг задержки к ступени обработки неравномерно укрупненного сигнала

Nk 2m+1 k,

Ark тТ/2ы + Ј m/2M,

i i

Таким образом, по окончании обработки неравномерно укрупненного сигнала второй ступенью, на выходах блока 36.2 регулируемой задержки сигнала появляются сигналы, соответствующие коду первого максимального экстремума с выхода первой ячейки блока 61 памяти, на интервале длительностью m/J2m+mf2, первый из которых поступает на вход интегратора 44 через коммутаторы 27 и 42. По окончании этого интервала на выходах блока 36.3 регулируемой задержки сигнала появляются сигналы, соответствующие коду второго максимального экстремума с выхода первой ячейки блока 61 памяти, на интервале длительностью mT/2m+m/ , первый из которых поступает на вход интегратора 44 через коммутаторы 27 и 42. Интегратор 44 и блок 52 выбора максимального значения работают аналогично описанному выше. Код четырех максимальных экстремумов записывается в вторую ячейку блока 61 памяти. Работа приемной стороны таким образом продолжается до конца записи информации в гН ячейку блока 61 памяти. После этого по сигналу из синхронизатора 29 коммутатор 44 подключает вход блока 52 выбора максимального значения к выходу коммутатора 42 и происходит поиск m/z максимальных экстремумов сигнала с первых выходов блоков 60.. регулируемой задержки сигнала и запись кодов максимальных экстремумов в п ячейку блока 61 памяти. Эти коды максимальных экстремумов, с выхода п ячейки блока 61 памяти гтосту- пают на управляющие входы блоков 60..2п регулируемой задержки сигнала, на сигнальные входы которых приходят сигналы с выходов блоков 60.,2п регулируемой задержки сигнала. Таким образом, на выходах блоков 60.2гИ+1- -60.2п регулируемой задержки сигнала поочередно с интервзлом Атп появляются сигналы с выхода фазового детектора 26, которые, проходя через коммутатор 54 и преобразователь 55 напряжение- код записывается в блок 62 памяти по т/2 импульсам записи от синхронизатора 29. По окончании записи сигнала в блок 62 памяти происходит последовательное считывание информации из блоков 30, 61, 62 памяти я запись информации в блок 57 записи-считывания и в блок 63 записи-считывания. В блок 63 записи-считывания информация записывается из п ячейки блока 61 памяти по четным импульсам синхронизатора 29, и из блока 62 памяти - по нечетным, Блоки 57, 63 записи-считывания состоят из двух каналов, в один из которых происходит запись информации, а с другого происходит считывание информации, принятой в предыдущем цикле, по пл импульсам считывания за время ml. Переключением каналов управляет синхронизатор 29. При считывании информация с выхода блока 57 записи-считывания преобразуется в аналоговую форму в цифро-аналоговом преобразователе 31, задерживается в линии 58 задержки и поступает на вход сумматора 32, где суммируется с

аналоговым сигналом, восстановленным из цифрового в блоке 59 восстановления квантованных значений и сглаженном в фильтре нижних частот 33. 8 результате суммирования получается оценка принятого сигнала НО (О .Линиязадержки58компенсирует временной сдвиг между каналами аналого- цифрового преобразователя 31 и блока 59 восстановления квантованных значений и

0 фильтра нижних частот 33.

Увеличение помехоустойчивости в предлагаемой системе связи достигается за счет увеличения энергии передачи разрядов цифрового кода выборок, несущих большую

5 информацию о сообщении, по сравнению с разрядами несущих меньшую информацию. Формулаизобретения 1. Система связи, содержащая на передающей стороне синхронизатор, генератор

0 сигнала, в ыход которого соединен с опорным входом блока фазовых модуляторов, выходы которого соединены с одними входами блока перемножителей, аналого-циф- ровойи цифроаналоговый i

5 преобразователи, блок фазоимпульсных модуляторов и генератор кодовых последова- , тельностей, а на приемной стороне-полосовой усилитель, вход которого является входом приемной стороны, амп0 литудный и фазовых детекторы, входы которых соединены с выходом полосового усилителя, первый коммутатор, второй коммутатор, управляющий вход которого соединен с одним выходом синхронизатора,

5 другой вход которого соединен с первым синхровходом первого блока памяти, цифроаналоговый преобразователь, сумматор и фильтр нижних частот, отличающая.с я тем, что, с целью повышения помехоустой0 чивости передачи сообщений в пороговой ; области, на передающей стороне введены блок вычитания, блок дискретизации сообщения, блок квантования, преобразователь ; код-напряжение, первый и второй блоки па5 мяти, амплитудный модулятор, блок, перемножитель и сумматор, один вход которого соединен с выходом амплитудного модулятора, остальные входы соединены с выходами блока фазоимпульсных модуляторов

0 через блок перёмножителей, а выход сумматора является выходом передающей стороны, входом которой является вход блока вычитания, и информационный вход анало- ro-цифрового преобразователя, соответст5 вующие выходы которого соединены с информационными входами второго блока памяти и информационными входами циф- роаналогового преобразователя, выход которого соединен через последовательно соединенные блок вычитания иблокдискретизации сообщения с входом блока квантования, выход которого соединен с информационным входом второго блока памяти, выходы которого соединены с одними входами блока фазоимпульсных модуляторов, к другим входам которого подключены выходы генератора кодовых последовательностей, выход блока квантования через преобразователь код-напряжение соединен с информационным входом первого блока памяти, выходы которого соединены с сигнальными входами блока фазовых модуляторов, а первый синхровход первого блока памяти соединен с первыми синхров- ходами второго блока памяти, опорным входомгенератора кодовых последовательностей, первым входом амплитудного модулятора, второй вход которого соединен с выходом генератора сигналов и одним выходом синхронизатора, соответствующие выходы которого подключены к тактовым входам аналого-цифрового и циф- роаналогового преобразователей, блока ди- скретизации сообщений и блока квантования, к вторым синхровходам первого и второго блоков памяти, выходы которых соединены с информационными входами генератора кодовых последовательностей, а на приемной стороне введены синхронизируемый генератор, блок обработки информации, последовательно соеди- ненные третий коммутатор, первый интегратор, первый блок выбора максимального значения последовательно соединенные четвертый коммутатор, второй интегратор и второй блок выбора максимального значения, блок регулируемой задержки сигнала, п-М ячеек блока памяти, последовательно включенные пятый коммутатор, преобразователь напряжение-код, второй блок памяти, шестой коммутатор, первый блок записи-считывания, и блок восстановления квантованных значений, выход которого через фильтр нижних частот соединен с первым входом первого сумматора, выход которого является выходом приемной стороны, а второй вход сумматора соединен через введенную линию задержки и цифроанзлоговый преобразователь с выходом второго введенного блока записи-считывания, соответствующие информационные входы которого соединены с выходом первого блока памяти и п ячеек блока памяти, а управляющий и первый тактовый входы соединены с управляющим и первым тактовым входами первого блока записи-считывания соответственно и выходами синхронизатора, вход которого подключен к выходу амплитудного детектора, первому сигнальному входу блока обработки сигнала и первым

информационным входам третьего и четвертого коммутаторов, а соответствующие выходы синхронизатора подключены к управляющему входу четвертого коммутатора, второй информационный вход которого соединен с вторым информационным входом третьего коммутатора и выходом первого коммутатора, к управляющему входу третьего коммутатора, к управляющему и

0 первому тактовому входам второго интегратора, к управляющему и первому тактовому входам первого интегратора, к первому тактовому входу первого блока выбора максимального значения и второму тактовому

5 входу первого интегратора, к синхровходу и второму тактовому входу первого блока выбора максимального значения, выход которого соединен с первым информационным входом второго коммутатора, к первомутак0 товому входу второго блока выбора максимального значения и второму тактовому входу второго интегратора, к синхровходу и второму тактовым входу второго блока выбора максимального значения, выход кото5 рого соединен с вторым информационным входом второго коммутатора, выход которого соединен с информационными входами первого блока памяти, к первому синхронизационному входу п ячеек блока памяти и

0 второму синхровходу первого блока памяти, причем разрядные выходы п ячеек блока памяти соединены с управляющими входами блока обработки сигнала, одни выходы которого подключены к одним входам пер5 вого коммутатора, другие входы которого подключены к сигнальным входам блока регулируемой задержки сигнала, сигнальные входы которого подключены к вторым выходам блока обработки сигнала, а управляю0 щие входы блока регулируемой задержки сигнала соединены с разрядными выходами блока памяти соответственно, п-1, ячеек памяти, к второму синхровходу п ячеек блока памяти, и к управляющему входу шестого

5 коммутатора, информационные входы которого соединены с выходами п ячеек блока памяти, к управляющему входу пятого коммутатора, информационные входы которого соединены с выходами блока регулируемой

0 задержки сигнала, к управляющему входу первого коммутатора, к первому входу синхронизируемого генератора, второй вход которого соединен с выходом полосового усилителя и входом амплитудного детектора,

5 а выход синхронизируемого генератора соединен с вторым входом фазового детектора, выход которого подключен к второму сигнальному входу блока обработки сигналов.

2. Система по п. 1,отличающаяся тем, что генератор кодовых последовательностей на передающей стороне содержит фазоимлульсный модулятор и (2П -1) ячеек блока регулируемой задержки импульса, информационные входы которых, информационный вход фазоимпульсного модулятора и опорный вход фазоимпульсного модулятора являются информационными и опорным входами генератора кодовых последовательностей, выходами которого являются выходы (2 ) ячеек блока регулируе- мой задержки импульса, причем выход фазоимпульсного модулятора подключен к опорному входу первого блока регулируемой задержки импульса, а каждый из двух выходов каждого блока регулируемой за- держки импульса из числа первого - -2п-1 ячеек блока регулируемой задержки импульса соединен с опорным входом другого блока регулируемой задержки импульса.

3. Система по п. 2, о т л и ч а ю щ а я с я тем, что блок регулируемой задержки импульса генератора кодовых последовательностей содержит линию задержки, первый и второй фазоимпульсные модуляторы, информационные входы и выходы которых яв- ляются информационными входами и выходами блока регулируемой задержки импульса соответственно, а опорный вход первого фазоимпульсного модулятора, соединенный с опорным входом второго фазо- импульсного модулятора через линию задержки, является опорным входом блока регулируемой задержки импульса,

4. Система п. 1,отлича ю щаясятем, что блок обработки сигнала на приемной сто- роне содержит 2п-2 ячеек блока линий задержек, первые 2п-1 ячейки блока регулируемой задержки сигнала, управляющие входы которых являются управляющими входами блока обработки сигнала, а первые выходы являют- ся одними выходами блока обработки сигнала, другими выходами которого являются первый и второй выходы 2 -1+2п-2 ячеек блока линий задержек, входы которых соединены с выходами 2n V2n-1 ячеек блока регу- лируемой задержки сигнала соответственно, причем первый и второй сигнальные входы первой ячейки блока регулируемой задержки сигнала являются соответственно пер

вым и вторым сигнальными входами блока обработки сигнала, а первый и второй выходы каждого блока регулируемой задержки сигнала из числа 2 ячеек блока регулируемой задержки сигнала соединены с первым и вторым входами двух ячеек блока линий задержек, а первый и второй выходы каждой ячейки блока линий задержек, из числа ячейки блока линий задержек, подключены к первому и второму сигнальным входам блока регулируемой задержки сигнала соответственно.

5. Система по п. 4, отличающаяся тем, что каждый блок регулируемой задержки сигнала блока обработки сигнала содержит первую и вторую линии задержек, входы которых являются первым и вторым сигнальными ЁХОДЭМИ блока регулируемой задержки сигнала соответственно, первый и второй коммутаторы, информационные входы которых соединены с выходами первой и второй линий задержек соответственно, а объединенные управляющие входы и выходы первого и второго коммутаторов являются управляющим входом, первым и вторым выходами блока регулируемой задержки сигнала соответственно,

6. Система поп. 1, о уличающаяся тем, что каждый интегратор на приемной стороне содержит сумматор, первую и вторую ячейки памяти, линию задержки и коммутатор, управляющий вход и выход которого являются управляющим входом и выходом интегратора соответственно, сигнальным входом которого являются соеди- неиные первые входы сумматора и коммутатора, а соединенный вход линии задержки, выход которой соединен с первым тактовым входом первой ячейки памяти, первый тактовый вход второй ячейки памяти, соединенные вторые тактовые входы первой и второй ячеек памяти являются первым и вторым тактовыми входами интегратора соответственно, причем выход сумматора соединен с вторым входом коммутатора через вторую ячейку памяти, выход которой соединен с вторым входом сумматора через первую ячейку памяти.

CM

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель отношения переменных напряжений | 1986 |

|

SU1357855A1 |

| ИМПУЛЬСНЫЙ РАДИОЛОКАТОР | 1985 |

|

SU1840927A1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР | 1992 |

|

RU2067316C1 |

| Широкополосная система связи | 1985 |

|

SU1401625A1 |

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| Каскад линии задержки | 1989 |

|

SU1629959A1 |

| Устройство для передачи телеметрической информации | 1976 |

|

SU661593A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Устройство для формирования корректирующего сигнала телевизионного датчика | 1982 |

|

SU1125772A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1996 |

|

RU2099739C1 |

Изобретение относится к радиотехнике и предназначено для использования в радиосвязи для передачи аналоговых сигналов. Целью изобретения является повышение помехоустойчивости передачи сообщений в пороговой области. Для этого на передающей стороне введены блок вычитания, блок дискретизации сообщёния;блок квантования, преобразователь код-напряжение, первый блок памяти, второй блок памяти, ячейки памяти, амплитудный модулятор, сумматор, а на приемной стороне - синхронизируемый генератор, блок обработки сигнала, коммутаторы первого и второго интеграторов, первого и второго блоков выбора максимального значения, блок регулируемой задержки сигнала, п + 1 ячеек блока памяти, преобразователь напряжение-код, первый и второй блоки записи-считывания, линия задержки 57 и блок восстановления квантованных значений. 5 з.п. ф-лы, 2 ил. (Л С

| Авторское свидетельство № 1591740, кл | |||

| Н .0.4.27/00, 1988 | |||

| Широкополосная система связи | 1985 |

|

SU1401625A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-05-15—Публикация

1989-12-06—Подача