Изобретение относится к импульсной технике и может быть использовано в радиотехнике и вычислительной технике.

Известен генератор псевдослучайных последовательностей, содержащий два счетчика, генератор тактовых импульсов, регистр, блок управления, сумматор и блок памяти с соответствующими связями, выбранный в качестве прототипа. Устройство-прототип позволяет генерировать псевдослучайные последовательности (ПСП) длины N.

Однако такое устройство обладает узкими функциональными возможностями, так как не позволяет оперативно изменять структуру и длительность генерируемых последовательностей.

Цель изобретения - расширение функциональных возможностей за счет обеспечения оперативного изменения структуры и длительности генерируемых псевдослучайных последовательностей.

Для этого в генератор псевдослучайных последовательностей, содержащий генератор тактовых импульсов, два счетчика и блок памяти, введены блок подготовки к работе, две схемы сравнения, два элемента ИЛИ, сумматор по модулю, мультиплексор, элемент И, формирователь импульсов, причем первый вход блока подготовки к работе соединен с входом задания модуля, второй вход соединен с входом задания первообразного элемента, третий вход соединен с входом запуска, первый выход блока подготовки к работе соединен с первым входом элемента И, второй выход соединен с первыми входами элементов ИЛИ, третий выход соединен с первыми входами схем сравнения и первым входом сумматора по модулю, четвертый выход соединен с первым входом мультиплексора, пятый выход соединен с управляющим входом мультиплексора, шестой выход соединен с информационным входом блока памяти, а седьмой выход соединен с входом разрешения записи блока памяти, выход генератора тактовых импульсов соединен с вторым входом элемента И, выход которого соединен с счетным входом первого счетчика и входом формирователя импульсов, выход которого соединен с входом разрешения чтения блока памяти, выход первого счетчика соединен с вторым входом сумматора по модулю и с вторым входом первой схемы сравнения, выход которой соединен с вторым входом первого элемента ИЛИ и с счетным входом второго счетчика, выход которого соединен с третьим входом сумматора по модулю и с вторым входом второй схемы сравнения, выход которой соединен с вторым входом второго элемента ИЛИ, выход которого соединен с обнуляющим входом второго счетчика, выход первого элемента ИЛИ соединен с обнуляющим входом первого счетчика, выход сумматора по модулю соединен со вторым входом мультиплексора, выход которого соединен с адресным входом блока памяти, выход которого является выходом генератора, причем блок подготовки к работе содержит умножитель, три элемента задержки, два элемента ИЛИ, схему сравнения, мультиплексор, формирователь остатка, счетчика, триггер и элемент И, первый вход блока соединен с первым входом формирователя остатка, первым входом схемы сравнения и третьим выходом блока, второй вход блока соединен с первым входом умножителя, третий вход блока соединен с вторым входом блока, с входом установки единичного состояния триггера, с входом установки единичного состояния счетчика, с входом первого элемента задержки, выход которого соединен с первыми входами первого и второго элемента ИЛИ, с управляющим и первым информационным входом мультиплексора, выход которого соединен с вторым входом умножителя, выход которого соединен с вторым входом формирователя остатка, информационный выход которого соединен с вторым информационным входом мультиплексора и четвертым выходом блока, управляющий выход формирователя остатка соединен с пятым выходом блока, с вторым входом первого элемента ИЛИ, с входом второго элемента задержки, с вторым входом второго элемента ИЛИ, выход которого соединен с седьмым выходом блока, выход первого элемента ИЛИ соединен с входом третьего элемента задержки, выход которого соединен с первым входом элемента И, выход которого соединен с шестым выходом блока и вторым входом схемы сравнения, выход которой соединен с обнуляющим входом счетчика, с входом установки в нуль триггера, прямой выход которого соединен с вторым входом элемента И, а инверсный выход с первым выходом блока.

Сущность изобретения реализуется за счет введения новой совокупности конструктивных признаков, определяющих его соответствие критерию "Новизна".

Введение первой и второй схемы сравнения обеспечивает изменение коэффициента пересчета первого и второго счетчиков.

Введение элемента И обеспечивает управление работой генератора.

Введение блока подготовки к работе обеспечивает подготовку к работе генератора псевдослучайных последовательностей.

Введение сумматора по модулю обеспечивает формирование адресов на входе блока памяти в необходимой последо- вательности.

Введение мультиплексора обеспечивает коммутацию адресов на входе блока памяти.

Введение формирователя импульсов обеспечивает формирование импульсов чтения для блока памяти.

Введение элементов ИЛИ обеспечивает управление режимами работы счетчиков.

Существенными отличительными признаками предлагаемого изобретения являются элемент И, первая и вторая схемы сравнения, элементы ИЛИ, блок подготовки к работе, сумматор по модулю, мультиплексор и формирователь импульсов.

Указанные признаки являются существенными, так как они отсутствуют в прототипе, и их совокупность придает генератору возможность оперативного изменения структуры и длительности генерируемых псевдослучайных последовательностей.

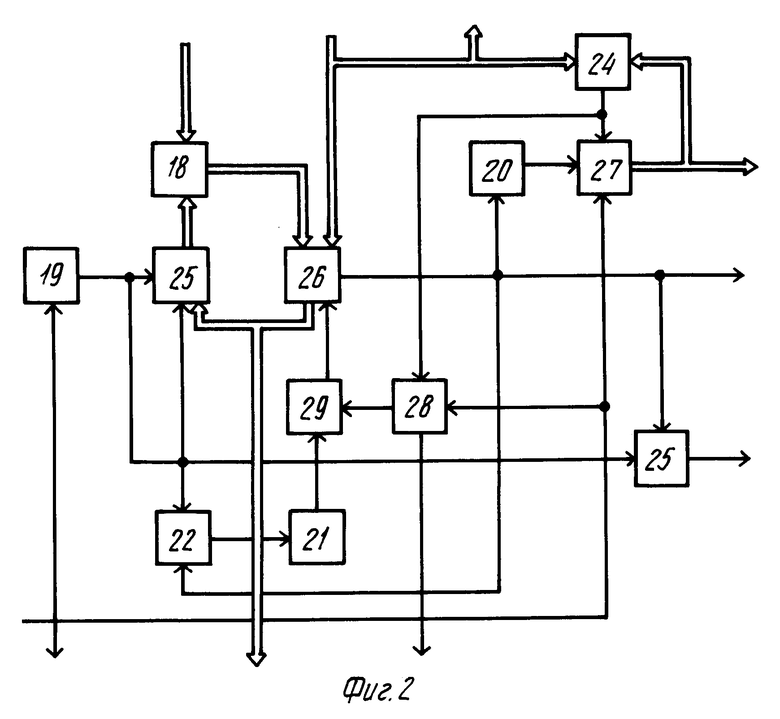

На фиг. 1 представлена функциональная схема генератора псевдослучайных последовательностей; на фиг. 2 - функциональная схема блока формирования кодов.

Генератор псевдослучайных последовательностей (фиг.1) содержит вход 1 задания модуля, вход 2 задания первообразного элемента, вход 3 запуска генератора, генератор 4 тактовых импульсов, первый 5 и второй 6 счетчики, блок 7 памяти, блок 8 формирования кодов, первую 9 и вторую 10 схемы сравнения, первый 11 и второй 12 элементы ИЛИ, сумматор 13 по модулю, мультиплексор 14, элемент И 15, формирователь 16 импульсов, выход 17 генератора.

Блок 8 (фиг.2) содержит умножитель 18, первый 19, второй 20 и третий 21 элементы задержки, первый 22 и второй 23 элементы ИЛИ, схему 24 сравнения, мультиплексор 25, формирователь 26 остатка, счетчик 27, триггер 28 и элемент И 29 с соответствующими связями.

Генератор псевдослучайных последовательностей работает следующим образом.

Перед началом работы на вход 1 генератора подается значение модуля, а на вход 2 значение первообразного элемента, которые удерживаются в течение всего времени работы генератора. Начало работы генератора определяется моментом подачи на его вход 3 импульса запуска. При этом импульс запуска запускает блок 8 подготовки к работе, и, проходя через него, поступает на первые входы элементов ИЛИ 11 и 12 и на обнуляющие входы счетчиков 5 и 6, устанавливая их в нулевое состояние. Блок 8 формирует элемент базовой ПСП, который поступает на информационный вход блока 7 памяти, а также формирует адрес, по которому записывается сформированный элемент, который через мультиплексор 14 управляет блоком 7 памяти. После прихода с блока 8 подготовки к работе импульса записи на вход разрешения записи блока 7 памяти, происходит запись сформированного элемента по заданному адресу. После записи Р-1 элементов базовой ПСП в блок 7 памяти, блок 8 вырабатывает единичный потенциал свидетельствующий о том, что генератор готов к работе и подает его на элемент И 15. Тактовые импульсы с выхода генератора 4 тактовых импульсов через открытый элемент И 15 поступают на счетный вход счетчика 5, который осуществляет их последовательное суммирование. При этом модуль пересчета счетчиков 5 и 6 будет определяться величиной длительности ПСП, поступаемой с третьего выхода блока 8 на первые входы схем 9 и 10 сравнения. После подсчета счетчиком 5 количества импульсов, равного длительности ПСП, срабатывает схема 9 сравнения, и импульс с ее выхода обнуляет счетчик 5. Счетчик 6 подсчитывает этот импульс с выхода схемы 9 сравнения. Схема 10 сравнения срабатывает по мере того, как объем счетчика 6 достигает значения длительности ПСП и обнуляет своим импульсом счетчик 6. Выходы счетчиков 5 и 6 соединены со вторым и третьим входом сумматора 13 по модулю. Сумматор 13 по модулю производит суммирование по модулю (равному величине длительности ПСП) входной информации и формирует адрес считывания ПСП, который через мультиплексор 14 поступает на блок 7 памяти. Формирователь 16 импульсов формирует импульсы чтения для блока 7 памяти, при подаче которых на его вход разрешения чтения на выходе этого блока, являющегося выходом устройства, появляются символы ПСП в соответствии с формируемыми адресами.

Очевидно, что последовательность адресов, формируемая сумматором 14, имеет вид 0, 1, 2, 3.....N-1,1,2,3.....N-1,0,2,3.....N-1,0,1....., где N - период ПСП.

Таким образом, генератор псевдослучайных последовательностей формирует псевдослучайную последовательность и все ее автоморфные преобразования, т. е. циклические сдвижки.

Блок 8 (фиг.2) работает следующим образом.

В данном устройстве блок 8 реализует функцию генератора кодов квадратичных вычетов, правила формирования которых приведены в книге Свердлик М.Б. Оптимальные дискретные сигналы. М. : Сов. радио, 1975. Код модуля, воздействуя на первый вход блока 8, определяет поле GF(P), в котором будет осуществляться формирование кодов квадратичных вычетов. Этот код поступает на первый вход формирователя 26 остатка, на первый вход схемы 24 сравнения и на третий выход, который является выходом задания длины ПСП. На второй вход блока 8 воздействует код первообразного элемента, импульс запуска устройства, поступает на третий вход блока, проходит на его второй выход, переводит триггер 28 в единичное состояние, записывает в счетчик 27 единицу и поступает на вход элемента 19 задержки. После того, как произошла установка триггера 28 и счетчика 27, импульс с выхода элемента 19 задержки, проходя через элемент 23 ИЛИ, поступает на вход блока 7 разрешения записи. В результате в блок 7 памяти по нулевому адресу (так как адрес поступает через мультиплексор 14 с выхода сумматора 13, а счетчики 5 и 6 обнулены) записывается единица. Одновременно импульс с выхода элемента 19 задержки поступает на управляющий вход мультиплексора 25 и на его первый информационный вход. В результате мультиплексор 25 оказывается скоммутированным таким образом, что на его выходе единица оказывается в самом младшем разряде, а в остальных разрядах - нули. Блок 18 осуществляет умножение первообразного элемента θ на единицу и результат выдает на второй информационный вход формирователя 26 остатка. К этому времени импульс, прошедший через элемент ИЛИ 22, элемент 21 задержки и открытый элемент И 29, запускает формирователь 26 остатка в работу. По мере того, как формирователь 26 остатка осуществляет вычисление остатка по модулю Р, он выдает на свой управляющий выход импульс, а на информационный выход - величину сформированного остатка. Импульс с выхода формирователя 26 остатка поступает на управляющий вход мультиплексора 14, а через элемент ИЛИ 23 поступает на вход разрешения записи блока 7 памяти. В результате выход мультиплексора 14 оказывается скоммутированным с его первым входом, и в блок 7 памяти по адресу, задаваемому величиной остатка, записывается содержимое счетчика 27 (единица, так как θ1= θ). Этот же импульс с выхода формирователя 26 остатка через элемент 20 задержки поступает на счетный вход счетчика 27, добавляя к его содержимому единицу, а также поступает через цепочку элемента ИЛИ 22, элемента 21 задержки и элемента И 29 на управляющий вход формирователя 26 остатка. На втором входе формирователя 26 остатка к этому времени образуется величина θ2, которую формирователь 26 остатка приводит по модулю Р. Далее работа блока происходит как описано выше. Как только содержимое счетчика станет равным величине модуля, сработает схема 24 сравнения, которая обнуляет счетчик 27 и переводит триггер 28 в нулевое состояние. При этом единичный потенциал с инверсного выхода триггера 28 открывает элемент И 15 (фиг.1) и генератор переходит в режим генерации псевдослучайных последовательностей, записанных, к этому времени в блок 7 памяти.

Итак, предлагаемый генератор ПСП позволяет генерировать псевдослучайные последовательности различной длительности и различной структуры, а также все их циклические сдвижки. Путем изменения величины модуля Р и первообразного элемента θ обеспечивается изменение структуры и длительности генерируемых последовательностей. Причем при изменении структуры блока 8 могут быть изменены классы генерируемых последовательностей. В предлагаемом устройстве структура блока 8 предназначена для генерирования последовательностей типа кодов квадратичных вычетов.

Технико-экономическая эффективность предлагаемого изобретения заключается в расширении области применения за счет гибкого реагирования на состояние канала связи путем изменения структуры и длительности генерируемых последовательностей.

Изобретение относится к импульсной технике может быть использовано в радиотехнике и вычислительной технике. Цель изобретения - расширение функциональных возможностей за счет обеспечения оперативного изменения структуры и длительности генерируемых псевдослучайных последовательностей. Для этого в генератор псевдослучайных последовательностей, содержащий генератор 4 тактовых импульсов, счетчики 5 и 6 импульсов и блок 7 памяти, введены блок 8 формирования кодов два блока 9 и 10 сравнения, элементы ИЛИ 11 и 12, сумматор 13 по модулю, мультиплексор 14, элемент И 15, формирователь 16 импульсов. 1 з.п. ф-лы, 2 ил.

| Генератор псевдослучайных последовательностей | 1986 |

|

SU1406739A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-03-27—Публикация

1991-07-10—Подача