(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1990 |

|

RU2020766C1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1988 |

|

SU1596473A1 |

| Генератор псевдослучайных чисел | 1984 |

|

SU1239844A1 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

| Дискретный согласованный фильтр | 1978 |

|

SU771891A2 |

| Устройство поиска псевдослучайной последовательности | 1991 |

|

SU1788592A1 |

| Управляемая линия задержки | 1990 |

|

SU1725370A2 |

| Устройство для генерирования кодов заданного веса | 1985 |

|

SU1275413A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

Изобретение может быть использовано в радио-и вычислительной нике и позволяет расширить функциональные возможности устройства. Генератор содержит счетчики 3 и 4, генератор 1 тактовых импульсов и регистр 7. Введение блока 2 управления, сумматора 5, блока 6 памяти и образование новых функциональных связей расширяет класс генерируемых псевдосяу- чайных последовательностей. В пписа- сании приведен пример реализации блока 2 управления. 1 з.и. ф-лы, 3 ил

LiJM

i-1-Ч

6

I ,.. I ...

1

Од Ч

00 со

Изобретение относится к импульсно технике и может быть использовано п радиотехнике и вьпшслительНой технике .

Целью изобретения является расши- функциональных возможностей за счет расширения класса генерируемых псевдослучайных последовательностей.

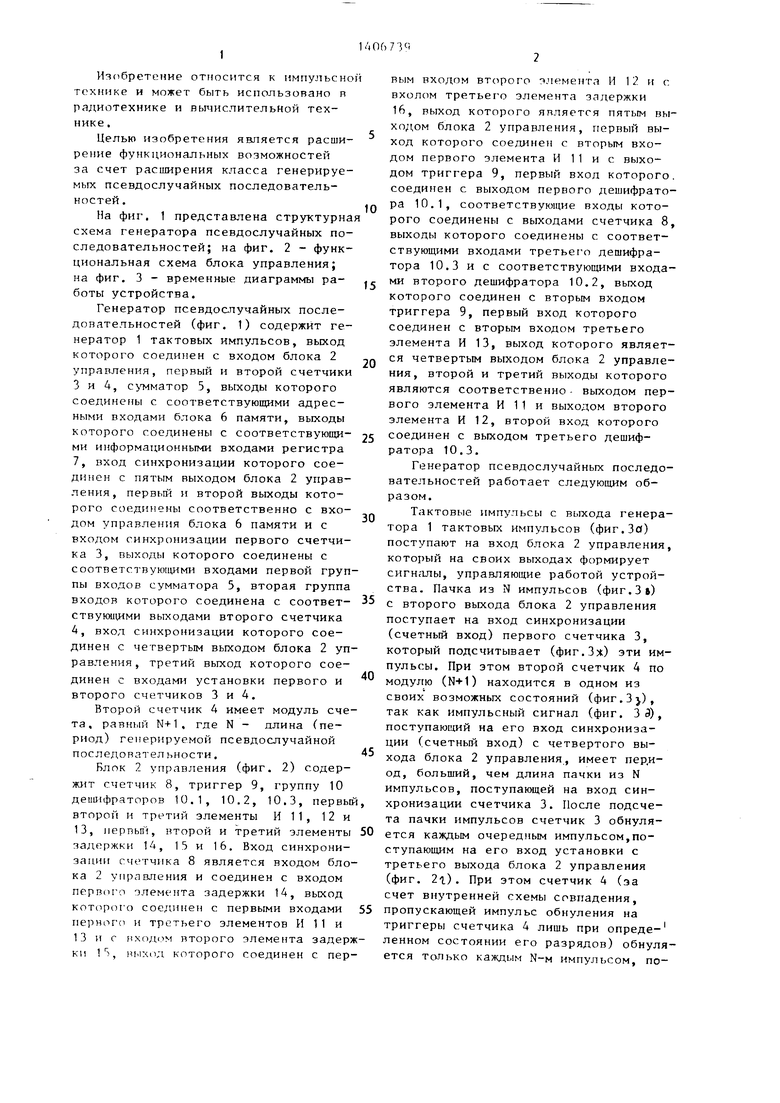

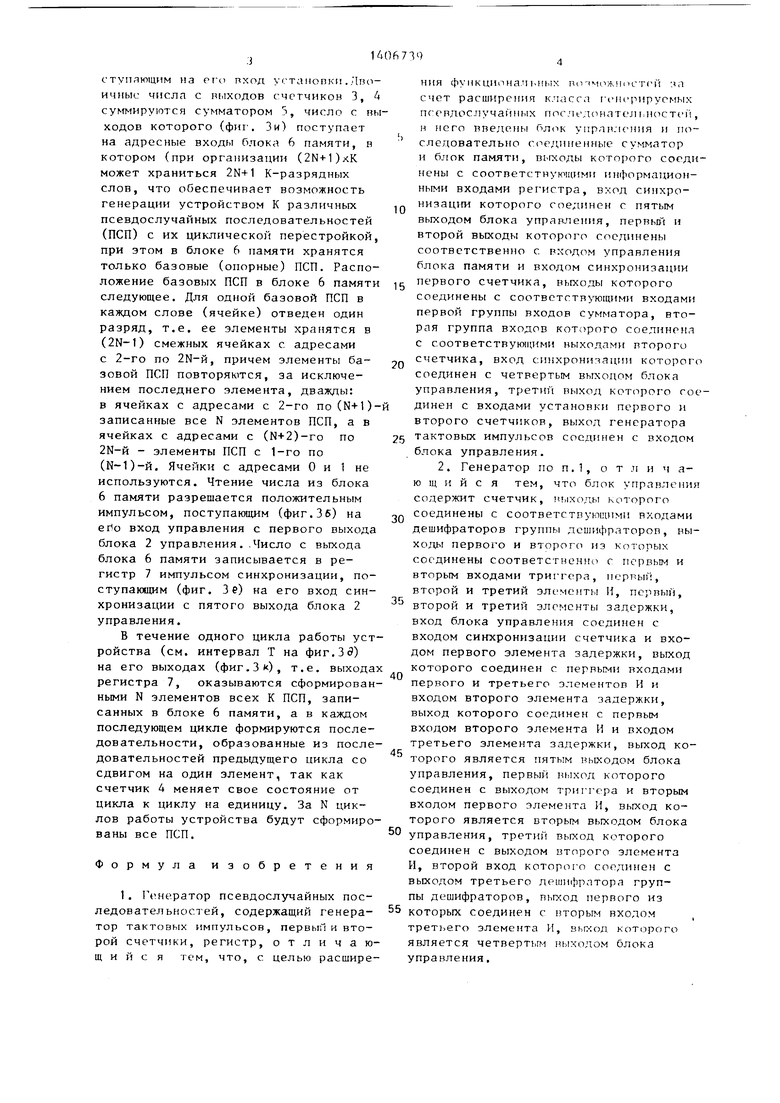

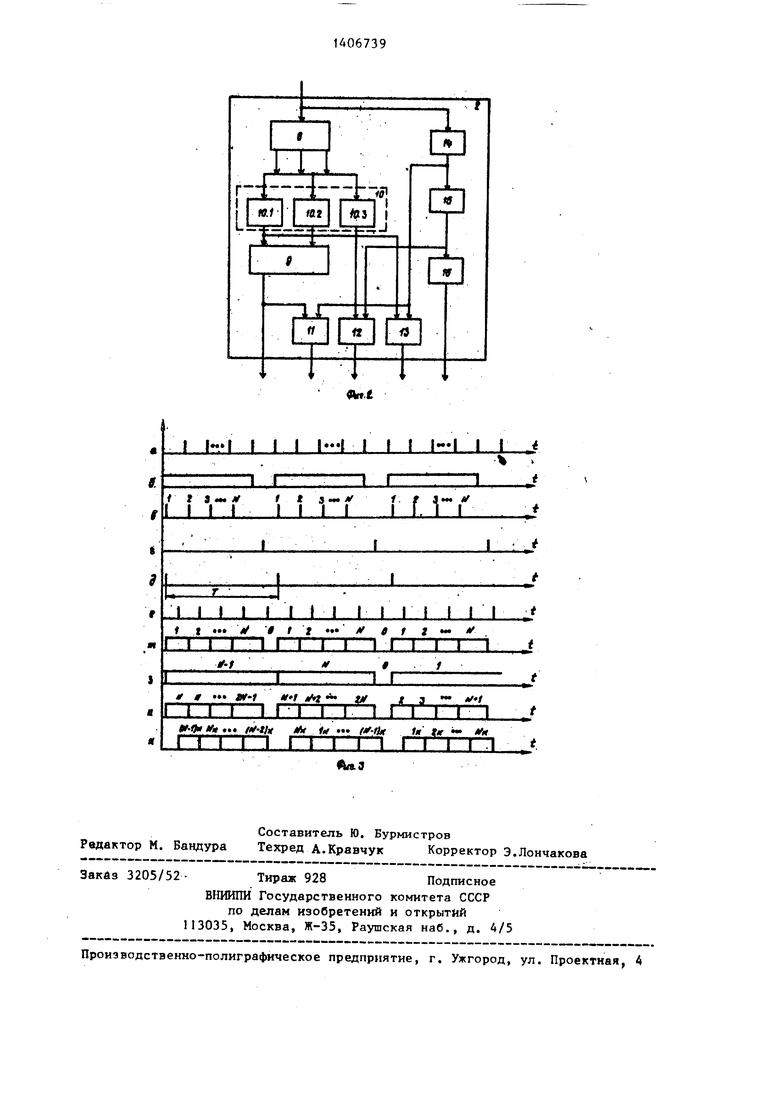

На фиг. 1 представлена структурна схема генератора псевдослучайных последовательностей; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - временные диаграммы ра- боты устройства.

Генератор псевдослучайных последовательностей (фиг. 1) содержит генератор 1 тактовых импульсов, выход

которого соединен с входом блока 2

управления, первый и второй счетчики 3 и 4, с матор 5, выходы которого соединены с соответствующими адресными входами блока 6 памяти, выходы которого соединены с соответствующи- ми информационными входами регистра 7, вход синхронизации которого соединен с пятым выходом блока 2 управления, первый и второй выходы которого соединены соответственно с входом управления блока 6 памяти и с входом синхронизации первого счетчика 3, выходы которого соединены с соответствуюнщми входами первой группы входов сумматора 5, вторая группа входов которого соединена с соответ- ствующими выходами второго счетчика 4, вход синхронизации которого соединен с четвертым выходом блока 2 управления, третий выход которого соединен с входами установки первого и второго счетчиков 3 и 4.

Второй счетчик 4 имеет модуль счета, равный N+1, где N - ллина (период) генерируемой псевдослучайной последовательности.

Блок 2 управления (фиг. 2) содержит счетчик 8, триггер 9, группу 10 деиифраторов 10.1, 10.2, 10.3, первы второй и третий элементы И 11, 12 и 13, лерпьй, второй и третий элементы задержки 14, 15 и 16. Вход синхронизации счетчика 8 является входом блока 2 управления и соединен с входом перв(Ч о элемента задержки 14, выход котсфог о соединен с первыми входами перногс и третьего элементов И 1 1 и 13 и с иход()м второго элемента задерки 1 S, HMXiv i которого соединен с пер

0

0

0

5 5

0 5 5

вым входом BT iporo элемента И 12 и с входом третьего элемента задержки 16, выход которого является пятым выходом блока 2 управления, первый выход которого соединен с вторым входом первого элемента Н 11 и с выходом триггера 9, первый вход которого. coeдиt eн с выходом первого дешифратора 10.1, соответствующие входы которого соединены с выходами счетчика 8, выходы которого соединены с соответствующими входами третьего дешифратора 10.3 и с соответствуюгдими входами второго дешифратора 10.2, выход которого соединен с вторым входом триггера 9, первый вход которого соединен с вторым входом третьего элемента И 13, выход которого является четвертым выходом блока 2 управления, второй и третий выходы которого являются соответственно- выходом первого элемента И 11 и выходом второго элемента И 12, второй вход которого соединен с выходом третьего дешифратора 10.3.

Генератор псевдослучайных последовательностей работает следующим образом.

Тактовые импульсы с выхода генератора 1 тактовых импульсов (фиг.За) поступают на вход блока 2 управления, который на своих выходах формирует сигнгшы, управляющие работой устройства. Пачка из N импульсов (фиг.3 ft) с второго выхода блока 2 управления поступает на вход синхронизации (счетный вход) первого счетчика 3, который подсчитывает (фиг.З);) эти импульсы. При этом второй счетчик 4 по модулю (М-ь1) находится в одном из своих возможных состояний (фиг.З), так как импульсный сигнал (фиг. 35), поступающий на его вход синхронизации (счетный вход) с четвертого выхода блока 2 управления, имеет пер.и- од, больший, чем длина пачки из N импульсов, поступающей на вход синхронизации счетчика 3. После подсчета пачки импульсов счетчик 3 обнуляется каждым очередным импульсом,по- cтyпaюш м на его вход установки с третьего выхода блока 2 управления (фиг. 21). При этом счетчик 4 (за счет внутренней схемы совпадения, пропускающей импульс обнуления на триггеры счетчика 4 лишь при опреде- ленном состоянии его разрядов) обнуляется талько каждым N-M импульсом, поступающим на efo пход установки. Лвс1- ичиыс числа с ныходов счетчиков 3, 4 cyNfMHpyioTCH су тматором 5, число с выходов которого (фиг . Зи) поступает на адресные входр) блока 6 памяти, н котором (при организации (2N+l)xK может храниться 2N+1 К-разрядных слов, что обеспечивает возможность генерации устройством К различных псевдослучайных последовательностей (ПСП) с их циклической перестройкой, при этом в блоке 6 памяти хранятся только базовые (опорные) ПСП. Расположение базовых ПСП в блоке 6 памяти следующее. Для одной базовой ПСП в каждом слове (ячейке) отведен один разряд, т.е. ее элементы хранятся в (2N-1) смежных ячейках с адресами с 2-го по 2М-й, причем элементы базовой ПСП повторяются, за исключением последнего элемента, дважды: в ячейках с адресами с 2-го по ()записанные все N элементов ПСП, а в ячейках с адресами с (N+2)-ro по 2Ы-й - элементы ПСП с 1-го по (Н-1)-й. Ячейки с адресами О и 1 не используются. Чтение числа из блока 6 памяти разрешается положительным импульсом, поступающим (фиг.Зб) на вход управления с первого выхода блока 2 управления. .Число с выхода блока 6 памяти записывается в регистр 7 импульсом синхронизации, поступающим (фиг. 3е) на его вход синхронизации с пятого выхода блока 2 управления.

В течение одного цикла работы устройства (см. интервал Т на фиг. 35) на его выходах (фиг.Зх), т.е. выхода регистра 7, оказываются сформирован N элементов всех К ПСП, записанных в блоке 6 памяти, а в каждом последующем цикле формируются последовательности, образованные из последовательностей предыдущего цикла со сдвигом на один элемент, так как счетчик 4 меняет свое состояние от цикла к циклу на единицу. За N циклов работы устройства будут сформированы все ПСП.

Формула изобретения

5

0

5

НИЯ функциональных П(1Ч -10ЖИОСТ(М 3,1

счет расширения класса гчми рирусмых ПС евл ослу чайных последстнатсмп ностсГ, н него введены блок упрлнлония и последовательно соединенные сумматор и блок памяти, вьгходы которого соединены с соответствующими информационными входами регистра, вход синхронизации которого соединен с пятым выходом блока управления, первьв и второй выходы которого соединены соответственно с входом управления блока памяти и входом синхронизации первого счетчика, в)1ходы которого соединены с соответствующими входами первой группы входов сумматора, вторая группа входов которого соединрна с соответствующими выходами второго счетчика, вход синхрони: 1ац11и которого соединен с четвертым выходом блока управления, третий выход которого соединен с входами установки первого и второго счетчиков, выход генератора тактовых импульсов соединен с входом блока управления.

0

5

0

5

0

| Генератор псевдослучайных последовательностей | 1980 |

|

SU942013A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU942014A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-30—Публикация

1986-12-01—Подача