Изобретение относится к автоматике и вычислительной технике и может быть использовано в контрольно-измерительных приборах с семисегментными индикаторами.

Целью изобретения является упрощение преобразователя.

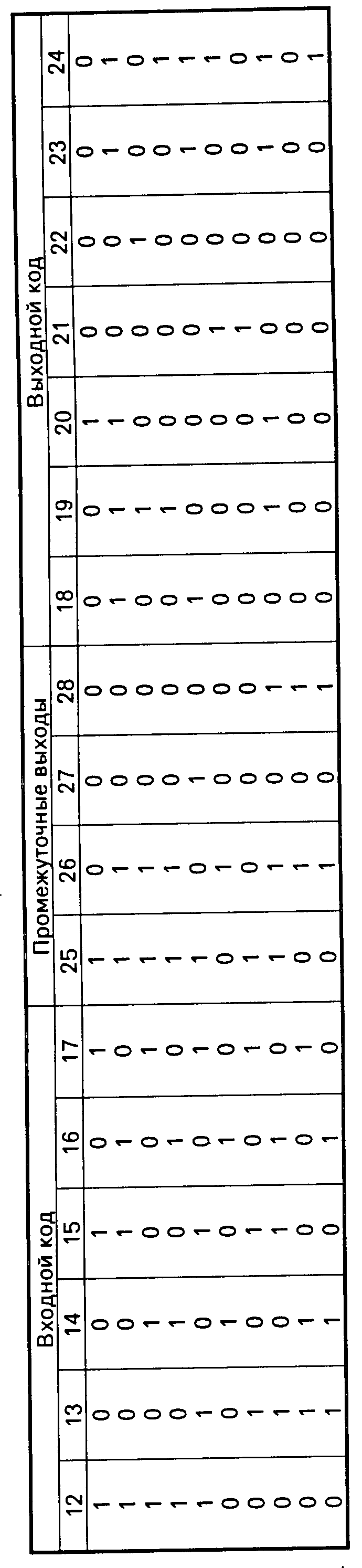

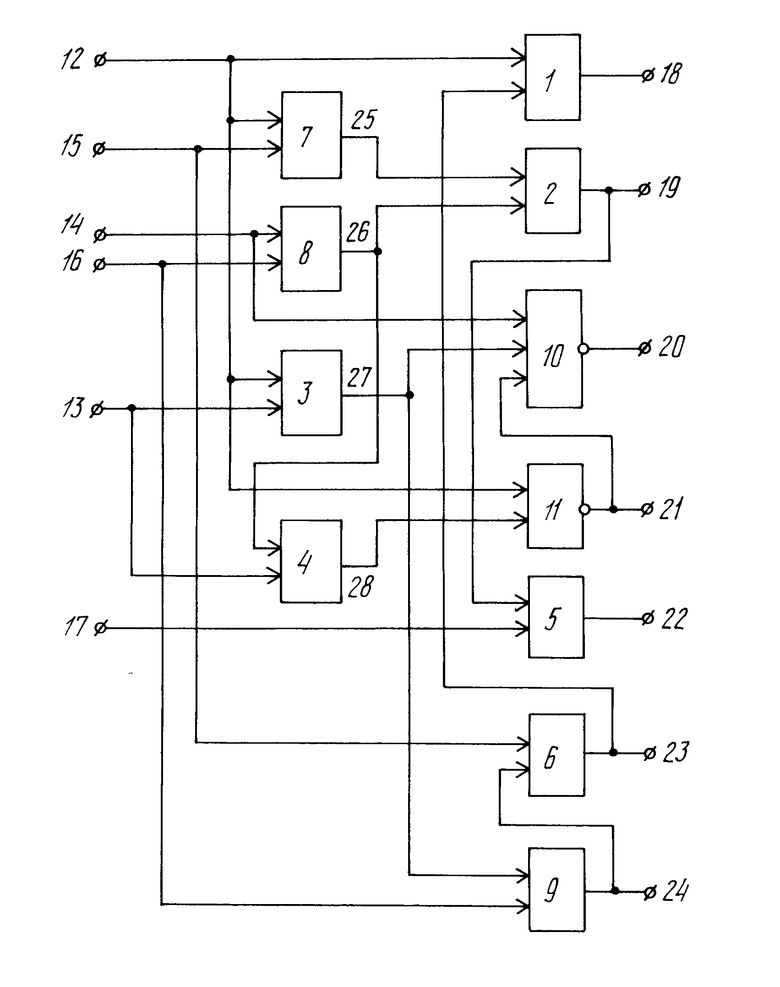

На чертеже представлена функциональная схема заявляемого преобразователя.

Преобразователь кода 2421 в двоично-десятичный код содержит элементы И 1-6, элементы ИЛИ 7-9, элементы ИЛИ-НЕ 10,11, входы 12-17 кода 2421, выходы 18-24 семипозиционного двоично-десятичного кода и промежуточные выходы 25-28.

Преобразователь работает следующим образом (см.также табл.),

На входы 12-17 подаются сигналы разрядов входного кода 2421, а именно: на вход 12 - инверсный сигнал четвертого разряда (с весом "2"): на вход 13 - прямой сигнал третьего разряда (с весом "4"); на входы 14,15 - соответственно прямой и инверсный сигналы второго разряда (с весом "2"); на входы 16,17 - соответственно прямой и инверсный сигналы первого разряда (с весом "1"). С поступлением указанных сигналов на входы 12-17 формируются сигналы на промежуточных выходах 25-28 с выходов элементов ИЛИ 7,8, И 3,4 соответственно. На выходах 19,21,24 формируются сигналы второго, четвертого и седьмого разрядов выходного семипозиционного двоично-десятичного кода. При этом сигнал на выходе 19 формируется в элементе И 2 из сигналов с выходов 25,26; сигнал на выходе 21 формируется в элементе ИЛИ-НЕ 11 из сигналов с входа 12 и выхода 28 ; сигнал на выходе 24 формируется в элементе ИЛИ 9 из сигналов с входа 16 и выхода 27. По сигналу с выхода 19, передаваемому по цепи обратной связи, и по сигналу с входа 17 на выходе 22 элемента И 5 формируется сигнал пятого разряда выходного кода.

По сигналу с выхода 24, передаваемому по цепи обратной связи, и по сигналу с входа 15 на выходе 23 элемента И 6 формируется сигнал шестого разряда выходного кода. По сигналу с выхода 23, передаваемому по цепи обратной связи, и по сигналу с входа 12 на выходе 18 элемента И 1 формируется сигнал первого разряда выходного кода. По сигналу с выхода 19, передаваемому по цепи обратной связи, и по сигналу с входа 17 на выходе 22 элемента И 5 формируется сигнал пятого разряда выходного кода. По сигналу с выхода 21, передаваемому по цепи обратной связи, и по сигналам с входа 12 и выхода 28 на выходе 20 элемента ИЛИ-НЕ 10 формируется сигнал третьего разряда выходного кода.

Для работы с преобразователем предполагается использование полупроводникового семисегментного индикатора с общим анодом.

Построение преобразователя обеспечило его упрощение за счет cокращения общего чиcла элементов c 17 до 11 (в 1,5 раза), чиcла cвязей - c 35 до 23 (в 1,5 раза) при cокращении в 2,3 раза параметра "чиcло элементов х чиcло cвязей", определяющего cложноcть преобразователя. При этом cледует учеcть, что для данного преобразователя доcтаточно иcпользование шеcти, а не воcьми входных cигналов.

Изобретение относится к автоматике и вычислительной технике и может быть использовано в контрольно-измерительных приборах с семисегментными индикаторами. Преобразователь содержит элементы И 1 - 6 и элементы ИЛИ 7 - 9. Благодаря введению элементов ИЛИ-НЕ 10, 11 и соответствующих связей достигается упрощением преобразователя по сравнению с прототипом в 2,3 раза по параметру "число элементов X число связей". 1 ил., 1 табл.

ПРЕОБРАЗОВАТЕЛЬ КОДА "2421" В ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД, содержащий шесть элементов И и три элемента ИЛИ, первый вход первого элемента И объединен с первым входом второго элемента И и является первым входом преобразователя, а выход является первым выходом преобразователя, выходы третьего, четвертого, пятого элементов И и выход первого элемента ИЛИ являются соответственно вторым, третьим, четвертым и пятым выходами преобразователя, второй вход второго элемента И является вторым входом преобразователя, а выход соединен с первым входом первого элемента ИЛИ, второй вход которого является третьим входом преобразователя, первые входы третьего и четвертого элементов И являются четвертым и пятым входами преобразователя соответственно, отличающийся тем, что в него введены два элемента ИЛИ - НЕ, первый и второй входы второго элемента ИЛИ соединены с первыми входами первого и четвертого элементов И соответственно, а выход соединен с первым входом пятого элемента И, первый вход третьего элемента ИЛИ соединен с первым входом первого элемента ИЛИ - НЕ и является третьим входом преобразователя, второй вход третьего элемента ИЛИ соединен с вторым входом первого элемента ИЛИ и является шестым входом преобразователя, а выход соединен с вторым входом пятого элемента И и первым входом шестого элемента И, второй вход которого соединен с вторым входом второго элемента И, а выход соединен с первым входом второго элемента ИЛИ - НЕ, второй вход которого подключен к первому входу второго элемента И, а выход соединен с вторым входом первого элемента ИЛИ - НЕ и является шестым выходом преобразователя, третий вход первого элемента ИЛИ - НЕ подключен к выходу второго элемента И, а выход является седьмым выходом преобразователя, выход четвертого элемента И соединен с вторым входом первого элемента И, выход первого элемента ИЛИ соединен с вторым входом четвертого элемента И, выход пятого элемента И соединен с вторым входом третьего элемента И.

| Справочник | |||

| Применение интегральных микросхем в электронной вычислительной технике /Под ред | |||

| В.В.Тарабрина | |||

| - М.: Радио и связь, 1987, рис.5.2. |

Авторы

Даты

1995-03-27—Публикация

1990-06-25—Подача