Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано в электроэнергетике для получения гистограммы отклонений напряжения с целью контроля (по ГОСТ 13109-67) качества электроэнергии в электрических сетях промышленных предприятий и энергосистем.

Известен анализатор гистограммы отклонений напряжения, содержащий аналого-цифровой преобразователь, регистр, блоки памяти, блок индикации, двоично-десятичный счетчик, генератор выборки, тактовый генератор, первый и второй распределители уровней, элементы НЕ, И-НЕ и И, первый и второй триггеры.

Недостатком аналога является невысокая надежность, обусловленная большим расходом элементов для его реализации.

Наиболее близким известным техническим решением к предлагаемому является статистический анализатор отклонений напряжения сети, содержащий преобразователь переменного напряжения в постоянное, аналого-цифровой преобразователь, двоичный счетчик, коммутатор, оперативное запоминающее устройство, двоично-десятичный счетчик, индикатор, генератор выборки, генератор тактовых импульсов, триггер, распределитель уровней, элементы И и ИЛИ, элемент установки в ноль, многопозиционный переключатель, шифратор из унитарного кода в двоичный, двухпозиционный переключатель режима.

Недостатком прототипа является невысокая надежность, обусловленная большим расходом элементов для его реализации, а также большим числом связей между элементами.

Цель изобретения повышение надежности анализатора.

Указанная цель достигается тем, что в статистический анализатор отклонений напряжения, содержащий преобразователь переменного напряжения в постоянное, вход которого является входом анализатора, а выход через аналого-цифровой преобразователь соединен с информационным входом первого двоичного счетчика, выход которого соединен с вторым информационным входом коммутатора, а тактовый вход подключен к выходу первого элемента И-НЕ, второй вход которого подключен к старшему разряду выхода второго двоичного счетчика, а первый вход соединен с входом установки нуля двоично-десятичного счетчика, через контакты кнопки с общей шиной анализатора и через резистор с шиной единичного потенциала анализатора, многопозиционный переключатель, через контакты которого общая шина анализатора соединена с входами шифратора из унитарного кода в двоичный, выход которого соединен с первым информационным входом коммутатора, управляющий вход которого через контакты переключателя режима соединен с общей шиной и с шиной единичного потенциала анализатора, генератор выборки, прямой выход которого соединен с объединенными входами установки нуля второго и третьего двоичных счетчиков, а инверсный выход соединен с входом записи первого двоичного счетчика и через второй элемент И-НЕ с входом записи первого D-триггера, инверсный выход которого соединен с входом записи второго D-триггера, информационный вход которого объединен с информационным входом первого D-триггера и подключен к шине единичного потенциала анализатора, а прямой выход через третий элемент И-НЕ соединен с тактовым входом двоично-десятичного счетчика, выход переноса которого соединен с первым входом второго элемента И-НЕ, генератор тактовых импульсов, выход которого соединен с тактовым входом второго двоичного счетчика, оперативное запоминающее устройство, блок индикации, дополнительно введены постоянное запоминающее устройство, универсальный регистр, первый и второй одновибраторы, а используемое в анализаторе оперативное запоминающее устройство имеет одноразрядную организацию памяти, причем выход второго одновибратора соединен с вторым входом третьего элемента И-НЕ, а прямой вход подключен к инверсному выходу первого одновибратора, связанному с входом установки нуля первого D-триггера и входом записи двоично-десятичного счетчика, информационный выход которого соединен с информационным входом блока индикации и с входом для занесения информации в параллельном коде универсального регистра, выход которого соединен с информационным входом двоично-десятичного счетчика.

Выход коммутатора соединен с первой группой старших разрядов адресного входа оперативного запоминающего устройства, вторая группа средних разрядов адресного входа которого подключена к выходу второго двоичного счетчика, связанного с управляющим входом блока индикации, а информационный выход оперативного запоминающего устройства соединен с входом для занесения информации в последовательном коде универсального регистра, старший разряд выхода которого соединен с информационным входом оперативного запоминающего устройства, третья группа младших разрядов адресного входа которого подключена соответственно к выходам третьего и четвертого разрядов третьего двоичного счетчика, выход пятого разряда которого соединен с тактовым входом второго двоичного счетчика, выходы третьего двоичного счетчика соединены с адресными входами постоянного запоминающего устройства, информационные выходы которого соответственно соединены первый с первым тактовым входом универсального регистра, второй с инверсным входом первого одновибратора, третий с управляющим входом универсального регистра, четвертый с входом записи блока индикации, вторым тактовым входом универсального регистра и входом установки нуля второго D-триггера, пятый с входом записи оперативного запоминающего устройства.

Блок индикации содержит дешифратор из двоичного кода в десятичный, вход которого подключен к управляющему входу блока индикации, а инверсные выходы соединены соответственно с первыми входами элементов ИЛИ-НЕ, вторые входы которых объединены и подключены к входу записи блока индикации, а выходы соответственно соединены с входом записи регистров, информационные входы которых объединены и подключены к информационному входу блока индикации, выход каждого регистра через шифратор из двоичного кода в код индикатора соединен с информационным входом индикатора.

Существенными отличиями предлагаемого изобретения являются использование новых элементов, а также новая организация структуры анализатора. Эти отличия обеспечивают достижение положительного эффекта повышение надежности анализатора.

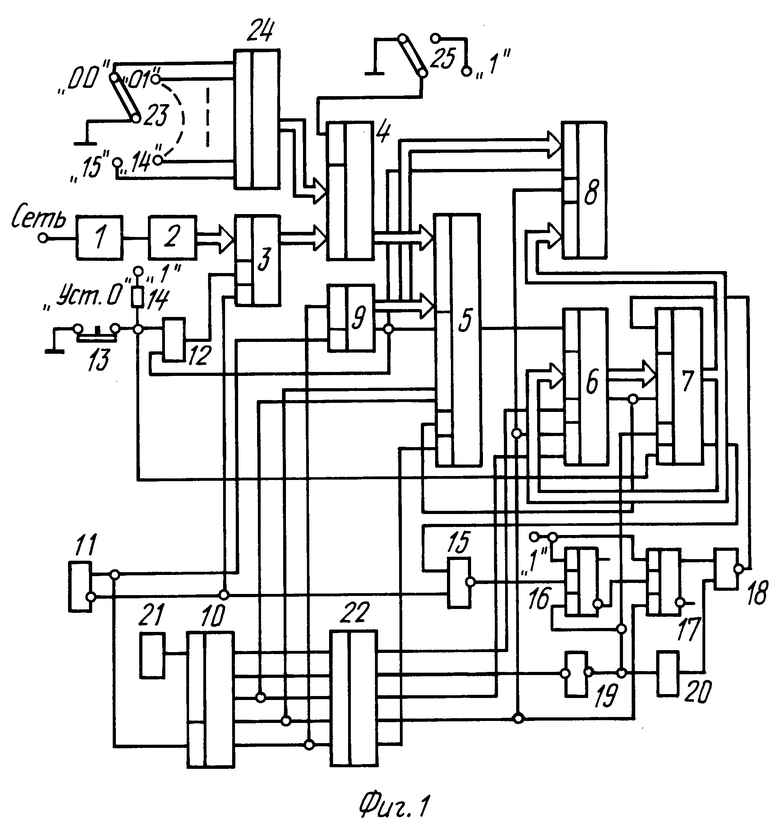

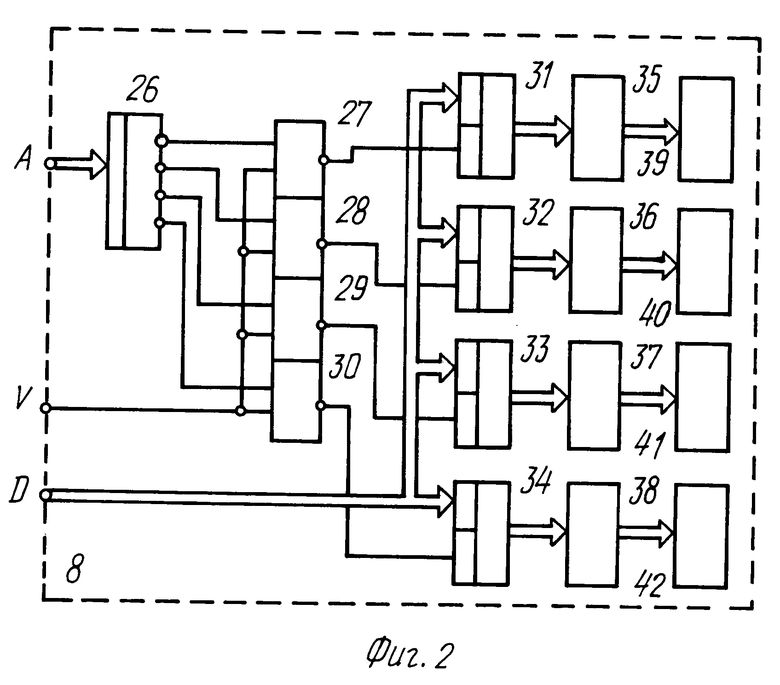

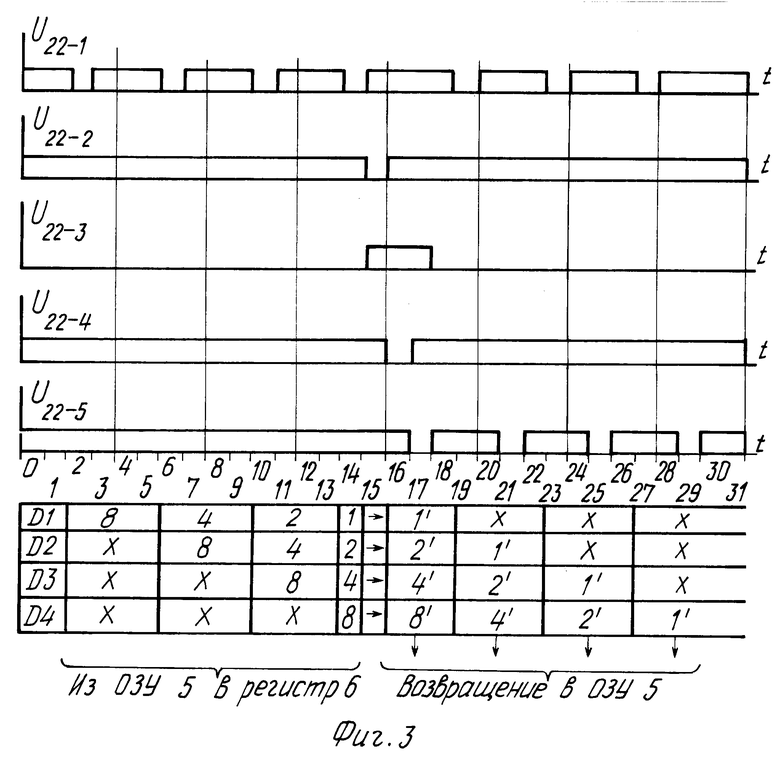

На фиг. 1 представлена структурная схема анализатора; на фиг. 2 схема блока индикации; на фиг. 3 графики изменения напряжений на выходах постоянного запоминающего устройства совместно с таблицей, иллюстрирующей процесс обращения к оперативному запоминающему устройству с помощью универсального регистра.

Анализатор содержит преобразователь 1 переменного напряжения в постоянное, вход котоpого является входом анализатора, а выход через аналого-цифровой преобразователь (АЦП) 2 соединен с информационным входом первого двоичного счетчика 3, выход которого соединен с вторым информационным входом коммутатора 4, выход которого соединен с первой группой старших разрядов адресного входа блока памяти оперативного запоминающего устройства (ОЗУ) 5, выход которого соединен с входом "ДО" для занесения информации в последовательном коде универсального регистра 6, выход которого соединен с информационным входом двоично-десятичного счетчика 7, информационный выход которого соединен с входом для занесения информации в параллельном коде универсального регистра 6 и с информационным входом "Д" блока 8 индикации, управляющий вход "А" которого объединен с второй группой средних разрядов адресного входа ОЗУ 5 и подключен к выходу второго двоичного счетчика 9, вход установки нуля которого объединен с входом установки нуля третьего двоичного счетчика 10 и подключен к прямому выходу генератора импульсов 11 выборки, старший разряд выхода второго двоичного счетчика 9 соединен с вторым входом первого элемента И-НЕ 12, выход которого соединен с тактовым входом первого двоичного счетчика 3, а первый вход соединен с входом установки нуля двоично-десятичного счетчика 7, через контакты кнопки 13 с общей шиной и через резистор 14 с шиной единичного потенциала анализатора, инверсный выход генератора 11 выборки соединен с входом записи первого двоичного счетчика 3 и через второй элемент И-НЕ 15 с входом записи первого D-триггера 16, инверсный выход которого соединен с входом записи второго D-триггера 17, информационный вход которого объединен с информационным входом первого D-триггера 16 и подключен к шине единичного потенциал анализатора, а прямой выход через третий элемент И-НЕ 18 соединен с тактовым входом двоично-десятичного счетчика 7, вход записи которого подключен к инверсному выходу первого одновибратора 19, связанному с входом установки нуля первого D-триггера 16 и через второй одновибратор 20 с вторым входом третьего элемента И-НЕ 18, выход генератора 21 тактовых импульсов соединен с тактовым входом третьего двоичного счетчика 10, выходы которого соединены с адресными входами постоянного запоминающего устройства (ПЗУ) 22, информационные выходы которого соответственно соединены первый с первым тактовым входом универсального регистра 6, второй с инверсным входом первого одновибратора 19, третий с управляющим входом универсального регистра 6, четвертый с входом записи "У" блока 8 индикации, вторым тактовым входом универсального регистра 6 и входом установки нуля второго D-триггера 17, пятый с входом записи ОЗУ 5, третья группа младших разрядов адресного входа которого подключена соответственно к выходам третьего и четвертого разрядов третьего двоичного счетчика 10, выход пятого разряда которого соединен с тактовым входом второго двоичного счетчика 9, старший разряд выхода универсального регистра 6 соединен с информационным входом ОЗУ 5, многопозиционный переключатель 23, через контакты которого общая шина анализатора соединена с входами шифратора 24 из унитарного кода в двоичный, выход которого соединен с первым информационным входом коммутатора 4, управляющий вход которого через контакты (двухпозиционного) переключателя 25 режима соединен с общей шиной и шиной единичного потенциала анализатора.

Блок 8 индикации содержит дешифратор 26 из двоичного кода в десятичный, вход которого подключен к управляющему входу "А" блока 8 индикации, а инверсные выходы соединены соответственно с первыми входами элементов ИЛИ-НЕ 27-30, вторые входы которых объединены и подключены к входу записи "У" блока 8 индикации, а выходы соединены соответственно с входами записи регистров 31-34, информационные входы которых объединены и подключены к информационному входу "Д" блока 8 индикации, а выходы каждого из них через шифраторы 35-38 из двоичного кода в код индикатора соединены соответственно с информационными входами индикаторов 39-42.

Анализатор выполнен многоканальным. Ширина младшего значащего разряда (МЗР) АЦП 2 равняется ширине разряда искомой гистограммы отклонений напряжения. В анализаторе используется АЦП 2 следящего типа, очередное изменение кода на выходе которого происходит после изменения его входного напряжения на ширину МЗР.

Коду числа на выходе АЦП 2 соответствует номер разряда измеряемой гистограммы: коду 0000 нулевой разряд гистограммы, коду 0001 второй разряд и т.д.

При опросе каналов анализатора номера разрядов гистограммы соответственно задаются положением контактов многопозиционного переключателя 23: "00", "01" и т.д.

В качестве примера рассмотрим 16-канальный анализатор, емкость каждого канала которого составляет 104; в этом случае первая старшая группа разрядов адресного входа ОЗУ 5 содержит четыре двоичных разряда, вторая средняя группа два разряда и третья младшая группа два разряда. При необходимости указанные параметры анализатора могут быть выбраны другими (кроме числа разрядов третьей группы, которое всегда равняется двум).

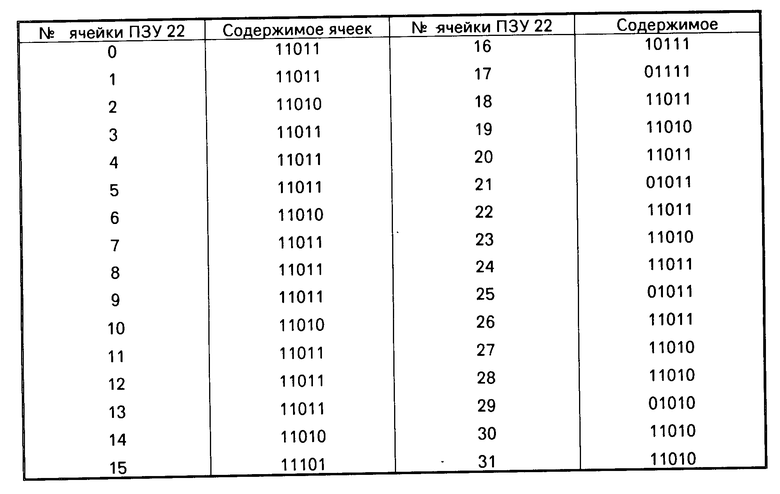

Процессом накопления информации в ОЗУ 5 анализатора управляет ПЗУ 22, содержимое которого представлено в таблице.

Анализатор работает следующим образом.

Для проведения измерений переключатель 25 устанавливается в положение "Измерение". В этом случае к управляющему входу коммутатора 4 прикладывается единичный потенциал и в результате на выходе коммутатора 4 появляется код, приложенный к его второму информационному входу с выхода первого двоичного счетчика 3.

Перед началом измерений нажатием на кнопку 13 обнуляется содержимое ОЗУ 5. Осуществляется это следующим образом. Единичный потенциал через кнопку 13 прикладывается к входу установки нуля двоично-десятичного счетчика 7. Появляющийся при этом на информационном выходе последнего нулевой код вписывается в регистр 6, нулевой четвертый разряд его выхода прикладывается к информационному входу ОЗУ 5. Единичный потенциал появляется также на первом входе элемента И-НЕ 12, выход которого связан с тактовым входом первого двоичного счетчика 3. Таким образом, при нажатой кнопке 13, во-первых, к информационному входу ОЗУ 5 приложен нулевой потенциал и, во-вторых, с высокой частотой начинают изменяться все разряды адресного входа ОЗУ 5 в результате в течение нескольких мс во все ячейки ОЗУ 5 вписываются нули.

После отпускания кнопки 13 начинается процесс накопления информации.

Генератором 11 вырабатываются узкие (длительностью в 1 мкс) импульсы выборки случайного процесса изменения отклонений напряжения.

Генератором 21 задается тактовая частота устройства, которая на несколько порядков превышает частоту генератора 11; например, генератор 11 работает с частотой 1 Гц, генератор 21 работает с частотой 1 МГц. Импульсы генератора 21 поступают на тактовый вход счетчика 10, изменяя последовательно его выходной код. Поскольку код на адресных входах ПЗУ 22 последовательно изменяется, то на его выходах также последовательно появляется информация, заложенная в ячейках ПЗУ 22. Графически этот процесс показан на фиг. 3, на которой вдоль оси абсцисс графика U22-5(t) указаны номера тактов генератора 21, начиная с нулевого кода счетчика 10.

В момент очередной выборки импульсом с инверсного выхода генератора 11 код из АЦП 2 (соответствующий уровню анализа отклонений напряжения в момент выборки, например, 0011) переписывается в счетчик 3 и вписывается единица в первый D-триггер 16, а импульсом с прямого выхода генератора 11 обнуляются счетчики 9 и 10. В результате на информационном выходе ОЗУ 5, связанном с входом D0 для занесения информации в последовательном коде универсального регистра 6, в нулевом такте генератора 21 появляется бит старшего двоичного разряда "8" младшего десятичного разряда (в дальнейшем декады) информации, накопленной в результате предыдущего анализа и хранящейся в ячейках ОЗУ 5 с адресами 00110000-00111111.

Во 2-м такте генератора 21 отрицательным импульсом с первого выхода ПЗУ 22 (U22-1 на фиг. 3) значение разряда "8" заносится в ячейку памяти D1 младшего разряда универсального регистра 6.

В 4-м такте генератора 21 код на адресном входе ОЗУ 5 становится равным 00110001 хранящийся в ячейке с этим адресом бит "4" обрабатываемой информации (соответствующей разряду гистограммы с номером 0011) прикладывается к входу D0 универсального регистра 6.

В 6-м такте генератора 21 в ячейку D1 универсального регистра 6 вписывается значение "4", а хранящийся перед этим в ячейке D1 бит "8" передвигается в ячейку D2 (таблица на фиг. 3).

Аналогичная операция повторяется в 10-м и 14-м тактах, в результате чего биты "2" и "1" информации, хранящейся соответственно в ячейках ОЗУ 5 с адресами 00110010 и 00110011, также последовательно вписываются в ячейки регистра 6. В итоге в начале 14-го такта на выходах D1-D4 регистра 6 появляется в коде 1-2-4-8 значение младшей декады информации, накапливаемой анализатором для построения разряда гистограммы с номером 0011.

В начале 15-го такта импульсом со 2-го выхода ПЗУ 22 (см. фиг. 3) запускается первый одновибратор 19, который своим выходным импульсом переписывает содержимое регистра 6 в счетчик 7, а также переводит из единичного в нулевое состояние первый D-триггер 16. По положительному перепаду напряжения на инверсном выходе триггера 16 во второй D-триггер 17 вписывается единица единичное напряжение его прямого выхода прикладывается к первому входу элемента И-НЕ 18.

Заканчиваясь, выходной импульс одновибратора 19 запускает одновибратор 20, импульс выхода которого, проходя через элемент И-НЕ 18, увеличивает на единицу содержимое двоично-десятичного счетчика 7. Если при этом значение декады становится равным 10, то на выходе переноса счетчика 7 появляется отрицательный импульс напряжения, который, проходя через элемент И-НЕ 15, вновь переводит D-триггер 16 в единичное состояние.

Поскольку длительность выходных импульсов одновибратора 19 и 20 мала (примерно 0,3-0,4 мкс), то процесс увеличения значения декады заканчивается в течение 15-го такта генератора 21. Новые значения двоичных разрядов декады обозначены в таблице на фиг. 3, как "11", "21", "31", "41".

В 16-м такте эта информация переписывается отрицательным импульсом с 4-го выхода ПЗУ 22 из счетчика 7 в регистр 31 блока 8 индикации, а также в универсальный регистр 6. Для возможности занесения в регистр 6 информации в параллельном коде к его управляющему входу в течение 15-17 тактов приложено единичное напряжение.

В 17-м также бит "81", приложенный с выхода D4 универсального регистра 6 к информационному входу ОЗУ 5, записывается в ячейку ОЗУ 5 с адресом 00110000 из этой же ячейки во 2-м такте был перенесен в регистр 6 бит "8".

В 19-м такте отрицательным импульсом с 1-го выхода ПЗУ 22 осуществляется сдвиг информации внутри универсального регистра 6 (таблица на фиг. 3), в результате на выходе D4 регистра 6 появляется бит "41", который в 21-м такте записывается в ячейку ОЗУ 5 с адресом 00110001.

Аналогично в 25-м и 29-м тактах возвращаются обновленные значения битов "21" и "11" соответственно в ячейки с адресами 00110010 и 00110011.

После прохождения полного цикла работы счетчика 10, состоящего из 32 тактов, на единицу увеличивается содержимое счетчика 9, которое в рассматриваемом примере становится равным 01.

Следующие 32 такта генератора 21 по описанному выше алгоритму осуществляется обработка (и, если был сигнал переноса при обработке предыдущей декады, то увеличение на единицу) двоичных разрядов следующей декады информации, хранящейся в ячейках ОЗУ 5 с адресами 00110100-00110111. При этом в 16-м такте информация вписывается в регистр 32 блока 8 индикации и т.д. до полного обновления всех четырех декад.

После обновления всего 4-декадного числа до следующей выборки описанный выше циклический процесс непрерывно продолжается, однако при этом информация считывается из ОЗУ 5 и затем возвращается назад без изменений.

После накопления достаточно большого объема информации переключатель 25 режима переводится в состояние "Опрос". При этом к управляющему входу коммутатора 4 прикладывается нулевой потенциал в результате на выходе коммутатора появляется код, приложенный к его первому информационному входу с выхода шифратора 24. В этом режиме осуществляется опрос содержимого ОЗУ 5. Для этого многопозиционный переключатель 23 поочередно переводится в положения "00", "01", "02", "03" и т.д. На выходе шифратора 24 при этом появляются соответственно коды "0000", "0001", "0010", "0011" и т.д. которые через коммутатор 4 прикладываются к первой группе старших разрядов адресного входа ОЗУ 5 на индикаторах 39-42 появляются статистики, накопленные в каналах блока памяти анализатора с номерами 1-4 и т.д. которые используются для построения соответствующих разрядов гистограммы отклонений напряжения, используемой для оценки качества электроэнергии контролируемой сети по ГОСТ 13109-67.

Преимуществами предлагаемого анализатора по сравнению с известными являются большая экономичность и надежность схемы, меньшая стоимость и потребляемая мощность элементов, обусловленные уменьшением числа необходимых элементов и связей между ними. В настоящее время анализатор изготовлен на интегральных микросхемах. Для доведения предлагаемого изобретения до промышленного использования требуется 1 год.

Изобретение относится к информационно-измерительной технике и может быть использовано в электроэнергетике для получения гистограммы отклонений напряжения. Цель изобретения повышение надежности анализатора за счет упрощения его реализации. Анализатор содержит шифратор, коммутатор, счетчики, переключатели, распределитель импульсов, блок памяти, ключ, генератор тактовых импульсов, генератор импульсов выборки, триггеры, блок индикации, элементы И-НЕ, аналого-цифровой преобразователь, преобразователь переменного напряжения в постоянное, одновибраторы и регистр. 1 з.п. ф-лы, 3 ил. 1 табл.

| Статистический анализатор отклонений напряжения сети | 1985 |

|

SU1262524A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-08-09—Публикация

1992-01-04—Подача