Изобретение относится к области информационно-измерительной и вычислительной техники и может быть использовано в электроэнергетике для получения гистограммы отклонений напряжения с целью контроля по ГОСТ 13109-87 качества электроэнергии в электрических сетях промышленных предприятий и энергосистем.

Наиболее близким к изобретению является статистический анализатор отклонений напряжения сети, содержащий преобразователь переменного напряжения в постоянное, аналого-цифровой преобразователь, двоичный счетчик, коммутатор, оперативное запоминающее устройство, двоично-десятичный счетчик, индикатор, генератор выборки, генератор тактовых импульсов, триггер, распределитель уровней, элементы И и ИЛИ, элемент установки в ноль, многопозиционный переключатель, шифратор из унитарного кода в двоичный, двухпозиционный переключатель режима работы.

Недостатком прототипа является недостаточно высокая надежность работы анализатора, которая проявляется при переводе его в режим опроса, при этом появляется возможность искажения накопленной в блоке памяти информации; в том случае, если момент перевода совпал с моментом выборки случайного процесса отклонений напряжения, в двух каналах оказывается одинаковая информация.

Техническая задача изобретения повышение надежности работы анализатора за счет исключения возможности искажения информации, накопленной в блоке памяти анализатора.

Техническая задача решается благодаря тому, что в статистический анализатор отклонений напряжения сети, содержащий шифратор, коммутатор, первый и второй счетчики, двухпозиционный и многопозиционный переключатели, блок памяти, ключ, генератор тактовых импульсов, генератор импульсов выборки, первый триггер, блок индикации, аналого-цифровой преобразователь и преобразователь переменного напряжения в постоянное, вход которого является информационным входом анализатора, а выход соединен с информационным входом аналого-цифрового преобразователя, шина нулевого потенциала соединена с первым выводом ключа и через многопозиционный переключатель соединена со входами шифратора, выход которого соединен с первым информационным входом коммутатора, управляющий вход которого через двухпозиционный переключатель соединен с шинами нулевого и единичного потенциала, выход блока памяти подключен к информационному входу блока индикации и к информационному входу первого счетчика, информационный выход которого соединен с информационным входом блока памяти, второй вывод ключа соединен со входом обнуления первого счетчика, введены токозадающий резистор, два счетчика, дешифратор, три элемента И-НЕ, элемент НЕ и второй триггер, второй вывод ключа соединен с первым входом первого элемента И-НЕ и через токозадающий резистор с шиной единичного потенциала, выход первого элемента И-НЕ соединен с тактовым входом второго счетчика, вход записи которого соединен с первым входом второго элемента И-НЕ и подключен к инверсному выходу генератора импульсов выборки, прямой выход которого соединен со входами обнуления третьего и четвертого счетчиков, тактовые входы которых подключены соответственно к выходу генератора тактовых импульсов и к выходу старшего разряда третьего счетчика, младшие разряды адресного входа блока памяти соединены со входом выбора канала блока индикации и подключены к выходу четвертого счетчика, выход старшего разряда которого соединен со вторым входом первого элемента И-НЕ, выход второго элемента И-НЕ соединен со входом записи первого триггера, инверсный выход которого соединен со входом записи второго триггера, прямой выход которого соединен с первым входом третьего элемента И-НЕ, выход которого соединен с тактовым входом первого счетчика, выход переноса которого соединен со вторым входом второго элемента И-НЕ, информационные входы первого и второго триггеров подключены к шине единичного потенциала, выходы третьего счетчика подключены ко входам дешифратор а, первый инверсный выход которого соединен со входом установки в ноль первого триггера и входами управления записью блока индикации и первого счетчика, второй инверсный выход дешифратора через элемент НЕ соединен со вторым входом третьего элемента И-НЕ, третий инверсный выход дешифратора соединен со входом установки в ноль второго триггера и входом управления записью блока памяти, старшие разряды адресного входа которого подключены к выходу второго счетчика, информационный вход которого подключен к выходу коммутатора, второй информационный вход которого подключен к выходу аналого-цифрового преобразователя, а управляющий вход соединен с третьим входом третьего элемента И-НЕ.

Существенными отличиями предлагаемого изобретения являются использование новых элементов (дешифратора, двух счетчиков, второго триггера, трех элементов И-НЕ и элемента НЕ), а также новая организация структуры анализатора (в частности, наиболее существенно в этом плане то, что первый счетчик, включенный в прототипе между аналого-цифровым преобразователем и коммутатором, в предлагаемом анализаторе введен между коммутатором и блоком памяти). Именно эти существенные отличия обеспечивают достижение положительного эффекта - повышение надежности работы за счет исключения возможности искажения накопленной статистической информации в режиме опроса блока памяти анализатора.

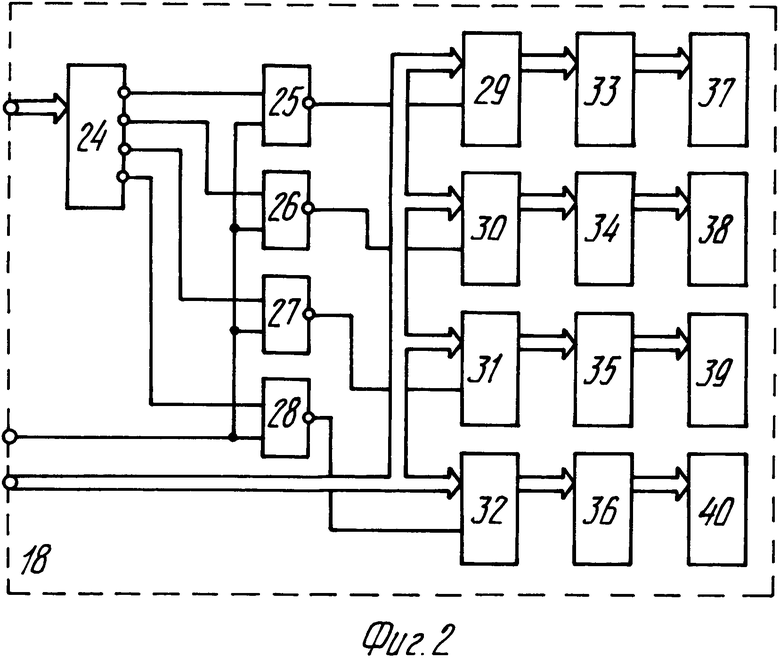

На фиг. 1 представлена структурная схема анализатора); на фиг.2 схема блока индикации.

Анализатор содержит преобразователь 1 переменного напряжения в постоянное, вход которого является входом анализатора, а выход через аналого-цифровой преобразователь (АЦП) 2 соединен с вторым информационным входом коммутатора 3, управляющий вход которого через двухпозиционный переключатель 4 соединен с шинами нулевого и единичного потенциала, шина нулевого потенциала через многопозиционный переключатель 5 соединена со входами шифратора 6, выход которого соединен с первым информационным входом коммутатора 3, шина нулевого потенциала через ключ 7 соединена с первым входом первого элемента И-НЕ 8, связанным со входом обнуления первого счетчика 9 и через токозадающий резистор 10 с шиной единичного потенциала, выход первого элемента И-НЕ 8 соединен с тактовым входом второго счетчика 11, вход записи которого объединен с первым входом второго элемента И-НЕ 12 и подключен к инверсному выходу генератора 13 импульсов выборки, прямой выход которого соединен со входами обнуления третьего 14 и четвертого 15 счетчиков, тактовые входы которых подключены соответственно к выходу генератора 16 тактовых импульсов (ГТИ) и к выходу старшего разряда третьего счетчика 14, младшие разряды адресного входа блока 17 памяти (БП) соединены со входом выбора канала блока 18 индикации (БИ) и подключены к выходу четвертого счетчика 15, выход старшего разряда которого соединен со вторым входом первого элемента И-НЕ 8, выход второго элемента И-НЕ 12 соединен со входом записи первого триггера 19, инверсный выход которого соединен со входом записи второго триггера 20, прямой выход которого соединен с первым входом третьего элемента И-НЕ 21, выход которого соединен с тактовым входом первого счетчика 9, информационный выход которого соединен с информационным входом БП 17, информационный выход которого соединен с информационными входами БИ 18 и первого счетчика 9, выход переноса которого соединен со вторым входом второго элемента И-НЕ 12, информационные входы первого 19 и второго 20 триггеров подключены к шине единичного потенциала, выход коммутатора 3 соединен с информационным входом второго счетчика 11, выход которого соединен со старшими разрядами адресного входа БП 17, выход третьего счетчика 14 соединен с информационным входом дешифратора 22, инверсные выходы которого соединены соответственно первый со входом установки в ноль первого триггера 19 и входами управления записью БИ 18 и первого счетчика 9, второй через элемент НЕ 23 со вторым входом третьего элемента И-НЕ 21, третий со входом управления записью БП 17 и входом установки в ноль второго триггера 20, управляющий вход коммутатора 3 соединен с третьим входом третьего элемента И-НЕ 21.

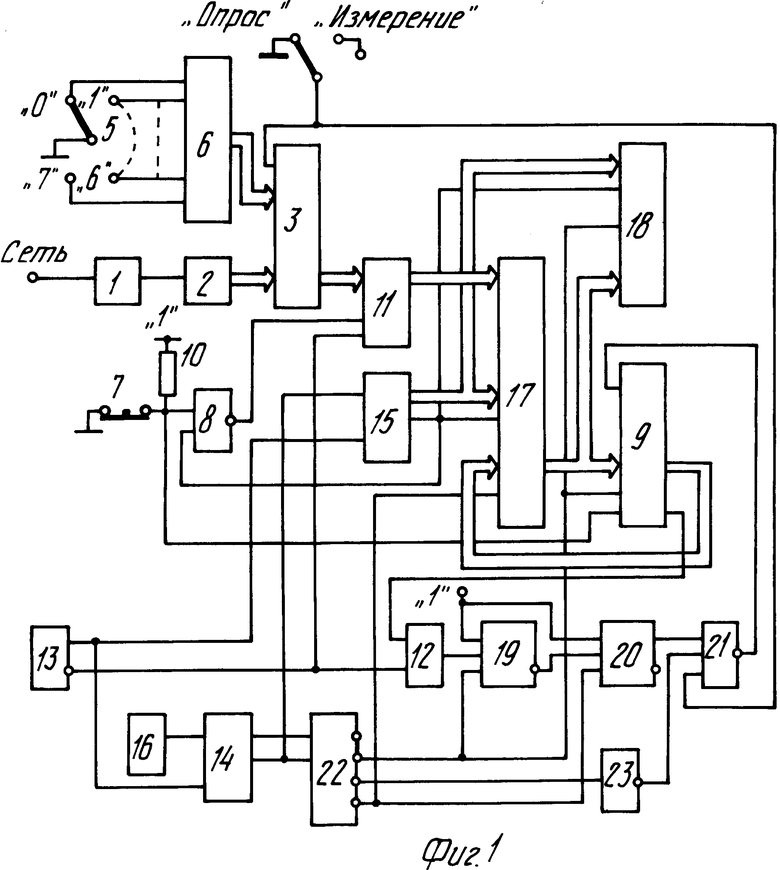

Блок 18 индикации (фиг. 2) содержит дешифратор 24 из двоичного кода в унитарный позиционный код, вход которого является входом выбора канала БИ 18, а выходы соединены с первыми входами элементов ИЛИ-НЕ 25 28, вторые входы которых подключены ко входу управления записью БИ 18, информационный вход которого соединен с информационными входами регистров 29 32, синхровходы которых подключены к выходам соответствующих элементов ИЛИ-НЕ 25 28, выходы регистров 29 32 через шифраторы 33 -36 соединены со входами соответствующих индикаторов 37 40.

Анализатор выполнен многоканальным. Ширина младшего значащего разряда (МЗР) АЦП 2 равняется ширине разряда искомой гистограммы отклонений напряжения. В анализаторе используется АЦП 2 следящего типа, очередное изменение кода на выходе которого происходит после изменения входного напряжения на ширину МЗР.

Коду числа на выходе АЦП 2 соответствует номер разряда измеряемой гистограммы: коду 000 нулевой разряд гистограммы, коду 001 первый разряд и т. д.

При опросе каналов анализатора номера разрядов гистограммы соответственно задаются положением контактов многопозиционного переключателя 5: "0", "1" и т. д.

В качестве примера рассмотрим 8-канальный анализатор, емкость каждого канала которого составляет 104; в этом случае группа старших разрядов адресного входа БП 17 содержит 3 двоичных разряда, а группа младших разрядов - 2 разряда. При необходимости указанные параметры анализатора могут быть выбраны другими (большими).

Генератор 16 работает с высокой нестабильной частотой 0,1 2 МГц. Низкая частота генератора 13 (например, 1 Гц) должна быть стабильной, в частности, генератор 13 может быть выполнен кварцевым. Генератором 13 вырабатываются узкие (длительностью в 1 мкс) импульсы выборки случайного процесса изменения отклонений напряжения.

Анализатор работает следующим образом.

Для проведения измерений переключатель 4 устанавливается в положение "Измерение", при котором к управляющему входу коммутатора 3 прикладывается единичный потенциал. В этом случае на выход коммутатора 3 пропускается код, приложенный ко второму информационному входу коммутатора с выхода АЦП 2.

Перед началом измерений нажатием на ключ 7 обнуляется БП 17. Осуществляется это следующим образом. Единичный потенциал через резистор 10 прикладывается ко входу установки нуля первого счетчика 9, который выполнен двоично-десятичным. Появляющийся при этом на информационном выходе счетчика 9 нулевой код последовательно вписывается во все ячейки БП 17. Быстрая смена кода адресов ячеек БП 17 обеспечивается благодаря тому, что после нажатия на ключ 7 к первому входу элемента И-НЕ 8 прикладывается единичный потенциал в результате элемент И-НЕ 8 начинает пропускать на тактовый вход счетчика 11 импульсы с выхода старшего разряда счетчика 15. Благодаря высокой частоте ГТИ 16 обнуление БП 17 осуществляется за несколько миллисекунд.

После отпускания ключа 7 начинается процесс накопления информации в БП 17.

Во время очередной выборки импульсом с инверсного выхода генератора 13 код из АЦП 2 (соответствующий уровню анализа отклонений напряжения в момент выборки, например, 011) переписывается в счетчик 11, а также вписывается единица в первый триггер 19, а импульсом с прямого выхода генератора 13 обнуляются счетчики 14 и 15. В результате на информационном выходе БП 17 появляется значение младшего десятичного разряда (в дальнейшем декады) информации, накопленной в результате предыдущего анализа и хранящейся в ячейках БП 17 с адресами 01100 01111; в частности, в первом такте генератора 16 на выходе БП 17 появляется значение младшей декады, хранящейся в ячейке с адресом 01100. Поскольку в момент выборки ко входу дешифратора 22 с выхода счетчика 14 приложен нулевой код, то управляющее напряжение присутствует на нулевом выходе дешифратора 22, который остается свободным.

Следует также учитывать, что выходной нулевой код счетчика 15 в момент выборки обеспечивает наличие управляющего нулевого напряжения на нулевом выходе дешифратора 24 БИ 18 в результате подготовленным к записи информации оказывается нулевой канал БИ 18, содержащий элементы 25, 29, 33, 37.

В следующем такте генератора 16 выходной код счетчика 14 становится равным 01, что приводит к появлению управляющего отрицательного импульса на первом выходе дешифратора 22. При этом осуществляются следующие операции: 1) переходит в нулевое состояние триггер 19, который перепадом напряжения на инверсном выходе вписывает единицу в триггер 20; 2) значение младшей декады информации с выхода БП 17 вписывается в счетчик 9; 3) значение младшей декады информации с выхода БП 17 вписывается в регистр 29 БИ 18.

В следующем такте генератора 16 появляющийся на втором выходе дешифратора 22 отрицательный импульс, проходя последовательно через элементы 23 и 21, увеличивает на единицу значение младшей декады информации. Если при этом значение декады становится равным 10, то на выходе переноса счетчика 9 появляется отрицательный импульс напряжения, который, проходя через И-НЕ 12, вновь переводит триггер 19 в единичное состояние.

Появляющийся в следующем такте генератора 16 на третьем выходе дешифратора 22 импульс возвращает в БП 17 увеличенное на единицу значение декады, а также в исходное нулевое состояние триггер 20.

В следующем такте генератора 16 код счетчика 14 снова становится нулевым управляющее нулевое напряжение появляется на свободном нулевом выходе дешифратора 22. По заднему фронту напряжения с выхода старшего разряда счетчика 14 срабатывает счетчик 15, содержимое которого становится равным 01. При этом на выходе БП 17 появляется значение второй декады накопленной ранее информации, а в БИ 18 подготовленным к записи информации оказывается первый канал, содержащий элементы 26, 30, 34 и 38.

Следующие 3 такта генератора 16 по описанному выше алгоритму осуществляется обработка второй декады информации, хранящейся в ячейке БП 17 с адресом 01101. При этом значение декады вписывается в регистр 30 БИ 18, и т. д. до полного обновления всех четырех декад.

После обновления всего 4-декадного числа до следующей выборки описанный выше циклический процесс непрерывно продолжается, однако при этом информация считывается из БП 17 и затем возвращается назад без изменений.

После накопления достаточно большого объема информации переключатель 4 переводится в состояние "Опрос", при этом к управляющему входу коммутатора 3 и третьему входу элемента И-НЕ 21 прикладывается нулевой потенциал. Это блокирует элемент И-НЕ 21 для прохождения импульсов с третьего выхода дешифратора 22 в результате накопления информации в анализаторе в режиме опроса не происходит. На выходе коммутатора 3 появляется код, приложенный к его первому информационному входу с выхода шифратора 6. В этом режиме осуществляется опрос содержимого БП 17. Для этого многопозиционный переключатель 6 поочередно переводится в положения "0", "1", "2" и т. д. На выходе шифратора 6 появляются соответствующие коды "000", "001", "010" и т. д. которые через коммутатор 3 прикладываются к группе старших разрядов адресного входа БП 17 на индикаторах 37 40 появляются статистики, накопленные в каналах блока памяти анализатора с номерами 0, 1, 2 и т. д. которые используются для построения соответствующих разрядов гистограммы отклонений напряжения, используемой для оценки качества электроэнергии сети по ГОСТ 13109-87.

Преимуществом анализатора по сравнению с известными является повышение надежности работы за счет исключения возможности искажения накопленной статистической информации в режиме опроса блока памяти анализатора.

Изобретение относится к информационно-измерительной и вычислительной технике и может быть использовано в электроэнергетике для получения гистограммы отклонений напряжения с целью, повышения точности и надежности работы. Анализатор содержит преобразователь 1 переменного напряжения в постоянное, аналого-цифровой преобразователь 2, коммутатор 3, двухпозиционный 4 и многопозиционный 5 переключатели, шифратор 6, ключ 7, первый 8, второй 12 и третий 21 элементы И - НЕ, первый 9, второй 11, третий 14 и четвертый 15 счетчики, генератор 13 импульсов выборки, генератор 16 тактовых импульсов, блок 17 памяти, блок 18 индикации, первый 19 и второй 20 триггеры, дешифратор 22, элемент НЕ 23. Преимуществом предлагаемого анализатора по сравнению с известными является повышение надежности работы за счет исключения возможности искажения накопленной статистической информации в режиме опроса блока памяти анализатора. 2 ил.

Анализатор отклонений напряжения, содержащий шифратор, коммутатор, первый и второй счетчики, двухпозиционный и многопозиционный переключатели, блок памяти, ключ, генератор тактовых импульсов, генератор импульсов выборки, первый триггер, блок индикации, аналого-цифровой преобразователь и преобразователь переменного напряжения в постоянное, вход которого является информационным входом анализатора, а выход соединен с информационным входом аналого-цифрового преобразователя, шина нулевого потенциала соединена с первым выводом ключа и через многопозиционный переключатель соединена с входами шифратора, выход которого соединен с первым информационным входом коммутатора, управляющий вход которого через двухпозиционный переключатель соединен с шинами нулевого и единичного потенциала, выход блока памяти подключен к информационному входу блока индикации и информационному входу первого счетчика, информационный выход которого соединен с информационным входом блока памяти, второй вывод ключа соединен с входом обнуления первого счетчика, отличающийся тем, что в него введены токозадающий резистор, два счетчика, дешифратор, три элемента И-НЕ, элемент НЕ и второй триггер, второй вывод ключа соединен с первым входом первого элемента И-НЕ и через токозадающий резистор с шиной единичного потенциала, выход первого элемента И-НЕ соединен с тактовым входом второго счетчика, вход записи которого соединен с первым входом второго элемента И-НЕ и подключен к инверсному выходу генератора импульсов выборки, прямой выход которого соединен с входами обнуления третьего и четвертого счетчиков, тактовые входы которых подключены соответственно к выходу генератора тактовых импульсов и выходу старшего разряда третьего счетчика, младшие разряды адресного входа блока памяти соединены с входом выбора канала блока индикации и подключены к выходу четвертого счетчика, выход старшего разряда которого соединен с вторым входом первого элемента И-НЕ, выход второго элемента И-НЕ соединен с входом записи первого триггера, инверсный выход которого соединен с входом записи второго триггера, прямой выход которого соединен с первым входом третьего элемента И-НЕ, выход которого соединен с тактовым входом первого счетчика, выход переноса которого соединен с вторым входом второго элемента И-НЕ, информационные входы первого и второго триггеров подключены к шине единичного потенциала, выходы третьего счетчика подключены к входам дешифратора, первый инверсный выход которого соединен с входом установки в ноль первого триггера и входами управления записью блока индикации и первого счетчика, второй инверсный выход дешифратора через элемент НЕ соединен с вторым входом третьего элемента И-НЕ, третий инверсный выход дешифратора соединен с входом установки в ноль второго триггера и входом управления записью блока памяти, старшие разряды адресного входа которого подключены к выходу второго счетчика, информационный вход которого подключен к выходу коммутатора, второй информационный вход которого подключен к выходу аналого-цифрового преобразователя, а управляющий вход соединен с третьим входом третьего элемента И-НЕ.

| SU, авторское свидетельство, 1262524, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1998-02-27—Публикация

1995-06-16—Подача