Изобретение относится к автоматике и вычислительной технике и может быть использовано для считывания и предварительной обработки изображений.

Известно устройство для считывания изображения [1] содержащее телевизионный датчик, выход которого подключен к входу видеоусилителя, один из выходов которого соединен с входом блока видеоконтроля, первый, второй и третий счетчики, генератор импульсов, выход которого подключен к одному из входов элемента И, выход которого соединен с импульсным входом второго счетчика, блок приема и передачи информации и блок синхронизации и управления, выходы которого подключены к управляющим входам первого и третьего счетчиков, блоки выделения границ по координатам Х и Y, цифроаналоговый преобразователь и последовательно включенные селектор видеосигнала, амплитудный дискриминатор и сдвиговый регистр, информационный выход которого подключен к информационному входу блока приема и передачи информации, информационные выходы которого соединены с соответствующими входами цифроаналогового преобразователя, первого и второго счетчиков и блоков выделения границ по координатам Х и Y, а управляющий выход подключен к одному из входов блока синхронизации и управления, другие входы которого соединены с выходами селектора видеосигнала, выход которого подключен к управляющим входам блоков выделения границ по координатам Х и Y, причем выход первого счетчика соединен с соответствующим входом блока выделения границ по координате Y, выход которого подключен к другому входу элемента И, вход второго счетчика соединен с соответствующим входом блока выделения границ по координате Х, выход которого подключен к соответствующим входам сдвигового регистра и третьего счетчика, выход которого соединен с одним из входов блока приема и передачи.

Недостатком данного устройства является снижение эффективности использования устройства при считывании относительно большого числа сечений одного и того же объекта.

Наиболее близким к заявляемому является устройство для считывания изображений [2] содержащее телевизионный датчик, видеоусилитель, блок синхронизации, счетчики, блоки выделения границ по координатам Х и Y, генератор импульсов, элемент И, блок приема и передачи информации.

Целью предлагаемого изобретения является расширение области применения устройства путем увеличения скорости считывания и передачи информации и соответственно устранения отмеченного недостатка.

Поставленная цель достигается тем, что в устройство, содержащее телевизионный датчик, выход которого подключен к входу видеоусилителя, один из выходов которого соединен с входом блока видеоконтроля, первый, второй и третий счетчики, генератор импульсов, выход которого подключен к одному из входов элемента И, выход которого соединен импульсным входом второго счетчика, блок приема и передачи информации и блок синхронизации и управления, выходы которого подключены к управляющим входам первого и третьего счетчиков, блока выделения границ по координатам Х и Y, селектор видеосигнала, блока приема и передачи информации, информационные выходы которого соединены с соответствующими входами первого и второго счетчиков и блоков выделения границ по координатам Х и Y, а управляющий выход подключен к одному из входов блока синхронизации и управления, другие входы которого соединены с выходами селектора видеосигнала, выход которого подключен к управляющим входам блоков выделения границ по координатам Х и Y, причем выход первого счетчика соединен с соответствующим входом блока выделения границ по координате Y, выход которого подключен к другому входу элемента И, вход второго счетчика соединен с соответствующим входом блока выделения границ по координате Х, выход которого подключен к входу третьего счетчика, выход которого соединен с одним из входов блока приема и передачи, дополнительно введены блок амплитудных компараторов, блок выбора уровней, преобразователь позиционного кода в двоичный, первый и второй регистры хранения информации, блок сравнения, блок формирования машинного и управляющего слов, буферный блок памяти границ, причем информационные входы амплитудных компараторов соединены с выходом селектора видеосигнала, а вторые входы амплитудных компараторов соединены с соответствующими выходами блока выбора уровней, входы которого соединены с информационными выходами блока приема и передачи, информационные входы первого и второго регистров хранения соединены шиной данных с выходами преобразователя позиционного кода в двоичный, входы которого соединены с выходами блока амплитудных компараторов, причем выходы первого регистра хранения соединены с первой группой входов схемы сравнения кодов и входами буферного блока памяти границ, а выходы второго регистра хранения соединены со второй группой входов схемы сравнения кодов, выход которой соединен с соответствующими информационным входом блока формирования машинного и управляющего слов и входом разрешения записи буферного блока памяти границ, другой информационный вход блока формирования машинного и управляющего слов преобразователя позиционного кода в двоичный соединен с выходом, адресные входы и информационные выходы блока формирования машинного и управляющего слов буферного блока памяти границ соединены общей шиной с вводами блока приема и передачи, входы управления которого соответственно соединены с выходом генератора импульсов и блока выделения границ по координате Х, причем блок формирования машинного и управляющего слов содержит первую и вторую пары регистров сдвига и две секции оперативного запоминающего устройства ОЗУ со схемами обрамления, информационные входы пар регистров сдвига соединены соответственно с выходами преобразователя позиционного кода в двоичный код и схемы сравнения кодов, информационные входы секций ОЗУ соединены шинами данных с выходами соответствующих пар регистров сдвига, а входы управления пар регистров сдвига и секций ОЗУ соединены шиной управления с соответствующими выводами генератора импульсов и блока выделения границ, причем буферный блок памяти границ со схемами обрамления содержит ОЗУ, информационные входы которого через буферный регистр соединены с выходами первого регистра хранения, а адресные входы и информационные выходы которого соединены общей шиной с вводами блока приема и передачи информации, входы разрешения записи буферного регистра и ОЗУ соединены с выходом схемы сравнения кодов, а их входы управления соединены с соответствующими выходами генератора импульсов, входы управления регистров хранения соединены с выходом блока выделения границ.

По сравнению с прототипом заявляемое техническое решение имеет следующие отличительные признаки: введены блок амплитудных компараторов, блок выбора уровней, преобразователь позиционного кода в двоичный код, первый и второй регистры хранения, схема блока сравнения кодов, блок формирования машинного и управляющего слов, буферный блок памяти границ, расширены функции генератора импульсов, определены связи между блоками и схемами. Следовательно, заявляемое техническое решение соответствует критерию "новизна".

При реализации изобретения по сравнению с прототипом с помощью введенных блоков, схем и устройств осуществляют одновременное считывание информации от всех сечений, формирование массива управляющих слов, массива значений границ сечений с последующей их передачей в ЭВМ, что позволяет увеличить скорость считывания и передачи информации, уменьшить требуемый объем памяти для записи информации от каждого кадра. Следовательно, заявляемое техническое решение соответствует критерию "Положительный эффект".

По сравнению с прототипом заявляемое техническое решение отличается тем, что в него введены новые блоки, схемы и устройства, установлены их связи.

Известны амплитудные компараторы и объединение их в блоки, регистры сдвига и хранения, логические элементы.

Известны блоки памяти как полупроводниковые БИС ЗУ, состоящие из накопителей и схем обрамления. В схему обрамления входят:

адресная часть (строчные и столбцовые дешифраторы), обеспечивающие выбор одного или нескольких запоминающих элементов в накопителе в соответствии с поданными на адресные входы комбинаций двоичных сигналов;

числовая часть, с помощью которой производится передача информации от входа БИС ЗУ к выбранному запоминающему элементу при записи и передачи информации от запоминающего элемента к выходу БИС ЗУ при считывании;

блок местного управления, осуществляющий координацию работы всех узлов в режиме хранения, записи, считывания, регенерации. Первичные команды, поданные на входы БИС ЗУ преобразуются во вторичные управляющие сигналы, посылаемые в различные узлы БИС ЗУ в определенные моменты времени. Внешние схемы обрамления содержат регистры адреса и дешифраторы, обеспечивающие выбор определенных БИС ЗУ ячеек выбранной БИС ЗУ, обеспечивает параллельную запись информации в секции обратного хода развертки (см. Полупроводниковые запоминающие устройства и их применение. Под редакцией А.Ю.Гордонова. М. "Радио и связь", 1981 г.).

Функции генератора импульсов расширены, формируют прямую и инверсную последовательности импульсов синхронизации, сигналы управления, синхронные с опорной частотой генератора, сигналы управления поочередной работой регистров сдвига пар, блокирование работы схемы на время обратного хода развертки. Формирование таких сигналов известно (Схематическое проектирование ЭВМ. Учебное пособие. Барашев А.Ф. Быков В.И. г.Владимир, 1990 г.)

Новые признаки в совокупности позволяют повысить скорость считывания изображений по сечениям и его передачи в ЭВМ, дополнительно позволяют делать запись того же объема информации от всех сечений в меньшем объеме памяти. Следовательно, заявляемое техническое решение соответствует критерию "существенные отличия".

На фиг. 1-3 приведена схема устройства.

Устройство состоит из телевизионного датчика 1, видеоусилителя 2, селектора 3 видеосигнала, блока 4 синхронизации и управления, первого счетчика 6, блока 7 выделения границ по координате Х, элемент И 9, блока 10 видеоконтроля (на схеме не показан), блока 11 приема и передачи информации сопряжения, блока выбора уровней, блока 13 амплитудных компараторов, генератора 14 импульсов, позицией 15 обозначена ЭВМ, преобразователь позиционного кода в двоичный, третий счетчик 17, первый 19 и второй 18 регистры хранения информации, блок сравнения 20, блок формирования машинного и управляющего слов 21, буферный блок памяти границ 22. Блок формирования машинного и управляющего слов содержит первую 23 и вторую 24 пары регистров сдвига и две секции 25, 26 оперативного запоминающего устройства ОЗУ. Буферный блок памяти содержит буферный регистр 27, ОЗУ 28 со схемами обрамления.

Телевизионный датчик 1 представляет собой функциональный модуль, предназначенный для получения стандартного телевизионного видеосигнала. Видеоусилитель 2 предназначен для усиления видеосигнала до необходимого уровня, селектор 3 видеосигнала для выделения из полного телевизионного видеосигнала сигналов строчной и кадровой синхронизации и приведения этих сигналов к необходимому логическому уровню. Импульсы строчной частоты выделяются дифференцированием, а кадровой частоты интегрированием сигналов. Введение в состав устройства селектора 3 позволяет обрабатывать видеосигнал не только от телевизионного датчика, но и от других стандартизованных по выходу источников видеосигнала: видеомагнитофонов, линий связи, имитаторов и синтезаторов видеосигнала, что расширяет функциональные возможности устройства.

Блок 4 осуществляет синхронизацию блоков устройства в соответствии с пиком телевизионных разверток растра и установку счетчиков в исходное состояние. Счетчик 5 выполняет функции управляемого делителя частоты. Он уменьшает частоту следования строчных синхроимпульсов в два, четыре, восемь раз, чем достигается изменение масштаба дискретизации по кадру. Блок 7 выделения границ по координате Y выделяет для обработки "окно", т.е. участок растра по кадру (по координате Y). Блок содержит счетчик начала и конца участка, триггеры начала То и конца Тко окна и ключ. Если текущая строка находится внутри "окна", определенного содержимым счетчиком начала и конца участка, устанавливается триггер То и разрешает прохождение строчных импульсов через ключ на элементе И 9. После окончания "окна" триггер закрывает ключ. Элемент И 9 разрешает прохождение импульсов опорной частоты генератора 14 в счетчик 6 по сигналу из блока 7 выделения границ по координате Y. Счетчик 6 аналогичен счетчику 5 и выполняет аналогичную функцию делит частоты опорного генератора 14 в два, четыре, восемь раз до нужного масштаба дискретизации в пределах строки разложения. Блок 8 выделения границ по координате Х выделяет для ввода участок строки. Блок содержит счетчики начала и конца участка (на схеме не показаны). Значениями счетчиков определяется участок строки для обработки. В течение цикла ввода изображения блок 8 выделяет последовательность импульсов, соответствующую во временной области моментам формирования первичных отсчетов изображения в объеме выбранного числа элементов разложения. Эти импульсы управляют работой сдвиговых регистров.

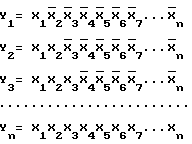

Функциональная схема блока 8 границ аналогична схеме блока 7. Блок 11 приема и передачи информации предназначен для организации связи устройства для считывания информации с ЭВМ. Этот блок реализует прямой и программный режимы доступа к памяти ЭВМ, содержит буферные регистры для хранения информации о формате разложения, относительном местоположении считываемого участка растра, и порогах квантования видеосигнала по яркости, о начальном адресе сегментов ОЗУ. В качестве ЭВМ используется универсальная и специализированная вычислительная машина, которая осуществляет управление режимами работы устройства, катализацию и хранение видеоинформации. Генератор 14 импульсов генерирует опорную частоту, синхронную с частотой телевизионного датчика, формирует первичные сигналы управления секционированным оперативным запоминающим устройством, последовательность тактовых импульсов для синхронизации работы первого и второго регистров хранения информации, коммутацию регистров сдвига в парах, сигналы блокировки работы схемы на время обратного хода развертки по строке, вырабатывает сигналы начальной установки блоков и устройств. Блок 12 выбора уровней предназначен для выбора уровней срабатывания схемы при квантовании видеосигналов по амплитуде. Блок содержит по крайней мере один цифроаналоговый преобразователь и делитель напряжения. Выходное напряжение цифроаналогового преобразователя служит источником питания делителя напряжения, с помощью которого задаются уровни порогов для амплитудных компараторов блока 13. Величина уровней порогов соответствует цифровому коду на входах ЦАП из ЭВМ через блок 11. Блок 13 амплитудных компараторов содержит амплитудные компараторы, число которых определяется числом сечений изображения, имеющих прямой и инверсный выходы. На один вход всех аналоговых быстродействующих компараторов подают видеосигнал, на другой вход каждого компаратора подают опорное напряжение с делителя напряжения таким образом, что каждому амплитудному компаратору соответствует свой уровень, свое сечение. В результате видеосигнал сравнивается с пороговыми уровнями, каждый компаратор выдает результат (превышает ли видеосигнал установленный порог или нет) в виде двухуровневого сигнала. В совокупности на выходах блока формируется код типа 11110000000. начиная с выхода амплитудного компаратора с наименьшим порогом срабатывания. Единицы соответствуют тем компараторам, для которых порог срабатывания (опорное напряжение) по величине меньше значения видеосигнала в момент считывания информации. На инверсных выходах амплитудных компараторов формируется код типа 00001111111. Блок 16 предназначен для преобразования кода, снимаемого с выходов блока амплитудных компараторов, в двоичный код и код "четное/нечетное" сечение, причем "0" на данном выходе соответствует четному номеру сечения, а "1" нечетному. На первой ступени блок выдает унитарный код, принимающий значение логической единицы только на одном выходе, соответствующем самому высокому уровню, для которого выполняется условие напpяжение на входе больше порогового уровня, при этом реализуется система переключательных функций

На второй ступени блока унитарный код преобразуется в двоичный путем объединения операцией ИЛИ соответствующих выходов первой ступени по правилу формирования двоичного кода на выходе блока, т.е.

B

·

· объединяются все выхо ды Yi, в двоичном коде уровней которого содержатся единицы в младшем разряде;

объединяются все выхо ды Yi, в двоичном коде уровней которого содержатся единицы в младшем разряде;

B2=  Yi объединяются все единицы в разряде двоек;

Yi объединяются все единицы в разряде двоек;

Bст.разряд=  Yi объединяются все единицы в старшем разряде. Выход "четное/нечетное" соответствует выходу элемента ИЛИ, входы которого соединены с выходами Yi нечетных уровней блока

Yi объединяются все единицы в старшем разряде. Выход "четное/нечетное" соответствует выходу элемента ИЛИ, входы которого соединены с выходами Yi нечетных уровней блока

н

н ч

ч ч

ч

Первый 19 и второй 18 регистры хранения информации предназначены для записи и хранения информации о двух соседних точках в течение времени ее обработки схемой сравнения кодов и записи в один из регистров пары регистров сдвига блока 21. Первый регистр хранит информацию о текущем значении, а второй о предыдущем значении. Второй регистр выполнен двухступенчатым, в регистр первой ступени записывается информация о текущем значении, при записи нового текущего значения содержимое регистра первой ступени переписывается в регистр второй ступени и подается на схему сравнения кодов как предыдущее значение.

Блок сравнения кодов 20 предназначен для сравнения кодов, соответствующих значениям яркости двух соседних элементов разложения. При неравенстве сравниваемых кодов схема сравнения выдает сигнал логической единицы "1", который свидетельствует о наличии границы, фиксируется в одном из регистров пары и инициирует запись кода значения яркости в буферный блок памяти границ.

Блок 21 формирования машинного и управляющего слов предназначен для формирования в формате ЭВМ машинного и управляющего слов за 16 тактов (при использовании 16-разрядной ЭВМ) путем объединения информации от 16 расположенных подряд элементов разложения. При формировании следующего машинного и следующего управляющего слов сформированные машинное и управляющее слова записываются в соответствующие секции ОЗУ параллельным кодом, при этом в одном регистре пары идет формирование слова, а с другого регистра пары информация подается в секцию ОЗУ для ее записи, потом регистры меняются местами. Буферный блок памяти границ 22 предназначен для записи кодов значений границ в пределах кадра.

В предельном случае имеет объем, равный объему ОЗУ при поэлементной записи информации n x m x k, где n число элементов разложения вдоль строки, m число элементов разложения по кадру, k число разрядов для записи значения яркости элемента разложения. Информация в ОЗУ подается с выхода регистра хранения 19 через буферный регистр 27, который управляется сигналом с выхода схемы сравнения кодов 20.

Устройство работает следующим образом.

На этапе подготовки устанавливаются параметры вводимого изображения: относительное местоположение и размер считываемого растра Yнач, Хнач, Δ Y, Δ Х, число элементов разложения (масштаб дискретизации) К1, К2, начальное значение пороговых уровней. Эта информация передается из ЭВМ 15 через буферные регистры блока 11 в счетчики 5 и 6, блоки 7 и 8 выделения границ по координатам Y и Х, блок 12 выбора уровней. На этапе считывания видеоинформации из телевизионного датчика 1 через видеоусилитель 2 в селектор 3 непрерывно подается видеосигнал. В селекторе происходит разделение видеосигнала на синхронизирующие кадровые, строчные и видеосигнал. Сигнал "Пуск", поступающий из ЭВМ 15 через блок 11, переводит блок 4 в режим управления вводом изображения. С приводом кадрового синхроимпульса (КСИ) происходит привязка к конкретному полукадру (четному или нечетному) и строчные синхроимпульсы (ССИ) начинают поступать на счетчик 5. Счетчик 5 "разряжает" растр, т.е. уменьшает число строк до выбранного формата разложения. Коэффициент деления установлен по коду из ЭВМ. Синхроимпульсы (СИ), соответствующие необходимой частоте строк в считываемом растре, поступают в блок 7 выделения границ по координате Y. В счетчиках начала и конца окна этого блока содержится код, соответствующий номеру строки, с которой начинается считывание и строки, на которой ввод изображения заканчивается. При переполнении счетчиков во время подсчета строчных импульсов устанавливается триггер начала и конца окна То и Тко, которые определяют границы участка растра по коду для считывания. Если текущая строка находится в пределах этого участка, элемент И 9 открывается разрешающим сигналом с блока 7 выделения границ и пропускает импульсы генератора 14, которые размещают выделенную строку в счетчик 6. Счетчик 6, как и счетчик 5, в соответствии с установленным коэффициентом деления, уменьшает частоту дискретизации по строке (по координате Х). С выхода счетчика 6 импульсы дискретизации поступают на вход блока 8 выделения границ по координате Х, в котором определяется участок строки для считывания. Функционирование блока 7 не отличается от рассмотренного. Импульсы на выходе блока 8 выделения границ по координате Х соответствуют моментам дискретизации данного участка всего растра, доступного сканированию телевизионным датчиком, в данном объеме разложения. Эти импульсы подаются на регистры сдвига 21 для фиксации мгновенных значений видеосигнала в кодированном виде. Формирование машинных и управляющих слов в формате ЭВМ продолжается 16 тактов сдвига регистров пар 23, 24, после чего необходимо инициировать коммутацию регистров сдвига пар и обмен с двумя секциями оперативного запоминающего устройства.

Сущность формирования машинного и управляющего слов поясняется на фиг. 1 и 2.

Для сжатия информации при ее считывании по сечениям блок 16 выдает на выходе четное/нечетное сигнал логического нуля "0", если уровень входного сигнала соответствует четному сечению, и сигнал логической единицы, если уровень входного сигнала соответствует нечетному сечению, поле растра содержит n элементов разложения вдоль строки (например, 256) и m элементов по кадру (например, 256), всего n x m элементов, при этом яркость элементов разложения кодируется k-разрядным словом, объем одного кадра равен n x m x k (19) бит. При считывании по сечениям объем информации от одного кадра увеличивается и составляет (n x m x 2k) бит, при принятом формате разложения 256 х 256 х 256 составляет 224 бит, по отношению к случаю кодирования яркости k-разрядными словами (k 8, объем 256 х256 х 8 составляет 219 бит) требуется значительно большее время для передачи информации одного кадра и значительно больший объем памяти для ее записи. При этом все сечения проектируются на плоскость (фиг. 1). При таком представлении требуется объем памяти 256 х 256 х 1 216, что значительно меньше рассмотренного раньше (256 х 256x х 256 224), но в этом случае есть ограничения как (фиг. 1).

1. Совпадение границ сечения N 1 и 2 со- ответственно потеря перехода "0"->>"1"/"1"->> ->> "0" и границы.

2. Неразличимость вершин и впадин (сечение N 7 и 1).

3. Верхнее сечение не может быть шире нижнего, но может быть равно, поэтому возможно поглощение верхним сечением нижнего, то есть отличие выше лежащего сечения более чем на единицу (сечение N 6 поглотило сечения N 4 и N 5).

4. При поглощении сечений возможно совпадение кодировки (поглощение нечетного числа сечений) и, как следствие, поглощение границ всего сечения.

Данные ограничения снимаются при формировании на каждое машинное слово одного управляющего слова и массива значений границ, при этом объем памяти, необходимый для записи одного кадра, возрастает, максимальное значение объема памяти не превосходит объема записи двух сечений плюс объем памяти n x m x k бит (217 + 219), что меньше чем при записи по отдельным сечениям.

Формирование машинного и управляющего слов (фиг. 2) осуществляется следующим образом.

До поступления импульса "Пуск" от ЭВМ регистры хранения 19 и 18 находятся в нулевом состоянии, что соответствует позиции 0 на фиг. 2. После запуска устройства осуществляется обработка первого элемента разложения растра позиция 1 на фиг. 2. В этом случае входной сигнал превышает только уровень 01, поэтому позиции 1 соответствует код 1000000000. Этот код сравнивается с предыдущим значением кодом 0000000000. Так как единица соответствует нечетному сечению, то в первый разряд машинного слова записывается единица (поз. 1а на фиг. 2). Текущее значение кода отличается от предыдущего, что говорит о переходе к новому сечению, а в разряд управляющего слова записывается единица, а код значения яркости текущего элемента записывается в массив буферного блока памяти границ. Далее код позиции 2 сравнивается с кодом поз. 1, в следующий разряд машинного слова записывается 0, так как сечение имеет четный номер, а в разряд управляющего слова снова записывается единица и новое значение границы записывается в ББПГ. При равенстве кодов двух соседних позиций (поз. 9 и 10) в разряд управляющего слова записывается 0, а код границы не формируется.

Число разрядов формируемых слов равно числу элементов разложения в пределах каждой строки. В соответствии с форматом применяемой ЭВМ данные слова разбиваются на ряд слов (например, при числе элементов разложения вдоль строки 256 и использовании 16-ти разрядной ЭВМ строку разбивают на 16 16-ти разрядных слов). При переходе к следующей строке формирование машинных и управляющих слов происходит аналогично. Блок амплитудных компараторов 13 осуществляет сравнение входного видеосигнала с рядом пороговых уровней, которые задаются блоком 12 выбора уровней. В результате сравнения блок вырабатывает код, который соответствует входному сигналу и показан на i-позиции на фиг. 2. Блок 16 преобразует данный код в двоичный и вырабатывает сигнал четное/нечетное, где четному номеру сечения соответствует сигнал 0, а нечетному сечению 1. Двоичный код как текущее значение входного видеосигнала записывается по сигналу с блока 8 в первый 19 регистр хранения и в регистр первой ступени регистра 18, при этом содержимое регистра первой ступени переписывается в регистр второй ступени, как предыдущее значение сигнала. С выходов регистров 19 и 18 коды текущего и предыдущего значений видеосигнала подаются на схему сравнения 20, сигнал на выходе которой фиксирует границу между сечениями и инициирует запись кода границы в ОЗУ через буферный регистр 27. В блоке 21 на первые регистры пар регистров сдвига 23, 24 подают соответственно сигнал четное/нечетное с выхода логического блока 16 и сигнал с выхода логического блока 16 и сигнал с выхода блока сравнения кодов 20, инициализация работы этих регистров осуществляется сигналом с выхода блока 8. При завершении обработки n элементов разложения формируется машинное и управляющее слова в формате ЭВМ (например, равно 16). После обработки каждого 16-го элемента разложения информацию подают на входы вторых регистров пар, коммутируя входы и выходы регистров сдвига пар сигналами с выхода триггера генератора 14 импульсов (на схеме триггер не показан), который опрокидывается импульсами сдвига после деления на 16 с помощью делителя частоты входит в состав генератора импульсов, на схеме не показан. При этом выходы первых регистров пар подключают ко входам двух секций ОЗУ 25, 26 сигналом с генератора 14 осуществляют запись в секции ОЗУ. Информацию с секций ОЗУ формирователя машинного и управляющего слов и с буферного блока памяти границ подают по общей шине на блок приема и передачи 11, осуществляя передачу массивов данных в память ЭВМ в режиме прямого доступа.

Таким образом, вместо k-массивов информации о k-сечениях передается два массива объемом, необходимым для записи двух сечений и массив, объемом, не превышающим объем, необходимый для записи информации поэлементно, что меньше, чем при считывании информации по отдельным сечениям, поэтому увеличивается скорость считывания и передачи информации в ЭВМ, для ее записи требуется меньший объем памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2051416C1 |

| Устройство для считывания изображений | 1988 |

|

SU1642488A2 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162248C2 |

| Устройство для считывания изображений | 1985 |

|

SU1251135A1 |

| Устройство для считывания графической информации | 1986 |

|

SU1418776A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

| Устройство формирования телевизионного изображения с перемещением управляемого фрагмента | 1988 |

|

SU1644171A1 |

| Устройство для считывания изображений | 1987 |

|

SU1481816A2 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

Изобретение относится к автоматике и вычислительной технике. Расширение области применения, повышение скорости считывания изображений по сечениям и передачи ее в ЭВМ достигаются за счет введения преобразователя позиционного кода в двоичный код, первого и второго регистров хранения информации, блока сравнения кодов, блока формирования машинного и управляющего слоев, буферного блока памяти. 3 ил.

УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ, содержащее последовательно соединенные телевизионный датчик, видеоусилитель и селектор видеосигнала, первый выход которого соединен с информационным входом блока синхронизации и управления, первый выход которого подключен к счетному входу первого счетчика, выход которого соединен с информационным входом блока выделения границ по координате Y, генератор импульсов, первый выход которого соединен с одним из входов элемента И, другой вход которого подключен к выходу блока выделения границ по координате Y, а выход к счетному входу второго счетчика, выход которого соединен с информационным входом блока выделения границ по координате X, выход которого соединен с информационным входом третьего счетчика, выход которого подключен к управляющему входу второго счетчика, блок приема и передачи информации, первые вход и выход которого являются соответственно входом и выходом устройства, а второй и третий выходы соединены с информационными входами первого и второго счетчиков соответственно, второй выход блока синхронизации и управления подключен к управляющим входам блоков выделения границ по координатам X и Y, третьего счетчика и генератора импульсов, второй выход которого соединен с тактовыми входами блока синхронизации и управления, блока выделения границ по координате X и блока приема и передачи информации, отличающееся тем, что в устройство введены блок выбора уровней, блок амплитудных компараторов, преобразователь позиционного кода в двоичный код, регистры хранения информации, блок сравнения, блок формирования машинного и управляющего слов, буферный блок памяти, вход блока выбора уровней соединен с третьим выходом блока приема информации, а выход с первым входом блока амплитудных компараторов, второй вход которого подключен к второму выходу селектора видеосигнала, а выход к входу преобразователя позиционного кода в двоичный код, первый выход которого соединен с информационным входами первого и второго регистров, выход которого подключен к первому входу блока сравнения, выход которого соединен с вторым информационным входом блока формирования машинных и управляющих слов и вторым информационным входом буферного блока, второй вход которого соединен с первым информационным входом буферного блока и выходом первого регистра, тактовый вход которого подключен к второму выходу генератора импульсов и тактовым входам второго регистра, буферного блока и блока формирования машинных и управляющих слов, информационный вход которого соединен с четвертым выходом блока приема и передачи информации и вторым информационным входом буферного блока, выход которого и выход блока машинного и управляющего слов подключен к второму информационному входу блока приема и передачи информации, блок формирования машинного и управляющего слов содержит регистры сдвига и оперативные запоминающие устройства, первые информационные входы и выходы которых являются соответственно третьим информационным входом и выходом блока соответственно, а тактовые входы соединены с тактовыми входами регистров и являются тактовым входом блока, информационные входы первого и второго регистров являются соответственно первым и вторым информационными входами блока, а выходы регистров соединены соответственно с вторыми информационными входами первого и второго оперативных запоминающих устройств, буферный блок содержит оперативное запоминающее устройство и буферный регистр, выход которого соединен с первым информационным входом оперативного запоминающего устройства, второй информационный вход и выход которого являются соответственно информационным входом и выходом блока, а тактовый вход соединен с тактовым входом буферного регистра и является тактовым входом блока.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для считывания изображений | 1987 |

|

SU1481816A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-10-10—Публикация

1992-07-29—Подача