Изобретение относится к измерительной технике и может быть использовано при создании измерительных систем в геодезии.

Известно устройство для измерения амплитуды и фазы радиосигнала, включающее измерительный блок, состоящий из последовательно соединенных задающего генератора, усилителя мощности, антенного переключателя, соединенного с приемопередающей антенной, приемника и амплитудно-фазового измерителя, второй вход которого подключен к второму выходу задающего генератора, а также генератора низкой частоты и расположенного между выходом генератора низкой частоты и вторыми входами антенного переключателя коммутатора-формирователя, вторые выходы которого подключены к вторым входам усилителя мощности, и рентранслятор,

содержащий последовательно соединенные задающий генератор, усилитель мощности, антенный переключатель, соединенный с приемопередающей антенной, приемник и блок автоматической подстройки фазы, выход которого подключен и входу задающего генератора, а также расположенные между вторым выходом блока автоматической подстройки фазы и вторыми входами антенного переключателя последовательно соединенные генератор низкой частоты и коммутатор-формирователь, вторые выходы которого подключены к усилителю мощности, а третьи к приемнику, и расположенный между вторым выходом задающего генератора и вторым входом блока автоматической подстройки фазы амплитудно-фазовый измеритель, второй вход которого соединен с вторым выходом приемника.

Недостатком устройства является низкая точность измерения информационного параметра из-за излучения сигнала только на частоте опорного генератора.

Известно устройство для измерения фазы радиосигнала, содержащее измерительный блок, состоящий из опорного генератора, синтезатора частот, коммутатора-формирователя, последовательно соединенных усилителя мощности, антенного переключателя, смесителя, усилителя промежуточной частоты, усилителя-ограничителя, фазового детектора и решающего блока, приемопередающей антенны, соединенной с антенным переключателем, причем выход опорного генератора соединëн с первыми входами синтезатора частот, коммутатора-формирователя и вторым входом фазового детектора, выходы решающего блока соединены с управляющими входами опорного генератора, синтезатора частот и коммутатора-формирователя, выходы которого соединены с управляющими входами усилителями мощности, антенного переключателя и фазового детектора, выходы синтезатора частот соединены с усилителем мощности и смесителем,

ретранслятор, состоящий из опорного генератора, синтезатора частот, коммутатора-формирователя, последовательно соединенных фазовращателя, усилителя мощности, антенного переключателя, смесителя промежуточной частоты, усилителя-ограничителя, фазового детектора и решающего блока, приемопередающей антенны, соединенной с антенным переключателем, причем выход опорного генератора соединен с первыми входами, синтезатора частот, коммутатора-формирователя и вторым входом фазового детектора, выходы решающего блока соединены с управляющими входами фазовращателя и синтезатора частот, выходы которого соединены с фазовращателем и смесителем, выходы коммутатора-формирователя соединены с усилителем мощности, антенным переключателем и фазовым детектором.

Данное устройство характеризуется тем, что позволяет с высокой точностью измерять расстояние между измерительным блоком и ретранслятором за счет излучения сигналов на нескольких частотах.

Недостатком устройства является низкая точность измерения расстояния при воздействии помех в зоне работы измерительного блока и ретранслятора.

Цель изобретения повышение точности измерения информационного параметра.

Это достигается тем, что в устройство для измерения фазы радиосигнала, содержащее измерительный блок, состоящий из опорного генератора, синтезатора частот, коммутатора-формирователя, последовательно соединенных усилителя мощности, антенного переключателя, смесителя, усилителя промежуточной частоты, усилителя-ограничителя фазового детектора и решающего блока, приемопередающей антенны, соединенной с антенным переключателем, причем выход опорного генератора соединен с первыми входами синтезатора частот,

коммутатора-формирователя и вторым входом фазового детектора, выходы решающего блока соединены с управляющими входами опорного генератора, синтезатора частот и коммутатора-формирователя, выходы которого соединены с управляющими входами усилителя мощности, антенного переключателя и фазового детектора, выходы синтезатора частот соединены с усилителем мощности и смесителем, ретранслятор, состоящий из опорного генератора, синтезатора частот, коммутатора-формирователя, последовательно соединенных фазовращателя, усилителя мощности, антенного переключателя, смесителя, усилителя промежуточной частоты,

усилителя-ограничителя, фазового детектора и решающего блока приемопередающей антенны, соединенной с антенным переключателем, причем выход опорного генератора соединен с первыми входами синтезатора частот, коммутатора-формирователя и вторым входом фазового детектора, выходы решающего блока соединены с управляющими входами, фазовращателя и синтезатора частот, выходы которого соединены с фазовращателем и смесителем, выходы коммутатора-формирователя соединены с усилителем мощности,

антенным переключателем и фазовым детектором, в измерительной блок введены блок ввода, блок вывода и К фильтров фазовых измерений, причем входы К фильтров фазовых измерений соединенных с выходом фазового детектора, а их выходы соединены с информационными входами блока ввода, выход которого соединен с решающим блоком, выходы решающего блока соединены с входами блока ввода и блока вывода, выходы которого соединены с входами управления К фильтров фазовых измерений.

Введение перечисленных блоков с описанным связями позволяет повысить точность измерения информационного параметра при воздействии помех за счëт введения дополнительной фильтрации фазовых измерений на каждой из принимаемых частот устройства.

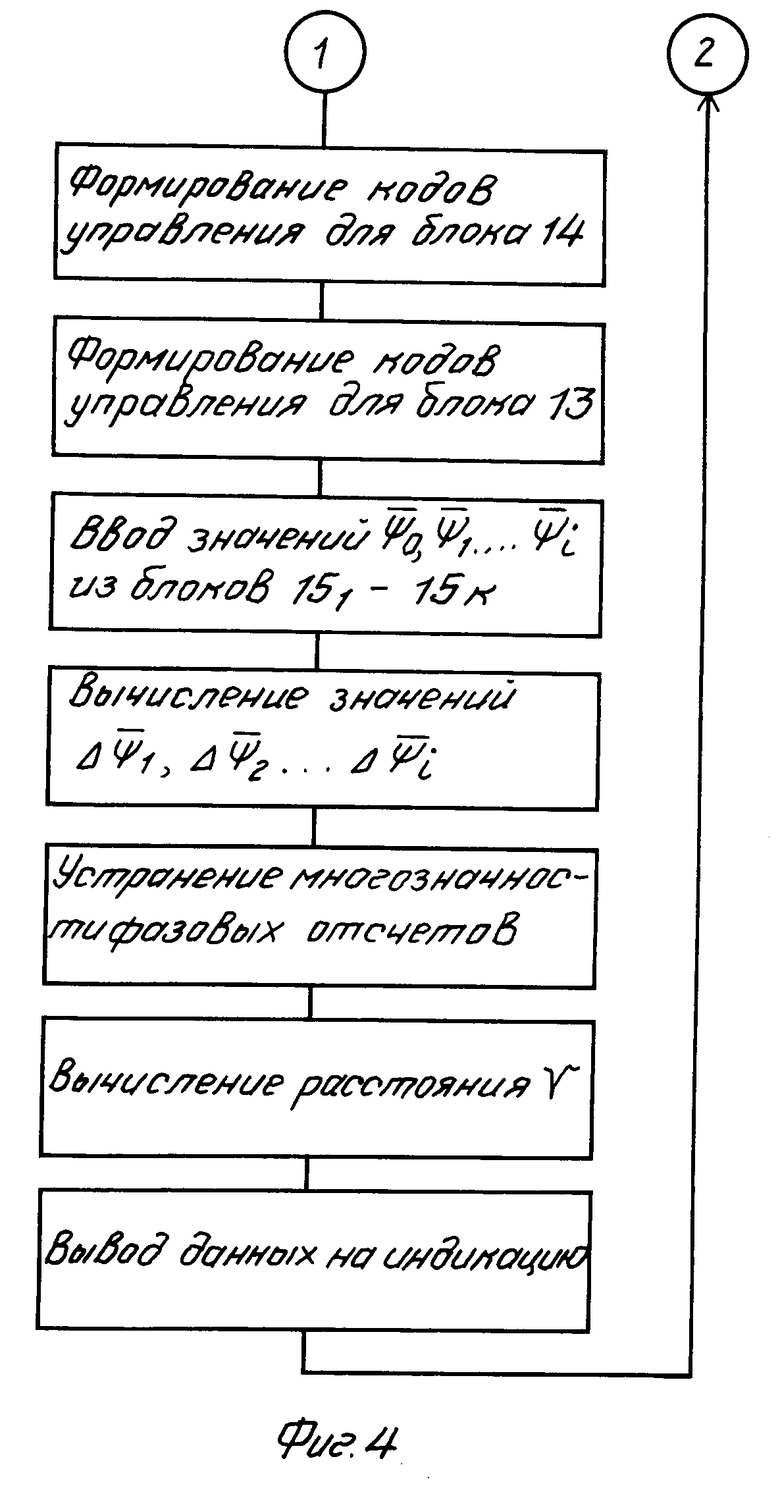

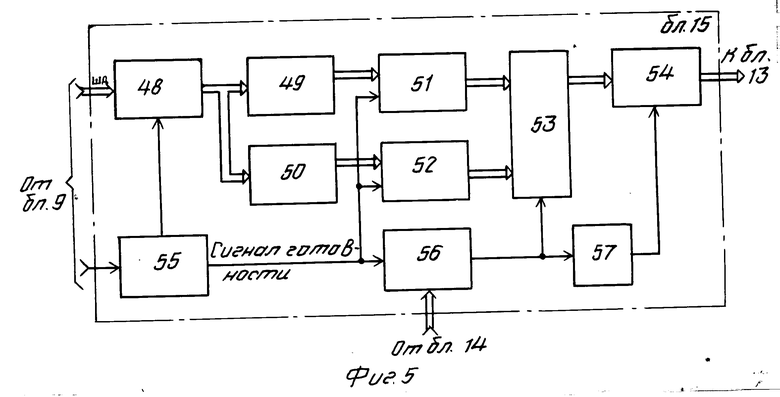

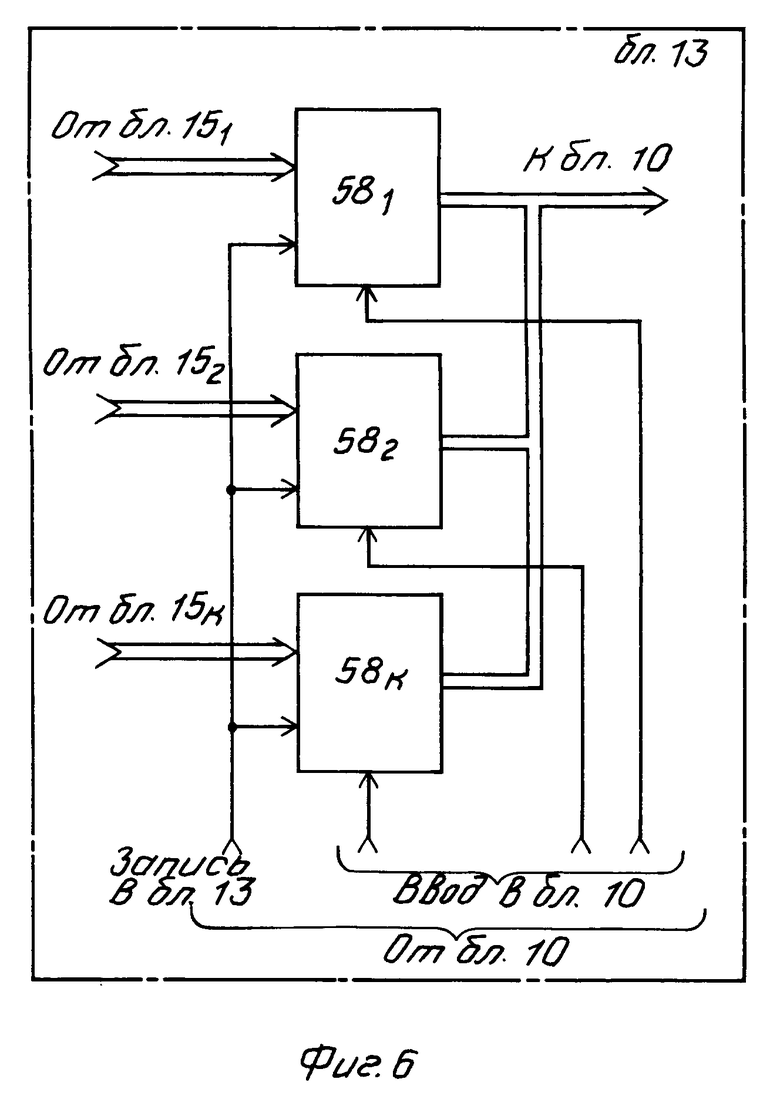

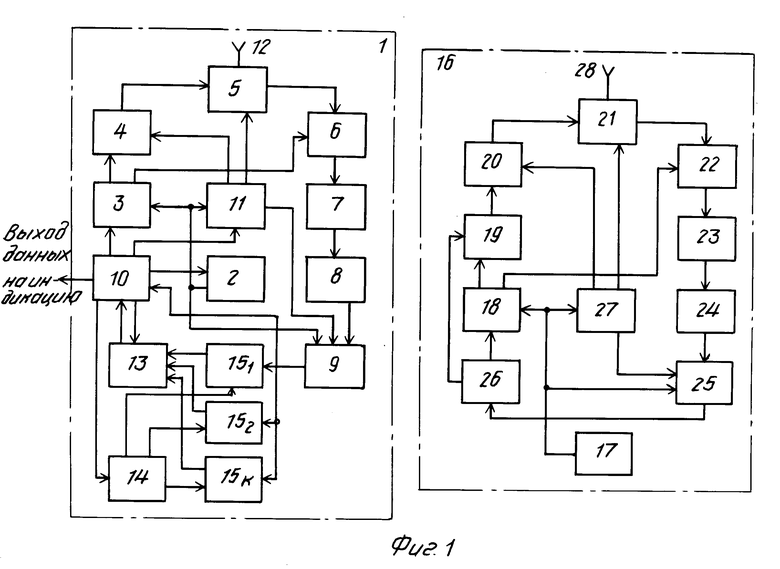

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 временные диаграммы, поясняющие его работу; на фиг. 3 вариант решающего блока; на фиг. 4 блок-схема алгоритма его работы в измерительном блоке; на фиг. 5 вариант фильтра фазовых измерений; на фиг. 6 и 7 варианты реализации блоков ввода и вывода соответственно; на фиг. 8 вариант фазового детектора.

Устройство содержит измерительный блок 1, состоящий из последовательно соединенных опорного генератора 2, синтезатора частот 3, усилителя мощности 4, антенного переключателя 5, смесителя 6, усилителя промежуточной частоты 7, усилителя-ограничителя 8, фазового детектора 9, образующих амплитудно-фазовый измеритель решающего блока 10, коммутатора-формирователя 11, выходы которого соединены с усилителем мощности 4, фазовым детектором 9 и антенным переключателем 5, соединенным с приемопередающей антенной 12, блока ввода 13, блока вывода 14, К фильтров фазовых измерений 151 15к, входы К фильтров 151 15ксоединены с выходом

фазового детектора 9, а выходы К фильтров 151 15к соединены с информационными входами блока ввода 13, выход которого соединен с решающим блоком 10, выходы решающего блока 10 соединены с входами управления опорного генератора 2, синтезатора частот 3, блока ввода 13 и блока вывода 14, выходы которого соединены с входами управления К фильтров 151 15к, выход опорного генератора 2 соединен с фазовым детектором 9 и коммутатором-формирователем 11, второй выход синтезатора частот 3 соединен со смесителем 6,

ретранслятор 16, содержащий последовательно соединëнные опорный генератор 17, синтезатор частот 18, фазовращатель 19, усилитель мощности 20, антенный переключатель 21, смеситель 22, усилитель промежуточной частоты 23, усилитель-ограничитель 24, фазовый детектор 25 и решающий блок 26, выходы которого соединены с входами управления синтезатора частот 18 и фазовращателя 19, выход опорного генератора 17 соединен с фазовым детектором 25 и коммутатором-формирователем 27, выходы которого соединены с фазовым детектором 25, усилителем мощности 20 и антенным переключателем 21, антенный переключатель 21 соединен с приемопередающей антенной 28, второй выход синтезатора частот 18 соединен со смесителем 22.

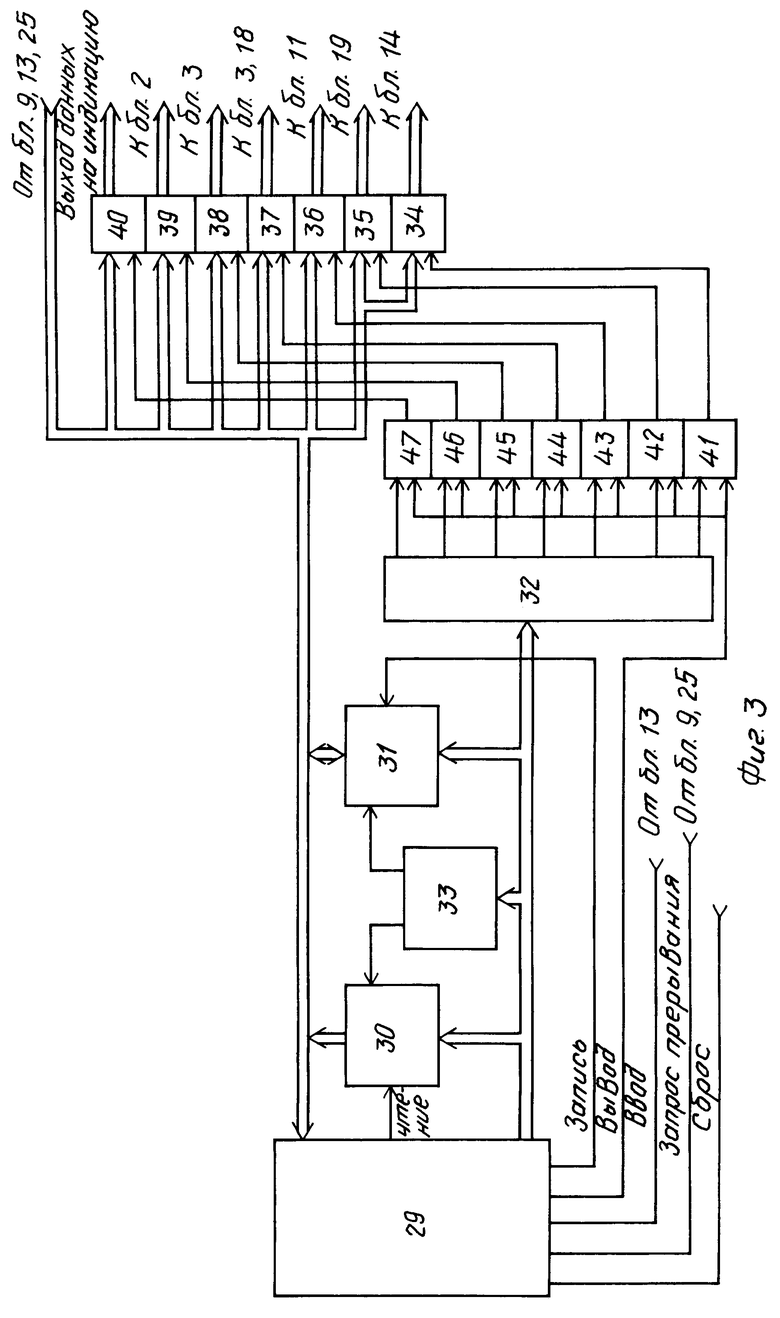

Решающий блок 10(26) содержит (см. фиг. 3) содержит микропроцессорный модуль 29, шина адреса которого соединена с адресными входами постоянного запоминающего элемента 30, оперативного запоминающего элемента 31 и входами дешифратора 32, 33, выходы которого соединены с управляющими входами запоминающих элементов 30 и 31, управляющие выходы микропроцессорного модуля 29 "чтение", "запись" соединены с входами управления постоянного 30 и оперативного 31 запоминающих элементов соответственно, информационные входы выходы микропроцессорного модуля 29 соединены с выходами постоянного запоминающего элемента 30, с информационными входами выходами оперативного запоминающего элемента 31, с входами регистров 34 40, выходы дешифратора 32 соединены через элементы 41 47 с входами управления регистров 34 40.

Фильтр фазовых измерений 151 15к (см. фиг. 5) содержит регистр 48, выходы которого соединены с вычислителем синусов 49 и вычислителем косинусов 50, накопители 51 и 52, выходы которых соединены с выходным регистром 53, вычислительный блок 54, выходы которого являются выходами блока 15, формирователь импульсов 55, выход которого соединен с входами накопителей 51, 52 и входом счетчика 56, входы управления которого соединены с блоком 14, а выход соединен с выходным регистром 53 и формирователем импульсов 57, выход которого соединен с входом управления вычислительного блока 54.

Блок ввода 13 (см. фиг. 6) содержит К регистров 581 58к, выходы которых являются выходами блока 13 и соединены с блоком 10, входы управления регистров 581 58к соединены с блоком 10.

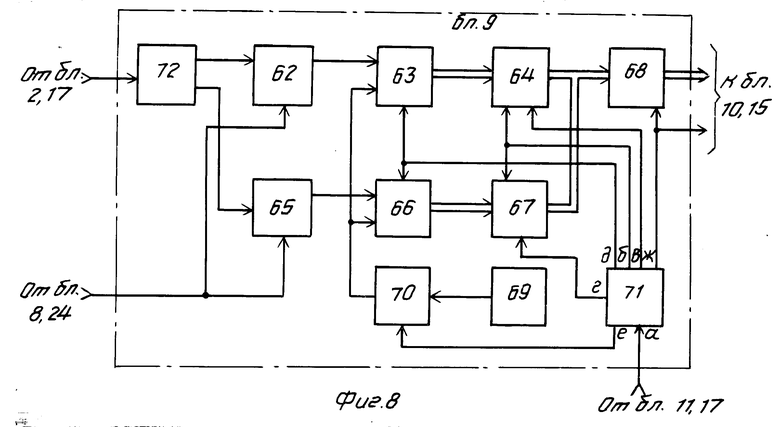

Фазовый детектор 9(25) содержит (см. фиг. 8) последовательно соединенные элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 62, счетчик 63 и регистр 64, последовательно соединенные элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 65, счетчик 66 и регистр 67, вычислительный блок 68, входная шина которого соединена с выходами регистров 64, 67, генератор импульсов 69, соединенный через элемент совпадения 70 со счетными входами счетчиков 63, 66, формирователь импульсов 71, соединенный со счетчиком 63, регистром 64, счетчиком 66, регистром 67, вычислительным блоком 68, элементом совпадения 70, формирователь ортогонального сигнала 72, соединенный с элементами ИСКЛЮЧАЮЩЕЕ ИЛИ 62, 65.

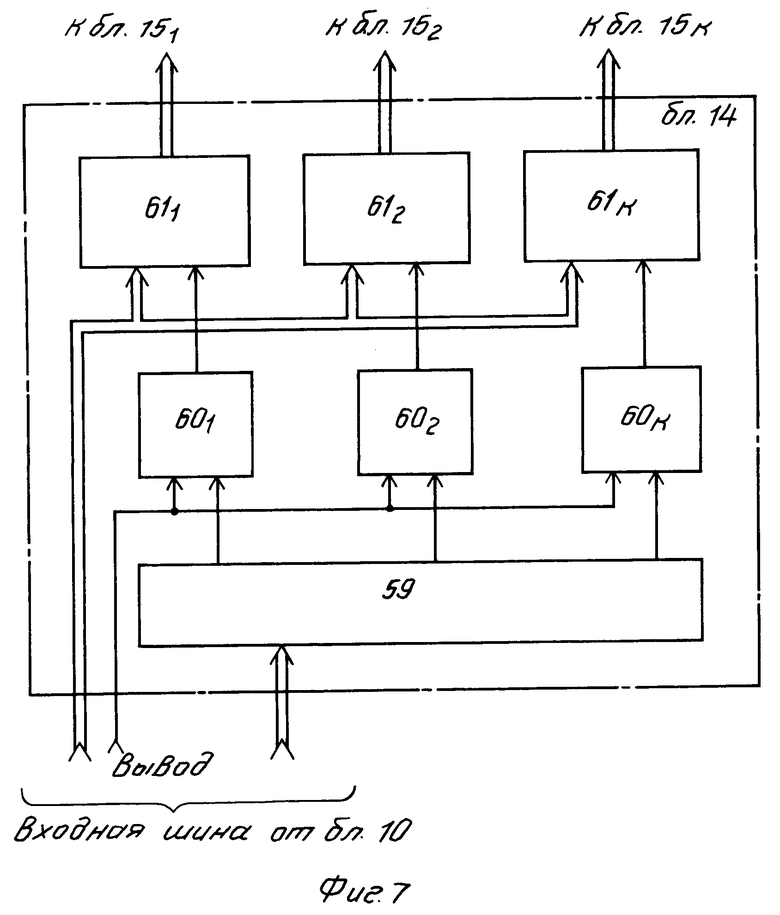

Блок вывода 14 (см. фиг. 7) содержит дешифратор 59, выходы которого соединены через элемент И 601 60к с входами управления регистров 611 61к.

Работает устройство следующим образом.

Опорные генераторы 2, 17 вырабатывают непрерывные гармонические сигналы частотой f, которые поступают на коммутаторы-формирователи 11, 27 и синтезаторы частот 3, 18. Синтезаторы частот 3 и 18 вырабатывают для излучения опорный сигнал частотой fo и несколько вспомогательных сигналов частотами f1, f2,fi, кроме того, в синтезаторах частот 3 и 18

формируются сигналы гетеродина для смесителей 6 и 22 с частотами fОГ, f1Г, f2г.fiг, при этом управление частотой излучаемых (принимаемых) сигналов осуществляется решающим блоком 10, причëм fО fОГ fПР, f1 f1Г fПР, f2 f2Г fПР, fi fiГ fПР, где fПР промежуточная частота, выделяемая усилителями 7, 23, на которой осуществляется измерение фазы принятых сигналов. Коммутаторы-формирователи 11 и 27 вырабатывают сигналы управления для блоков 4 (см. фиг. 2,а), 5,9 (см. фиг. 2,б), 21, 25 (см. фиг. 2,в), 20 (см. фиг. 2,г).

Временные диаграммы на фиг. 2 приведены для установившегося рабочего режима устройства, когда временные интервалы излучения и приëма сигналов измерительного блока 1 синхронизированы с соответствующими интервалами ретранслятора 16. Здесь Тц временный цикл работы устройства; t интервал излучения (приема) опорного сигнала частотой fО; 2t интервал излучения (приема) вспомогательных сигналов с частотами fi; tп длительность паузы.

В усилителе мощности 4 осуществляется усиление сигналов от синтезатора частот 3 до необходимой величины и формирование выходных радиоимпульсных сигналов под воздействием управляющего сигнала от коммутатора-формирователя 11 (см. фиг. 2,а). Радиоимпульсный сигнал от усилителя мощности 4, пройдя через антенный переключатель 5, излучается в пространство приемопередающей антенной 12 (см. фиг. 2, д). Сигнал, излучаемый в пространство измерительным блоком 1 в течение времени Ти, пройдя через среду распространения, принимается приемопередающей антенной 28 ретранслятора 16 и через антенный переключатель 21 поступает на вход смесителя 22. На второй вход смесителя 22 подаются сигналы от синтезатора частот 18 с частотами (fОГ, f1Г, f2Г, fiГ) в соответствии с фиг. 2,в.

В смесителе 22 осуществляется преобразование принимаемого сигнала на частоту fПР (причëм fO fОГ fПР, f1 f1Г fПР и т. п.), в усилителе промежуточной частоты 23 сигналы частотой fПР фильтруются и усиливаются, а затем нормируются по амплитуде в усилителе-ограничителе 24 и поступают на фазовый детектор 25. В фазовом детекторе 25 под воздействием управляющих сигналов осуществляется измерение фазовых сдвигов принятых сигналов, при этом измеряются фазовые сдвиги ϕ01, ϕ02, ϕoi, ϕoi' опорных сигналов частоты fО (фиг. 2, в) и фазовые сдвиги ϕ1, ϕ2, ϕi вспомогательных сигналов частотами f1, f2. fi. Информация с фазового детектора 25 поступает в решающий блок 26, в котором вычисляются фазовые соотношения в течение интервалов tn:

,

,

(1)

(1)

ϕ1' ϕ1 Δ ϕ1 ϕ2' ϕ2 Δ ϕ2 ϕi' ϕi Δ ϕi (2)

Полученные значения фазы Δ ϕ1 Δ ϕ2 Δ ϕi запоминаются в решающем блоке 26. В течение интервала Тризлучаются в пространство сигналы от ретранслятора 16, при этом управление частотой и фазой излучаемых сигналов осуществляется решающим блоком 26 через блоки 18 и 19 соответственно. В моменты времени t, когда ретранслятором 16 излучаются в пространство основные сигналы частотой fОфазовращатель 19 решающим блоком 26 установлен в исходное (нулевое) состояние, тогда излучаемые опорные сигналы частотой fО имеют фазу сигнала f опорного генератора 17. В течение интервалов 2t, когда ретранслятором 16 излучаются в пространство вспомогательные сигналы частотами f1, f2,fi, сигналами управления от решающего блока 26 устанавливаются в фазовращателе 19 фазовые сдвиги Δ ϕ1Δ ϕ2 Δ ϕi соответственно.

Таким образом, в течение интервала Тр ретранслятор 16 излучает вспомогательные сигналы, фаза которых равна фазе принятых сигналов в течение интервала Ти от измерительного блока 1, а также опорные сигналы, фаза которых равна фазе опорного генератора 17. В усилителе мощности 20 осуществляется усиление сигналов от фазовращателя 19 и формирование выходных радиоимпульсных сигналов под воздействием управляющего сигнала от коммутатора-формирователя 27 (см. фиг. 2,г). Радиоимпульсный сигнал от усилителя мощности 20, пройдя через антенный переключатель 21, излучается в пространство приëмопередающей антенной 28 (см. фиг. 2,е).

Сигнал, излучаемый в пространство ретранслятором 16 в течение времени Тр, пройдя через среду распространения, принимается приëмопередающей антенной 12 измерительного блока 1 и через антенный переключатель 5 поступает на вход смесителя 6, на второй вход которого подаются сигналы от синтезатора частот 3 с частотами (fОГ, f1Г, f2Г.fiГ) в соответствии с фиг. 2б. В смесителе 6 осуществляется преобразование принимаемого сигнала на частоту fПР (причем fО fОГ fПР, f1 f1Г fПР и т. п.), в усилителе промежуточной частоты 7 сигналы частотой fПР фильтруются и усиливаются, а затем нормируются по амплитуде в усилителе-ограничителе 8 и поступают на фазовый детектор 9. В фазовом детекторе 9 под воздействием управляющих сигналов (см. фиг. 2,б) осуществляется измерение фазовых сдвигов принятых сигналов, при этом измеряются фазовые сдвиги ϑ01, ϑ02, ϑoi, ϑoi' опорных сигналов частоты fО и фазовые сдвиги ϑ1, ϑ2, ϑi вспомогательных сигналов частотами f1, f2,fi.

Информация с фазового детектора 9 поступает в решающий блок 10. При этом, накапливая информацию в решающем блоке 10 об изменениях фазовых сдвигов Δ ϑ, например, для частоты fО, т. е. ϑ01, ϑ02, ϑoi за один или несколько циклов работы устройства Тц, можно определить отклонение Δ f частоты опорного генератора 2 от частоты опорного генератора 17 за время наблюдения Δ t за отклонением частоты генераторов. Код отклонения частоты опорного генератора 2 Δ f поступает от решающего блока 10 на вход управления опорного генератора 2, обеспечивая изменение его выходной частоты и уменьшая Δ f до нуля.

Кроме того, в решающем блоке 10 по измеренным данным ϑо, ϑ1, ϑiопределяются случайные составляющие погрешностей фазовых измерений за один или несколько циклов Тц работы устройства, величины которых используются затем в решающем блоке 10 для управления режимом фильтрации фазовых измерений в блоках 151 15к.

Информация с фазового детектора 9 поступает также на входы фильтров фазовых измерений 151 15к, причëм фазовые сдвиги опорных сигналов частоты fО(ϑ01, ϑ02, ϑoi, ϑoi') накапливаются в фильтре 151, фазовые сдвиги вспомогательных сигналов частоты f(ϑ 1) накапливаются в фильтре фазовые сдвиги сигналов частоты f2 (ϑ 2) в фильтре 153 и т. д. до частоты fi, для которой фазовые сдвиги ϑi накапливаются в фильтре 15к. В фильтрах фазовых измерений 151 15к осуществляется обработки первичных фазовых измерений, полученных за несколько циклов Тц работы устройства. При этом управление режимами работы фильтров фазовых измерений 151 15к осуществляется от решающего блока 10 через блок вывода 14.

Информация с выходов фильтров 151 15к (ϑо, ϑ1, ϑ2, ϑi) поступает через блок ввода 13 в решающий блок 10, в котором вычисляются фазовые соотношения -

- =

=  ,

,  -

- =

=

-

- =

=  , (3) где

, (3) где  ,

,  ,

, оценки фазовых сдвигов, полученные в результате обработки первичных фазовых измерений блоках 151 15к.

оценки фазовых сдвигов, полученные в результате обработки первичных фазовых измерений блоках 151 15к.

Управление приëмом информации с выходов фильтров 151 15косуществляется от решающего блока 10 через блок ввода 13.

Полученные значения фазовых сдвигов  , ΔΨ2,

, ΔΨ2,  запоминаются в решающем блоке 10, а затем используются в решающем блоке 10 для устранения многозначности фазовых отчетов. На практике частоты f0, f1, f2.fi выбираются таким образом, чтобы выполнялись соотношения f0 f1 F1, f0 f2 F2,f0 fi Fi, F1/F2 m2,F(i-1)/Fi= mi, где F1 частота точной ступени (рабочая частота устройства); F2, F3,Fi частота грубых ступеней; m1, m2,mi коэффициенты сопряжения частот.

запоминаются в решающем блоке 10, а затем используются в решающем блоке 10 для устранения многозначности фазовых отчетов. На практике частоты f0, f1, f2.fi выбираются таким образом, чтобы выполнялись соотношения f0 f1 F1, f0 f2 F2,f0 fi Fi, F1/F2 m2,F(i-1)/Fi= mi, где F1 частота точной ступени (рабочая частота устройства); F2, F3,Fi частота грубых ступеней; m1, m2,mi коэффициенты сопряжения частот.

Таким образом, величина фазового сдвига  с учетом коррекции при устранении многозначности соответствует сигналу частотой F1, прошедшего дважды через среду распространения, соответствует времени запаздывания радиоволн в точке приëма по отношению к моменту их излучения и может использоваться для точного определения расстояния (r) между антенной 12 измерительного блока 1 и антенной 28 ретранслятора 16 при известной скорости распространения радиоволн и измеренной величине

с учетом коррекции при устранении многозначности соответствует сигналу частотой F1, прошедшего дважды через среду распространения, соответствует времени запаздывания радиоволн в точке приëма по отношению к моменту их излучения и может использоваться для точного определения расстояния (r) между антенной 12 измерительного блока 1 и антенной 28 ретранслятора 16 при известной скорости распространения радиоволн и измеренной величине  по формуле

по формуле

r  (4) где С скорость распространения радиоволн.

(4) где С скорость распространения радиоволн.

При большой скорости движения объекта, на котором установлен измерительный блок 1 для повышения точности измерения фазовых сдвигов принимаемых сигналов, фильтры фазовых измерений 151 15к могут осуществлять обработку фазовых измерений, полученных в соответствии с выражениями (3) за несколько циклов работы устройства. Тогда в фильтре 151 накапливаются фазовые сдвиги  , в фильтре 152

, в фильтре 152 а в фильтре 15к

а в фильтре 15к , при этом вычисления по формулам (3) должны выполняться в соответствующих фильтрах 151 15к либо фазовом детекторе 9.

, при этом вычисления по формулам (3) должны выполняться в соответствующих фильтрах 151 15к либо фазовом детекторе 9.

Структурная схема варианта решающего блока 10 (26) приведена на фиг. 3. Дешифратор 33 обеспечивает выбор постоянного 30 или оперативного 31 запоминающего элемента, в котором хранится программа, константа или текущая информация соответственно. Микропроцессорный модуль 29 выполняет обработку и обмен информацией в соответствии с блок-схемой фиг. 4 и связан с блоками 30 33 шиной адреса (ША) и с блоками 30, 31, 34 40

информационной шиной данных (ШД), может иметь управляющие выходы с сигналами "чтение" и "запись" для управления постоянным 30 и оперативным 31 запоминающими элементами соответственно "вывод", например, для вывода информации по шине ШД в блоки 2, 3, 11, 13, 14, 18, 19, вход "запрос прерывания" для ввода информации в блок 10 (26) по сигналам от блока 9 (25), вход "ввод" для ввода информации от блока 13, сигналы обращения (вывода) со стороны блока 10 (26) к внешним блокам формируются путем дешифрирования кода адреса соответствующего регистра в дешифраторе 32 и коньюнкции его выходных сигналов с сигналом "вывод" в элементах И 41 47. По выходным сигналам элементов и 41 47 производится запись информации из микропроцессорного модуля 29 в регистры 34 40. При реализации решающего блока 10 (26) на базе микропроцессора К580 микропроцессорный модуль 29 состоит из трëх БИС-центрального процессора К580ИК80, системного контроллера К580ВК28, тактового генератора К580ГО24.

Структурная схема варианта фильтра фазовых измерений 151 15кприведена на фиг. 5. Устройство обеспечивает обработку первичных измерений фазовых сдвигов и при наличии во входном сигнале измерительного блока 1 различного рода помех обеспечивает повышение точности оценки фазовых сдвигов за счëт реализации алгоритмов фильтрации. Сигналы с выхода фазового детектора 9 подаются на буферный регистр 48 и логический элемент 55. От буферного регистра 48 коды данных поступают на вычислитель синусов 49 и вычислитель косинусов 50, представляющие, например, собой постоянное запоминающее устройство табличного типа. Вычисленные значения подаются в накопители 51 и 52 соответственно.

Сигнал от счëтчика 56 первичных оценок, управляющего числом накопленных данных, в течение нескольких циклов Тц работы устройства поступает на выходной регистр 53 и формирователь 57 сигнала готовности прерывания данных для вычислительного блока 54. Формирователь импульсов 55 обеспечивает ввод информации в регистр 48 и формирует сигнал готовности для блоков 51, 52, 56. Управление режимом работы фильтра 15 осуществляется от блока 14 путëм изменения циклов накопления благодаря предустановке счëтчика 56.

Блок ввода 13 (см. фиг. 6) выполняет функции обмена информацией между блоками 151 15к и решающим блоком 10. По сигналам управления от блока 10 "запись" информация с выходов блоков 151 15к переписывается в регистры 581 58к соответственно.

Затем по сигналам управления от блока 10 последовательно во времени считывается информация из регистров 581, 582,58к в решающий блок 10.

Блок вывода 14 (см. фиг. 7) обеспечивает обмен информацией между блоком 10 и блоками 151 15к, при этом сигналы обращения (вывода) со стороны блока 10 к блокам 151 15к формируются путëм дешифрирования кода адреса соответствующего регистра в дешифраторе 59 и коньюкции его выходных сигналов с сигналом "вывод" в элементах И 601 60к. По выходным сигналам элементов И 601 60к производится запись информации из блока 10 в регистры 611 61к.

Фазовые детекторы 9 (25) можно реализовать по известным схемам, либо на основе ортогональных фазоизмерителей ограниченных сигналов по структурной схема фиг. 8.

Прямоугольные импульсы с выхода ограничителя 8 или 24 частотой fпрподаются на элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 62, 65. Формирователь ортогонального сигнала 72 вырабатывает из сигналов опорного генератора 2 или 17 два прямоугольных квадратурных колебания частотой fпр, первое колебание поступает на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ62, второе, сдвинутое на 90о относительно первого, на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 65.

Элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 62 и 65 обеспечивают выполнение операций перемножения сигналов с выходов ограничителя и с выходов формирователя ортогонального сигнала 72. Импульсные последовательности с выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 62 и 65 поступают на управляющие входы счëтчиков 63 и 66 соответственно.

Сигналы с выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 62 и 65 используются для управления режимом работы счëтчиков 63 и 66, которые подсчитывают количество импульсов, поступающих от генератора импульсов 69 через элемент совпадения 70.

По окончании времени измерения t, формируемого формирователем импульсов 71, элемент совпадения 70 закрывается, коды чисел К1 и К2, накопленные в счëтчиках 63 и 66 соответственно за измерительный интервал, переписываются по сигналам управления от блока 71 в регистры 64 и 67 соответственно.

По сигналам управления от формирователя 71 в вычислительный блок 68 считывается измерительная информация последовательно из регистров 64, 67 (К1, К2). Счëтчики 63, 66 затем устанавливаются в исходное (нулевое) состояние сигналом от формирователя 71, элемент совпадения 70 открывается и цикл повторяется.

Вычислительный блок 68 вычисляет функцию арктангенса отношения измеренных величин, т.е.

ϕ arctg K1/K2, может вычислять также значение разности фаз.

Формирователи импульсов 55, 71 выполняют функции формирования управляющих сигналов, необходимых для организации обмена информацией между соответствующими блоками.

При практической реализации фазового детектора 9 (см. фиг. 8) счëтчики 63 и 66 могут быть выполнены в виде реверсивных или в виде суммирующих счëтчиков. В случае применения реверсивных счëтчиков 63 и 65 сигналы с выходов элементов 62 и 65 управляют режимом счëта, т. е. в моменты совпадения полярностей входных импульсов элементов 62 и 65 реверсивные счëтчики работают на суммирование, при несовпадении полярностей входных импульсов элементов 62 и 65 на вычитание.

При использовании суммирующих счëтчиков 63 и 66 в моменты совпадения полярностей входных импульсов элементов 62 и 65 счëтчики 63 и 66 суммируют импульсы, поступающие от генератора 69, при несовпадении полярностей входных импульсов элементов 62 и 65 не считают. Для вычисления фазового сдвига (в этом случае в вычислительном блоке 68) результаты, полученные за такт измерения в счëтчиках 63 и 66, центрируются, т. е. из этих результатов вычисляются поправки, равные половине известного количества импульсов генератора 69 за измерительный такт и вычисляется функция арктангенса отношения полученных величин.

Вычислительный блок 54, 68 может быть выполнен на основе микропроцессора по типовой структуре.

Управляемые синтезаторы частот 3 и 18 могут быть реализованы, например, аналогично синтезатору Ч6-31.

Коммутаторы-формирователи 11 и 27 могут быть выполнены в виде счëтчика, выходы которого соединены с адресными входами постоянного запоминающего устройства, хранящего значения кодов чисел, соответствующих временным диаграммам фиг. 2.

Переключатели 5, 21, могут быть выполнены, например, на pin-диодах или на микросхемах КР590КН4.

Формирователь ортогонального сигнала 72 может быть выполнен в виде трëх триггеров, работающих в режиме деления частоты на два, причëм к прямому и инверсному выходам первого триггера подключены входы второго и третьего триггеров соответственно. Тогда сигналы с выходов второго и третьего триггеров будут сдвинуты относительно друг друга на четверть периода выходной частоты.

Регистры 48, 53, 581 58к, 611 61к, 64, 67 могут быть выполнены, например, на микросхемах К155ИР15, К555ИР23 с тремя состояниями на выходе, что легко обеспечивает режим обмена информацией.

Таким образом, благодаря новым элементам и связям повышается точность измерения расстояния между измерительным блоком и ретранслятором при наличии помех за счëт обеспечения дополнительной фильтрации фазовых измерений на каждой из принимаемых частот устройства. Тогда предлагаемое устройство будет функционировать при воздействии на входной сигнал измерительного блока широкополосных и сосредоточенных по спектру помех.

В прототипе для определения информационного параметра устройства используется измерение фазовых сдвигов на каждой из принимаемых частот, по значениям которых осуществляется устранение многозначности фазовых отсчëтов и расчëт расстояния. При этом наличие помех в принимаемом сигнале приведëт к понижению точности определения расстояния, а также может привести к нарушению условий верного устранения многозначности фазовых отсчëтов и как следствие к сбоям в правильном определении расстояний. Такая работа измерительного блока возможна не только при наличии помех, но и при увеличении расстояния между измерительным блоком и ретранслятором на значительную величину, что приводит к уменьшению уровня принимаемого сигнала. Эти недостатки исключены в прилагаемом устройстве.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗЫ РАДИОСИГНАЛА | 1991 |

|

RU2048677C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ДВИЖЕНИЯ ОБЪЕКТОВ | 1992 |

|

RU2042144C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗЫ РАДИОСИГНАЛА | 1988 |

|

SU1600518A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗЫ РАДИОСИГНАЛА | 1992 |

|

RU2050552C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ПОГРЕШНОСТЕЙ РАДИОДАЛЬНОМЕРА | 1990 |

|

RU2048685C1 |

| ФАЗОВАЯ РАДИОГЕОДЕЗИЧЕСКАЯ СИСТЕМА | 1991 |

|

RU2088948C1 |

| ДАЛЬНОМЕРНАЯ СИСТЕМА С ИЗМЕРЕНИЕМ ФАЗЫ РАДИОСИГНАЛА | 1990 |

|

RU2076333C1 |

| Устройство для измерения амплитуды и фазы радиосигнала | 1989 |

|

SU1665811A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АМПЛИТУДЫ И ФАЗЫ РАДИОСИГНАЛА | 1988 |

|

SU1556370A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АМПЛИТУДЫ И ФАЗЫ РАДИОСИГНАЛА | 1987 |

|

SU1485851A1 |

Сущность изобретения: устройство для измерения фазы радиосигнала содержит измерительный блок 1, включающий опорный генератор 2, синтезатор частот 3, усилитель мощности 4, антенный переключатель 5, смеситель 6, усилитель промежуточный частоты 7, усилитель-ограничитель 8, фазовый детектор 9, решающий блок 10, коммутатор-формирователь 11, приемопередающую антенну 12, блок ввода 13, блок вывода 14 и К фильтров фазовых измерений 15, ретранслятор 16, включающий опорный генератор 17, синтезатор частот 18, фазовращатель 19, усилитель мощности 20, антенный переключатель 21, смеситель 22, усилитель промежуточной частоты 23, усилитель-ограничитель 24, фазовый детектор 25, решающий блок 26, коммутатор-формирователь 27 и приемопередающую антенну 28. 2-3-4-12-6-7-8-9-15-13-10-11-9-10-13, 10-14-15, 11-5-12, 2-11-4, 2-9, 14-15-13, 10-3, 25-26-18-19-20-21-22-23-24-25, 17-18-22, 27-20, 27-21, 27-25, 17-25. 8 ил.

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗЫ РАДИОСИГНАЛА, содержащее измерительный блок, включающий опорный генератор, коммутатор-формирователь, последовательно соединенные усилитель мощности, антенный переключатель, смеситель, усилитель промежуточной частоты, амплитудно-фазовый измеритель, выход опорного генератора соединен с вторым входом амплитудно-фазового измерителя и первым входом коммутатора-формирователя, выходы которого соединены с управляющими входами усилителя мощности, амплитудно-фазового измерителя и антенного переключателя, соединенного с приемнопередающей антенной, ретранслятор, включающий опорный генератор, коммутатор-формирователь, последовательно соединенные усилитель мощности, антенный переключатель, смеситель, усилитель промежуточной частоты, амплитудно-фазовый измеритель, выход опорного генератора соединен с вторым входом амплитудно-фазового измерителя и входом коммутатора-формирователя, выходы которого соединены с управляющими входами амплитудно-фазового измерителя, усилителя мощности и антенного переключателя, соединенного с приемопередающей антенной, отличающееся тем, что в измерительный блок введены синтезатор частот, решающий блок, блок ввода, блок вывода и K фильтров фазовых измерений, первый и второй выходы решающего блока соединены с управляющими входами коммутатора-формирователя и синтезатора частот, вход которого соединен с выходом опорного генератора, выходы с входом усилителя мощности и вторым входом смесителя соответственно, выход амплитудно-фазового измерителя соединен с первым входом решающего блока и входами K фильтров фазовых измерений, выходы которых соединены с информационными входами блока ввода, выход которого соединен с вторым входом решающего блока, третий, четвертый и пятый выходы которого соединены с управляющим входом опорного генератора и входами блока ввода и блока вывода, выходы которого соединены с входами управления K фильтров фазовых измерений, а в ретранслятор введены последовательно соединенные решающий блок, синтезатор частот и фазовращатель, выход которого соединен с входом усилителя мощности, выход амплитудно-фазового измерителя соединен с входом решающего блока, выход которого соединен с управляющим входом фазовращателя, выход опорного генератора соединен с входом синтезатора частот, второй выход которого соединен с вторым входом смесителя.

| Устройство для измерения амплитуды и фазы радиосигнала | 1977 |

|

SU734592A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1995-11-20—Публикация

1991-12-03—Подача