Изобретение относится к измерительной технике и может быть использовано при создании измерительных систем в геодезии.

Известно устройство для измерения амплитуды и фазы радиосигнала, включающее измерительный блок, состоящий из последовательно соединенных задающего генератора, усилителя мощности, антенного переключателя, соединенного с приемопередающей антенной, приемника и амплитудно-фазового измерителя, второй вход которого подключен к второму выходу задающего генератора, а также генератора низкой частоты и расположенного между выходом генератора низкой частоты и вторыми входами антенного переключателя коммутатора-формирователя, вторые выходы которого подключены к вторым входам усилителя мощности, и ретранслятор, содержащий последовательно соединенные задающий генератор, усилитель мощности, антенный переключатель, соединенный с приемопередающей антенной, приемник и блок автоматической подстройки фазы, выход которого подключен к входу задающего генератора, а также расположенные между вторым выходом блока автоматической подстройки фазы и вторыми входами антенного переключателя последовательно соединенные генератор низкой частоты и коммутатор-формирователь, вторые выходы которого подключены к усилителю мощности, а третьи к приемнику, и расположенный между вторым выходом задающего генератора и вторым входом блока автоматической подстройки фазы амплитудно-фазовый измеритель, второй вход которого соединен с вторым выходом приемника.

Недостатком устройства является низкая точность измерения информационного параметра при изменении уровней входных сигналов измерительного блока и ретранслятора.

Целью изобретения является повышение точности измерения путем учета погрешностей, возникающих в узлах аппаратуры при изменении уровней входных сигналов в широких пределах.

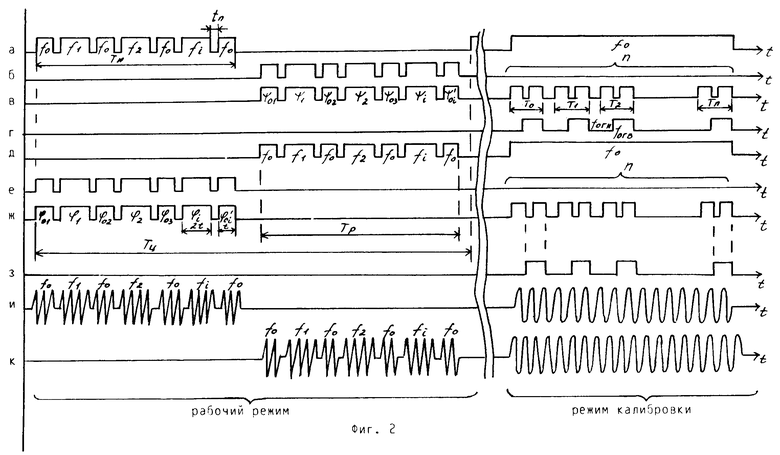

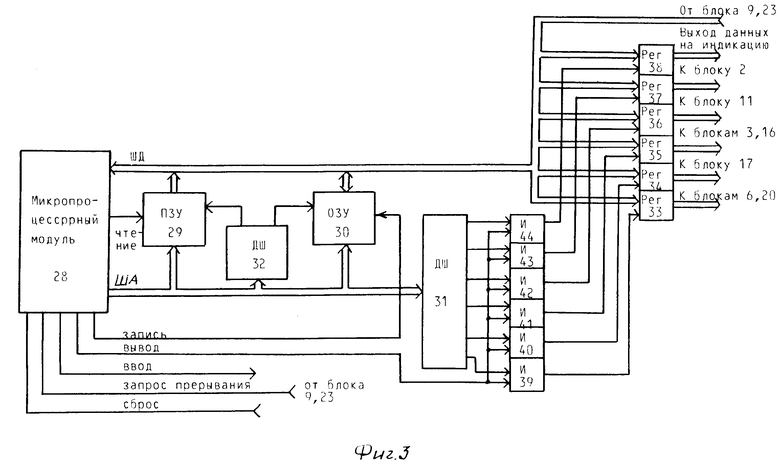

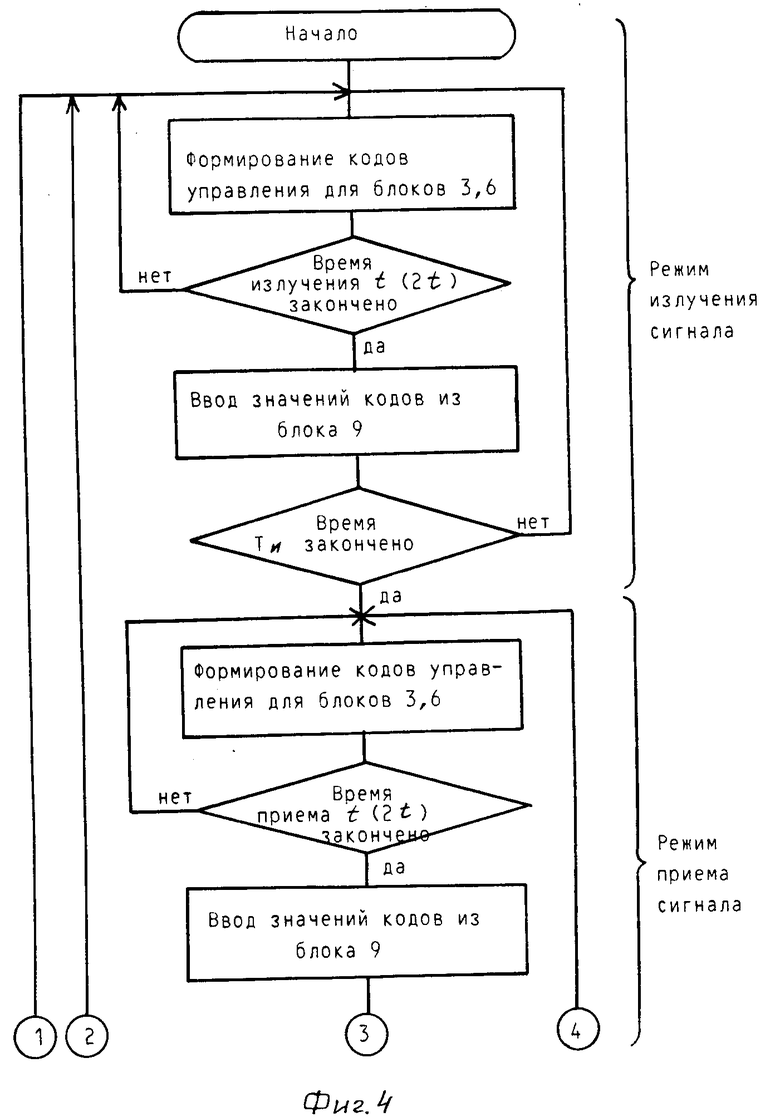

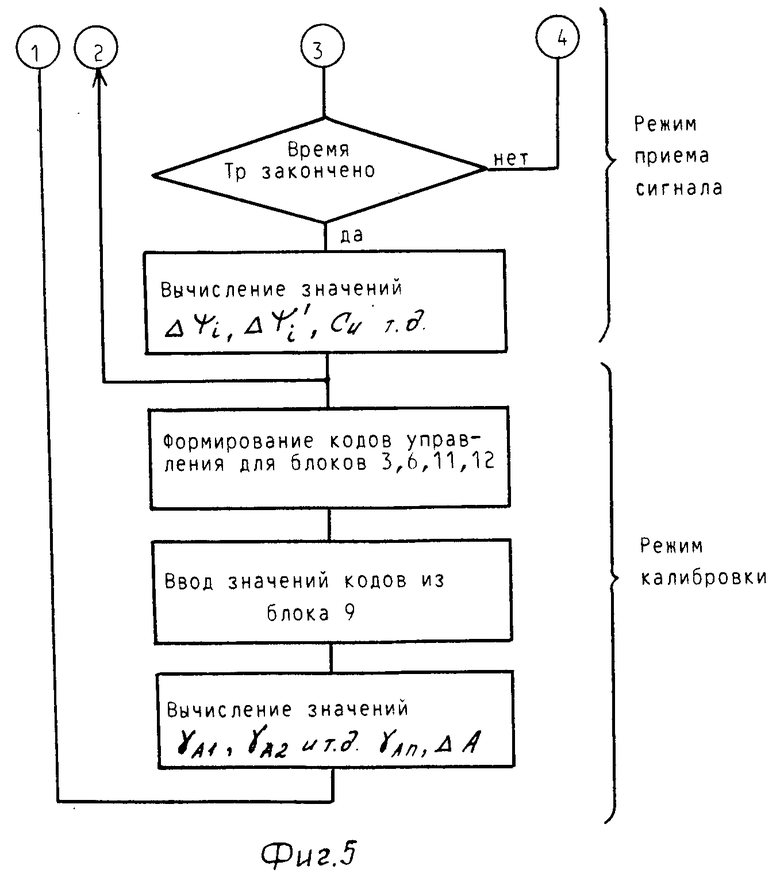

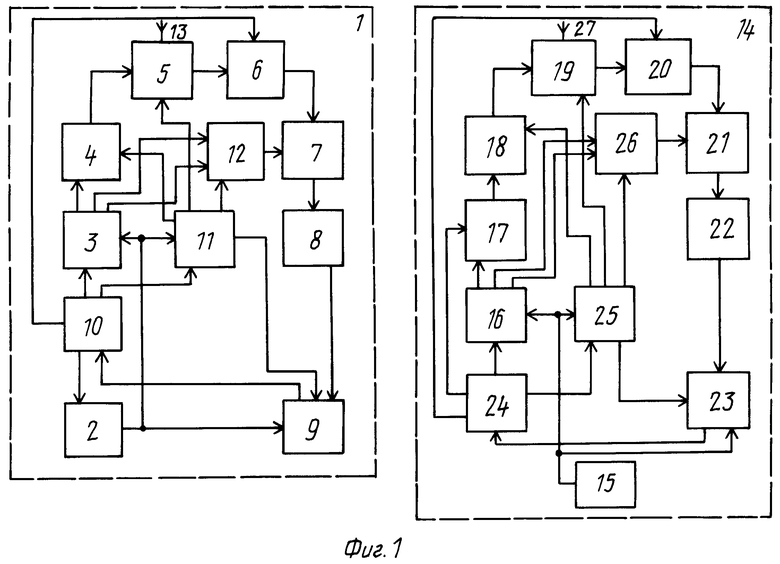

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 временные диаграммы, поясняющие его работу; на фиг.3 вариант выполнения решающего блока; на фиг.4 и 5 блок-схема алгоритма его работы в измерительном блоке; на фиг.6 и 7 варианты выполнения амплитудно-фазового измерителя; на фиг.8 вариант выполнения синтезатора частот.

Устройство содержит измерительный блок 1, состоящий из последовательно соединенных опорного генератора 2, синтезатора частот 3, усилителя мощности 4, антенного переключателя 5, аттенюатора 6, смесителя 7, усилителя промежуточной частоты 8, амплитудно-фазового измерителя 9, решающего блока 10, коммутатора-формирователя 11 и коммутатора 12, входы которого соединены с синтезатором частот 3, а выход с входом смесителя 7, выходы опорного генератора 2 соединены с амплитудно-фазовым измерителем 9 и коммутатором-формирователем 11, выходы которого соединены с усилителем мощности 4, амплитудно-фазовым измерителем 9, коммутатором 12 и антенным переключателем 5, соединенным с приемопередающей антенной 13, выходы решающего блока 10 соединены с входами управления опорного генератора 2, синтезатора частот 3 и аттенюатора 6, ретранслятор 14, содержащий последовательно соединенные опорный генератор 15, синтезатор частот 16, фазовращатель 17, усилитель мощности 18, антенный переключатель 19, аттенюатор 20, смеситель 21, усилитель промежуточной частоты 22, амплитудно-фазовый измеритель 23 и решающий блок 24, выходы которого соединены с входами управления синтезатора частот 16, фазовращателя 17 и аттенюатора 20, выходы опорного генератора 15 соединены с амплитудно-фазовым измерителем 23, синтезатором частот 16, и коммутатором-формирователем 25, выходы которого соединены с амплитудно-фазовым измерителем 23, усилителем мощности 18, антенным переключателем 19 и коммутатором 26, входы которого соединены с синтезатором частот 16, а выход с входом смесителя 21, антенный переключатель 19 соединен с приемопередающей антенной 27.

Решающий блок 10 (24) содержит (см. фиг.3) микропроцессорный модуль 28, шина адреса которого соединена с адресными входами постоянного запоминающего элемента 29, оперативного запоминающего элемента 30 и входами дешифраторов 31 и 32, выходы которого соединены с управляющими входами запоминающих элементов 29 и 30, управляющие выходы микропоцессорного модуля 28 "чтение", "запись" соединены с входами управления постоянного 29 и оперативного 30 запоминающих элементов соответственно, информационные входы-выходы микропроцессорного модуля 28 соединены с выходами постоянного запоминающего элемента 29, с информационными входами-выходами оперативного запоминающего элемента 30, с входами регистров 33-38, выходы дешифратора 31 соединены через элементы И 39-44 с входами управления регистров 33-38.

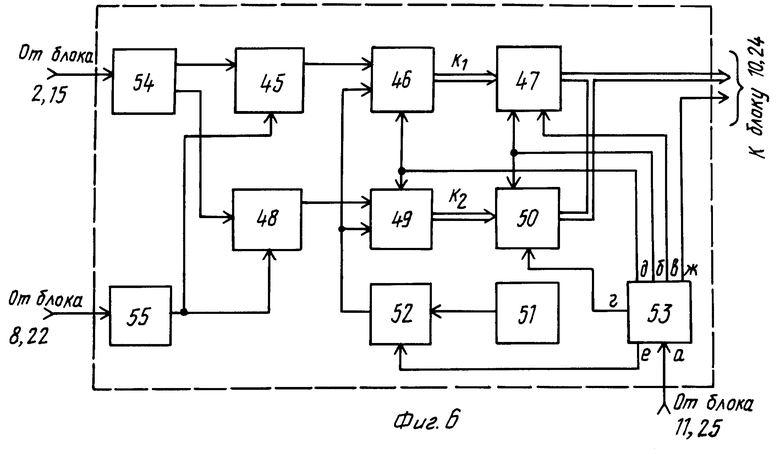

Амплитудно-фазовый измеритель 9 (23) содержит (см. фиг.6) последовательно соединенные элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 45, счетчик 46 и регистр 47, последовательно соединенные элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 48, счетчик 49 и регистр 50, генератор импульсов 51, соединенный через элемент И 52 со счетными входами счетчиков 46 и 49, формирователь импульсов 53, соединенный со счетчиками 46, 49, регистрами 47, 50, элементом И 52, формирователь ортогонального сигнала 54, соединеный с элементами ИСКЛЮЧАЮЩЕЕ ИЛИ 45, 48, ограничитель 55, соединенный с элементами ИСКЛЮЧАЮЩЕЕ ИЛИ 45, 48. Входы формирователя ортогонального сигнала 54, ограничителя 55, формирователя импульсов 53 являются входами амплитудно-фазового измерителя, а выходы регистров 47, 50 и выход формирователя импульсов 53 его выходом.

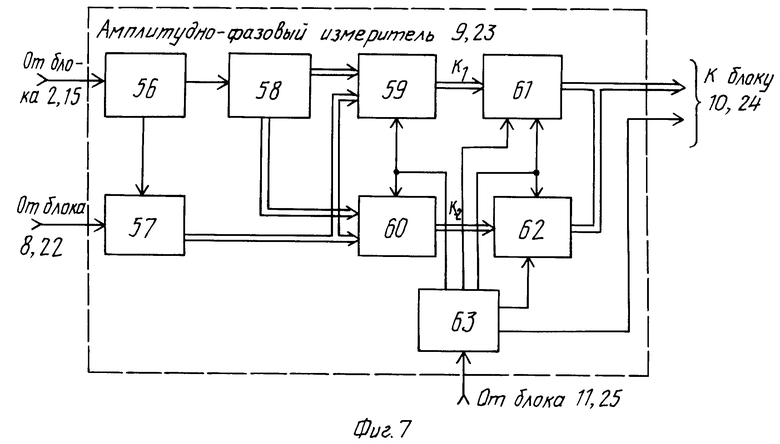

Кроме того, амплитудно-фазовый измерител 9 (23), реализованный по схеме, показанной на фиг.6, содержит блок синхронизации 56, аналого-цифровой преобразователь 57, постоянное запоминающее устройство 58, перемножители 59, 60, регистры 61, 62, формирователь импульсов 63.

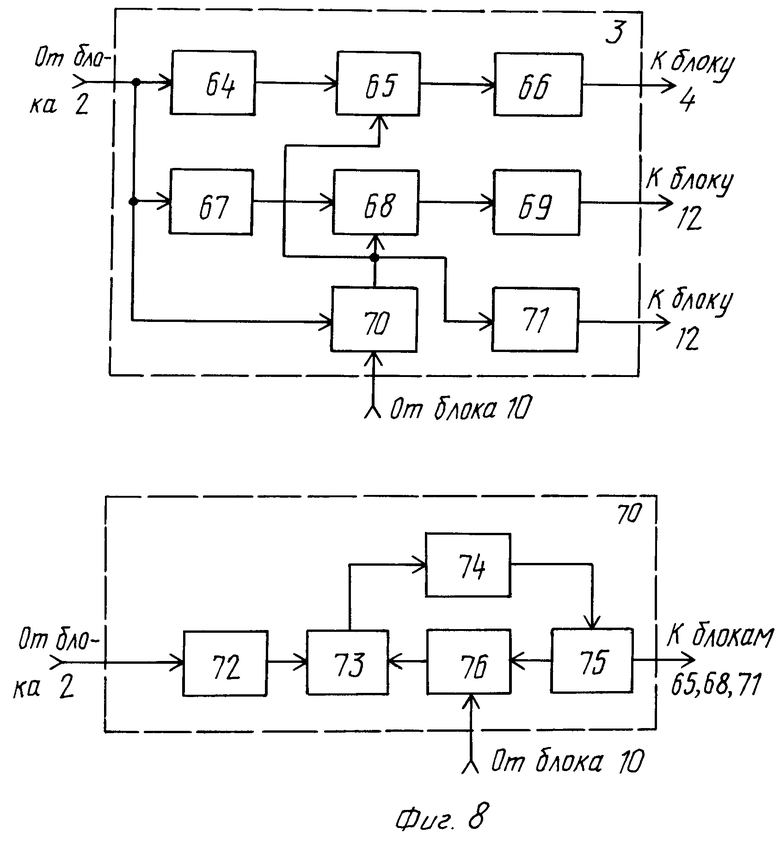

Синтезатор частот 3 (16) содержит (см. фиг.8) последовательно соединенные делитель частоты 64, смеситель 65 и фильтр 66, последовательно соединенные делитель частоты 67, смеситель 68 и фильтр 69, перестраиваемый генератор 70, выход которого соединен с входами смесителей 65 и 68, входом фильтра 71, причем перестраиваемый генератор 70 содержит последовательно соединенные делитель частоты 72, фазовый детектор 73, фильтр 74, управляемый генератор 75 и делитель с переменным коэффициентом деления 76, выход которого соединен с фазовым детектором 73.

Работает устройство следующим образом.

Опорные генераторы 2, 15 вырабатывают непрерывные гармонические сигналы частотой f, которые поступают на коммутаторы-формирователи 11, 25 и синтезаторы частот 3, 16. Синтезаторы частот 3 и 16 вырабатывают для излучения опорный сигнал частотой fo и несколько вспомогательных сигналов частотами f1, f2,fi, кроме того, в синтезаторах частот 3 и 16 формируются сигналы гетеродина для смесителей 7 и 21 частотой fогн, fогв, f1г, f2г,fiг, при этом управление частотой излучаемых (принимаемых) сигналов осуществляется решающим блоком 10 (24), причем fo- fогн fпр, f1 f1г= fпр, f2 f2г fпр, fifiг fпр, fогв fo= fпр, где fпр промежуточная частота, выделяемая блоками 8, 22, на которой осуществляется измерение фазы прринятых сигналов.

Коммутаторы-формирователи 11 и 25 вырабатывают сигналы управления для блоков 4 (см. фиг.2,а), 5 (см.фиг.2,б) 9 (см. фиг.2,в), 12 (см. фиг.2г) и соовтетствующих блоков ретранслятора 18 (см. фиг.2,д), 19 (см. фиг.2,е), 23 (см. фиг.2,ж), 26 (см. фиг.2,з). Временные диаграммы на фиг.2 приведены для установившегося рабочего режима устройства, когда временные интервалы излучения и приема сигналов измерительного блока 1 синхронизированы с соответствующими интервалами ретранслятора 14 (Тц временной цикл работы устройства; t интервал излучения (приема) опорного сигнала частотой fo; 2t интервал излучения (приема) вспомогательных сигналов с частотами fi; tп длительность паузы; Ти, Тр- временные циклы, в течение которых измерительный блок 1 и ретранслятор соответственно работают на излучение сигналов в пространство; То, Т1,Ти временные интервалы, формируемые в режиме калибровки для измерения погрешностей аттенюаторов.

На фиг.2а изображены временные диаграммы, показывающие, что для рабочего режима в течение интервала времени Ти осуществляется управление работой усилителя мощности 4, при котором в течение интервалов времени t блок 4 усиливает сигналы частотой fo, в течение интервалов времени 2t блок 4 усиливает сигналы частотами f1, f2, fi. На фиг.2,б изображены временные диаграммы, показывающие, что для рабочего режима в течение интервала Ти блок 5 включен на передачу сигнала от блока 4 к приемопередающей антенне 13, а в интервале от времени Тр блок 5 включен на передачу сигнала от антенны 13 через аттенюатор 6 к смесителю 7 в течение интервала времени t и 2t.

На фиг.2в изображены временные диаграммы, показывающие, что для рабочего режима в течение интервалов времени t и 2t осуществляется измерение фазовых сдвигов Ψ01,Ψ1,Ψ02 и т.д. в блоке 9.

На фиг.2ж изображены временные диаграммы, показывающие, что для рабочего режима в течение интервалов времени t и 2t осуществляется измерение фазовых сдвигов ϕ01,ϕ1и т.д. в блоке 23.

Кроме того, на фиг.2в,ж приведены сигналы управления для амплитудно-фазовых измерителей 9 и 23 соответственно в режиме калибровки устройства. Причем в течение первой половины интервала То(Т1.Ти) на смеситель 7 (21) поступает с коммутатора 12 (26) сигнал частотой fогн(см. фиг.2г, з), в течение второй половины интервала То (Т1,Ти) на смеситель 7 (21) поступает с коммутатора 12 (26) сигнал частотой fогв(см. фиг.2,г,з).

В усилителе мощности 4 осуществляется усиление сигналов от синтезатора частот 3 до необходимой величины и формирование выходных радиоимпульсных сигналов под воздействием управляющего сигнала от коммутатора-формирователя 11 (см. фиг.2,а). Радиоимпульсный сигнал от усилителя мощности 4, пройдя через антенный переключатель 5, излучается в пространство приемопередающей антенной 13 (см. фиг.2,и).

Сигнал, излучаемый в пространство измерительным блоком 1 в течение времени Ти, пройдя через среду распространения, принимается приемопередающей антенной 27 ретранслятора 14 и через антенный переключатель 19, аттенюатор 20 поступает на вход смесителя 21. На второй вход смесителя 21 подаются сигналы от синтезатора частот 16 через коммутатор 26 частотами (fогн, fогв, f1г, f2г..fiг) в соответствии с фиг.2а. В смесителе 21 осуществляется преобразование принимаемого сигнала на частоту fпр (причем fo-fогн fпр, f1-f1г= fпр и т.д.), в усилителе промежуточной частоты 22 сигналы частотой fпр фильтруются, усиливаются и поступают на амплитудно-фазовый измеритель 23. В амплитудно-фазовом измерителе 23 под воздействием управляющих сигналов осуществляется измерение фазовых сдвигов принятых сигналов, при этом измеряются фазовые сдвиги ϕ01,ϕ02. ϕ0i,ϕ0iI опорных сигналов частоты fo и фазовые сдвиги ϕ1,ϕ2,ϕi (см. фиг.2,ж) вспомогательных сигналов частотами f1, f2.fi. Информация с амплитудно-фазового измерителя 23 поступает в решающий блок 24, в котором вычисляются фазовые соотношения в течение интервалов tп:

(1)

(1)

ϕ1I-ϕ1=Δ ϕ1,ϕ2I-ϕ2=Δ ϕ2,ϕiI-ϕi=Δ ϕi (2)

Полученные значения фазы Δ ϕi,Δ ϕ2,Δ ϕi запоминаются в решающем блоке 24. В течение интервала Тризлучаются в пространство сигналы от ретранслятора 14, при этом управление частотой и фазой излучаемых сигналов осуществляется решающим блоком 24 через блоки 16 и 17 соответственно. В моменты времени t, когда ретранслятором 14 излучаются в пространство основные сигналы частотой fo, фазовращатель 17 решающим блоком 24 установлен в исходное (нулевое) состояние, тогда излучаемые опорные сигналы частотой fo имеют фазу сигнала частотой f опорного генератора 15. В течение интервалов 2t, когда ретранслятором 14 излучаются в пространство вспомогательные сигналы частотами f1, f2, fi, сигналами управления от решающего блока 24 устанавливаются в фазовращателе 17 фазовые сдвиги Δ ϕ1I,Δ ϕ2I,Δ ϕiIсоответственно. Здесь: Δ ϕ1I=Δ ϕ1-θ, Δ ϕ2I, Δ ϕ2-θ,Δ ϕiI=Δ ϕi-θ, θ- фазовые сдвиги, возникающие в аппаратуре ретранслятора 14 и вычисляются в решающем блоке 24 в режиме калибровки).

Таким образом, в течение интервала Тр ретранслятор 14 излучает вспомогательные сигналы, фаза которых равна фазе принятых сигналов в течение интервалов Ти от измерительного блока 1, и не содержит фазовых набегов, обусловленных аппаратурой ретранслятора 14, а также опорных сигналов, фаза которых равна фазе опорного генератора 15. В усилителе мощности 16 осуществляется усиление сигналов от фазовращателя 17 и формирование выходных радиоимпульсных сигналов под воздействием управляющего сигнала от коммутатора-фор- мирователя 25 (фиг. 2д). Радиоимпульсный сигнал от усилителя мощности 18, пройдя через антенный переключатель 19, излучается в пространство приемопередающей антенной 27 (см. фиг.2,к).

Сигнал, излучаемый в пространство ретранслятором 14 в течение времени Тр, пройдя через среду распространения, принимается приемоперадающей антенной 13 измерительного блока 1 и через антенный переключатель 5, аттенюатор 6 поступает на вход смесителя 7, на второй вход которого подаются сигналы от синтезатора частот 3 частотам (fогв, fогн, f1г, f2г,fiг) в соответствии с фиг. 2к. В смесителе 7 осуществляется преобразование принимаемого сигнала на частоту fпр(причем fo-fогн= fпр, f1-f1г= fпр и т.п.) в усилителе промежуточнрой частоты 8 сигналы частотой fпр фильтруются, усиливаются и поступают на амплитудно-фазовый измеритель 9. В амплитудно-фазовом измерителе 9 под воздействием управляющих сигналов (см. фиг.2,в) осуществляется измерение фазовых сдвигов принятых сигналов, при этом измеряются фазовые сдвиги Ψ01, Ψ02,Ψ0i,Ψ0iI опорных сигналов частоты fо и фазовые сдвиги Ψ1,Ψ2, Ψiвспомогательных сигналов частотами f1, f2,fi. Информация с фазового детектора 9 поступает в решающий блок 10, в котором вычисляются фазовые соотношения:

(3)

(3)

Ψ1I-Ψ1=Δ Ψ1,Ψ2I-Ψ2=Δ Ψ2,ΨiI-Ψi=Δ Ψi (4)

Полученные значения фазовых сдвигов Δ Ψ1,Δ Ψ2,Δ Ψiзапоминаются в решающем блоке 10, затем в решающем блоке 10 вычисляются фазовые сдвиги Δ Ψ1I=Δ Ψ1-γ, Δ Ψ2I= Δ Ψ2-γ, Δ ΨiI=Δ Ψi-γзначения которых используются в решающем блоке 10 для устранения многозначности фазовых отсчетов γ- фазовые сдвиги, возникающие в аппаратуре измерительного блока 1, и вычисляются в решающем блоке 10 в режиме калибровки блока 1. На практике частоты fo, f1, f2,fi выбиратся так, чтобы выполнялись соотношения

fo-f1=F1, fo-f2=F2, fo fi=Fi,

F1/F2= m1, F2/F3=m2,F(i-1)/Fi=mi где F1 частота точной ступени (рабочая частота устройства);

F2, F3,Fi частоты грубых ступеней,

m1,m2,mi коэффициенты сопряжения частот.

Таким образом, величина фазового сдвига Δ Ψ1I с учетом коррекции при устранении многозначности соответствует сигналу частотой F1, прошедшего дважды через среду распространения, равна времени запаздывания радиоволны в точке приема по отношению к моменту их излучения, не содержит фазовых набегов, обусловленных аппаратурой ретранслятора и измерительнрого блока и может использоваться для точного определения расстояния (r) между антенной 13 измерительного блока 1 и антенной 27 ретранслятора 14 при известной скорости распространения радиоволны и измеренной величине Δ Ψ1I по формуле

r  (5) где С скорость распространения радиоволны.

(5) где С скорость распространения радиоволны.

В случае, если опорные генераторы 2 и 15 имеют недостаточную долговременную стабильность частоты, в измерительном блоке 1, накапливая информацию в решающем блоке 10 об изменениях фазовых сдвигов Δ Ψ, например, для частоты fo, т.е. Ψ01, Ψ02 Ψ0i за один или несколько циклов работы устройства Тц можно определить отклонение Δ f частоты опорного генератора 2 от частоты опорного генрератора 15 за время наблюдения Δ t за отклонением частоты генераторов. Код отклонения частоты опорного генератора 2 Δ f поступает от решающего блока 10 на вход управления опорного генератора 2, обеспечивая изменение его выходной частоты и уменьшая Δ f до нуля. Формирование двух интервалов излучения (приема) для опорной частоты fo относительно каждого интервала излучения (приема) для вспомогательных частот f1, f2 и т.д. позволяет повысить точность измерения информационных параметров фазовых сдвигов принимаемых сигналов при последовательном излучении сигналов во времени и большой скорости движения объекта.

Кроме описанных операций, решающие блоки 10 и 24 осуществляют управление дискретными аттенюаторами 6 и 20 соответственно. При этом в первом цикле работы устройства аттенюаторы 6, 20 устанавливаются в нулевое ослабление принимаемых сигналов. В амплитудно-фазовых измерителях 9, 23 и решающих блоках 10, 24 измеряются уровни принимаемых сигналов от ретранслятора 14 и измерительного блока 1 соответственно и сравниваются с выбранными пороговыми значениями. При превышении уровней принимаемых сигналов максимального заданного порогового значения в решающих блоках 10, 24 формируются сигналы управления, под действием которых вводятся соответствующие дискретные значения ослаблений в аттенюаторах 6 и 20. При уменьшении уровней принимаемых сигналов ниже минимального выбранного порогового значения в решающих блоках 10, 24 формируются сигналы управления, уменьшающие ослабления, вносимые аттенюаторами 6 и 20 соответственно.

Таким образом, решающие блоки 10 и 24 осуществляют с помощью дискретных аттенюаторов 6 и 20 автоматическое регулирование уровней входных сигналов, поступающих на входы смесителей 7 и 21 при изменении уровней входных сигналов измерительного блока 1 и ретранслятора 14 в широких пределах.

Однако дискретные аттенюаторы 6, 20 вносят дополнительные фазовые сдвиги при изменении уровней ослабления, что приводит к снижению точности измерения информационного параметра устройства ( Δ Ψ1I). Для повышения точности измерения при изменении уровней входных сигналов измерительнрого блока 1 и ретранслятора 14 в широких пределах в предлагаемом устройстве предусмотрен дополнительный учет фазовых сдвигов, возникающих в аппаратуре измерительнго блока 1 (γ) и ретранслятора 14 (θ).

С этой целью в измерительном блоке 1 и ретрансляторе 14 выполняется режим калибровки, при котором усилители мощности 4 и 16 переводятся в непрерывное излучение сигналов частотой fo, а коммутаторы-формирователи 11, 25 обеспечивают формирование сигналов управления для блоков 9, 23 и для коммутаторов 12, 26 в соответствии с фиг.2в, ж, з соответственно.

В течение времени калибровки по сигналам с решающих блоков 10 и 24 задаются последовательно n дискретных значений ослаблений аттенюаторов 6 и 20 соовтетственно от нуля до максимального значения, причем в течение первой половины интервалов То Ти на смеситель 7 (21) поступает с коммутатора 12 (26) сигнал частотой fогн, в течение второй половины интервалов То-Ти на смеситель 7 (21) подается сигнал частотой fогв. Здесь fогн=fo-fпр, fогв= fo-fпр соответственно нижняя и верхняя частоты преобразования частоты fo в смесителе 7 (21), То, Т1, Т2,Тп соответствуют временным интервалам, когда введено нулевое, первое, второе и т.д. ослабления аттенюатора 6 (20), Ти временной интервал, когда введено максимальное ослабление аттенюатора 6 (20).

В амплитудно-фазовом измерителе 9 (23) имзеряются при этом фазовые сдвиги, которые можно представить для интервала То в виде

γ70+γ80=γ0I

(6)

γ70+γ80+γn= γ0II где γn- фазовый сдвиг в аппаратуре измерительного блока 1, возникающий из-за измерений на нижней и верхней частотах гетеродина (fогн) и (fогв), может быть определен в решающем блоке 10 по формуле

γ0II-γ0I=γn (7)

Для первой точки ослабления аттенюатора 6 (20) фазовые сдвиги, измеренные в блоках 9 (23) в течение интервала Т1 при двух значениях частоты гетеродина fогн и fогв можно записать в виде

γA1+γ71+γ81=γ1I

(8)

-γA1+γ71+γ81+γn=γ1II

Тогда фазовый сдвиг аттенюатора 6 для первой точки ослабления рассчитывается в решающем блоке 10 по данным формул (7) и (8): γA1 (9) где γ70,γ71и γ80,γ81. фазовые сдвиги, возникающие для нулевого, первого и т.д. ослаблений сигнала в блоках 7 и 8 соответственно.

γA1 (9) где γ70,γ71и γ80,γ81. фазовые сдвиги, возникающие для нулевого, первого и т.д. ослаблений сигнала в блоках 7 и 8 соответственно.

Для второй точки ослабления аттенюатора 6 и измерений в течение Т2на частотах fогн и fогв фазовых сдвигов аппаратуры получим в решающем блоке 10 фазовый сдвиг аттенюатора 6 в виде

γA2+γ72+γ82=γ2I

(10)

-γA2+γ72+γ82+γn=γ2II γA2

γA2

Аналогично определяются фазовые сдвиги аттенюатора 6 (20) в 3, 4, и точках ослабления (γA3,γA4,γAn). Полученные значения фазовых сдвигов аттенюатора 6 (20) запоминаются в решающем блоке 10 (24). На практике для многочастотных радиодальномеров всегда выполняются неравенства fo >> F1, f1 >> F1, тогда по значениям γA1,γA2,γAnопределенным для рабочей частоты fо, можно вычислять в решающем блоке 10, например, также величины Δ γA12=γA1-γA2, Δ γA13= γA1-γA3и т.д. и использовать их для уточнения фазовых сдвигов, вносимых узлами измерительного блока 1 при изменении уровней входных сигналов устройства в широких пределах для всех рабочих частот измерительного блока 1.

Таким образом достигается повышение точности измерения устройства за счет автоматического измерения и учета фазовых погрешностей, возникающих в аттенюаторах 6 (20) при изменении уровней входных сигналов измерительного блока и ретранслятора в широких пределах.

Аналогичные измерения выполняются автоматически в ретрансляторе 14, при этом определяются соответственно величины θA1, θA2, θAn по формулам (6) (10), а также Δ θA12=θA1-θA2, Δ θA13=θA1-θA3и т.д. запоминаются в решающем блоке 24.

Измерение фазовых сдвигов аттенюаторов 6 (20) может выполняться не только на частоте fo, но и на всех рабочих частотах устройства, однако это приведет к значительному усложнению синтезатора частот 3 (16), увеличению памяти решающего блока 10 (24), увеличению продолжительности режима калибровки устройства, что на практике не всегда целесообразно.

Описанный режим калибровки может выполняться перед началом работы устройства, а также повторяться автоматически с заданным циклом и обеспечивает автоматическое измерение фазовых сдвигов γA, θA, Δ γAи Δ θAаттенюаторов 6 (20) при изменении уровней входных сигналов устройства в широких пределах.

Амплитудно-фазовые измерители 9, 23 можно реализовать на основе ортогональных фазоизмерителей ограниченных сигналов по структурной схеме на фиг. 6. Сигналы частотой fпр с выхода усилителя промежуточной частоты 8 (22) подаются на ограничитель 55.

Прямоугольные импульсы с выхода ограничителя 55 подаются на элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 45, 48. Формирователь ортогонального сигнала 54 вырабатывают из сигналов опорного генератора 2 и 15 два прямоугольных квадратурных колебания частотой fпр, первое колебание поступает на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 45, второе, сдвинутое на 90о относительно первого, на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 48. Элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 45 и 48 обеспечивают выполнение операций перемножения сигналов с выходов ограничителя и с выходов формирователя ортогонального сигнала 54. Импульсные последовательности с выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 45 и 48 поступают на управляющие входы счетчиков 46 и 49 соответственно.

Сигналы с выходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 45 и 48 используются для управления режимом работы счетчиков 46 и 49, которые подсчитывают количество импульсов, поступающих от генератора импульсов 51 через элемент совпадения 52. По окончании времени измерения t (2t), формируемого формирователем импульсов 53, элемент совпадения 52 закрывается, коды чисел К1 и К2, накопление в счетчиках 46 и 48 соответственно за измерительный интервал, переписываются по сигналам управления от блока 53 и регистры 47 и 50 соответственно.

По сигналам управления от блока 53 в решающий блок 10 (24) в соответствии с блок-схемой алгоритма его работы считывается измерительная информация последовательно с регистров 47, 50 К1, К2. Счетчики 46 и 49 затем устанавливаются в исходное (нулевое) состояние сигналом от блока 53, элемент совпадения 52 открывается и цикл повторяется.

Решающий блок 10 (24) вычисляет функцию арктангенса отношения измеренных величин, т.е.

ϕ= arctg K1/K2 (11)

Кроме измеренного фазового сдвига, в решающем блоке 10 (24) может вычисляться также уровень принимаемого сигнала устройства при соотношении сигнал/шум меньше единицы на входе блока 9 по формуле

C  (12) значения которого могут использоваться для управления дискретным аттенюатором 6 (20).

(12) значения которого могут использоваться для управления дискретным аттенюатором 6 (20).

Для обеспечения измерения амплитуд входных сигналов с высокой точностью целесообразно амплитудно-фазовый измеритель 9, 23 реализовать по схеме, приведенной на фиг.7. При этом в аналого-цифровом преобразователе 57 осуществляется преобразование входных сигналов в цифровые коды. Перемножение кодов значений измеряемого сигнала на синусные и косинусные значения кодов опорного сигнала, хранящиеся в постоянном запоминающем устройстве 56 и суммирование результатов перемножения производится перемножителями 59, 60 соответственно. По окончании времени измерения t(2t), формируемого формирователем импульсов 63, коды чисел К1 и К2, накопленные в перемножителях 59 и 60 соответственно за измерительный интервал, переписываются по сигналам управления от блока 63 в регистры 61 и 62 соответственно. По сигналам управления от блока 63 в решающий блок 10 (24) в соответствии с блок-схемой алгоритма его работы считывается измерительаня информация последовательно с регистров 61, 62 К1, К2. В решающем блоке 10 (24) вычисляются функции измеренных величин по формулам (11) и (12). Блок синхронизации 56 обеспечивает синхронизацию работы блоков 57 и 58 по времени.

Структурная схема варианта решающего блока 10 (24) приведена на фиг.3. Дешифратор 32 обеспечивает выбор постоянного 29 или оперативного 30 запоминающих элементов, в которых хранятся программы, констранты или текущая информация соответственно. Микропроцессорный модуль 28 выполняет обработку и обмен информацией в соответствии с блок-схемой на фиг.4 и 5 и связан с блоками 29-32 шиной адреса (ША) и с блоками 29, 30, 33-38 информационной шиной данных (ШД), может иметь управляющие выходы с сигналами "чтение" и "запись" для управления постоянными 29 и оперативным 30 запоминающим элементами соответственно, "вывод", например для вывода информации по шине ШД в блоки 2, 3, 6, 11, 16, 17, 20, вход "запрос прерывания" для ввода информации в решающий блок 10 (24) по сигналам амплитудно-фазового измерителя 9 (23), сигналы обращения (вывода) со стороны решающего блока 10 (24) к внешним блокам формируются путем дешифрования кода адреса соответствующего регистра в дешифраторе 31 и конъюнкции его выходных сигналов с сигналом "вывод" в элементах И 39 44. По выходным сигналам элементов И 34-44 производится запись информации из микропроцессорного модуля 28 в регистры 33 38.

При реализации решающего блока 10 (24) на базе микропроцессора К 580 микропроцессорный модуль 28 состоит из трех БИС-центрального процессора К580, ИК80, системного контроллера К580, ВК28, тактового генератора К580Г⊘24.

Структурная схема варианта синтезатора частот 3 (16) приведена на фиг.8 и построена с использованием преобразования частоты на основе смесителей.

Делители частоты 64, 67 имеют разные коэффициенты деления. Тогда на первых входах смесителей 65, 68 всегда присутствуют когерентные сигналы разных частот, а на вторые входы смесителей подается один и тот же сигнал от перестраиваемого генератора 70. Таким образом, на выходах блока 3 (16) формируются когерентные сигналы, разность частот которых равна преобразованной частоте, при этом когерентность выходных сигналов не нарушается при изменении значений частоты перестраиваемого генератора 70.

Рассмотрим численный пример формирования частот выходных сигналов синтезатора 3 (16).

Пусть частота опорного генератора 2 равна f 1 МГц, fпр 10 кГц, коэффициент деления блока 64 равен 100, коэффициент деления блока 67 равен 50. Тогда на блок 65 поступает сигнал частотой 10 кГц, на блок 68 частотой 20 кГц. Пусть устройство излучает сигналы в диапазоне частот 100 110 МГц, а перестраиваемый генератор 70 поочередно формирует частоты, которые поступают также на выход фильтра 71:

fпго 110010 кГц f огв

fпг1 100010 кГц

fпг2 101010 кГц

fпг3 100110 кГц

Тогда на выходе фильтра 66 выделяются сигналы частотами соответственно:

fo 110010 10 110000 кГц;

f1 100010 10 100000 кГц;

f2 101010 10 101000 кГц;

f3 100110 10 100100 кГц, а на выходе фильтра 69 формируются сигналы частотами соответственно

fогн 110010 20 109990 кГц;

f1г 100010 20 99990 кГц;

f2г 101010 20 100990 кГц;

f3г 100110 20 100090 кГц. При этом выполняются соотношения fo -fогн f1 f1г f2 f2г f3 f3г fогв fo 10 кГц; fo-f1=F1 10000 кГц; fo f2 F2 1000 кГц; fo-f3 F3 100 кГц; F1/F2 F2/F3 m 10.

Перестраиваемый генератор 70 может быть выполнен как на основе пассивных систем синтеза частот, так и на основе активных систем на базе ФАПЧ. Для приведенного выше численного примера при частоте сравнения фазового детектора 73 равной 1 кГц коэффициент деления блока 72 равен 1000, а коэффициенты деления ДПКД 76 принимают значения 110010, 101010, 100110, 100010, что обеспечивает дискретную перестройку управляемого генератора 75 в требуемых пределах.

Кроме рассмотренной структуры построения синтезатора 3 (16) на основе смесителей, синтезаторы частот 3 (16) могут быть реализованы на основе преобразования частоты в кольце ФАПЧ.

Формирователь импульсов 53, 63 выполняет функции формирования управляющих сигналов, необходимых для организации обмена информацией между блоками 46, 49 и 59, 60, регистрами 47, 50 и 61, 62, решающим блоком 10 (24).

Коммутаторы 12, 26, антенные переключатели 5, 19 мгут быть выполнены на p i n-диодах или на микросхемах серии КР590.

При реализации коммутатора 12 (26) на микросхеме КР 590КН3 аналоговыми входами коммутатора являются, например, входы 1А и 2А, выход коммутатор А, вход управления С1.

Коммутаторы-формирователи 11, 25 служат для формирования сигналов управления в соответствии с приведенным описанием предлагаемого устройства. Сигналы, которые формируются блоками 11, 25, приведены на фиг.2 (а-з) и служат для управления блоками 4, 5, 9, 12, 18, 19, 23, 26. В простейшем случае коммутаторы-формирователи 11, 25 могут бть вполнены в виде счетчика, вход которого соединен с выходом опорного генератора 2 (15), а выходы счетчика соединены с адресными входами постоянного запоминающего устройства, хранящего значения кодов чисел, соответствующих временным диаграммам, приведенным на фиг.2. Выходы постоянного запоминающего устройства являются выходами коммутатора-формирователя 11 (25).

При практической реализации блока 9 (23) (см. фиг.6) счетчики 46 и 49 могут быть выполнены в виде реверсивных или в виде суммирующих счетчиков. В случае применения реверсивных счетчиков 46 и 49 сигналы с выходов элементов 45 и 48 управляют режимом счета, т.е. в моменты совпадения полярностей входных импульсов элементов 45 и 48 реверсивные счетчики работают на суммирование, при несовпадении полярностей входных импульсов элементов 45 и 48 на вычитание. При использовании суммирующих счетчиков 46 и 49 в моменты совпадения полярностей входных импульсов элементов 45 и 48 счетчики 46 и 49 суммируют импульсы, поступающие от генератора 51, при несовпадении полярностей входных импульсов элементов 45 и 48 их не считают. Для вычисления фазового сдвига (в этом случае в блоке 10) результаты, полученные на такт измерения в счетчиках 46 и 49 центрируются, т.е. из этих результатов вычисляются поправки, равные половине известного количества импульсов генератора 51 за измерительный такт, и вычисляется функция арктангенса отношения полученных величин.

Формирователь ортогонального сигнала 54 может быть выполнен в виде трех триггеров, работающих в режиме деления частоты на два, причем к прямому и инверсному выходам первого триггера подключены входы второго и третьего триггеров соответственно. Тогда сигналы с выходов второго и третьего триггеров будут сдвинуты относительно друг друга на четверть периода выходной частоты.

Регистры 47, 50, 61, 62, 33 38 могут быть выполнены, например, на микросхемах К155ИР15, К555ИР23 с тремя состояниями на выходе, что легко обеспечивает режим обмена информацией.

Таким образом, благодаря новым элементам и связям достигается повышение точности предлагаемого устройства за счет исключения фазовых сдвигов, вносимых узлами измерительного блока и ретранслятора при изменении в широких пределах уровней входных сигналов. При этом обеспечивается работа смесителей, усилителей промежуточной частоты, ограничителей при постоянных уровнях входных сигналов, а фазовая погрешность, вносимая аттенюаторами, автоматически измеряется и учитывается в результатах измерений устройства.

В известном устройстве фазовые сдвиги, вносимые узлами измерительного блока и ретранслятора при изменении уровней входных сигналов, не учитываются в результате измерений и проявляются в аппаратуре измерительного блока и ретранслятора в виде фазовой погрешности. Известно, что узлы приемников при изменении уровней входных сигналов вносят значительные по величине фазовые сдвиги. Например, фазовые сдвиги, вносимые преобразователями частоты приемников при изменении уровней входных сигналов в 3-5 раз, достигают единиц градусов и сильно зависят от частотного диапазона работы устройства (частотных свойств транзисторов).

Тогда в предлагаемом устройстве повышается точность измерения фазовых сдвигов по сравнению с прототипом за счет автоматического управления уровнем входного сигнала, поступающего на вход смесителя, и поддержанием его в заданных пределах изменений. Кроме того, автоматическое измерение фазовых сдвигов, возникающих в узлах измерительного блока и ретранслятора, в том числе в дискретных аттенюаторах, при изменении уровней входных сигналов в широких пределах и их учет в результирующих значениях фазовых сдвигов позволяет на порядок и более повысить точность измерения информационных параметров устройства.

В этом заключается технико-экономический эффект предлагаемого устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ДВИЖЕНИЯ ОБЪЕКТОВ | 1992 |

|

RU2042144C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗЫ РАДИОСИГНАЛА | 1991 |

|

RU2048677C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗЫ РАДИОСИГНАЛА | 1991 |

|

RU2048676C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ПОГРЕШНОСТЕЙ РАДИОДАЛЬНОМЕРА | 1990 |

|

RU2048685C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗЫ РАДИОСИГНАЛА | 1988 |

|

SU1600518A1 |

| ФАЗОВАЯ РАДИОГЕОДЕЗИЧЕСКАЯ СИСТЕМА | 1991 |

|

RU2088948C1 |

| ДАЛЬНОМЕРНАЯ СИСТЕМА С ИЗМЕРЕНИЕМ ФАЗЫ РАДИОСИГНАЛА | 1990 |

|

RU2076333C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АМПЛИТУДЫ И ФАЗЫ РАДИОСИГНАЛА | 1992 |

|

RU2063051C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ АМПЛИТУДЫ И ФАЗЫ РАДИОСИГНАЛА | 1987 |

|

SU1485851A1 |

| Устройство для измерения амплитуды и фазы радиосигнала | 1989 |

|

SU1665811A1 |

Использование: измерительная техника, измерительные системы в геодезии. Сущность изобретения: устройство содержит: измерительный блок 1, состоящий из генератора 2, синтезатора частот 3, усилителя мощности 4, антенного переключателя 5, аттенюатора 6, смесителя 7, усилителя промежуточной частоты 8, амплитудно-фазового измерителя 9, решащего блока 10, коммутатора-формирователя 11, коммутатора 12, приемнопередающей антенны 13 и ретранслятор 14, состоящего из генератора 15, синтезатора частоты 16, фазовращателя 17, усилителя мощности 18, антенного переключателя 19, аттенюатора 20, смесителя 21, усилителя промежуточной частоты 22, амплитудно-фазового измерителя 23, решающего блока 24, коммутатора-формирователя 25, коммутатора 26, приемопередающей антенны 27. 8 ил.

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗЫ РАДИОСИГНАЛА, содержащее измерительный блок и ретранслятор, каждый из которых состоит из опорного генератора, амплитудно-фазового измерителя, коммутатора-формирователя, усилителя мощности, антенного переключателя и приемопередающей антенны, соединенной с антенным переключателем, причем выход опорного генератора соединен с первым входом коммутатора-формирователя, первый и второй выходы которого соединены с управляющими входами усилителя мощности и антенного переключателя, выход усилителя мощности соединен с входом антенного переключателя, отличающееся тем, что в измерительный блок введены смеситель, синтезатор частот, усилитель промежуточной частоты, решающий блок, аттенюатор, коммутатор, выход которого подключен к первому входу смесителя, второй вход которого подключен к выходу аттенюатора, а выход к входу усилителя промежуточной частоты, выход которого подключен к первому входу амплитудно-фазового измерителя, второй и третий входы которого подключены к третьему выходу коммутатора-формирователя и выходу опорного генератора соответственно, причем первый вход синтезатора частот подключен к выходу опорного генератора, группа выходов к группе входов коммутатора, вход которого подключен к четвертому выходу коммутатора-формирователя, причем выход антенного переключателя подключен к первому входу аттенюатора, а выход амплитудно-фазового измерителя к входу решающего блока, первый выход которого подключен к второму входу аттенюатора, второй выход к второму входу синтезатора частот, а третий выход к второму входу коммутатора-формирователя, причем выход синтезатора частот подключен к входу усилителя мощности, а вход опорного генератора к четвертому выходу решающего блока, кроме того, в ретранслятор введены смеситель, синтезатор частот, усилитель промежуточной частоты, решающий блок, аттенюатор, фазовращатель, коммутатор, выход которого подключен к первому входу смесителя, второй вход которого подключен к выходу аттенюатора, а выход к входу усилителя промежуточной частоты, выход которого подключен к первому входу амплитудно-фазового измерителя, второй и третий входы которого подключены к третьему выходу коммутатора-формирователя и выходу опорного генератора соответственно, причем первый вход синтезатора частот подключен к выходу опорного генератора, группа выходов к группе входов коммутатора, вход которого подключен к четвертому выходу коммутатора-формирователя, причем выход антенного переключателя подключен к первому входу аттенюатора, а выход амплитудно-фазового измерителя к входу решающего блока, первый выход которого подключен к второму входу аттенюатора, второй выход к второму входу синтезатора частот, а третий выход к второму входу коммутатора-формирователя, причем выход синтезатора частот подключен к первому входу фазовращателя, второй вход которого подключен к четвертому выходу решающего блока, а выход к входу усилителя мощности.

| Устройство для измерения амплитуды и фазы радиосигнала | 1977 |

|

SU734592A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1995-12-20—Публикация

1992-02-19—Подача