Изобретение относится к устройствам оперативной памяти и управления в гибридных вычислительных устройствах с оптоэлектронными сеточными или нейтросетевыми процессорами и предназначено для моделирования распределенных систем.

Известно гибридное вычислительное устройство с оптоэлектронными сеточными процессорами, содержащими модель-сетку из оптронов и цифровые блоки управления проводимостью этих оптронов [1]

Известна ячейка памяти, содержащая разрядные триггеры, в плечи которых включен источник излучения [2] Такой блок работает как обычный блок оперативной памяти электронной ЦВМ. При этом за счет высвечивания оптических двоичных сигналов с источников излучения, включенных в элементы памяти, этот блок может применяться как управляющее устройство в оптоэлектронных гибридных сетевых моделях для создания проводимости оптокодоуправляемых элементов таких моделей.

Параллельный вывод оптических сигналов повышает быстродействие гибридной системы в целом за счет задания структуры управления параметрами элементов сеточного аналогового процессора непосредственно из блока оперативной памяти без промежуточного интерфейса.

Однако известное устройство не позволяет непосредственно осуществлять управление параметрами элементов сеточного аналогового процессора, узловые и межузловые элементы которых имеют управление аналоговыми сигналами. Для этого требуется применение цифроаналоговых преобразователей, осуществляющих преобразование хранимых значений моделируемых цифровых величин в аналоговые сигналы.

Целью изобретения является расширение функциональных возможностей устройства и одновременно повышение быстродействия за счет процесса параллельного преобразования хранимых в памяти цифровых сигналов в поток оптических квазианалоговых сигналов.

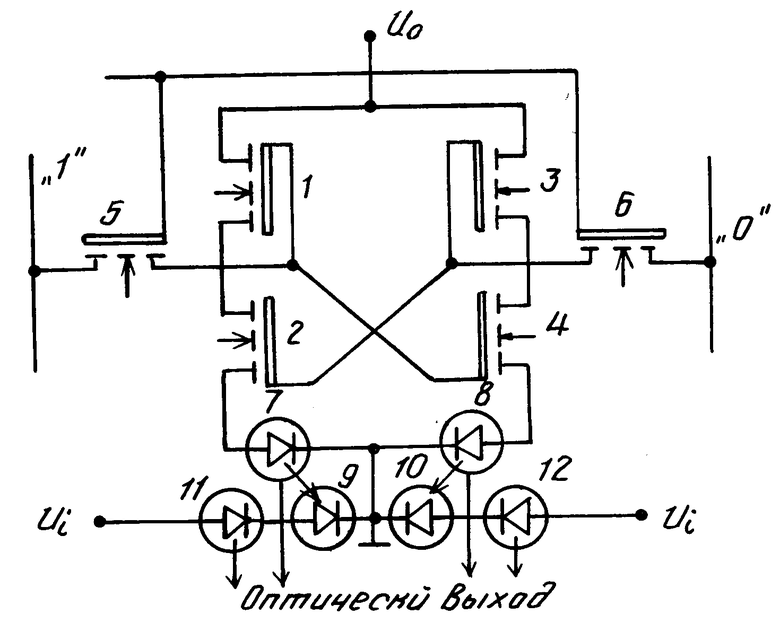

На чертеже представлена схема ячейки памяти.

Она содержит МОП-транзисторы 1-6, источники излучения оптических двоичных сигналов (светодиоды) 7 и 8, фотоприемники (фотодиоды) 9 и 10, источники излучения оптических квазианалоговых сигналов 11 и 12, Uo потенциал источника питания, U1 потенциал опорного источника питания оптронов элемента памяти первого разряда, индексом "0" обозначена шина "нулевого" сигнала, индексом "1" шина "единичного" сигнала.

Отличительная конструктивная особенность предлагаемой ячейки памяти от типовых в наличии дополнительных узлов параллельного вывода информации о содержимом элементов памяти потоком оптических двоичных и квазианалоговых сигналов. Причем оптические двоичные сигналы имеют определенную яркость свечения и высвечиваются источниками излучения и включенными в плечи триггеров элементов памяти. Эти сигналы могут применяться для управления проводимостью оптоэлектронных элементов гибридной сеточной модели, выполненной из оптокодоуправляемых элементов.

Для управления проводимостью оптоэлектронных элементов сетевых гибридных моделей с аналоговым управлением, например модели-сетки на фоторезисторах, можно использовать квазианалоговые оптические сигналы, высвечиваемые с источников излучения 11, 12 оптронов. Яркость свечения этих источников излучения пропорциональна разряду числа, хранимого в том элементе памяти, с которым соединен данный оптрон.

При этом с каждого элемента памяти высвечивается оптический сигнал, по яркости свечения пропорциональный разряду хранимого в элементе памяти числа, а суммарная яркость светимости всех источников излучения будет пропорциональна величине хранимого числа и этот суммарный световой поток от всех излучателей одной ячейки памяти подается на оптический вход одного из фоторезисторов оптоэлектронной модели-сетки.

Кроме того, такие квазианалоговые оптические сигналы могут применяться для визуального контроля за процессом решения, когда хранимые в памяти результаты решения высвечиваются в виде картины оптических сигналов с яркостью свечения, пропорциональной численным значениям хранимых результатов моделирования. За счет вводимых дополнительных оптронов развязанных с электронными цепями элементов памяти можно задавать различную яркость свечения источников излучения 11 и 12 этих оптронов. Например, подавая на их вход различные значения опорных потенциалов (0,1-10 В) в соответствии со значением разряда численного значения моделируемой переменной, можно реализовать тем самым десять двоичных разрядов. Если моделируемые величины принимают большие значения, то в качестве источников излучения 11 и 12 больших разрядов хранимых чисел следует применять источники излучения с другим спектром излучения. Например, применяя для низших разрядов красного, для высших разрядов оранжевого и затем зеленого и голубого излучения, можно с высокой степенью наглядности моделировать задачи тепломассопереноса в распределенных системах, в какой-то мере соблюдая подобие моделируемых тепловых процессов, имитируя при этом значения моделируемых температур изменением спектра излучения источников излучения оптронов.

К вводимым в блок оперативной памяти управления и визуального контроля, оптоэлектронным элементам должны предъявляться следующие требования. Источники излучения 7 и 8 должны иметь низкие показатели поглощения энергии и обеспечивать оптический сигнал такой яркости свечения, который переводит фотодиоды 9 и 10 из непроводящего состояния в проводящее и подключает источники излучения 11 и 12 к шине соответствующего опорного потенциала. При этом источники излучения 11 и 12 должны иметь характеристики, которые обеспечивают генерацию на них оптических сигналов необходимой величины для управления параметрами модели-сетки визуального контроля. Причем в качестве источников излучения 11 и 12 могут применяться и полупроводниковые, и электролюминесцентные излучатели и элементы электронакаливания. Необходимый спектр излучения может обеспечиваться необходимым подбором материалов полупроводниковых излучателей либо применением соответствующих светофильтров.

На чертеже показан вариант с включением двух источников излучения 7, 8 в оба плеча триггера. Чаще бывает достаточно одного источника излучения и оптрона для индикации сигнала "1" и передачи его в оптическую цепь управления для изменения проводимости узловых и межузловых элементов модели-сетки.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГИБРИДНАЯ ЯЧЕЙКА ОПТОЭЛЕКТРОННОГО НЕЙРОПРОЦЕССОРА | 1992 |

|

RU2057363C1 |

| ГИБРИДНАЯ ОПТОЭЛЕКТРОННАЯ ЯЧЕЙКА | 1991 |

|

RU2025776C1 |

| ГИБРИДНАЯ ЯЧЕЙКА ОПТОЭЛЕКТРОННОГО НЕЙРОПРОЦЕССОРА | 1992 |

|

RU2057362C1 |

| Оптоэлектронное вычислительное устройство для решения дифференциальных уравнений в частных производных | 1988 |

|

SU1605221A1 |

| ОПТОЭЛЕКТРОННАЯ МОДЕЛЬ НЕЙРОННОЙ СЕТИ | 1991 |

|

RU2074417C1 |

| ОПТОЭЛЕКТРОННЫЙ НЕЙРОЧИП | 1994 |

|

RU2137192C1 |

| ОПТОЭЛЕКТРОННАЯ МОДЕЛЬ НЕЙРОННОЙ СЕТИ | 1992 |

|

RU2070334C1 |

| ГИБРИДНЫЙ ПРОЦЕССОР | 1992 |

|

RU2096823C1 |

| Модуль нейроподобной сети | 1990 |

|

SU1803923A1 |

| Оптоэлектронный управляемый элемент сеточного процессора | 1988 |

|

SU1603407A1 |

Изобретение относится к устройствам оперативной памяти и управления в гибридных вычислительных устройствах с оптоэлектронными сеточными или нейросетевыми процессорами и предназначено для моделирования распределенных систем. Расширение функциональных возможностей и одновременно повышение быстродействия за счет параллельного преобразования хранимых в памяти цифровых сигналов в поток оптических квазианалоговых сигналов достигается введением в каждый триггер ячейки памяти фотоприемника и второго источника излучения. 1 ил.

ЯЧЕЙКА ПАМЯТИ, содержащая разрядные триггеры, в плечи каждого из которых включены первые источники излучения, выходы которых являются выходами ячейки, отличающаяся тем, что в каждый триггер ячейки введены последовательно включенные между шиной нулевого потенциала и шиной опорного напряжения соответствующего разряда фотоприемники и вторые источники излучения, оптические выходы вторых источников излучения являются дополнительными выходами ячейки, при этом в каждом триггере первый источник излучения и фотоприемник выполнены в виде оптрона.

| Оптоэлектронное вычислительное устройство для решения дифференциальных уравнений в частных производных | 1988 |

|

SU1605221A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-12-20—Публикация

1991-03-15—Подача