Изобретение касается устройства интегральной схемы, содержащее по меньшей мере один кристалла (чип) интегральной схемы, имеющей контактные площадки, соединенные с набором соединительных выводов, посредством проводящих соединений; соединительные выводы включают в себя по меньшей мере первый вывод питания для приема первого и второго питающего напряжения соответственно; а также касается полупроводниковой подложки, снабженной по меньшей мере одной интегральной схемой и имеющей набор контактных площадок, включающих в себя по меньшей мере одну первую контактную площадку питания и вторую контактную площадку для приема первого и второго питающего напряжения соответственно.

Интегральные схемы такого типа хорошо известны, например, в герметизированном корпусном виде, причем соединительные выводы выступают за корпус.

Согласно известной сейчас терминологии ИС, возможно выполнить на подложке структуры, имеющие минимальные размеры порядка десятой доли микрона. Однако каждая последующая миниатюризация влечет за собой увеличение склонности схемы к паразитным электрическим эффектам. Примером таких эффектов являются флуктуации напряжения на внутренних линиях питания подложки, вызванные работой схемы, с одной стороны, и индуктивностями соединительных проводников и выводов питания, с другой. Главным фактором, ограничивающим скорость переключения цифровой схемы, является возможность индуктивных флуктуаций напряжения, которые могут оказать вредное воздействие на ИС.

Герметизация в корпусе ИС, например, микропроцессоров и элементов памяти, при которой выводы питания диаметрально противоположны один другому, является широко распространенным стандартом Ссылкой является [1] где показана схема выводов для запоминающего устройства, и [2] где показана схема выводов микроконтроллера.

Однако, поскольку миниатюризация продолжается и максимальная тактовая частота увеличивается, недостаток этого стандарта становится более явным. Например, сглаживающие емкости, на практике располагаемые между первым и вторым выводами питания, нуждаются в длинных проволочных выводах для перекрытия расстояния между выводами, расположенными диаметрально противоположно. Паразитный импеданс этих проволочных выводов уменьшает эффективность сглаживающей емкости. Кроме того, такие длинные проволочные выводы могут действовать как антенна для приема или передачи возмущений, интерферирующих с электрической схемой.

Кроме того, индуктивный контур, содержащий подложку, на которой расположены контактные площадки для соединительных проводников, присоединенных к выводу питания, и собственно соединительные проводники и выводы питания, имеют значительную индуктивность из-за его относительно большой площади. Это вызывает возникновение выброса индуктивного напряжения и на внутренних линиях питания подложки, причем этот выброс может интерферировать с работой ИС.

Кроме того, последовательность устройств, состоящая из вывода питания и связанного с ним соединительного проводника, имеет наибольшую возможную электрическую длину в известной микросхеме с двурядным расположением вертикальных выводов. Это является причиной того, что импеданс, в частности индуктивность, является максимально возможной.

Известные расположения выводов, отличные от этого двухрядного расположения, влекут за собой подобные недостатки. Например, в расположении выводов микроконтроллера, приведенном в Philips Data Handbook, 1C 14, 1987, с. 34, соединительные выводы расположены вдоль окружности ИС. Два вывода питания предусмотрены с противоположных сторон ИС. Следовательно, сглаживающий конденсатор, присоединенный между выводами питания, подобным образом создает относительно большой контур. Другие расположения соединительных выводов могут содержать последние, установленные в решетку, имеющую более двух столбцов и более двух рядов.

Такое решетчатое расположение обеспечивает высокую плотность выводов, что, в частности, является преимуществом для ИС с большим потреблением тока. В особенности в области высокого энергопотребления, где токи и их изменения велики, работа может ограничиваться вышеописанным индуктивным эффектом.

В качестве прототипа выбран [3] В прототипе наряду с другим, показывается расположение проводящих соединений для чипа интегральной схемы с контактными площадками питания и заземления, установленных следом друг за другом по центру на кромке чипа. Следует отметить, что это описание относится к проблеме токовых петель на чипе, тогда как в рассматриваемой заявке основной проблемой является токовая петля, которая содержит вне чиповые элементы, такие как проводящие соединения и выводы. Прототип не содержит отличительного признака такого расположения соединительного вывода и проводящего соединения. Также следует отметить, что в нем нет указания на выходную площадку, расположенную смежно с одной из площадок питания.

Поэтому в основу изобретения положена задача уменьшения склонности интегральной схемы к упомянутым паразитным эффектам. Для этого интегральная схема согласно изобретению отличается тем, что совокупная длина электрической траектории по крайней мере одного из выводов питания и его соответствующего проводящего соединения равна или короче, чем совокупная длина электрической траектории любого из соединительных выводов, не являющегося выводом питания, и его соответствующего проводящего соединения, причем выходной вывод расположен следом за одним из выводов питания.

Вариант исполнения интегральной схемы на полупроводниковой подложке согласно изобретению отличается тем, что площадка первого питания расположена смежно с площадкой второго питания и выходной площадкой.

Легко выполнимо расширение схем, разработанных согласно изобретению, поскольку расположение большей части выводов и, следовательно, основной части топологии определено заранее. В частности, для элементов памяти ячейки матрицы могут отличаться лишь размером адресуемого пространства, но не элементами топологии.

В соответствии с экспериментами, проведенными на КМОП памяти согласно изобретению, амплитуда возмущающих напряжений, вызванных переключениями, оказались ниже в 4 5 раз, чем для памяти известного типа.

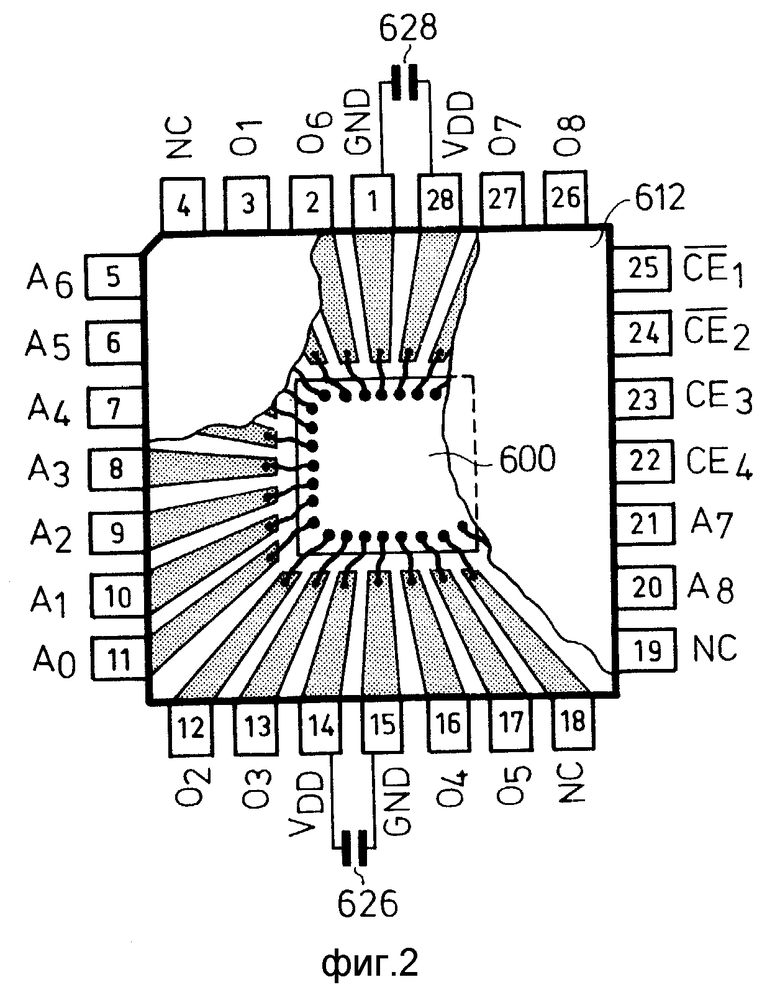

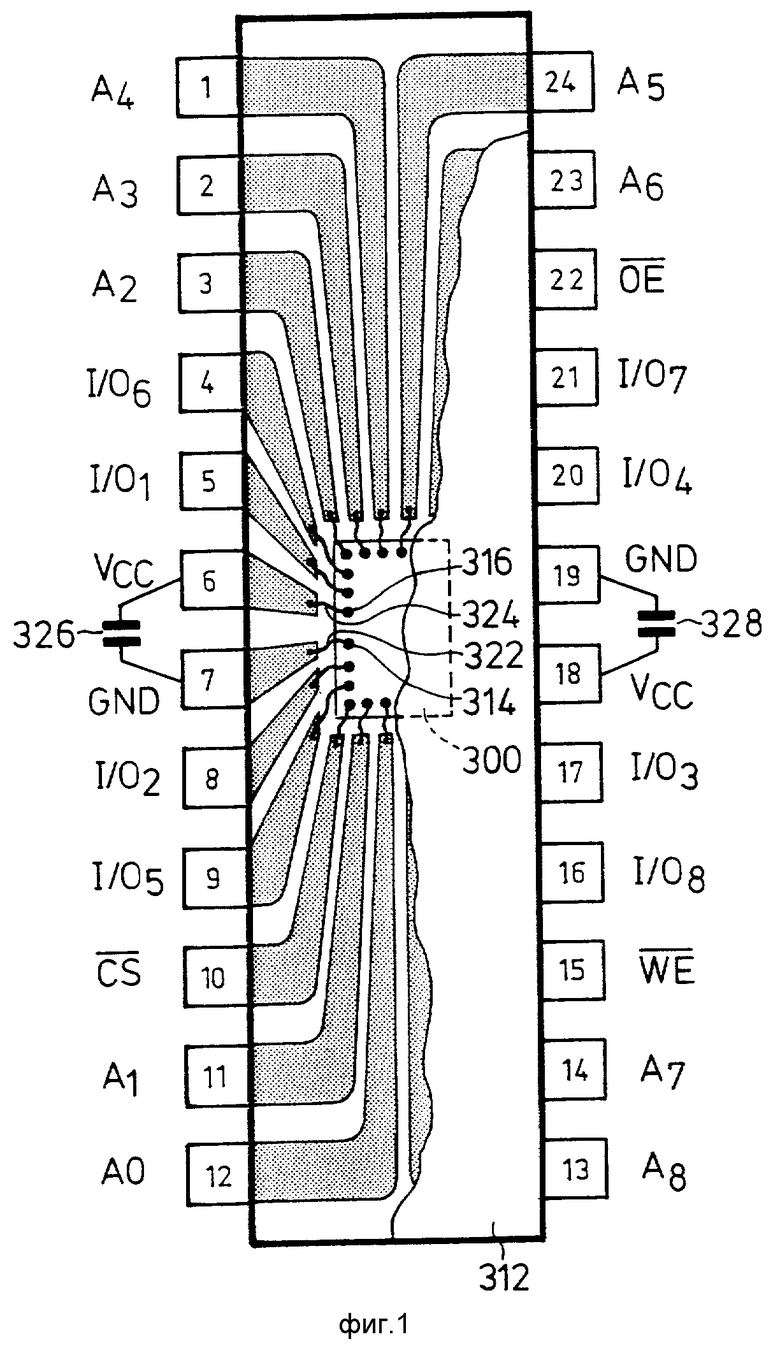

На фиг. 1 изображено размещение выводов согласно изобретению микросхемы с двухрядным размещением выводов; на фиг. 2 размещение выводов микросхемы, имеющей выводы, расположенные по окружности согласно изобретению.

На фиг. 1 показана ИС запоминающего устройства, содержащая подложку интегральной схемы 300, загерметизированную внутри герметичного корпуса 312, что показано лишь частично для ясности. Подложка 300 снабжена контактными площадками, такими как 314 и 316, которые расположены рядом с краями подложки 300. Контактные площадки присоединены проводящими соединениями, 322 и 324, к соединительным выводам 1 24, выступающим за пределы корпуса 312. Подложка 300 питается напряжением питания Vcc через выводы питания 6 и 18 и напряжением питания GND через выводы питания 7 и 19.

Выводы питания 6 и 7 (и 18 и 19) теперь располагаются таким образом, чтобы свести к минимуму полную электрическую длину соответствующего вывода питания и связанного с ним проводящего соединения.

Для этого выводы питания 6 и 7, с одной стороны, и выводы питания 18 и 19, с другой, расположены в центре связанной с ними последовательности соединительных выводов. Посредством сведения к минимуму упомянутой электрической длины полная индуктивность последовательности устройств, состоящей из выводов питания и связанных с ними проводящих соединений, значительно уменьшается по сравнению с полной индуктивностью, имеющейся в соответствующем выводе питания и проводящем соединении известным образом цоколеванной ИС с предыдущего чертежа.

Посредством расположения выводов питания для Vcc и GND один за другим, или выводов 6 и 7 (и выводов 18 и 19), сглаживающий конденсатор 326 (328) может быть присоединен между ними, используя при этом очень короткие проволочные выводы.

Контур, образованный двумя выводами питания 6 и 7, соединительными проводниками 322 и 324, подложкой 300 и конденсатором 326 теперь имеет чрезвычайно короткую окружность и, вследствие этого, заключает в себе чрезвычайно малую область. Проводники, соединяющие конденсатор 326 (328) с выводами питания, имеют много меньший импеданс, чем в известном устройстве /1/, чем увеличивается эффективность конденсаторов.

Кроме того, область упомянутого контура является много меньшей, чем в известном устройстве, что подразумевает много меньшую индуктивность контура, а следовательно, и много меньшую подверженность, например, влиянию возбуждаемых снаружи электромагнитных полей. Если пространство позволяет, то сглаживающий конденсатор 326 (например, смонтированное на поверхности устройство) может быть присоединен между соответствующими выводами питания внутри герметичного корпуса 312 или может быть интегральным компонентом вблизи собственно выводов питания.

Преимуществом размещения выводов питания, имеющего Vcc вывод в непосредственной близости от GND вывода, является сокращение эффективной полной индуктивности выводов питания и связанных с ними проводящих соединений. Это сокращение вызвано противопараллельной ориентацией токов, протекающих в проводниках, каждый из которых содержит вывод питания и связанные с ним проводящее соединение. Взаимная индуктивность, возникающая посредством противопараллельно направленных токов в двух проводниках, расположенных параллельно один другому, приводит к тому, что индуктивность параллельно расположенных проводников является меньше, чем половина индуктивности одного проводника.

Показанная ИС также снабжена двумя выводами питания 6 и 18 для питающего напряжения Vcc и двумя выводами питания 7 и 19 для напряжения питания GND. Ток, проводимый выводом питания, теперь равен половинному по сравнению с известным устройством, что сокращает амплитуду индуктивных выбросов напряжения.

Расположение выводов Vcc 6 и 18 и GND выводов 7 и 19 преимущественно выбрано таким образом, чтобы быть поворотно-симметричным, как можно видеть из чертежа. В отличие от этого, зеркально-симметричное расположение выводов питания может привести к разрушению ИС в случае, если она не преднамеренно будет вставлена в колодку другим способом, чем показанным на чертеже.

Как можно видеть из фиг. 1 выходные выводы 5, 8, 17, 20 расположены вслед за выводом питания. Эти выходные выводы являются доступными снаружи клеммами, присоединенными к выходам буферов подложки (не показаны). Размещение выходных выводов вслед за выводами питания имеет различные преимущества. Во-первых, электрическая длина, образованная выходным выводом и связанным с ним проводящим соединением имеет тот же порядок величины, что и электрическая длина, образованная выводом питания и связанным с ним проводящим соединением, или равна ей. Во-вторых, выходные буферы расположены с краю подложки 300. Благодаря тому, что буферы расположены рядом с контактными площадками для присоединения к клеммам питания и для присоединения к выходным выводам, буферы питаются через короткие линии питания на подложке (не показаны).

Короткие линии питания являются преимуществом в частности для выходных буферов, поскольку они обычно переключают большой ток, что может вызвать индуктивные выбросы напряжения на связанных с ними линиях питания. Если линии питания выдерживаются как можно более короткими, то их индуктивность будет пропорционально низкой.

Управляющий вывод 10 для сигнала выброса подложки, управляющий вывод 15 для сигнала разрешения записи и управляющий вывод 22 для разрешения расположены смежно с выходным валом в последовательности соединительных выводов. Набор выводов питания 6, 7, 8, 19, выходных выводов 4, 5, 8, 9, 16, 17, 20, 21 и управляющих выводов 10, 15, 22 образуют ядро или управляющее ядро из частично встречающихся выводов запоминающих ИС.

Для другого типа ИС, например, микроконтроллеров, другой набор может быть установлен, поскольку может требоваться специфическое, конкретное применение ИС. Концентрация упомянутых выводов питания выходных выводов и управляющих выводов в ядре, а также разделение кристалла между схемой ядра и дополнительной схемой имеет различные преимущества.

Во-первых, ИС менее чувствительна к индуктивным выбросам напряжения. Во-вторых, ядро из стандартных соединительных выводов представляет для разработчиков ИС отправную точку, которая является общей для различных топологий и к которой относительно легко могут быть присоединены различные дополнительные и производные схемы.

На фиг. 1 адресные выводы 2, 1, 3, 11, 12, 13, 14, 23, 24 расположены за выходами управления и выходными выводами. Для разработчиков запоминающих устройств, в частности это разделение между схемой и дополнительной схемой имеет то преимущество, что запоминающие устройства с различными емкостями могут использовать идентичные ядра, менее чувствительные к выше описанной индуктивной интерференции.

На фиг. 2 показан пример размещения выводов ИС, выводы которой расположены по окружности. Показана подложка интегральной схемы 600 внутри герметичного корпуса 612. VDD питающие выводы 14 и 28 теперь расположены после GND вывода питания 15 и 1 соответственно.

Более того, размещение VDD вывода питания вслед за GND выводами питания находится в центре соответствующей последовательности соединительных выводов, расположение закрыто сбоку другими соединительными выводами с обеих сторон, число других соединительных выводов приблизительно равно с обоих сторон.

Сглаживающие конденсаторы 626 и 628 преимущественно являются поверхностно установленными устройствами и присоединены между выводами питания 14 и 15 и выводами питания 1 и 28 соответственно. Выходные выводы 12, 13 и 16, 17 расположены вслед за размещением выводов питания 14 и 15. Выходные выводы 3, 2, 27 и 26 расположены вслед за размещением выводов питания 1 и 28. Соединительные выводы 22 25 образуют выводы управления для различных размещающихся сигналов, соединительные выводы 54 11, 20 и 22 образуют адресные выводы.

Хотя вышеприведенные примеры относятся к запоминающим устройствам, подобное размещение выводов может быть выполнено для других типов схем, например, микроконтроллеров. А также подобные размещения возможны для интегральных модулей, держащих более одной подложки, причем размещение выводов подобным образом отражает цель изобретения, состоящую в уменьшении индуктивных выбросов напряжения посредством спаривания выводов питания в непосредственной близости от подложки и посредством расположения выходных выводов вслед за выводами питания в соответствующем размещении соединительных выводов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ПЕРЕДАЧИ ДВУПОЛЯРНОГО СИГНАЛА | 1992 |

|

RU2099793C1 |

| КОМПОНОВКА СВЕТОДИОДНОЙ СХЕМЫ | 2011 |

|

RU2563042C2 |

| ИНФОРМАЦИОННЫЙ НОСИТЕЛЬ, УСТРОЙСТВО, ПОДЛОЖКА И СИСТЕМА | 2001 |

|

RU2284574C2 |

| УСТРОЙСТВО ОТОБРАЖЕНИЯ ПЛОСКОГО ТИПА | 1990 |

|

RU2095879C1 |

| МАТРИЦА ДЕТЕКТОРОВ ИЗЛУЧЕНИЯ | 2007 |

|

RU2408110C2 |

| МОДУЛЬНАЯ СИСТЕМА ТВЕРДОТЕЛЬНОГО ОСВЕЩЕНИЯ | 2008 |

|

RU2462004C2 |

| УСОВЕРШЕНСТВОВАННАЯ СБОРКА СОЕДИНЕНИЙ LED | 2010 |

|

RU2528611C2 |

| СХЕМА ПИТАНИЯ И УСТРОЙСТВО, СОДЕРЖАЩЕЕ СХЕМУ ПИТАНИЯ | 2007 |

|

RU2427954C2 |

| СХЕМА ПИТАНИЯ ПЕРЕКЛЮЧАЮЩЕЙ СХЕМЫ | 2010 |

|

RU2537787C2 |

| МЕЖСОЕДИНЕНИЕ МЕТОДОМ ПЕРЕВЕРНУТОГО КРИСТАЛЛА НА ОСНОВЕ СФОРМИРОВАННЫХ СОЕДИНЕНИЙ | 2007 |

|

RU2441298C2 |

Назначение: электронная техника. Сущность изобретения: Расположение выводов питания интегральной схемы выбрано таким образом, чтобы свести к минимуму длину соединительных проводников. Кроме того, выводы питания расположены один за другим таким образом, чтобы уменьшить эффективную индуктивность связанных с ними соединительных проводников. Выходные выводы расположены следом за выводами питания с тем, чтобы уменьшить величину индуктивных паразитных эффектов. После выходных выводов расположены выводы управления. Как следствие, хорошо защищенное ядро стандартных выводов может быть использовано, например, в интегральных схемах запоминающих устройств с различными топологиями. 2 с. и 11 з.п. ф-лы, 2 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Philips Data Handbook, 1C 10, 1987, c | |||

| Клапанный регулятор для паровозов | 1919 |

|

SU103A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Philips Data Handbook, 1C 14, 1987, c | |||

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ЕПВ, патент, 0138650, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1997-10-10—Публикация

1990-02-12—Подача