Изобретение относится к технике телевидения и может быть использовано в прикладных телевизионных камерах на приборах с зарядовой связью.

Известна телевизионная камера на ПЗС КТ-2. Недостатком ее является малый световой динамический диапазон в области больших освещенностей.

Известна телевизионная камера на ПЗС, являющаяся прототипом (авт.св. 1394463 М.кл. H 04 N 5/335. 3/14). Она содержит трехфазную матрицу ПЗС. содержащую секцию накопления (СН), секцию памяти (СП), выходной регистр (ВР), средний регистр (СР), а также преобразователи уровней секции накопления (ПУСН), секции памяти (ПУСП), выходного регистра (ПУВР), среднего регистра (ПУСР), Формирователи фаз секции накопления (ФФСН), секции памяти (ФФСП), выходного регистра (ФФВР), задающий генератор (ЗГ), первый делитель частоты (ДЧ1), второй делитель частоты (ДЧ2),третий делитель частоты (ДЧ3), счетчик времени прямого хода кадра (СВПХК), счетчик времени обратного хода кадра (СВОХК), D-триггер, инвертор, шесть элементов ИЛИ, усилитель-формирователь (УФ), четыре элемента И, компаратор, три элемента НЕТ, причем выход УФ является выходом телевизионной камеры и соединен с первым входом компаратора, выход компаратора и выход ПУСР соответственно соединен с первым и вторым входами СР, первый вход УФ соединен с выходом ВР, второй вход УФ и третий вход ФФСП соединены с вторым выходом ДЧ2, третий вход УФ, третий вход четвертого элемента И, второй вход третьего элемента И, вход ДЧ3 соединены с первым выходом СВОХК, второй выход СВОХК соединен с первым входом D-триггера и с вторым входом СВПХК, вход СВОХК соединен с выходом второго элемента И, вторые входы D-триггера и четвертого элемента И соединены с выходом ДЧ3, выход D-триггера соединен с первым входом четвертого элемента И. Выход четвертого элемента И соединен с входом инвертора, с первым входом ФФСП, с первым входом ФФСН, с вторыми входами шестого элемента ИЛИ, второго и третьего элементов НЕТ, первый, второй, третий выходы ФФВР соединены соответственно с первым, вторым третьим входами ПУВР и с первыми входами шестого элемента ИЛИ, второго и третьего элементов НЕТ, выходы шестого элемента ИЛИ, второго и третьего элементов НЕТ соединены соответственно с первыми входами первого элемента И, четвертого и пятого элементов ИЛИ, первый, второй, третий выходы ФФСН соединены соответственно с первым, вторым, третьим входами ПУСН и с вторыми входами первого элемента И, четвертого и пятого элементов ИЛИ, выходы первого элемента И, четвертого и пятого элементов ИЛИ соединены соответственно с первым, вторым, третьим входами ПУСР, четвертые входы ПУСН и ПУСР, первый вход третьего элемента И соединены с выходом инвертора,

Вторые входы первого элемента НЕТ, первого, второго, третьего элементов ИЛИ соединены с выходом третьего элемента И, первые входы первого элемента НЕТ, первого, второго, третьего элементов ИЛИ соединены соответственно с третьим, вторым, первым, четвертым выходами ФФСП, выходы первого элемента НЕТ, первого, второго, третьего элементов ИЛИ соединены соответственно с третьим, вторым, первым, четвертым входами ПУСП, выход ЗГ соединен с входом ДЧ1 и с вторым входом ФФВР, выход ДЧ1 соединен с входом ДЧ2, с первым входом второго элемента И, с первым входом СВПХК, с первым входом D-триггера, с вторыми входами ФФСН м ФФСП, второй вход второго элемента И соединен с вторым выходом СВПХК, первый выход СВПХК соединен с вторым входом компаратора, первый выход ДЧ2 соединен с первым входом ФФВР, выход ПУСН соединен с входом СП, выход ПУСП соединен с входом СП, выход ПУВР соединен с входом ВР.

Недостатком прототипа является малый световой динамический диапазон в области больших освещенностей.

В предлагаемом изобретении в телевизионную камеру, содержащую трехфазную матрицу ПЗС с СН, СП и ВР, а также ПУСН, ПУСП, ПУВР, ФФСН, ФФСП, ФФВР, ЗГ, строчный делитель частоты (СДЧ), кадровый делитель частоты (НДЧ), УФ, введены аналого-цифровой преобразователь (АЦП), два блока логического умножения (БЛУ), каждый из которых состоит из четырех элементов И с объединенными вторыми входами, пиковый детектор (ПД), постоянно-запоминающее устройство (ПЗУ), двухразрядный счетчик (ДС), блок памяти (БП), два элемента И, элемент ИЛИ, делитель частоты (ДЧ), счетчик импульсов (СИ), два блока логического сложения (БЛС), каждый из которых состоит из четырех элементов ИЛИ с объединенными вторыми входами, D-триггер.

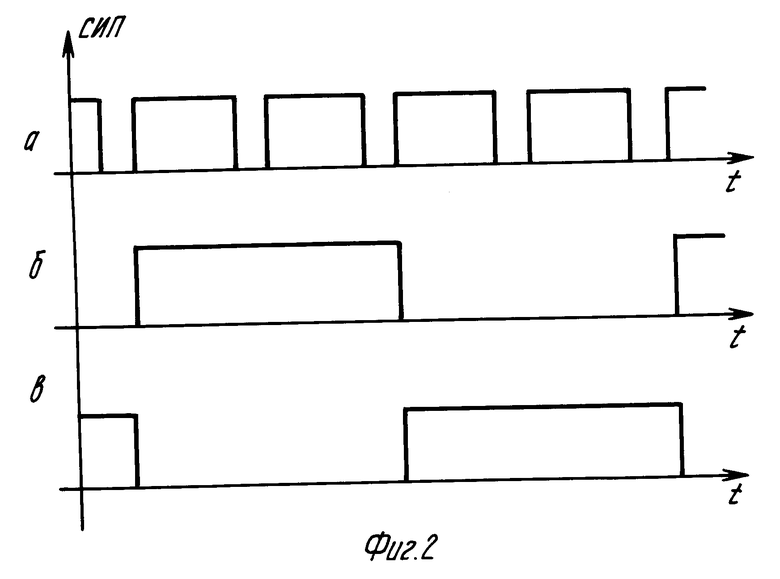

На фиг.1 представлена структурная схема телевизионной камеры на ПЗС; на фиг.2 временные диаграммы, поясняющие принцип работы телевизионной камеры.

Телевизионная камера (фиг. 1) содержит трехфазную матрицу 1 ПЗС с СН2, СП3, ВР4. а также ПУСН5, ПУСП6, ПУВР7, ФФВР8, ФФСН9, ФФСП10, ЗГ 11, СДЧ12, КДЧ13, УФ14. БП15, элементы И 16 и 17, БЛУ18, БЛУ19, БЛС20, БЛС21, ПД22, АЦП24, СИ25, ДЧ26. D-триггер 27, элемент ИЛИ 28, ДС29, где первым и вторым выходами ДС29 соответственно являются прямой и инверсный выходы второго разряда, причем выход БП 15 является выходом телевизионной камеры и соединен через ПД 22 с входом АЦП 23, выход АЦП23 соединен с адресным входом ПЗУ 24, выход ПЗУ 24 соединен с параллельным входом данных (первый вход) СИ25 и с вторым входом ДЧ26, выход ЗГ II соединен с первыми входами элемента И16 и ДЧ26, с входом СДЧ12, выход ДЧ26 соединен с тактовым входом (второй вход) СИ25, прямой выход (первый выход) D-триггера 27 соединен с входом разрешения параллельной загрузки (третий вход) СИ25 и с первым входом элемента ИЛИ29, выход окончания счета на уменьшение СИ25 соединен с R-входом (первый вход) D-триггера 27, второй (инверсный) выход D-триггера 27 соединен с вторыми входами БЛУ18 и БЛС 20, первый выход ДС29 соединен с вторыми входами БП15, элемента ИЛИ 28, элементов И 16 и 17, второй выход ДС29 соединен с вторым входом БЛС21 и с тактовым входом (второй вход) D-триггера 27, выход элемента ИЛИ 28 соединен вторым входом БЛУ19, выход СДЧ12 соединен с входом КДЧ13, с вторыми входами ФФСП10 и УФ14 с первым входом элемента И17, выход КДЧ13, являющийся выходом полукадровых синхроимпульсов (СИП) соединен с третьим входом УФ14, с первым входом ФФСП10, с входами ФФСН9 и ДС29, выход БЛУ18 соединен через ПУСН5 с входом СН2. Выход БЛУ19 соединен через ПУСП6 с входом СП3, выход ФФВР8 соединен через ПУВР 7 с входом ВР4, выходы элементов И16 и 17 соответственно соединены с вторым и первым входами ФФВР6, выход ФФСН9 соединен с первым входом БЛС20, выход ФФСП10 соединен с первым входом БЛС21, выход БЛС20 соединен с первым входом БЛУ18, выход БЛС21 соединен с первым входом БЛУ19, выход ВР4 соединен с первым входом УФ14, выход УФ14 соединен с первым входом БП15.

Телевизионная камера работает следующим образом. Выходя ной сигнал ЦД24, соответствующий максимальному видеосигналу на выходе БП15, преобразуется АЦП 23 в десятиразрядный код, определяющий выходной код ПЗУ24. Передний фронт сигнала инверсного выхода ДС29 (фиг.2, б) устанавливает на инверсном выходе D-триггера 27 сигнал нулевого уровня, задающий сигнал нулевого уровня на входе ПУСП6, и сигнал единичного уровня на прямом выходе D-триггера 27, определяющего сигнал единичного уровня на входе ПУСП6 и разрешающего работу счетчика 25, что обеспечивает накопление фотозаряда в СН2. Сигнал нулевого уровня на прямом выходе ДС29 (фиг.2, в) запрещает запись видеосигнала УФ14 в БП15 и определяет сигналы нулевых уровней на входах ФФВР18, запрещающих построчный сдвиг фотозаряда на СП3 в ВР4 и его поэлементный вывод на ВР4.

Импульсы ЗГ11, пройдя через ДЧ26 с коэффициентом деления, задаваемым выходным кодом ПЗУ24, уменьшают выходной код счетчика 25 до нуля и выходной сигнал счетчика 25 нулевого уровня устанавливает на прямом выходе D-триггера 27 сигнал нулевого уровня, определяющего выходной код счетчика 25 равным выходному коду ПЗУ24, сигнал нулевого уровня на входе ПУСП6, сигнал единичного уровня на входе ПУСП6, что запрещает накопление фотозаряда в СН2 и осуществляет перенос накопленного фотозаряда из СН2 в СП3. Таким образом, выходной код ПЗУ24 задает время экспозиции в интервале от 140 до 38 мс. Единичный уровень сигнала прямого выхода ДС29 разрешает прохождение сигналов ФФСП10, ЗГ 11, СДЧ12 соответственно к входу ПУСП6, к второму и первому входам ФФВР18, что обеспечивает в течение двух полукадров построчный сдвиг накопленного фотозаряда из СП3 в ВР4 и поэлементный вывод фотозаряда через преобразователь заряд напряжение матрицы из ВР4 к первому входу УФ14, а также запись видеосигнала с выхода УФ14 в БП15.

Программирование ПЗУ24 осуществляется таким образом, что младшим адресам соответствует большой вес выходного кода, а старшим адресам соответствует малый вес выходного кода. Предлагаемая камера имеет расширенный в область больших освещенностей световой динамический диапазон и может быть использована в прикладных телевизионных установках.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТЕЛЕВИЗИОННАЯ КАМЕРА НА ПРИБОРАХ С ЗАРЯДОВОЙ СВЯЗЬЮ | 1993 |

|

RU2083056C1 |

| Телевизионная камера на приборах с зарядовой связью | 1987 |

|

SU1394463A1 |

| УСТРОЙСТВО СТАБИЛИЗАЦИИ АМПЛИТУДЫ ВИДЕОСИГНАЛА | 1996 |

|

RU2119725C1 |

| УСТРОЙСТВО СТАБИЛИЗАЦИИ АМПЛИТУДЫ ВИДЕОСИГНАЛА | 1998 |

|

RU2137318C1 |

| УСТРОЙСТВО СТАБИЛИЗАЦИИ АМПЛИТУДЫ ВИДЕОСИГНАЛА | 1999 |

|

RU2150179C1 |

| ТЕЛЕВИЗИОННАЯ КАМЕРА | 1991 |

|

RU2010449C1 |

| УСТРОЙСТВО ОДНОКРАТНОГО ФОРМИРОВАНИЯ СИГНАЛА ИЗОБРАЖЕНИЯ | 1996 |

|

RU2145154C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТНЫЙ ДИСКРИМИНАТОР | 1996 |

|

RU2139640C1 |

| Устройство формирования сигнала изображения | 1988 |

|

SU1589427A2 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

Изобретение относится к технике телевидения и может быть использовано в прикладных телевизионных установках. Цель изобретения - расширение в область больших освещенностей светового динамического диапазона телевизионной камеры на приборах с зарядовой связью достигается введением в камеру аналого-цифрового преобразователя, постоянно-запоминающего устройства, двух блоков логического сложения, двух блоков логического умножения, двухразрядного счетчика, пикового детектора, счетчика импульсов, делителя частоты, блока памяти, двух элементов И, элемента ИЛИ, D-триггера. 2 ил.

Телевизионная камера на приборах с зарядовой связью, содержащая трехфазную матрицу приборов с зарядовой связью, состоящую из последовательно связанных зарядовой связью секции накопления, вход которой соединен с выходом преобразователя уровней секции накопления, секции памяти, вход которой соединен с выходом преобразователя уровней секции памяти, выходного регистра, вход которого соединен через преобразователь уровней выходного регистра с выходом формирователя фаз выходного регистра, а также формирователи фаз секции накопления и секции памяти, задающий генератор, первый делитель частоты, второй делитель частоты, усилитель-формирователь, причем выход выходного регистра, являющийся выходом матрицы приборов с зарядовой связью, соединен с первым входом усилителя-формирователя, выход задающего генератора соединен с входом первого делителя частоты, выход первого делителя частоты соединен с входом второго делителя частоты, первым входом формирователя фаз выходного регистра, вторыми входами формирователя фаз секции памяти и усилителя-формирователя, выход второго делителя частоты соединен с входом формирователя фаз секции накопления, первым входом формирователя фаз секции памяти, третьим входом усилителя-формирователя, отличающаяся тем, что введены пиковый детектор, аналого-цифровой преобразователь, постоянно-запоминающее устройство, счетчик импульсов, третий делитель частоты, D-триггер, элемент ИЛИ, двухразрядный счетчик, два блока логического умножения, два блока логического сложения, два элемента и блок памяти, причем выход блока памяти является выходом телевизионной камеры и соединен через пиковый детектор с входом аналого-цифрового преобразователя, выход аналого-цифрового преобразователя соединен с входом постоянно-запоминающего устройства, выход постоянно-запоминающего устройства соединен с информационным входом счетчика импульсов (первый вход) и первым входом третьего делителя частоты, задающим коэффициент деления делителя, выход задающего генератора соединен с вторым входом третьего делителя частоты, выход третьего делителя частоты соединен с тактовым входом счетчика импульсов (второй вход), прямой выход D-триггера (первый выход) соединен с входом разрешения параллельной загрузки счетчика импульсов (третий вход) и первым входом элемента ИЛИ, выход счетчика импульсов соединен с R-входом D-триггера (первый вход), второй (инверсный) выход D-триггера соединен с вторым входом первого блока логического сложения и вторым входом первого блока логического умножения, выход второго делителя частоты соединен с тактовым входом двухразрядного счетчика, прямой выход двухразрядного счетчика (первый выход) соединен с вторыми входами элемента ИЛИ, элементов И и блока памяти, второй (инверсный) выход двухразрядного счетчика соединен с вторым входом второго блока логического сложения и тактовым входом D-триггера (второй вход), выход элемента ИЛИ соединен с вторым входом второго блока логического умножения, выход формирователя фаз секции накопления соединен с первым входом первого блока логического сложения, выход первого блока логического сложения соединен с первым входом первого блока логического умножения, выход первого блока логического умножения соединен с входом преобразователя уровней секции накопления, выход формирователя фаз секции памяти соединен с первым входом второго блока логического сложения, выход второго блока логического сложения соединен с первым входом второго блока логического умножения, выход второго блока логического умножения соединен с входом преобразователя уровней секции памяти, выход задающего генератора соединен с первым входом первого элемента И, выход первого делителя частоты соединен с первым входом второго элемента И, выходы первого и второго элементов И соответственно соединены с вторым и первым входами формирователя фаз выходного регистра, выход усилителя-формирователя соединен с первым входом блока памяти.

| Телевизионная камера на приборах с зарядовой связью | 1987 |

|

SU1394463A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1997-10-10—Публикация

1993-07-01—Подача