Изобретение относится к многоканальным системам связи, построенным по принципу "каждый с каждым", и может быть использовано в системах синхронизации таких систем.

Из уровня техники известно устройство синхронизации [1] состоящее из первого и второго перемножителей, первые входы которых являются входом устройства, а их вторые входы подключены соответственно к выходам генератора несущей частоты, а выходы перемножителей соединены соответственно с входами модулятора сигналов, тактовый вход которого соединен с выходом блока управления и управляющим входом порогового блока, выход которого подключен к входу блока управления, выходы модулятора сигналов соединены соответственно с входами интеграторов, выходы нечетных интеграторов соединены соответственно с входами первого сумматора, а выходы четных интеграторов с входами второго сумматора, выходы первого и второго сумматора через соответствующие квадраторы соединены с соответствующими входами третьего сумматора, выход которого соединен с входом преобразователя типа "корень квадратный", первый выход которого является первым выходом устройства, а второй выход соединен с информационным входом порогового блока.

Известно также устройство синхронизации шумоподобных сигналов [2] являющееся дополнительным к [1] дополнительно содержащее последовательно соединенные блок памяти, схему сравнения, дополнительный сумматор и блок регулировки частоты, выход которого соединен с управляющим входом генератора несущей частоты, управляющие входы схемы сравнения и блока памяти соединены с соответствующими выходами порогового блока, а информационный вход блока памяти соединен с выходом блока управления.

Эти устройства реализуют параллельный метод поиска сигнала синхронизации по частоте.

Из уровня техники наиболее близким к изобретению является устройство для поиска псевдослучайного сигнала 3, состоящее из первого перемножителя, первый вход которого является входом устройства, а второй вход подключен к выходу управляемого генератора, а выход первого перемножителя соединен с первыми входами второго, третьего и четвертого переменожителей, вторые входы которых подключены к выходу соответствующего разряда регистра сдвига, выход второго перемножителя соединен с входами первого и второго усилителей промежуточной частоты, выходы которых соответственно через первый и второй детекторы подключены к соответствующим входам первого сумматора, выход которого через усилитель соединен с входом управляемого генератора, выходы третьего и четвертого перемножителей соединены соответственно с входами третьего и четвертого усилителей промежуточной частоты, выходы которых соответственно через третий и четвертый детекторы соединены соответственно с входами второго сумматора, выход которого подключен к входу фильтра нижних частот, выход которого подключен к входу управляемого тактового генератора, выход которого соединен с тактовым входом регистра сдвига.

Это устройство реализует последовательный метод поиска сигнала синхронизации по частоте.

Недостатком устройства, реализующего параллельный метод поиска и сопровождения сигнала синхронизации является избыточность оборудования, большая часть которого не используется в режиме синхронизма после окончания поиска.

Недостатком устройства, реализующего последовательный метод поиска по частоте сигнала синхронизации, является достаточно длительная процедура поиска.

Кроме этого, все известные устройства не пригодны для работы в спутниковых системах связи, построенных по принципу "каждый с каждым" и использующих разные псевдослучайные последовательности для передачи информации и для передачи сигналов синхронизации.

Технической задачей, на решение которой направлено устройство, является разработка устройства поиска и сопровождения сигнала синхронизации в системах спутниковой связи с шумоподобными сигналами, построенными по принципу "каждый с каждым" и использующих разные псевдослучайные последовательности для передачи сигналов информации и сигналов синхронизации.

Технический результат от использования устройства заключается в расширении арсенала технических средств решения указанной задачи, сокращении продолжительности поиска по частоте, повышении отношения сигнал/шум в каждом из каналов поиска и улучшения качества фильтрации сигналов в каждом из каналов.

Этот технический результат достигается тем, что в устройстве поиска и сопровождения сигнала синхронизации в спутниковых системах связи (ССС) по приему, содержащее первый преобразователь частоты, первый вход которого является информационным входом устройства, а второй вход соединен с выходом управляемого генератора, фильтр нижних частот, четыре детектора, три коррелятора, умножитель, сумматор, управляемый тактовый генератор и дискриминатор фазовой автоподстройки частоты, выходы первого, второго и третьего коррелятора соединены с входами соответственно первого, второго и третьего детекторов, введены усилитель высокой частоты, второй преобразователь частоты, гетеродин, четвертый, пятый и шестой корреляторы, пятый и шестой детекторы, резонансный усилитель, пороговый элемент, пять интеграторов, блок выделения максимального сигнала, формирователь кода канала, частотный дискриминатор, генератор частоты маркера, формирователь сигнала подстройки управляемого генератора, для генератора псевдослучайной последовательности, два коммутатора задержки, делитель частоты импульсов, ключ, формирователь сигналов управления, генератор опорной частоты, блок выборки-хранения, пропорционально-интегрирующий фильтр, детектор абсолютного значения и преобразователь "напряжение-частота", причем выход первого преобразователя частоты через усилитель высокой частоты соединены с первым входом второго преобразователя частоты, второй вход которого соединен с выходом гетеродина, а выход второго преобразователя частоты подключен к входу фильтра нижних частот, выход которого соединен с первыми информационными входами с первого по шестой корреляторов, выходы четвертого и пятого корреляторов соединены с входами соответственно четвертого и пятого детекторов, выходы первого-пятого детекторов подключены соответственно к информационным входам первого-пятого интеграторов, выходы которых подключены соответственно к входам блока выделения максимального сигнала, выходы которого подключены соответственно к входам формирователя кода канала, группа из четырех выходов которого соединен соответственно с первым четвертым управляющими входами первого и второго коммутаторов задержки, пятые управляющие входы которых и вход управления режимом работы формирователя сигналов управления объединены и соединены с выходом отсутствия сигнала обнаружения формирователя кода канала, четвертый выход группы выходов которого соединен также с входом установки полосы пропускания пропорционально -интегрирующего фильтра, информационный вход которого соединен с выходом блока выборки-хранения, информационный вход которого соединен с выходом дискриминатора фазовой автоподстройки частоты, первый и второй информационный входы которого соединены с выходами соответственно второго и третьего интеграторов, входы сброса всех интеграторов объединены и соединены с выходом "Сброс" формирователя сигналов управления, вход запуска которого является входом запуска устройства, а выходы "Сигнал обнаружения информации" и "Конец зоны поиска" формирователя сигналов управления являются соответствующими выходами устройства, выход шестого коррелятора через последовательно соединенные резонансный усилитель и шестой детектор подключен к информационному входу порогового элемента, вход задания порога которого является входом задания порога устройства, а выход порогового элемента является выходом маркера сигнала синхронизации устройства, выход генератора частоты маркера подключен к первому входу умножителя, выход которого соединен с вторым информационным входом шестого коррелятора, выход четвертого коррелятора подключен также к входу частотного дискриминатора, выход которого подключен к входу формирователя сигнала подстройки управляемого генератора, выходы которого соединены соответственно с входами управляемого генератора, выход пропорционально -интегрирующего фильтра соединен с входом детектора абсолютного значения, информационный выход которого соединен с входом преобразователя "напряжение-частота", выход которого соединен с первым управляющим входом управляющего тактового генератора, второй управляющий вход которого подключен к знаковому выходу детектора абсолютного значения, а тактовый вход управляемого тактового генератора подключен к выходу генератора опорной частоты, выход управляемого тактового генератора является выходом тактовых импульсов устройства и соединен с информационным входом ключа и первым тактовым входом формирователя сигналов управления, первый тактовый выход которого подключен к управляющему входу ключа, выход которого соединен с входом делителя частоты импульсов и с тактовыми входами первого и второго генераторов псевдослучайной последовательности, выход первого генератора псевдослучайной последовательности соединен с первым входом сумматора и информационным входом первого коммутатора задержки, первый -четвертый выходы которого подключены к вторым информационным входам соответственно первого-четвертого корреляторов, четвертый выход первого коммутатора задержки соединен также с вторым входом умножителя, выход делителя частоты импульсов подключен к второму тактовомоу входу формирователя сигналов управления, выход второго генератора псевдослучайной последовательности подключен к второму входу сумматора и информационному входу второго коммутатора задержки, выход которого является выходом "Информационная последовательность" устройства, а выход сумматора соединен с вторым информационным входом пятого коррелятора, вход записи сигнала блока выборки хранения и вход считывания пропорционально-интегрирующего фильтра объединены и соединены с вторым тактовым выходом формирователя сигналов управления.

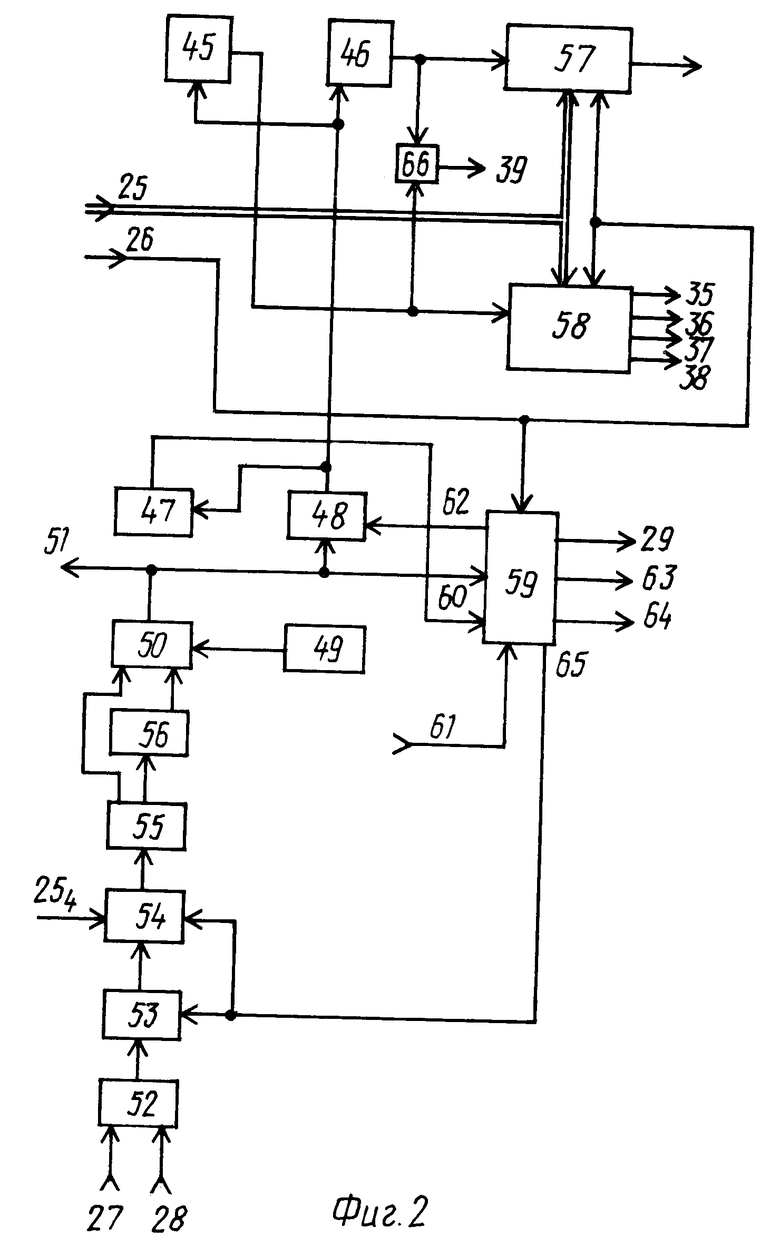

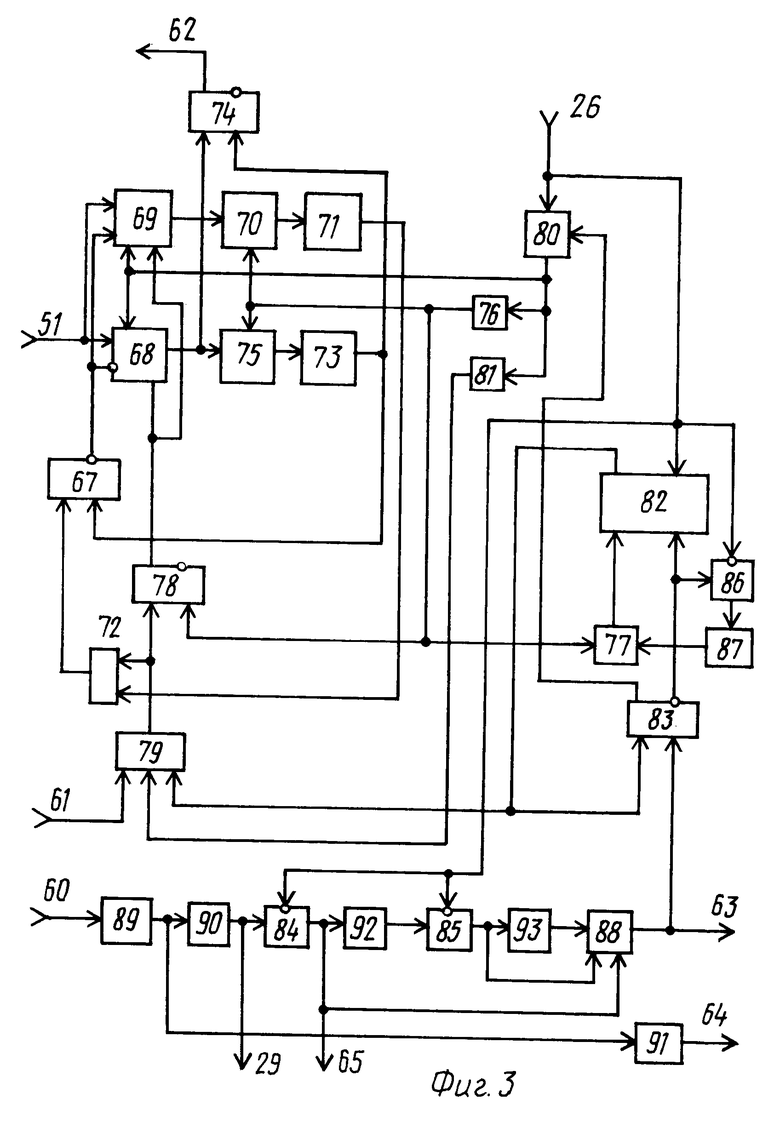

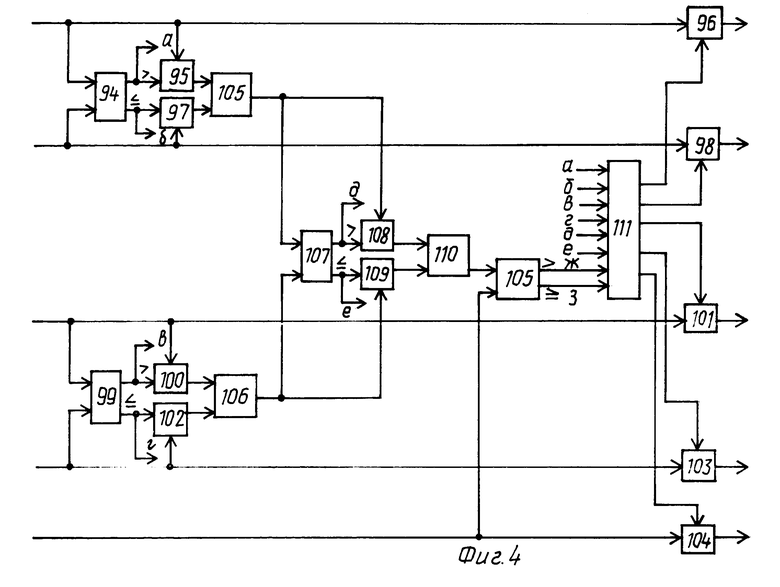

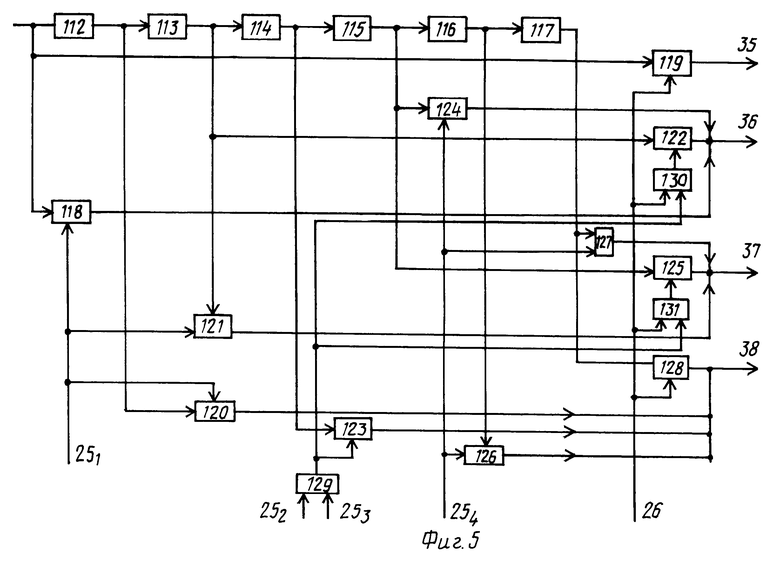

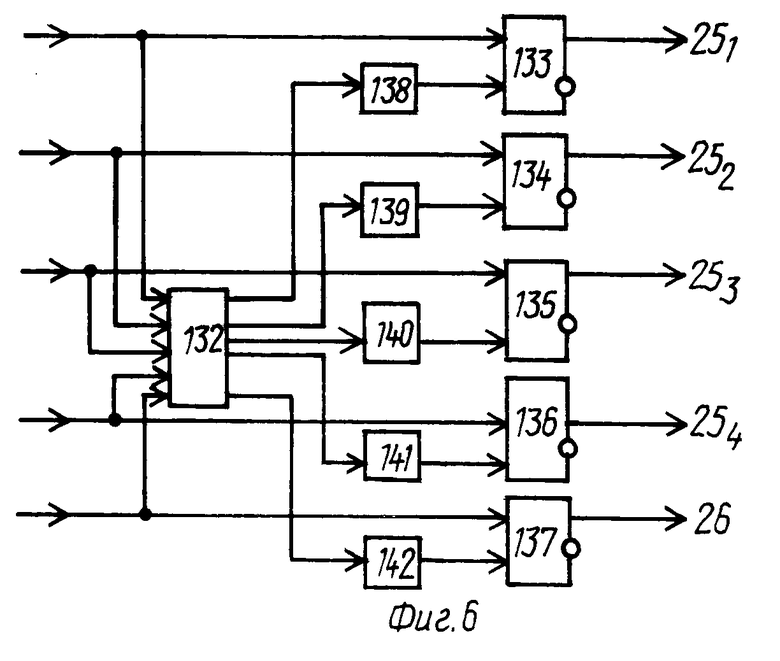

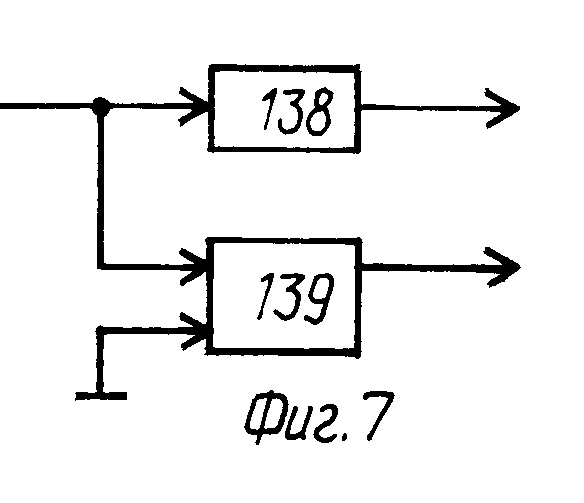

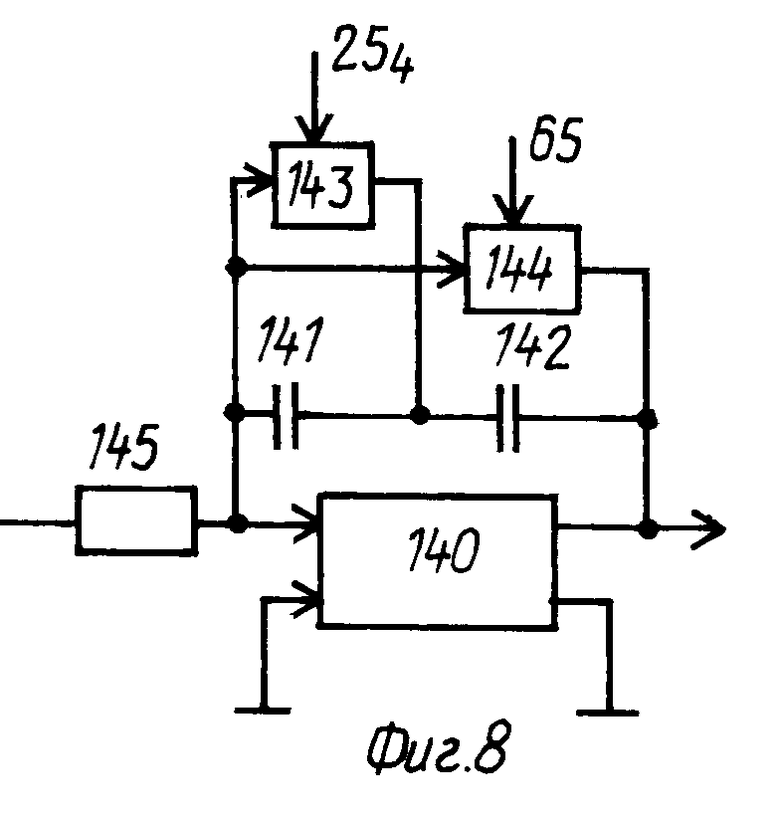

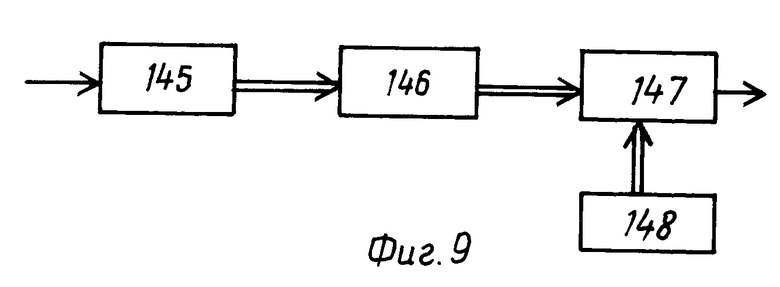

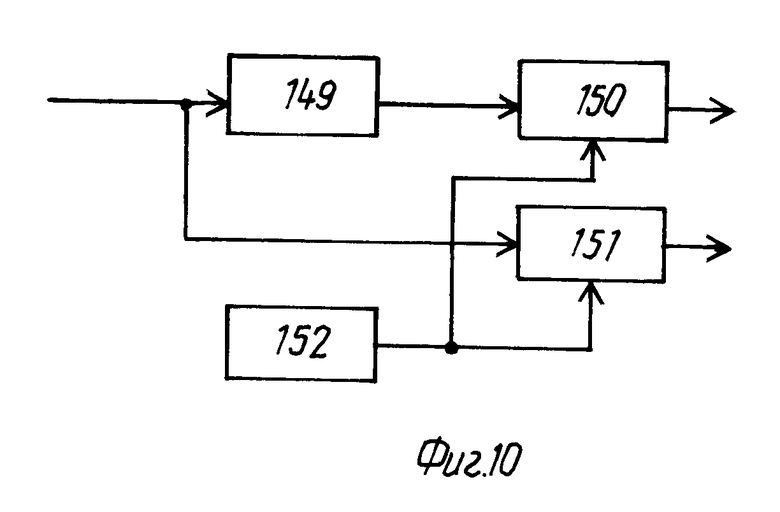

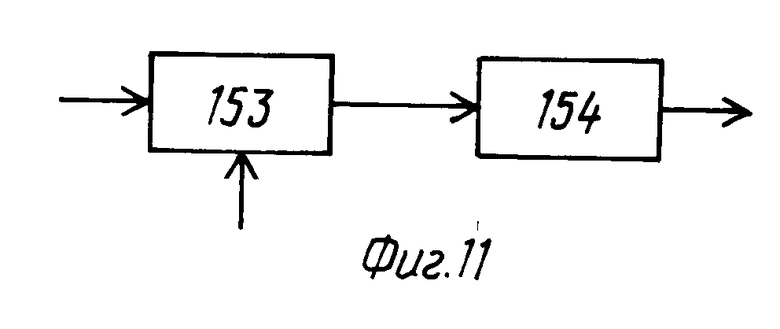

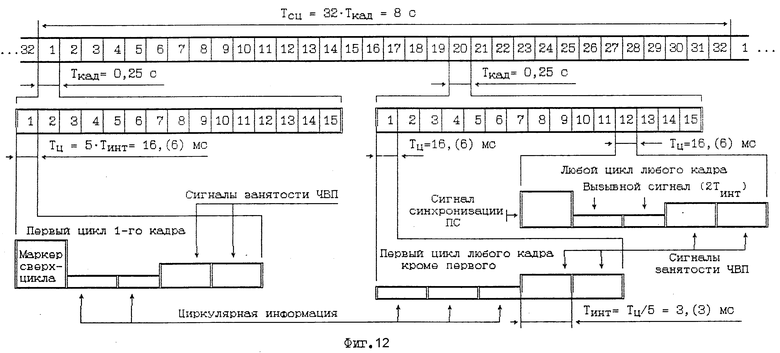

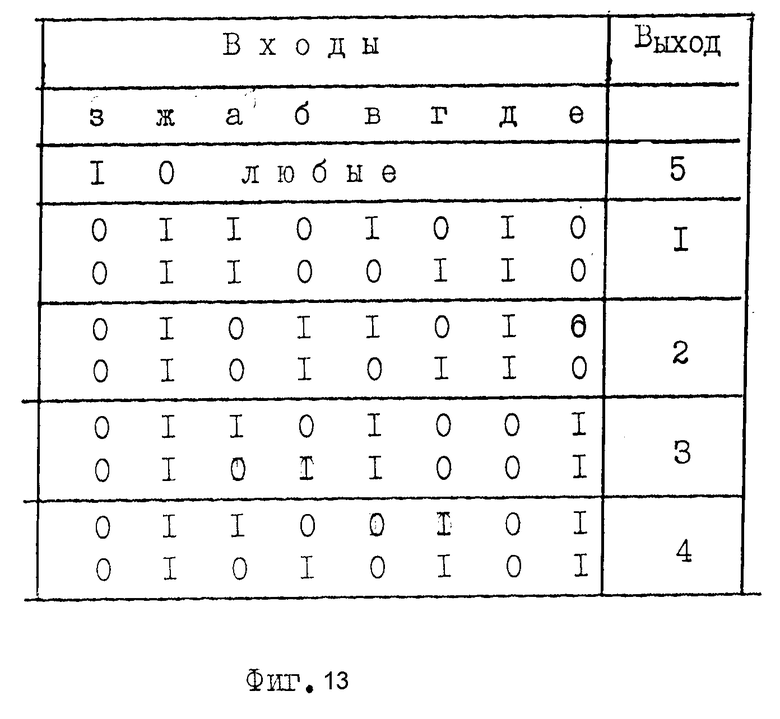

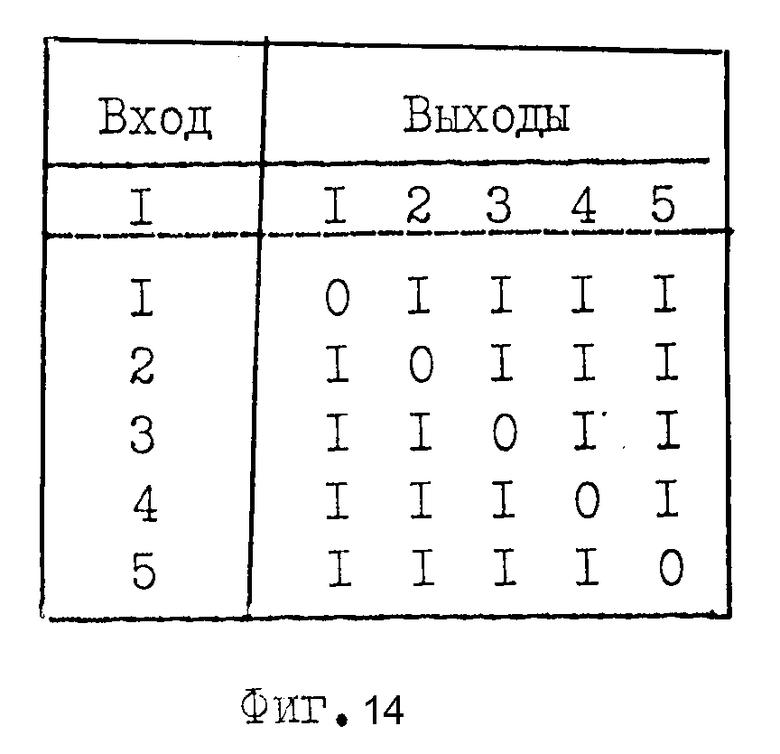

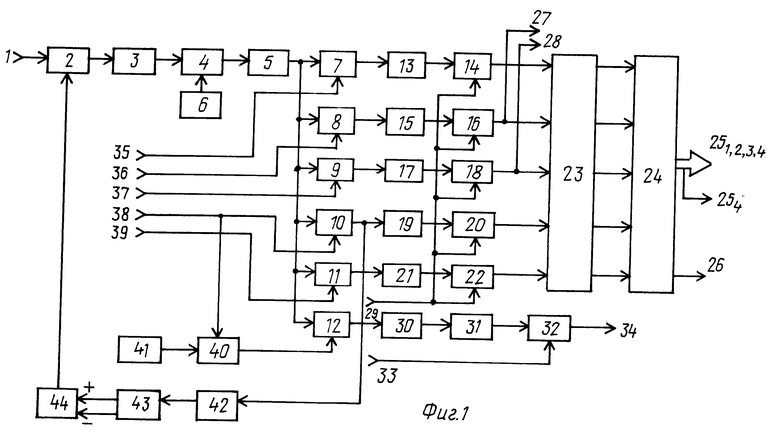

На фиг. 1 и фиг. 2 приведена схема устройства, на фиг. 3 вариант выполнения формирователя сигналов управления, на фиг. 4 вариант выполнения блока выделения максимального сигнала, на фиг. 5 вариант выполнения коммутатора задержки, на фиг. 6 вариант выполнения формирователя кода канала, на фиг. 7 вариант выполнения детектора максимального сигнала, на фиг. 8 схема, поясняющая принцип построения пропорционально-интегрирующего фильтра, на фиг. 9 вариант выполнения частотного дискриминатора, на фиг. 10 вариант выполнения формирователя сигналов подстройки управляемого генератора, на фиг. 11 схема корреляторов, на фиг. 12 структура сигнала синхронизации в системе, на фиг. 13 таблица соответствия сигналов дешифратора блока выделения максимального сигнала, на фиг. 14 таблица соответствия сигналов дешифратора формирователя кода канала.

Устройство содержит вход 1, являющийся первым входом первого преобразователя 2 частоты, и последовательно соединенные усилитель 3 высокой частоты, второй преобразователь 4 частоты, фильтр 5 нижних частот, выход первого преобразователя 2 частоты соединен с входом усилителя 3 высокой частоты, а другой вход второго преобразователя 4 частоты подключен к выходу гетеродина 6. Выход фильтра 5 нижних частот соединен с первыми информационными входами первого 7, второго 8, третьего 9, четвертого 10, пятого 11 и шестого 12 корреляторов, выход первого коррелятора 7 через первый детектор 13 соединен с информационным входом первого интегратора 14, выход второго коррелятора 8 через второй детектор 15 соединен с информационным входом второго интегратора 16, выход третьего коррелятора 9 через третий детектор 17 подключен к информационному входу третьего интегратора 18, выход четвертого коррелятора 10 через четвертый детектор 19 подключен к информационному входу четвертого интегратора 20, а выход пятого коррелятора 11 через пятый детектор 21 соединен с информационным входом пятого интегратора 22, выходы первого 14, второго 16, третьего 18, четвертого 20 и пятого 22 интеграторов соединены соответственно с входами блока 23 выделения максимального сигнала, выходы которого подключены соответственно к входам формирователя 24 кода канала, первые четыре выхода которого образуют группу выходов 25, а выход 26 является выходом отсутствия обнаружения сигнала, позициями 27 и 28 обозначены соответственно выходы второго 16 и третьего 18 интеграторов, а установочные входы первого 14, второго 16, третьего 18, четвертого 20 и пятого 22 интеграторов объединены и обозначены позицией 29. Выход шестого коррелятора 12 через последовательно соединенные резонансный усилитель 30 и шестой детектор 31 подключен к информационному входу порогового элемента, вход 33 задания порога которого является соответствующим входом устройства, а выход 34 порогового элемента 32 является выходом маркера сигнала синхронизации устройства. Позициями 35, 36, 37, 38 и 39 обозначены вторые информационные входы соответственно первого 7, второго 8, третьего 9, четвертого 10 и пятого 11 корреляторов. Первый вход умножителя 40 соединен с выходом генератора 41 частоты маркера, а выход умножителя 40 подключен к второму информационному входу шестого коррелятора 12, выход четвертого коррелятора 10 соединен с входом частотного дискриминатора, выход которого подключен к входу формирователя сигнала подстройки управляемого генератора, выходы которого соединены с входами управляемого генератора 44, выход которого соединен с вторым входом первого преобразователя 2 частоты.

Устройство также содержит первый 45 и второй 46 генераторы псевдослучайной последовательности, делитель 47 частоты импульсов, ключ 48, генератор 49 опорной частоты, выход которого соединен с тактовым входом управляемого тактового генератора 50, выход которого является тактовым выходом 51 и соединен с информационным входом ключа, входы 27 и 28 дискриминатора 52 фазовой автоподстройки частоты соединены соответственно с выходами второго 16 и третьего 18 интеграторов, а выход дискриминатора 52 соединен с информационным входом блока 53 выборки -хранения, выход которого подключен к информационному входу пропорционально -интегрирующего фильтра, выход которого соединен с входом детектора абсолютного значения 55, информационный выход которого подключен к входу преобразователя 56 "напряжение-частота", выход которого соединен с первым информационным входом управляемого тактового генератора 50, второй информационный вход которого соединен со знаковым выходом детектора 55 абсолютного значения.

Устройство содержит также второй 57 и первый 58 коммутаторы задержки первые четыре управляющих входа которых подключены к группе выходов 25 формирователя 24 кода канала, а их пятые управляющие входы и вход управления режимом работы формирователя 59 сигналов управления объединены и соединены с выходом 26 формирователя 24 кода канала, четвертый выход группы 25 выходов которого соединен с входом установки режима работы пропорционально -интегрирующего фильтра 54. Выход 51 управляемого тактового генератора 50 соединен также с первым тактовым входом формирователя сигналов управления, входом запуска которого является вход 61, а второй тактовый вход 60 соединен с выходом делителя 47 частоты импульсов, первый тактовый выход 62 формирователя 58 сигналов управления соединен с управляющим входом ключа 48, выход которого подключен к входу делителя 47 частоты импульсов и тактовым входам первого 45 и второго 46 генераторов псевдослучайной последовательности. Выходом "Сигнал обнаружения информации" является выход 63, а выходом сигнала "Конец зоны поиска" является выход 64 формирователя 59 сигналов управления, выход 65 которого является вторым тактовым выходом и соединен с входом записи сигнала блока 53 выборки-хранения и входом обнуления пропорционально -интегрирующего фильтра 54. Выход первого генератора 45 псевдослучайной последовательности соединен с первым входом сумматора 66 и информационным входом первого коммутатора 58 задержки, первый 35, второй 36, третий 37 и четвертый 38 выходы которого соединены соответственно с вторыми информационными входами первого 7, второго 8, третьего 9 и четвертого 10 корреляторов, выход 38 соединен также с вторым входом умножителя 40. Выход второго 46 генератора псевдослучайной последовательности соединен с вторым входом сумматора 66 и информационным входом второго коммутатора 57 задержки, выход которого является выходом "Информационная последовательность" устройства, а выход сумматора 66 подключен к второму информационному входу пятого коррелятора 11.

Формирователь 59 сигналов управления (фиг. 3) содержит триггер 67 инверсный выход которого соединен с инверсным входом элемента И 68 и первым входом элемента И 69, второй вход которого и первый прямой вход элемента И 68 объединены и являются первым тактовым входом 51 формирователя, выход элемента И 69 соединен с информационным входом счетчика 70, выход переполнения которого через формирователь 71 импульсов подключен к первому входу элемента ИЛИ 72, выход которого соединен с нулевым входом триггера 67, единичный вход которого подключен к выходу формирователя 73 импульсов и единичному входу триггера 74, прямой выход которого является первым тактовым выходом 62 формирователя, а нулевой вход триггера 74 соединен с выходом элемента И 68 и информационным входом счетчика 75 импульсов, выход переполнения которого соединен с входом формирователя 73 импульсов. Установочные входы счетчиков 70 и 75 импульсов подключены к выходу формирователя 76 импульсов, первому входу элемента ИЛИ 77 и единичному входу триггера 78, нулевой вход которого соединен с выходом элемента ИЛИ 79 и вторым входом элемента ИЛИ 72, а прямой выход триггера 78 соединен с вторым прямым входом элемента И 68 и третьим входом элемента И 69, четвертый вход которого и третий прямой вход элемента И 68 объединены и подключены к выходу элемента И 80, входу формирователя 76 импульсов и входу формирователя 81 импульсов, выход которого подключен к первому входу элемента ИЛИ 79, второй вход которого является входом 61 запуска формирователя 59 сигналов управления, а третий вход элемента ИЛИ 79 подключен к выходу переполнения таймера 82 и нулевому входу триггера 83, прямой выход которого соединен с первым входом элемента И 80, второй вход которого является входом 26 формирователя 59 сигналов управления и соединен с инверсными входами элементов И 84, 85, 86, выход элемента И 86 подключен к входу формирователя 87 импульсов, выход которого подключен к второму входу элемента ИЛИ 77, выход которого соединен с установочным входом таймера 52, вход разрешения работы которого и прямой вход элемента И 86 соединены с инверсным выходом триггера 83, единичный вход которого подключен к выходу элемента И 88, являющимся выходом 63 "Сигнал обнаружения информации" формирователя 89 сигналов управления, вторым тактовым входом 60 формирователя 59 сигналов управления является вход счетчика 89, выход переполнения которого подключен к входу формирователя 90 импульсов и входу счетчика 91 импульсов, выход переполнения которого является выходом 64 "Конец зоны поиска" формирователя 59 сигналов управления, выход формирователя 90 импульсов является выходом 29 сброса и соединен с прямым входом элемента И 84, выход которого является вторым тактовым выходом 65 и соединен с первым входом элемента И 88 и входом элемента 92 задержки, выход которого соединен с прямым входом элемента И 85, выход которого подключен к второму входу элемента И 88 и входу элемента 93 задержки, выход которого подключен к третьему входу элемента И 88.

Блок 23 выделения максимального сигнала (фиг. 4) содержит схему 94 сравнения, первый вход которой, информационный вход ключа 95 и информационный вход ключа 96 является первым входом блока, вторым входом которого является второй вход схемы сравнения 94, информационный вход ключа 97 и информационный вход ключа 98, третьим входом блока является первый вход схемы сравнения 99, информационный вход ключа 100 и информационный вход ключа 101, четвертым входом блока является второй вход схемы сравнения 99, информационный вход ключа 102 и информационный вход ключа 108, пятым входом блока является информационный вход ключа 104 и первый вход схемы сравнения 105, выход "больше" схемы сравнения 94 соединен с управляющим входом ключа 95, выход которого подключен к первому входу элемента ИЛИ 105, второй вход которого соединен с выходом ключа 97, управляющий вход которого подключен к выходу "меньше или равно" схемы сравнения 94, выход "больше" схемы сравнения 99 соединен с управляющим входом ключа 100, выход которого подключен к первому входу элемента ИЛИ 106, второй вход которого соединен с выходом ключа 102, управляющий вход которого подключен к выходу "меньше или равно" схемы 99 сравнения, выход элемента ИЛИ 105 подключен к первому входу схемы сравнения 107 и информационному входу ключа 108, а выход элемента ИЛИ 106 соединен с вторым входом схемы сравнения 107 и информационным входом ключа 109, управляющий вход которого подключен к выходу "меньше или равно" схемы 107 сравнения, выход "больше" которой соединен с управляющим входом ключа 108, выход которого подключен к первому входу элемента ИЛИ 110, второй вход которого соединен с выходом ключа 109, выход элемента ИЛИ 110 подключен к второму входу схемы 105 сравнения, дешифратор 111, входы которого подключены соответственно к выходам схем сравнения 94, 99, 105 и 107, выходы которого являются соответственно управляющими входами ключей 96, 98, 101, 103 и 104, выходы ключей являются выходами блока.

Коммутаторы 57, 58 задержки выполнены одинаково и содержат (фиг. 5) последовательно соединенные элементы задержки 112, 113, 114, 115, 116 и 117, информационным входом коммутатора является вход элемента 112 задержки, соединенный с информационным входом ключа 118 и информационным входом ключа 119, выход элемента 112 задержки подключен также к информационному входу ключа 120, а выход элемента 113 задержки соединен с информационными входами ключей 121 и 122, выход элемента 114 задержки подключен к информационному входу ключа 123, а выход элемента задержки 115 подключен к информационным входам ключей 124 и 125, выход элемента 116 задержки соединен с информационным входом ключа 126, а выход элемента задержки 117 подключен к первому входу элемента ИЛИ 127 и информационному входу ключа 128, первым выходом коммутатора является выход ключа 119, вторым выходом коммутатора является объединенный выход ключей 118, 122 и 124, третьим выходом коммутатора являются объединенные выходы ключей 121 и 125 и выход элемента ИЛИ 127, четвертым выходом коммутатора являются объединенные выходы ключей 120, 123, 126 и 128, первым управляющим входом коммутатора являются объединенные управляющие входы ключей 118, 120 и 121, вторым и третьим управляющими входами коммутатора являются соответственно первый и второй входы элемента ИЛИ 129, выход которого соединен с управляющим входом ключа 123 и первыми входами элементов ИЛИ 130, 131, выходы которых подключены к управляющим входам соответственно ключей 122 и 125, четвертым управляющим входом коммутатора являются объединенные управляющие входы ключей 124 и 126 и второй вход элемента ИЛИ 127, а пятым управляющим входом коммутатора являются объединенные управляющие входы ключей 119 и 128 и вторые входы элементов ИЛИ 130, 131.

Формирователь 24 кода канала (фиг. 6) содержит дешифратор 132, триггеры 133, 134, 135, 136 и 137, формирователи импульсов 138, 139, 140, 141 и 142. Первым пятым входами формирователя являются нулевые входы соответственно триггеров 133-137. Первый пятый входы дешифратора 132 соединены соответственно с первым-пятым входами формирователя, первый-пятый выходы дешифратора соединены с входами соответственно формирователей импульсов 138-142, выходы которых соединены с единичными входами соответственно триггеров 133-136, выходы триггеров 133-136 образуют группу выходов 25, выход триггера 137 является выходом 26 формирователя.

Детектор абсолютного значения может быть выполнен в виде (фиг. 7) пикового детектора 138 и схемы сравнения 139, выход "больше или равно" которой является знаковым выходом детектора, информационным выходом которого является выход пикового детектора 138, вход которого и первый вход схемы сравнения объединены и является входом детектора, а второй вход схемы сравнения соединен с шиной нулевого потенциала.

Пропорционально-интегрирующий фильтр 54 (фиг. 8) может быть выполнен в виде операционного усилителя 140 с конденсаторами 141 и 142 в цепи обратной связи и ключей 144, 145, информационные входы ключей объединены и соединены с входом операционного усилителя, выход ключа 143 соединен со средней точкой конденсаторов, а выход ключа 144 подключен к выходу операционного усилителя. Управляющий вход ключа 143 является входом 254, и управляющий вход ключа 144 является входом 65 фильтра.

Частотный дискриминатор 42 (фиг. 9) может быть выполнен в виде последовательно соединенных аналого -цифрового преобразователя 145, измерителя частоты 146 и схемы 147 сравнения кодов, другая группа входов которой подключена к выходу датчика 148 номинального значения частоты, входом дискриминатора является вход аналого -цифрового преобразователя 145, а выходом -выход "больше или равно" схемы 147 сравнения кодов.

Формирователь сигналов подстройки управляемого генератора 43 (фиг. 10) может быть выполнен в виде элемента НЕ 149, выход которого подключен к входу первого элемента И 150, входом формирователя является вход элемента НЕ 149, соединенный с первым входом второго элемента и 151, вторые входы элементов И 150, 151 подключены к выходу генератора 152 импульсов, а выходами формирователя являются выходы элементов И.

Корреляторы 7-12 (фиг. 11) выполнены в виде перемножителя 152, входы которого являются входами коррелятора, а выход перемножителя соединен с входом полосового фильтра 154, выход которого является выходом коррелятора.

Система спутниковой связи, для которой предназначено данное устройство, является многоканальной децентрализованной синхронной системой связи, в которой каждая абонентская станция (АС) может одновременно обеспечить связь с несколькими абонентами по различным направлениям и адресам (принцип построения "каждый с каждым").

При этом все абонентские станции однотипны. Каждая из них может работать в режиме центральной станции, передающей синхросигнал, по которому входят в синхронизм остальные станции, и в режиме периферийной станции, когда она работает в режиме приема синхросигнала центральной станции и синхронизации своей работы осуществляет по синхросигналу центральной станции. Режим приема синхросигнала и является объектом рассмотрения в данном изобретении.

Структура синхросигнала, который передается в служебном канале, приведена на фиг. 12.

Сверхцикл сигнала синхронизации составляет 8с (Tсц=8с) и делится на 32 кадра, каждый из которых имеет длительность Tкад=250 мс. Каждый кадр делится на 15 циклов длительность Tц=16, (6) мс. Он, в свою очередь, состоит из пяти частотно-временных интервалов (позиций) длительность Tинт=3, (3) мс.

В служебном частотном канале передаются синхросигналы центральной (ЦС) периферийной (ПС) станций, сигналы занятости информационно-частотных каналов и служебные сигналы для организации связи между станциями.

Информационное наполнение любого цикла, за исключением первого, одинаково.

1. В 1-м цикле первого кадра передается:

на первом временном интервале маркер сверхцикла, представляющий меандр с частотой 14,4 кГц и длительностью маркера 3,3 мс;

на втором и третьем временных интервалах циркулярная информация;

на четвертом и пятом временных интервалах сигналы занятости частотно -временных позиций в информационно -частотном канале.

2. В первом цикле любого кадра, кроме первого, передается:

на первых трех частотно-временных интервалах циркулярная информация;

на четвертом и пятом частотно -временных позициях сигналы занятости частотно-временных позиций в информационно-частотном канале.

3. Во всех циклах, кроме первого, передается:

на первом временном интервале сигнал синхронизации ЦС по передаче;

на втором и третьем временных интервалах сигналы организации связи между абонентами (вызывной сигнал);

на четвертом и пятом временных интервалах сигналы занятости частотно -временных позиций в информационно -частотном канале 7.

Видеосигналами в служебном частотном канале (СЧК) являются функции Уолша, образующие пространство ортогональных сигналов. Частота следования функций Уолша (тактовая частота) составляет 57,6 кГц. Видеосигналы перемножаются с циклической псевдослучайной последовательностью (ЦСП). Каждый цикл ЦСП состоит из 1024 элементов, следующих с частотой 921,6 кГц. Результирующий сигнал поступает на фазовый модулятор.

В СЧК используются три типа ПСП:

1. Синхропоследовательность ЦС (СП ЦС). После перемножения СП ЦС и функции Уолша N 1 (постоянный ток) на ЦС образуется синхросигнал ССцс, который передается всем станциям сети. Он передается центральной станцией постоянно за исключением тех временных интервалов, где ЦС передает циркулярную информацию, или вызывные сигналы, или сигналы занятости. Любой станцией при работе в режиме ЦС образуется один и тот же синхросигнал ССцс.

2. Синхропоследовательность ЦС (СЦ ПС). Она используется для образования синхросигнала CCцс, по которому входят в синхронизм по передаче периферийные станции. Синхросигналы CCпс передаются на первых временных интервалах циклов.

3. Информационная ПСП. После перемножения информационной псевдослучайной последовательности с информационным сигналом любой станции образуется информационный радиосигнал, который может принять и обработать каждая станция сети, так как информационная последовательность для всех станций одна и та же.

Информационная псевдослучайная последовательность перемножается также с сигналами циркулярной информации, с вызывными сигналами и сигналами занятости частотно-временных интервалов.

Каждой абонентской станции в СЧК отводится конкретный временной интервал для передачи CCпс.

Принцип работы устройства состоит в следующем.

Синхросигнал синхропоследовательность центральной станции (СП ЦС) представляет собой почти непрерывную псевдослучайную последовательность с длительностью периода 1,1 мс, тактовой частотой 921,6 кГц, числом элементов 1024. Каждые 8 с в течение 3,3 мс на сигнал накладывается меандр частотой 14,4 кГц, образуя маркер сверхцикла.

Задача устройства состоит в том, чтобы при работе абонентской станции как периферийной (режим приема) обеспечить надежное выделение синхросигнала центральной станции и обеспечить сложение за ним по частоте и задержке, выработать маркер сверхцикла и другие сигналы для управления работой станции.

Особенность поиска шумоподобного сигнала заключается в том, что область тела неопределенности в частотно -временном пространстве невелика. Поэтому сигнал может быть обнаружен при достаточно близких значениях частоты опорных сигналов при корреляционном методе обнаружения. Необходимо также учитывать, что в системах спутниковой связи частота и задержка сигнала изменяется медленно. Поэтому в работу устройства положен последовательно -параллельный метод обнаружения, сущность которого состоит в следующем.

Принимаемый сигнал преобразуется в сигнал с низкой промежуточной частотой (28,8 кГц) и подается в перемножитель, на другой вход которого подается эталонный сигнал с той же ПСП, что и принимаемый. В результате перемножения при совпадении сигналов во времени манипуляция снимается, а узкополосным фильтром выделяется монохроматический сигнал. Полоса фильтра определяет время интегрирования сигнала узкополосным фильтром. Амплитуда сигнала на выходе коррелятора зависит от степени близости на временной шкале принимаемого и эталонного сигналов. Поэтому после детектирования и дополнительного интегрирования на интервале, равном длительности четырех ЦСП, выходной сигнал подается на пороговое устройство. Для ускорения поиска в устройстве используется четыре параллельно работающих канала, отличающихся тем, что в каждом из них эталонная ПСП задержала на один такт по отношению к эталонной ПСП в предыдущем канале обнаружения. Превышение в канале принимаемого сигнала над пороговым уровнем дает основание для принятия решения о наличии сигнала. Такое построение канала обнаружения с двумя этапами интегрирования исключает необходимость выделения несущего колебания с точностью до фазы, что очень сложно в реализации.

Пороговый уровень формируется в дополнительном пятом канале. Он отличается от других тем, что в качестве сигнала (эталонный последовательности) используется логическая смесь СП и ИН. Выходным эффектом канала является средний уровень шумовой составляющей корреляционной свертки сигналов. Превышение этого уровня в каком-либо канале является признаком наличия сигнала.

Такой эффект достигается только в том случае, если входной сигнал не только совпадает по времени с эталонным, но и частота сигнала близка к резонансной частоте фильтра. Поэтому путем перестройки гетередина можно добиться максимума выходного эффекта. Двухэтапное интегрирование позволяет разрешить противоречие между требованием обеспечения большого интервала накопления и необходимостью измерения частоты в достаточно широком диапазоне частот. Это позволяет сделать измерение частоты на выходе полосового фильтра, сравнение результатов измерения с номинальным значением и подстройку частоты гетеродина до требуемого значения. Поэтому поиск по частоте и задержке мало зависимы. Процесс измерения может происходить и при частичном совпадении принимаемой и эталонной ЦСП.

После обнаружения в каком-либо из четырех каналов сигнала, устройство переходит в режим автосопровождения по частоте и задержке, при котором происходит переключение каналов таким образом, что в контур подстройки по частоте подаются сигналы второго и третьего каналов, а в контур подстройки по задержке принимаемого сигнала подается сигнал четвертого канала, включенного по задержке теперь между вторым и третьим каналом. При кратковременных пропаданиях принимаемого сигнала состояние системы синхронизации запоминается, а при превышении пропадания сигнала более установленного, режим поиска возобновляется. Постройка по частоте и фазе возможно только при наличии обнаруженного сигнала.

Работает устройство следующим образом.

В исходном состоянии генераторы 44 и 50 вырабатывают сигналы с номинальной частотой, их подстройка отсутствует. Тактовый генератор 50 вырабатывает тактовые импульсы, которые поступают в другие блоки системы, на информационный вход ключа 48 и на тактовый вход формирователя 59. После его запуска сигналом со входа 61 в формирователе осуществляется счет тактовых импульсов и одновременно на выходе 62 появляется сигнал, который замыкает ключ 48. Тактовые импульсы начинают поступать и тактовые входы генераторов 45 и 46 начинают формировать псевдослучайные последовательности. Генератор 45 формирует синхропоследовательность СП ПС, а генератор 46 информационную синхропоследовательность ИП. Они логически суммируются в сумматоре 60, где формируется последовательность ИП+СП, а также поступают на один из коммутаторов 57, 58 задержки. В режиме поиска по задержке на выходах 35-38 образуются четыре синхропоследовательности СП (одна для каждого канала обнаружения) отличающиеся тем, что на каждом последующем выходе синхропоследовательность задержана на один такт относительно последовательности на предыдущем выходе. В коммутаторе 57 задержки используется только один выход, задержка которого равна задержке сигнала на четвертом выходе 38 коммутатора 58. После того как в формирователе 59 будет подсчитано 1024 импульса он запрещает прохождение следующих четырех тактовых импульсов от генератора 50 через ключ 48. Таким образом изменяется задержка по фазе сформированных синхропоследовательностей. Изменение задержки будет происходить до тех пор, пока не будет обнаружен сигнал центральной станции или не истечет заданное время поиска. С выходов коммутатора 58 и сумматора 66 синхропоследовательности поступают на вторые входы одного из корреляторов 7-11.

Сигнал с выхода отвального приемника поступает на вход преобразователя 2, с помощью которого осуществляется преобразование сигнала до частоты 70±20 МГц, усиливается усилителем 3 и с помощью преобразователя 4 осуществляется второе преобразование до частоты 28,8 кГц и после фильтрации и усиления фильтром 5 поступает на корреляторы. Двойное преобразование частоты входного сигнала позволяет довести промежуточную частоту до уровня на порядок меньший чем тактовая частота, в сигнале сама ПСП становится несущей, а непрерывное колебание огибающей.

Последовательно соединенные коррелятор, детектор и интегратор образуют четыре канала обнаружения сигнала, а канал формирования опорного напряжения, по отношению к которому принимается решение об обнаружении сигнала состоит из коррелятора 11, детектора 21 и интегратора 22. Пока в любом из каналов поиска сигнал не превысит опорное напряжение существует сигнал на пятом выходе блока 23 и на выходе 26 формирователя 24.

В каждом из каналов обнаружения с помощью перемножителей 153 снимается манипуляция входного сигнала, а полосовой фильтр 154 является первым интегратором канала. Проведенное снижение промежуточной частоты сигнала позволяет выполнить полосовой фильтр с очень высокой добротностью, его полоса сравнима с длительностью ПСП, что обеспечивает хорошие интегрирующие свойства фильтра и достаточно высокое соотношение сигнал/шум на его выходе. Детекторы 13, 15, 17, 19 и 21 выполнены в виде амплитудных линейных детекторов, поэтому на их выходе воспроизводится корреляционная функция сигнала. Повторное интегрирование с помощью интеграторов позволяет расширить интервал интегрирования на длительность нескольких ПСП (в данном случае 4).

При превышении в каком-либо канале обнаружения величины опорного сигнала, формируемого в пятом канале, на соответствующем выходе блока 23 и соответствующем выходе 25 формирователя появляется единичный сигнал, а сигнал на выходе 26 обнуляется. При этом в коммутаторах 57 и 58 происходит переключение задержки ПСП, а формирователь 59 включает цепь фазовой автоподстройки. Перекоммутация выходов в коммутаторах 57 и 58 осуществляется по следующему правилу.

Если обнаружение произошло в первом канале, то на месте выхода 35 подключается выход 36, на место выхода 36 выход 37, а выход 38 подключается к выходу элемента задержки 112, т.е. четвертый канал становится по величине задержки между вторых и третьими каналами. Первый канал не используется.

Если обнаружение произошло во втором или третьем канале, то их задержка не меняется, а четвертый выход 38 подключается к выходу элемента 114 задержки, т.е. опять по задержке образуется средняя точка.

Если обнаружение произошло в четвертом канале, то на его месте подключается третий канал, на место третьего второй канал, а четвертый канал опять подключается к средней точке по задержке между ними выходу элемента задержки 116.

При пропадании сигнала в каналах обнаружения и появления сигнала на входе 26 автоматически восстанавливается первоначальная схема подключения выходов 35-38.

После переключения начинается процесс точной подстройки частоты генератора 50 тактовых импульсов таким образом, чтобы максимальный сигнал появился на выходе четвертого канала. В начале процесса автоподстройки ширина полосы ФАПЧ выбирается более широкой за счет разомкнутого состояния ключа 143 в фильтре 54. Как только появляется сигнал на выходе 254 блока 24, то полоса фильтра уменьшается. Для формирования дискриминационной характеристики сигналы берутся с выхода интегратора 16 второго канала и выхода интегратора 18 третьего канала. Они поступают на дискриминатор 52, выполненный в виде блока вычитания, а разностный сигнал с него подается на блок выборки хранения. Сигналом с тактового выхода 65 формирователя 59 происходит запись сигнала в блок 53 и обнуление фильтра 54, который после обнуления начинает работу.

Сигнал с выхода фильтра 54 поступает на детектор 55, который определяет максимальное (пиковое) значение входного сигнала и знак сигнала путем его сравнения с нулевым потенциалом. При превышении нулевого уровня на выходе схемы 139 сравнения формируется единичный сигнал, в противоположном случае - нулевой. Эти сигналы поступают на вход генератора 50 для определения направления подстройки частоты. Величина подстройки определяется частотой импульсов с выхода преобразователя 56, в которые преобразуется сигнал с выхода детектора 55. При этом осуществляется отработка рассогласования в 0,5 τ до появления максимального сигнала на выходе четвертого канала.

Поиск сигнала по частоте осуществляется следующим образом.

Сигнал о выходе коррелятора 10 поступает на вход частотного дискриминатора 42, в котором с помощью аналого-цифрового преобразователя 145 преобразуется в цифровую форму и поступает на измеритель 146 частоты. С помощью схемы 147 сравнения кодов сравнивается измеренное и номинальное значение частоты. Сигнал логического нуля на выходе схемы 147 сравнения соответствует выполнению условия Fном≥Fизм, а сигнал логической единицы выполнению условия Fном ≅Fизм. С помощью формирователя 43 сигнал логического нуля проходит через элемент И 150 на уменьшение частоты управляемого генератора 44, а сигнал логической единицы через элемент И 151 увеличивает значение частоты генератора 44, который может быть выполнен по известным схемам синтезаторов частот.

Выделение маркера сверхцикла осуществляется с помощью коррелятора 12, на второй вход которого подается результат перемножения ПСП с входа 38 и сигнала генератора 41. Резонансный усилитель 30 и детектор выполняет роль интегратора, сигнал которого при превышении порогового уровня, задаваемого на входе 33, в пороговом элементе 32 используется в дальнейшем для формирования маркера сверхцикла.

Отдельные блоки устройства работают следующим образом.

В блоке 23 выделения максимального сигнала (фиг. 4) схемы 94, 99, 107 и 115 вырабатывают единичный сигнал на верхнем выходе (как это изображено на чертеже), если сигнал на верхнем входе больше сигнала на нижнем входе. В противном случае (сигнал на верхнем входе равен или меньше сигнала на нижнем входе) единичный потенциал появляется на нижнем выходе схем сравнения. Дешифратор 111 анализирует состояние схем сравнения и в зависимости от него вырабатывает сигнал на одном из своих выходов. Таблица соответствия сигналов на входе и выходе дешифратора приведена на фиг. 13. Таким образом всегда будет открыт только один из ключей 96, 98, 101, 103, 104, а в режиме поиска будет открыт ключ 104.

В формирователе 24 кода сигнала (фиг. 6) входным сигналом соответствующий ему триггер устанавливается в состояние, при котором на его прямом выходе появляется единичный сигнал, а остальные триггеры с помощью шифратора и формирователей импульсов переводятся в состояние, при котором на их прямых выходах устанавливается нулевой потенциал. Таблица соответствия между входными и выходными сигналами шифратора 132 приведена на фиг. 14. Формирователи импульсов вырабатывают короткий импульс по фронту перепада напряжения на соответствующем выходе шифратора для того, чтобы исключить неоднозначность состояния триггера в последующем при появлении сигнала на другом его входе.

В коммутаторах 57, 58 задержки (фиг. 5) величина задержки в каждом из элементов одинакова и равна 0,5 t где t длительность символа ПСП (тактовый интервал). В режиме поиска сигналом на входе 26 замкнуты ключи 119, 122, 125 и 128. В первом канале задержка ПСП нулевая, во втором t в третьем 2 t в четвертом 3 t При появлении сигнала на одном из входов 25, ключами осуществляется перекоммутация каналов в соответствии с вышеприведенным правилом.

Формирователь 58 сигналов управления (фиг. 3) работает следующим образом. формирователь 59 сигналов управления решает следующие задачи:

в режиме "поиск" запрещает прохождение четырех тактовых импульсов через ключ 47 на генераторы ПСП с периодом 4Tисп;

по истечении заданного времени поиска при необнаружении сигнала формирует сигнал "Конец зоны видимости";

при обнаружении сигнала в одном из каналов прекращает перестройку задержки и формирует внутренний сигнал разрешения подстройки тактовой частоты, которая осуществляется только при наличии обнаружения сигнала;

при трехкратном повторении сигнала обнаружения формирует внешний сигнал "СОИ" (сигнал обнаружения информации);

при кратковременном пропадании сигнала после фиксации сигнала СОИ запрещает подстройку частоты и включает таймер ожидания. При истечении установленного времени ожидания вырабатывается сигнал начальной установки, по которому возобновляется режим поиска.

В исходном состоянии (фиг. 3) все счетчики обнулены, таймер не запущен, триггер 67 установлен в состояние, при котором на его инверсном выходе имеется сигнал логической единицы, открывающий по соответствующему входу элемент И 69 и закрывающий по инверсному входу элемент И 68, триггер 78 установлен в состояние, при котором на его прямом выходе имеется сигнал логического нуля, закрывающий по соответствующим входам элементы И 68, 69, триггер 83 находится в состоянии, при котором на его прямом выходе имеется сигнал логической единицы, открывающий элемент И 80 по соответствующему входу. Триггер 74 установлен в состояние, при котором единичный сигнал имеется на его инверсном выходе и ключ 47 разомкнут.

Так как при отсутствии обнаружения сигнала единичный потенциал имеется на выходе 26 формирователя 24, то он поступает через элементы И 80 и открывает по соответствующим входам элементы И 68, 69.

Сигнал начала поиска со входа 61 через элемент ИЛИ 79 переводит триггер 78 в состояние, при котором единичный сигнал с его прямого выхода открывает по соответствующему входу элементы И 68, 69. А через элемент ИЛИ 72 триггер 67 переводится в состояние, при котором нулевой сигнал с его инверсного выхода открывает по соответствующему входу элемент И 68 и закрывает элемент И 69.

Тактовые импульсы поступают через элемент И 68 на счетчик 75, емкость которого равна 4nпсп, где nпсп число элементов псевдослучайной последовательности. Одновременно первый тактовый импульс с выхода элемента И 68 переводит триггер 74 в состояние, при котором единичный сигнал с прямого выхода разрешает прохождение тактовых импульсов на генераторы псевдослучайной последовательности через ключ 48.

Сигнал переполнения счетчика 75, носящий потенциальный характер, поступает на формирователь 73 импульсов, который по фронту сигнала вырабатывает короткий импульс, опрокидывающий триггер 74, и тактовые импульсы через ключ не проходят. Одновременно триггер 67 переводится в состояние, при котором сигналом с его инверсного выхода открывается элемент И 69 и закрывается элемент И 68. Теперь работает счетчик 70, емкость которого равна четырем. После переполнения счетчика 70 формирователь 71 вырабатывает короткий импульс: который через элемент ИЛИ 72 переводит триггер 67 в состояние, при котором нулевым сигналом с его инверсного выхода элемент И 69 закрывается, а элемент И 68 открывается. Первым прошедшим импульсом, прошедшим через элемент И 68, опрокидывается триггер 74 и тактовые импульсы через ключ снова начинают поступать на генераторы ПСП.

Произошло изменение задержки псевдослучайных последовательностей, подаваемых на корреляторы. Такое изменение задержки осуществляется периодически до тех пор, пока в одном из четырех каналов не произойдет обнаружение сигнала.

Счетчик 89, емкость которого равна четырем, считает импульсы "О ПРМ", соответствующие началу псевдослучайной последовательности. По его переполнению формирователь 90 вырабатывает короткий импульс, который по выходу 29 поступает на сброс интеграторов.

При обнаружении сигнала единичный потенциал на входе 26 исчезает, при этом на инверсным входам открываются элементы И 84, 85, 86, снимается напряжение с входа триггера 83 и по срезу сигнала формирователь 81 импульсов формирует импульс, который устанавливает в исходное состояние счетчики 70 и 75, и закрываются триггером 78 по соответствующему входу элементы И 68, 69 и подтверждается исходное состояние таймера 82. Произошло окончание режима поиска и начался режим подстройки по задержке. При этом импульсе с выхода формирователя 90 поступают на блок выборки-хранения и пропорционально -интегрирующий фильтр через открытый по инверсному входу элемент И 84.

При потере (пропадании) сигнала единичный потенциал снова появляется на входе 26 формирователя, поступают на вход запуска таймера 82, запуск которого запрещен сигналом с выхода триггера 83, закрывает по инверсному входу элемент И 84, прекращая режим автоподстройки. С выхода элемента И 80 сигнал открывает по соответствующим входам элементы И 68, 69, а короткий импульс с выхода формирователя 81, вырабатываемый по фронту сигнала на входе 26, через элемент ИЛИ 79 переводит триггер 78 в состояние, при котором единичный сигнал появляется на его прямом выходе, а у триггера 67 единичный сигнал появляется также на прямом выходе. Режим поиска возобновляется.

Если в процессе автоподстройки по задержке пропадания сигнала не происходит, то на элементе И 88 происходит совпадение трех импульсов, последовательно формируемых формирователем 90. Это обусловлено тем, что величина задержки в элементах 91, 92 задержки одинакова и равна длительности четырех ПСП. В результате совпадения на выходе элемента И 88 формируется сигнал обнаружения информации СОИ. Этот сигнал подается на выход системы и одновременно опрокидывает триггер 83, который разрешает запуск таймера 82 и закрывает элемент И 80 по соответствующему входу.

Теперь при кратковременном пропадании сигнала и появления потенциала на входе 26 возобновления режима поиска не произойдет, так как элемент И 80 закрыт и триггер 78 не будет переведен в состояние, открывающее элементы И 68, 69. В этом случае запускается таймер 82, который отрабатывает установленное время задержки и после его отработки сигнал с выхода таймера через открытый элемент ИЛИ 79 опрокидывает триггер 78 и возобновляется режим поиска. Если же до окончания работы таймера прием сигнала возобновляется, то формирователь 87 вырабатывает импульс, который через элемент ИЛИ 77 устанавливает таймер в исходное состояние.

Таким образом из структуры устройства и описания его работы видно, что назначение реализуется и указанный технический результат достигается.

Источник информации

1. Устройство синхронизации шумоподобных сигналов. Авт. свид. СССР N 576669, кл. H 04 J 3/06, 1975.

2. Устройство синхронизации шумоподобных сигналов. Авт. свид. СССР N 634473, кл. H 04 J 3/06, 1977.

3. Помехозащищенность радиосистем со сложными сигналами /Г.И. Тузов, В. А. Сивов, В.И. Прытков и др. Под ред. Г.И. Тузова. М. Радио и связь, 1985, с. 129, рис. 4, 12 (ближайший аналог).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА СИГНАЛА СИНХРОНИЗАЦИИ СПУТНИКОВОЙ СИСТЕМЫ СВЯЗИ | 1995 |

|

RU2093963C1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1982 |

|

SU1048581A1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШИРОКОПОЛОСНОГО СИГНАЛА | 1990 |

|

RU2040857C1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШИРОКОПОЛОСНОГО СИГНАЛА | 1991 |

|

RU2040858C1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШИРОКОПОЛОСНОГО СИГНАЛА | 1990 |

|

RU2037978C1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1976 |

|

SU1840434A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА В СИНХРОНИЗМ СИСТЕМЫ СВЯЗИ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1980 |

|

SU1840128A1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШИРОКОПОЛОСНОГО СИГНАЛА | 1990 |

|

RU2040856C1 |

| ПРИЕМОПЕРЕДАЮЩАЯ АППАРАТУРА ШИРОКОПОЛОСНЫХ ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 1979 |

|

SU1840119A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1979 |

|

SU1840071A1 |

Изобретение относится к многоканальным системам связи, построенным по принципу "каждый с каждым", и может быть использовано в системах синхронизации таких систем. Технический результат от использования изобретения заключается в расширении арсенала технических средств, сокращении продолжительности поиска по частоте, повышении отношения сигнал/шум в каждом из каналов поиска и улучшении качества фильтрации сигналов в каждом из каналов поиска. Устройство содержит четыре канала поиска, каждый из которых состоит из коррелятора, детектора и интегратора, кольцо фазовой автоподстройки частоты, кольца автоподстройки по частоте, блок выделения максимального сигнала, формирователь кода канала, два генератора псевдослучайной последовательности, коммутаторы задержки, формирователь сигналов управления. 14 ил.

Устройство поиска и сопровождения сигнала синхронизации в спутниковых системах связи по приему, содержащее первый преобразователь частоты, первый вход которого является информационным входом устройства, выход первого преобразователя частоты подключен к входу усилителя высокой частоты, а второй вход соединен с выходом управляемого генератора, фильтр нижних частот, два генератора псевдослучайной последовательности и четыре канала обнаружения сигнала, каждый из которых включает коррелятор, а также управляемый тактовый генератор, дискриминатор фазовой автоподстройки частоты и ключ, отличающееся тем, что в него введены канал формирования опорного напряжения, состоящий из последовательно соединенных коррелятора, детектора и интегратора, канал выделения маркера синхронизации, состоящий из последовательно соединенных коррелятора, резонансного усилителя и порогового элемента, второй преобразователь частоты, гетеродин, блок выделения максимального сигнала, формирователь кода канала, частотный дискриминатор, генератор частоты маркера, умножитель, формирователь сигнала подстройки управляемого генератора, сумматор, два коммутатора задержки, делитель частоты импульсов, формирователь сигналов управления, генератор опорной частоты, блок выборки-хранения, пропорционально-интегрирующий фильтр, детектор абсолютного значения и преобразователь напряжение частота, а в каждый канал обнаружения сигнала введены последовательно соединенные детектор и интегратор, а выход коррелятора соединен с входом детектора, причем выход усилителя высокой частоты соединен с первым входом второго преобразователя частоты, второй вход которого соединен с выходом гетеродина, а выход второго преобразователя частоты подключен к входу фильтра нижних частот, выход которого соединен с первыми информационными входами корреляторов каналов обнаружения сигнала, канала формирования опорного напряжения и канала выделения маркера синхронизации, выходы интеграторов каналов обнаружения сигнала и выход интегратора канала формирования опорного напряжения подключены к соответствующим входам блока выделения максимального сигнала, выходы которого подключены к соответствующим входам формирователя кода канала, четыре выхода которого соединены с соответствующими управляющими входами первого и второго коммутаторов задержки, пятые управляющие входы которых и вход управления режимом работы формирователя сигналов управления соединены с выходом отсутствия сигнала обнаружения формирователя кода канала, четвертый выход которого соединен также с входом установки полосы пропускания пропорционально-интегрирующего фильтра, информационный вход которого соединен с выходом блока выборки-хранения, информационный вход которого соединен с выходом дискриминатора фазовой автоподстройки частоты, первый и второй информационный входы которого соединены с выходами интеграторов соответственно второго и третьего каналов обнаружения сигнала, входы сброса интеграторов каналов обнаружения сигнала и канала формирования опорного напряжения соединены с выходом "Сброс" формирователя сигналов управления, вход запуска которого является входом запуска устройства, а выходы "Сигнал обнаружения информации" и "Конец зоны поиска" являются соответствующими выходами устройства, вход задания порога порогового элемента канала выделения маркера синхронизации является соответствующим входом устройства, а выход порогового элемента является выходом маркера сигнала синхронизации устройства, выход генератора частоты маркера подключен к первому входу умножителя, выход которого соединен с вторым информационным входом коррелятора канала выделения маркера синхронизации, выход коррелятора четвертого канала обнаружения сигнала подключен также к входу частотного дискриминатора, выход которого подключен к входу формирователя сигнала подстройки управляемого генератора, выходы которого соединены с соответствующими входами управляемого генератора, выход пропорционально-интегрирующего фильтра соединен с входом детектора абсолютного значения, информационный выход которого соединен с входом преобразователя напряжение частота, выход которого соединен с первым управляющим входом управляемого тактового генератора, второй управляющий вход которого подключен к знаковому выходу детектора абсолютного значения, а тактовый вход управляемого тактового генератора подключен к выходу генератора опорной частоты, выход управляемого тактового генератора является выходом тактовых импульсов устройства и соединен с информационным входом ключа и первым тактовым входом формирователя сигналов управления, первый тактовый выход которого подключен к управляющему входу ключа, выход которого соединен с входом делителя частоты импульсов и с тактовыми входами первого и второго генераторов псевдослучайной последовательности, выход первого генератора псевдослучайной последовательности соединен с первым входом сумматора и информационным входом первого коммутатора задержки, четыре выхода которого подключены к соответствующим вторым информационным входам корреляторов четырех каналов обнаружения сигнала, четвертый выход первого коммутатора задержки соединен также с вторым входом умножителя, выход делителя частоты импульсов подключен к второму тактовому входу формирователя сигналов управления, выход второго генератора псевдослучайной последовательности подключен к второму входу сумматора и информационному входу второго коммутатора задержки, выход которого является выходом "Информационная последовательность" устройства, а выход сумматора соединен с вторым информационным входом коррелятора канала формирования опорного напряжения, вход записи сигнала блока выборки-хранения и вход считывания пропорционально-интегрирующего фильтра соединены с вторым тактовым выходом формирователя сигналов управления.

| SU, авторское свидетельство, 576669, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| SU, авторское свидетельство, 634473, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| SU, авторское свидетельство, 1356229, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1997-10-20—Публикация

1995-04-21—Подача