Изобретение относится к электротехнике, в частности к защите электрических сетей, и предназначено для работы в электрических сетях с изолированной, компенсированной нейтралью, нейтралью, заземленной через высокоомный резистор, и в сетях с полной компенсацией основной гармоники тока однофазного замыкания на землю (ОЗЗ).

Известно устройство автоматического обнаружения повреждения кабельных линий в сетях 6-10 кВ типа ЗЗАГ-2, которое содержит блок поиска и контроля, исполнительный орган, включающий в себя усилитель, элемент сравнения и выходное реле, узел автоматического регулирования усиления, а также согласующий трансформатор и фильтр промышленной частоты. Данное устройство не предназначено для сигнализации (защиты от) ОЗЗ.

Наиболее близким к предлагаемому является другое устройство для защиты ОЗЗ электрической сети переменного тока, включающее пороговый орган, последовательно соединенные ограничитель сигнала и ключ, а также усилитель и исполнительный орган.

Недостаток устройства заключается в пониженном быстродействии, недостаточном для получения необходимого количества информации при контроле нескольких присоединений при быстропротекающих процессах (например, переходных), а также в ограниченной области применения только в сетях с изолированной нейтралью и нейтралью, заземленной через высокоомный резистор.

В основу изобретения положена задача создания такого устройства для сигнализации ОЗЗ в электрической сети переменного тока, которое при повышенной надежности обеспечивало бы необходимое быстродействие передачи и преобразования информации, а также повышенную селективность действия.

Поставленная цель достигается тем, что в устройство сигнализации ОЗЗ в электрической сети переменного тока, содержащее пороговый орган, подключаемый к трансформатору напряжения нулевой последовательности (ТННП) сети, последовательно соединенные первые подключаемый к первому трансформатору тока нулевой последовательности (ТТНП) контролируемого присоединения ограничитель сигналов и ключ, последовательно соединенные n-ные подключаемый к n-му ТТНП соответствующего контролируемого присоединения ограничитель сигналов и ключ, а также коммутатор, усилитель и цифровой индикатор, причем каждый из n выходов коммутатора соединен с управляющим входом соответствующего ключа, согласно изобретению введены последовательно соединенные генератор прямоугольных (тактовых) импульсов и микропроцессор (МП), а также (n+1)-й ключ, включенный между входами порогового органа и усилителя, аналого-цифровой преобразователь (АЦП), блок управления (БУ), оперативное запоминающее устройство (ОЗУ), постоянное перепрограммируемое запоминающее устройство (ПЗУ), регистр адреса (РА), контроллер запоминающих устройств (КЗУ), цифровой блок индикации (ЦБИ), шинная и системная магистрали, причем управляющий вход (n+1)-го ключа подсоединен к (n+1)-му выходу коммутатора, вторые выводы всех ключей объединены и подсоединены к входу усилителя, выход которого подключен к первому входу АЦП, первый выход РА через шинную магистраль соединен с первыми входами ПЗУ, ОЗУ и коммутатора, второй вход которого соединен с выходом порогового органа, системная магистраль соединена с первыми выходами АЦП и ПЗУ, с первыми входами РА, КЗУ, ЦБИ, с выходами/входами МП и ОЗУ, первый выход МП "Чтение данных" соединен с первым входом БУ и вторыми входами КЗУ и ОЗУ, второй выход МП "Запись данных" с вторыми входами БУ, ПЗУ и третьим входом КЗУ, третий выход МП "Обмен" с третьим входом БУ, четвертым входом КЗУ и вторым входом РА, четвертый выход МП "Побайтная запись" с пятым входом КЗУ, пятый выход МП "Установка внешних устройств" с вторым входом ЦБИ, второй выход РА подключен к четвертому входу БУ, а третий выход РА к шестому входу КЗУ, первый выход последнего соединен с третьим входом ОЗУ, второй выход с третьим входом ПЗУ, второй вход МП "Ответ" соединен с выходами: первым БУ и третьим КЗУ, второй выход БУ соединен с вторым входом АЦП "Разрешение считывания", третий выход БУ с третьим входом АЦП "Запуск АЦП", четвертый выход БУ с третьим входом ЦБИ, а пятый вход БУ с вторым выходом АЦП "Готовность", выход ЦБИ соединен с входом цифрового индикатора.

Отличительной особенностью изобретения является введение цифровых блоков микропроцессора, запоминающих устройств, регистра адреса и др. что позволило с высокой скоростью фиксировать большое количество информации о процессах в эл. сети при ОЗЗ и существенно повысить селективность определения поврежденного присоединения.

Пороговый орган реагирует на переменное напряжение и может быть выполнен в виде последовательно соединенных выпрямителя, компаратора и RS-триггера.

Ограничители сигнала предназначены для защиты входов устройства от перенапряжений и могут быть выполнены в виде цепочки резистор двухсторонний стабилитрон, причем выходной сигнал снимается со стабилитрона.

МП является основным управляющим и вычислительным блоком в устройстве сигнализации, в качестве МП может быть использована микросхема Н1806ВМ2 со схемой запуска.

В качестве коммутатора напряжения, АЦП, РА и ЦБИ можно применять микросхемы, соответственно 590 КНЗ, К1108ПВ1А, КР533ИР22 (23) и 514ПР1.

КЗУ представляет собой схему выборки сигналов, собранную на микросхеме К588ВГ2 [3, c. 223-225] ОЗУ и ПЗУ можно реализовать на микросхемах КР537РУ8А, КС573РФ2.

ЦБИ представляет собой кодопреобразователь, имеющий вход для сброса информации, соединенный с соответствующим выходом МП.

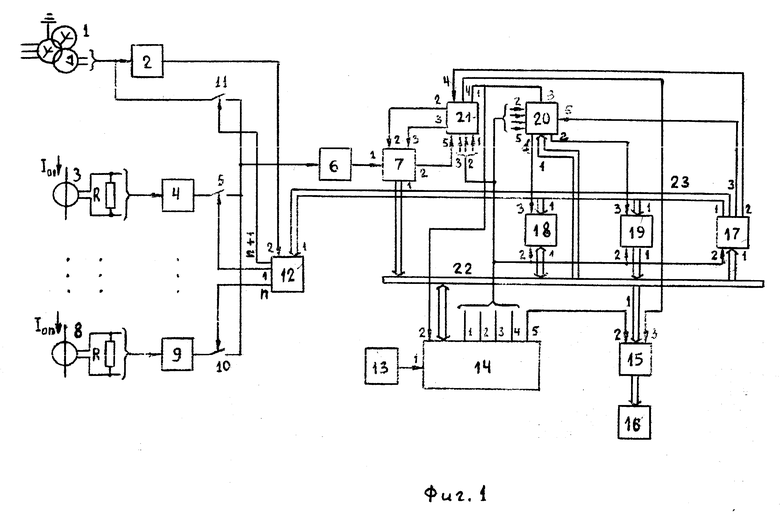

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема контроллера запоминающих устройств (КЗУ); на фиг. 3 - функциональная схема блока управления (БУ).

К трансформатору 1 напряжения нулевой последовательности (ТННП) сети подключен пороговый орган 2 (фиг. 1). К первому трансформатору 3 тока нулевой последовательности (ТТНП) контролируемого присоединения подключены последовательно соединенные первые ограничитель 4 сигнала, ключ 5, усилитель 6 и аналого-цифровой преобразователь (АЦП) 7.

К n-му ТТНП 8 n-го контролируемого присоединения подключены соответственно последовательно соединенные n-ные ограничитель 9 сигнала, ключ 10, второй вывод которого соединен с тем же входом усилителя 6. К вторичным обмоткам ТТНП подключены резисторы R, имеющие малое сопротивление. Вход порогового органа 2 через ключ 11 также соединен с входом усилителя 6. В схеме имеется коммутатор 12, первый, n-ный и (n+1)-й выходы которого соединены с управляющими входами ключей, соответственно, 5, 10 и 11.

Выход порогового органа 2 соединен с (n+2)-м входом коммутатора 12.

В схеме имеются последовательно соединенные генератор 13 прямоугольных (тактовых) импульсов и микропроцессор (МП) 14, а также цифровой блок 15 индикации (ЦБИ), выход которого через шинную (многопроводную) магистраль соединен с входом цифрового индикатора 16. В схеме имеются также регистр адреса (РА) 17, оперативное запоминающее устройство (ОЗУ) 18, постоянное (перепрограммируемое) запоминающее устройство (ПЗУ) 19, контроллер 20 запоминающих устройств (КЗУ), блок 21 управления (БУ) и системная (шинная) магистраль (СМ) 22 для передачи адресов и данных. При этом выход РА 17 по своей шинной магистрали 23 соединен с первыми входами коммутатора 12 напряжения и запоминающих устройств 19 и 18.

Соответствующие входы/выходы МП14 через СМ 22 соединены с первыми выходами АЦП 7, ПЗУ 19, первыми входами РА 17, КЗУ 20, ЦБИ 15, входами/выходами ОЗУ 18. Первый выход РА 17 через шинную магистраль 23 соединен с первыми входами ПЗУ 19, ОЗУ 18 и коммутатора напряжения КН 12. Второй вход последнего подключен к выходу порогового органа 2, а (n+1)-й выход к управляющему входу ключа 11.

Первый выход МП14 "Чтение данных" (ДЧТ) соединен с первым входом БУ 21 и вторыми входами КЗУ 20, ОЗУ 18. Второй выход МП 14 "Запись данных" (ДЗП) соединен с вторым входом БУ 21, ПЗУ 19 и третьим входом КЗУ 20. Третий выход МП 14 "Обмен" (ОБМ) соединен с третьим входом БУ 21, четвертым входом КЗУ 20 и вторым входом РА 17. Четвертый выход МП 14 "Побайтная запись" (ПЗП) соединен с пятым входом КЗУ 20.

Пятый выход МП 14 "Установка внешних устройств" (УВУ) соединен с вторым входом ЦБИ 15. Второй выход РА 17 (например, 5-й цифровой разряд слова) подключен к четвертому входу БУ 21, а третий выход (например, 12-й цифровой разряд слова) к шестому входу КЗУ 20. Первый выход последнего соединен с третьим входом ОЗУ 18, второй выход с третьим входом ПЗУ 19.

Второй вход МП 14 "Ответ" соединен с выходами первым БУ 21 и третьим КЗУ 20. Второй выход БУ 21 соединен с вторым входом АЦП "Разрешение считывания", третий выход с третьим входом АЦП "Запуск АЦП", четвертый выход с третьим входом ЦБИ 15, а пятый вход БУ 21 с вторым выходом АЦП "Готовность". Выход ЦБИ 15 соединен с входом цифрового индикатора 16.

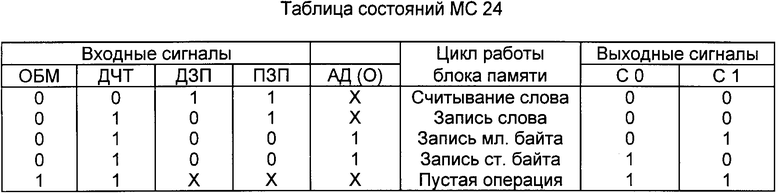

Функциональная схема КЗУ 20 (фиг. 2) содержит микросхему (МС) 24 контроллера запоминающих устройств и четыре логических элемента И 25-28, причем четыре адресных вывода МС 24 подключены к первому входу, выводы ДЧТ, ДЗП, ОБМ и ПЗП подключены соответственно к входам 2-5. К шестому входу подключены первые входы элементов И 25, 26 и 28. Первый вывод МС 24 соединен с вторым входом элемента И 25, а второй ее вывод с вторыми входами элементов И 26 и 27. Выход элемента И 28 подключен к второму входу элемента И 27. 1-й, 2-й и третий выходы КЗУ 20 соединены соответственно с выходами третьим МС 24, выходами элементов И 25 и 26 и выходом элемента И 27.

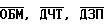

При совпадении кода на входе AD (разряды 0, 13, 14, 15 от системной магистрали) с единицами на входе А входные сигналы  и ПЗП в зависимости от их сочетания (см. таблицу) переключают выходные сигналы МС 24.

и ПЗП в зависимости от их сочетания (см. таблицу) переключают выходные сигналы МС 24.

В таблице Х означает любое значение (0 или 1) логического сигнала. Выход 1 выдает ответ (ОТВ) МП 14 после исполнения команды. Благодаря логическим элементам И 25-28 обеспечивается запись и чтение данных ОЗУ 18 (элементы И 25 и 26) выход 2 КЗУ 20. При этом логический "0" на выходе логического элемента И 25 определяет младший байт, а на выходе логического элемента 26 старший байт данных. На выходе 1 КЗУ 20 выдается сигнал ОТВ МП 14. Сигнал (низкий уровень) на выходе ЗКЗУ 20 обеспечивает чтение данных ПЗУ 19.

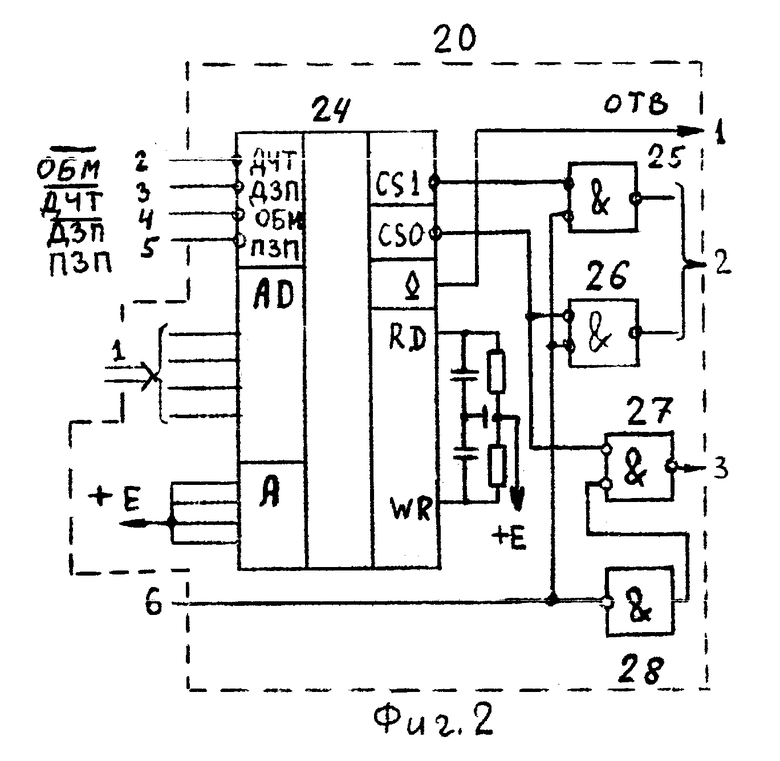

Функциональная схема БУ 21 (фиг. 3) содержит микросхему 2 х 2 И 29 с управляющим входом, D триггер 30 и 2 логических элемента ИЛИ 31, 32, причем к первому входу подключены первые входы первого элемента И микросхемы 29 и элемента ИЛИ 31, выход которого соединен с R-входом D-триггера 30. К второму входу БУ подключен первый вход 2-го элемента И микросхемы 29, к третьему входу вторые входы обоих элементов И микросхемы 29. К четвертому входу БУ подключен управляющий вход (два разряда) микросхемы 29. К пятому входу БУ подключен С-вход D-триггера 30. Первый вывод микросхемы 29 соединен с вторым выходом БУ, второй с четвертым выходом БУ и с первым входом элемента 32, выход которого подключен к первому выходу БУ. Третий выход микросхемы 29 подключен к третьему выходу БУ, а выход D-триггера к второму входу элемента ИЛИ 32.

Микросхемы (КР15ЗЗ ИДЧ) представляют собой сдвоенный дешифратор/демультиплексор. Схемы И его являются разрешающими входами, а АО и А1 управляющими. На АО поступает сигнал 5 разряда РА 17, а на А1 сигнал совпадения сигналов 9, 13, 14, 15 разрядов РА 17. Состояние сигналов АО и А1 указано на выходах микросхемы 29 (фиг. 3). С первого выхода БУ 21 поступает сигнал ответ (ОТВ) МП 14 об исполнении команды. Со второго выхода поступает сигнал "Запуск АЦП", с третьего "Разрешение считывания" АЦП.

Сигнал с четвертого выхода обеспечивает запись кода в буферные регистры ЦБИ 15, благодаря чему на индикаторе 16 будут высвечиваться соответствующие цифры номер контролируемого присоединения до поступления нового сигнала с выхода 4 БУ 21.

Работа устройства.

В нормальном режиме сети напряжение Uo на входе порогового органа 2 мало и на выходе его логический сигнал равен нулю, коммутатор 2 заблокирован. Ключи 11, 5 и 10 разомкнуты. На индикаторе 16 информация отсутствует.

При ОЗЗ в сети напряжение нейтрали Uo превышает уставку 0,3Uф порогового органа 2, на выходе последнего появляется логическая единица и разрешает работу коммутатора 12. МП работает в соответствии с программой, записанной в ПЗУ 19. Сначала он через РА 17 воздействует на КН 12, обеспечивая замыкание ключа 11. Затем через БУ 21 подает на управляющие входы АЦП 7 сигналы "Разрешение считывать" и "Запуск". АЦП 7 формирует сигнал "Готовность" на БУ 21, который выдает сигнал на вход МП 14 "Ответ". Последний выдает команды через РА 17, КЗУ 20 и непосредственно на ОЗУ 18 и информация с выхода АЦП 7 по указанному адресу через СМ 22 передается и записывается в ОЗУ 18. Далее МП 14 через РА 17 обеспечивает размыкание ключа 11 и замыкание ключа 5, описанный процесс повторяется с изменением адресов ячеек ОЗУ 18, куда записывается информация с АЦП 7 и т.д. МП 14 обеспечивает запись в ячейки ОЗУ 18 информации об уровнях входных сигналов, начиная с ключа 11, затем 5, 10 и далее циклически в течение одного периода Т промышленной частоты (20 мс). Например, при m 10 выходных сигналах за 20 мс будет записано количество точек  для каждого входного сигнала, где Δt время преобразования АЦП 7 и записи в ОЗУ 18 принято равным 0,01 мс.

для каждого входного сигнала, где Δt время преобразования АЦП 7 и записи в ОЗУ 18 принято равным 0,01 мс.

Далее МП 14 в соответствии с программой, записанной в ПЗУ 19, начинает обрабатывать запомненную в ОЗУ 18 информацию.

Например, определяются разности соседних чисел (точек) каждого из присоединений, всем полученным разностям присваиваются положительные знаки. Полученные значения суммируются для каждого из токовых входов (5-10), эти суммы сравниваются. Поврежденное присоединение находится по наибольшей сумме и номер этого присоединения загорается на индикаторе 16. Первый вход (ключ 11) нужен при обработке переходных составляющих напряжения Uo и токов присоединений Ioi для определения поврежденного присоединения.

Устройство обладает высокими быстродействием и селективностью, время съема информации 20 мс и обработки ее 100 мс.

Устройство для сигнализации однофазного замыкания на землю в электрической сети переменного тока согласно изобретению может успешно использоваться в электрических сетях напряжением 6-35 кВ промышленных предприятий городов и сельского хозяйства. Эти сети могут иметь любой применяемый режим нейтрали, а также содержать системы компенсации основной гармоники тока ОЗЗ.

Применение устройства позволяет автоматически определять поврежденное присоединение (с ОЗЗ) на подстанции или электростанции и исключает необходимость кратковременного отключения присоединений для этой цели.

Испытания предложенного устройства в сети 6 кВ показали его эффективную работу и возможность применения в эл. сетях напряжением 6-35 кВ с любым режимом нейтрали, в том числе в сетях с компенсацией основной гармоники тока ОЗЗ.

Использование устройства обеспечивает как экономический, так и социальный положительные эффекты.

Использование: для защиты электрических сетей с изолированной, компенсированной нейтралью, с нейтралью, заземленной через высокоомный резистор, и сетей с полной компенсацией основной гармоники тока однофазного замыкания на землю (ОЗЗ). Сущность: в устройство введены последовательно соединенные генератор тактовых импульсов и микропроцессор, аналого-цифровой преобразователь, оперативное и постоянное запоминающие устройства, регистр адреса, контроллер запоминающих устройств и цифровой блок информации, соединенные с микропроцессором через системную магистраль, соединяющую выход регистра адреса с входами запоминающих устройств и коммутатора, соединенного через соответствующие ключи с пороговым элементом и ограничителями сигнала, а также блок управления со связями. Устройство обладает высоким быстродействием и фиксирует большой объем информации о процессах в эл. сети при ОЗЗ, за счет чего повышается достоверность определения поврежденного присоединения (селективность действия) в переходном и установившихся режимах ОЗЗ при повышенной надежности устройства. 3 ил., 1 табл.

Устройство для сигнализации однофазного замыкания на землю в электрической сети переменного тока, содержащее пороговый орган, подключаемый к трансформатору напряжения нулевой последовательности сети (ТННП), последовательно соединенные первые подключаемые к первому ТТНП контролируемого присоединения ограничитель сигналов и ключ, последовательно соединенные n-е подключаемые к n-му ТТНП соответствующего контролируемого присоединения ограничитель сигналов и ключ, а также коммутатор напряжения, усилитель и цифровой индикатор, причем каждый из n выходов коммутатора напряжения соединен с управляющим входом соответствующего ключа, отличающееся тем, что в него введены последовательно соединенные генератор прямоугольных (тактовых) импульсов и микропроцессор (МП), а также (n+1)-й ключ, включенный между входами порогового органа и усилителя, аналого-цифровой преобразователь (АЦП), блок управления (БУ), включающий микросхему 2х2И (МС 2х2И) с управляющим входом, D-триггер, логические элементы ИЛИ и НЕ, оперативное запоминающее устройство (ОЗУ) и постоянное перепрограммируемое запоминающее устройство (ППЗУ), регистр адреса (РА), контроллер запоминающих устройств (КЗУ), включающий микросхему выборки сигналов (МВС), три логических элемента И и логический элемент НЕ, цифровой блок индикации (ЦБИ), шинную и системную магистрали, причем управляющий вход (n + 1)-го ключа подсоединен к (n + 1)-му выходу коммутатора напряжения, вторые выводы всех ключей объединены и подсоединены к входу усилителя, выход которого подключен к первому входу АЦП, первый вход РА через шинную магистраль соединен с первыми входами ППЗУ, ОЗУ и коммутатора напряжения, второй вход которого соединен с выходом порогового органа, системная магистраль соединена с первыми выходами АЦП и ППЗУ, первыми входами РА, ЦБИ, четырьмя адресными выводами МВС КЗУ, с выходами/входами МП и ОЗУ, первый выход МП "Чтение данных" (ДЧТ) соединен с первым входом первого элемента И МС 2х2И и входом элемента НЕ БУ, вторым входом ОЗУ, выводом ОБМ МВС КЗУ, второй выход МП "Запись данных" (ДЗП) со вторым входом ПЗУ, первым входом второго элемента И МС 2х2И БУ и выводом ДЧТ МВС КЗУ, третий выход МП "Обмен" (ОБМ) со вторыми входами обоих элементов и МС 2х2И БУ, выводом ДЗП МВС КЗУ и вторым входом РА, четвертый выход МП "Побайтная запись" (ПЗП) с выводом ПЗП МВС КЗУ, пятый выход МП "Установка внешних устройств" с вторым входом ЦБИ, второй выход РА подключен к управляющему входу (два разряда) МС 2х2И БУ, а третий выход РА к вторым входам первого и второго логических элементов И и входу логического элемента НЕ КЗУ, выходы первого и второго логических элементов И КЗУ соединены с третьим входом ОЗУ, выход третьего логического элемента И КЗУ соединен с третьим входом ПЗУ, второй вход МП "Ответ" соединен с выходом логического элемента ИЛИ БУ и третьим выходом МВС КЗУ, первый вывод МС 2х2И БУ соединен с вторым входом АЦП "Запуск АЦП", третий вывод МС 2х2И БУ с третьим входом АЦП "Разрешение считывания", второй вывод МС 2х2И БУ с третьим входом ЦБИ, а С-вывод D-триггера БУ с вторым выходом АЦП "Готовность", выход ЦБИ соединен с входом цифрового индикатора, первый вывод МВС КЗУ соединен с первым входом первого логического элемента И КЗУ, а второй вывод МВС с первыми входами второго и третьего логических элементов И КЗУ, выход логического элемента НЕ которого подключен к второму входу третьего логического элемента И КЗУ, выход логического элемента НЕ БУ соединен с R-входом D-триггера, второй вывод МС 2х2И БУ соединен с первым входом логического элемента ИЛИ БУ, второй вход которого подключен к выходу D -триггера БУ.

| SU, авторское свидетельство, 1042123, кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1998-01-10—Публикация

1995-06-14—Подача