Изобретение относится к автоматике, вычислительной технике и может быть использовано в системах управления, а также при автоматической обработке текстовой и языковой информации.

Из известных устройств наиболее близким к изобретению является функциональный преобразователь с многозначным кодированием (А.с. N 1510077 (СССР), МКВ H 03 K 19/08, опубл. в БИ 23.09.89 г., N 35), состоящий из аналого-цифрового и цифроаналогового преобразователей и дешифратора, который включает двухвходовой элемент И, а также счетчика, первые выходы которого соединены с одноименными первыми входами дешифратора, причем вход и выход аналого-цифрового преобразователя являются информационным входом преобразователя и соединены с одноименным вторым входом дешифратора, выходы дешифратора сгруппированы с одноименными вторыми выходами счетчика и подключены к соответствующим входам цифроаналогового преобразователя, выход которого является выходом преобразователя, тактовый и установочный входы счетчика являются соответственно тактовыми и установочными входами преобразователя.

Известный функциональный преобразователь с многозначным кодированием характеризуется неоднородностью схемных решений дешифратора и счетчика в связи с использованием вычислительных способов действия и, как следствие, низкой технологичностью в процессе микроэлектронной реализации, низкими функциональными возможностями, так как осуществляется только трехзначное кодирование, а также низким быстродействием в силу последовательного характера работы счетчика при настройке функционального преобразователя на осуществление необходимого преобразования.

В основу изобретения поставлена задача создания такого функционального преобразователя с многозначным кодированием, в котором за счет введения коммутатора и блока управления, однотипной, одноярусной и пространственной реализации их и дешифратора обеспечивается однородность исполнения всех узлов преобразователя, что ведет к повышению технологичности устройства в процессе микроэлектронной реализации и возрастания быстродействия, а также за счет повышения до десяти реализованной значности, обеспечивается расширение его функциональных возможностей.

Поставленная задача решается тем, что в функциональный преобразователь с многозначным кодированием, который состоит из аналого-цифрового преобразователя, вход которого является информационным входом функционального преобразователя и цифро-аналогового преобразователя, выход которого является информационным выходом функционального преобразователя, а также дешифратора, который включает в себя двухвходовой элемент И, в соответствии с изобретением дополнительно введены коммутатор, состоящий из десяти блоков коммутации, каждый из которых реализован на десяти двухвходовых элементах И, а также блок управления, включающий восемь двухвходовых элементов И, в дешифратор дополнительно введено семь двухвходовых элементов И, причем выходы аналого-цифрового преобразователя подключены к соответствующим восемнадцати информационным входам дешифратора, при этом первый вход дешифратора, который является первым входом первого элемента И, подключен к первому прямому выходу аналого-цифрового преобразователя, первый инверсный выход аналого-цифрового преобразователя транзитом подключен к первому выходу дешифратора, второй вход первого элемента И подключен к второму инверсному выходу аналого-цифрового преобразователя, выход первого элемента И подключен к второму выходу дешифратора, второй вход дешифратора, который является первым входом второго элемента И, подключен к второму прямому выходу аналого-цифрового преобразователя, второй вход второго элемента И подключен к третьему инверсному выходу аналого-цифрового преобразователя, выход второго элемента И подключен к третьему выходу дешифратора, третий вход дешифратора, который является первым входом третьего элемента И, подключен к третьему прямому выходу аналого-цифрового преобразователя, второй вход третьего элемента И подключен к четвертому инверсному выходу аналого-цифрового преобразователя, выход третьего элемента И подключен к четвертому выходу дешифратора, четвертый вход дешифратора, который является первым входом четвертого элемента И, подключен к четвертому прямому выходу аналого-цифрового преобразователя, второй вход четвертого элемента И подключен к пятому инверсному выходу аналого-цифрового преобразователя, выход четвертого элемента И подключен к пятому выходу дешифратора, пятый вход дешифратора, который является первым входом пятого элемента И, подключен к пятому прямому выходу аналого-цифрового преобразователя, второй вход пятого элемента И подключен к шестому инверсному выходу аналого-цифрового преобразователя, выход пятого элемента И подключен к шестому выходу дешифратора, шестой вход дешифратора, который является первым входом шестого элемента И, подключен к шестому прямому выходу аналого-цифрового преобразователя, второй вход шестого элемента И подключен к седьмому инверсному выходу аналого-цифрового преобразователя, выход шестого элемента И подключен к седьмому выходу дешифратора, седьмой вход дешифратора, который является первым входом седьмого элемента И, подключен к седьмому прямому выходу аналого-цифрового преобразователя, второй вход седьмого элемента И подключен к восьмому инверсному выходу аналого-цифрового преобразователя, выход седьмого элемента И подключен к восьмому выходу дешифратора, восьмой вход дешифратора, который является первым входом восьмого элемента И, подключен к восьмому прямому выходу аналого-цифрового преобразователя, второй вход восьмого элемента И подключен к девятому инверсному выходу аналого-цифрового преобразователя, выход восьмого элемента И подключен к девятому выходу дешифратора, девятый прямой выход аналого-цифрового преобразователя транзитом подключен к десятому выходу дешифратора, первые входы элементов И в каждом блоке коммутации соединены вместе и подключены к соответствующим выходам дешифратора, вторые входы первого, одиннадцатого - девяносто первого элементов И коммутатора соединены вместе и подключены к первому выходу блока управления, вторые входы второго, двенадцатого - девяносто второго элементов И коммутатора соединены вместе и подключены к второму выходу блока управления, вторые входы третьего, тринадцатого - девяносто третьего элементов И коммутатора также соединены вместе и подключены к третьему выходу блока управления, вторые входы четвертого, четырнадцатого - девяносто четвертого элементов И коммутатора соединены вместе и подключены к четвертому выходу блока управления, вторые входы пятого, пятнадцатого - девяносто пятого элементов И коммутатора соединены вместе и подключены к пятому выходу блока управления, вторые входы шестого, шестнадцатого - девяносто шестого элементов И коммутатора соединены вместе и подключены к шестому выходу блока управления, вторые входы седьмого, семнадцатого - девяносто седьмого элементов И коммутатора соединены вместе и подключены к седьмому выходу блока управления, вторые входы восьмого, восемнадцатого - девяносто восьмого элементов И коммутатора тоже соединены вместе и подключены к восьмому выходу блока управления, вторые входы девятого, девятнадцатого - девяносто девятого элементов И коммутатора соединены вместе и подключены к девятому выходу блока управления, вторые входы десятого, двадцатого - сотого элементов И коммутатора соединены вместе и подключены к выходу блока управления, выходы первого, одиннадцатого - девяносто первого элементов И коммутатора соединены вместе и образуют первый выход коммутатора, выходы второго, двенадцатого - девяносто второго элементов И коммутатора соединены вместе и образуют второй выход коммутатора, выходы третьего, тринадцатого - девяносто третьего элементов И коммутатора также соединены вместе и образуют третий выход коммутатора, выходы четвертого, четырнадцатого - девяносто четвертого элементов И коммутатора соединены вместе и образуют четвертый выход коммутатора, выходы пятого, пятнадцатого - девяносто пятого элементов И коммутатора соединены вместе и образуют пятый выход коммутатора, выходы шестого, шестнадцатого - девяносто шестого элементов И коммутатора соединены вместе и образуют шестой выход коммутатора, выходы седьмого, семнадцатого - девяносто седьмого элементов И коммутатора соединены вместе и образуют седьмой выход коммутатора, выходы восьмого, восемнадцатого - девяносто восьмого элементов И коммутатора тоже соединены вместе и образуют восьмой выход коммутатора, выходы девятого, девятнадцатого - девяносто девятого элементов И коммутатора соединены вместе и образуют девятый выход коммутатора, выходы десятого, двадцатого - сотого элементов И коммутатора соединены вместе и образуют десятый выход коммутатора, выходы коммутатора подключены к соответствующим входам цифроаналогового преобразователя, внешние входы управления функционального преобразователя образуют входы блока управления, причем первый инверсный вход управления транзитом подключен к первому выходу блока управления, первый вход первого элемента И блока управления подключен к первому прямому входу управления функционального преобразователя, а второй вход первого элемента И подключен к инверсному второму входу управления, выход первого элемента И является вторым выходом блока управления, первый вход второго элемента И блока управления подключен к второму прямому входу управления функционального преобразователя, а второй вход второго элемента И подключен к инверсному третьему входу управления, выход второго элемента И является третьим выходом блока управления, первый вход третьего элемента И блока управления подключен к третьему прямому входу управления функционального преобразователя, а второй вход третьего элемента И подключен к инверсному четвертому входу управления, выход третьего элемента И является четвертым выходом блока управления, первый вход четвертого элемента И блока управления подключен к четвертому прямому входу управления функционального преобразователя, а второй вход четвертого элемента И подключен к пятому инверсному входу управления, выход четвертого элемента И является пятым выходом блока управления, первый вход пятого элемента И блока управления подключен к пятому прямому входу управления функционального преобразователя, а второй вход пятого элемента И подключен к инверсному шестому входу управления, выход пятого элемента И является шестым выходом блока управления, первый вход шестого элемента И блока управления подключен к шестому прямому входу управления функционального преобразователя, а второй вход шестого элемента И подключен к инверсному седьмому входу управления, выход шестого элемента И является седьмым выходом блока управления, первый вход седьмого элемента И блока управления подключен к седьмому прямому входу управления функционального преобразователя, а второй вход седьмого элемента И подключен к инверсному восьмому входу управления, выход седьмого элемента И является восьмым выходом блока управления, первый вход восьмого элемента И блока управления подключен к восьмому прямому входу управления функционального преобразователя, а второй вход восьмого элемента И подключен к инверсному девятому входу управления, выход восьмого элемента И является девятым выходом блока управления, девятый прямой вход управления транзитом соединен с десятым выходом блока управления.

Введение в функциональный преобразователь с многозначным кодированием коммутатора, который состоит из десяти блоков коммутации, каждый из которых реализован на десяти двухвходовых элементах И, а также дешифратора и блока управления, которые включают по восемь двухвходовых элементов И и образуют в пространстве структуру параллельного типа с пространственным k-значным кодированием, реализованным в виде возбужденных двоичных состояний пространственных полюсов, позволило обеспечить однотипность и однородность внутренней структуры функционального преобразователя с многозначным кодированием, упростить шинную коммутацию, а также повысить быстродействие за счет минимальной задержки во всех звеньях преобразователя. Таким образом, в структуре функционального преобразователя с многозначным кодированием используются логические, а не вычислительные методы промежуточных преобразований с применением симбиоза двух - и 10-значного кодирования, что приводит к отсутствию учета межразрядных связей и набегания разрядной сетки и, как следствие, к уменьшению задержек во время преобразований, упрощению и параллелизму структуры. Наращивание значности структурного алфавита (числа параллельных каскадов ЦАП и АЦП) с 3 до 10 позволяет расширить функциональные возможности относительно реализации множества логических функций одной переменной в 1010/33 раз.

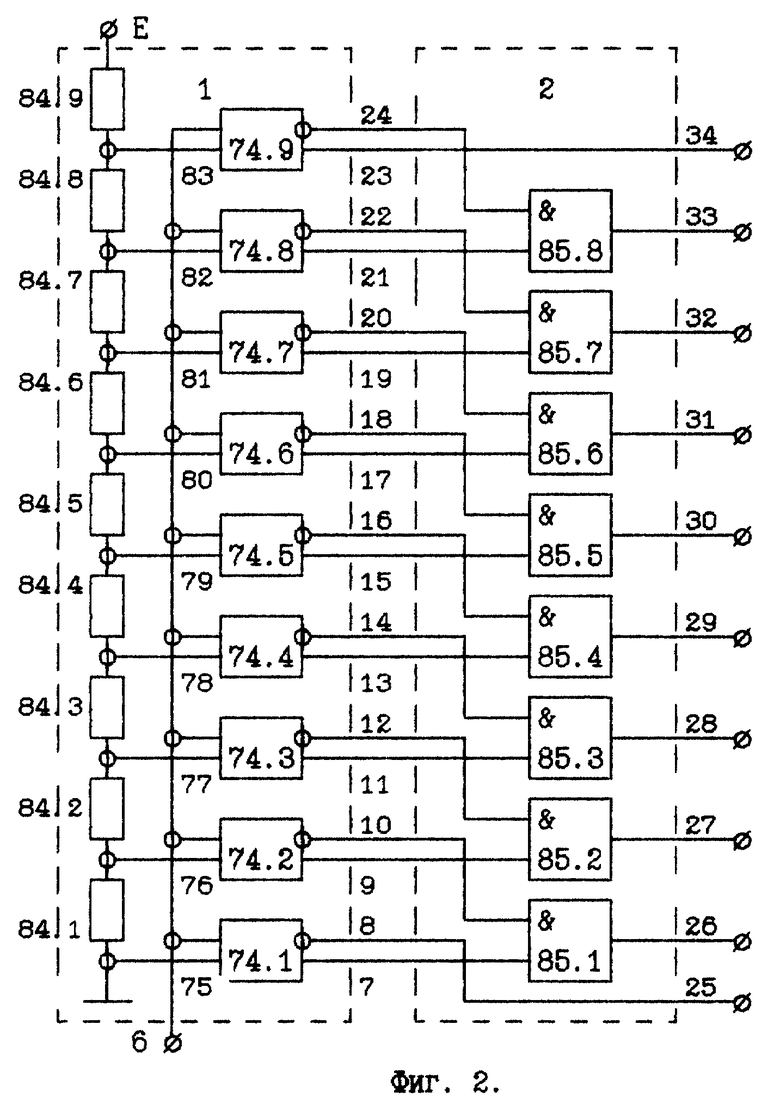

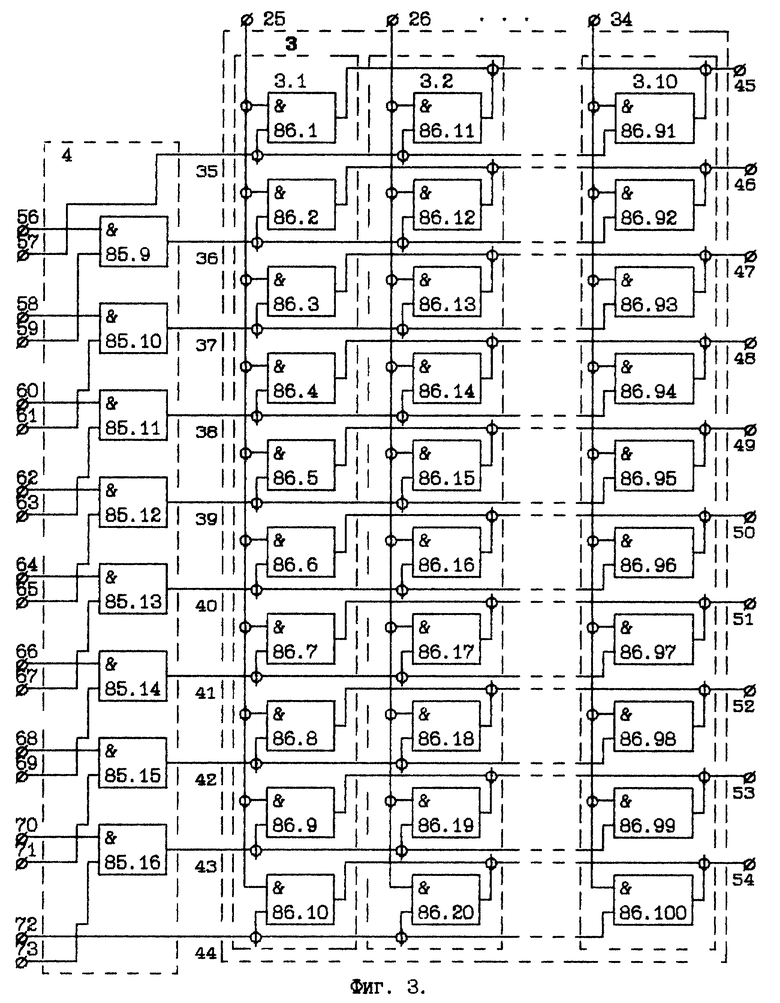

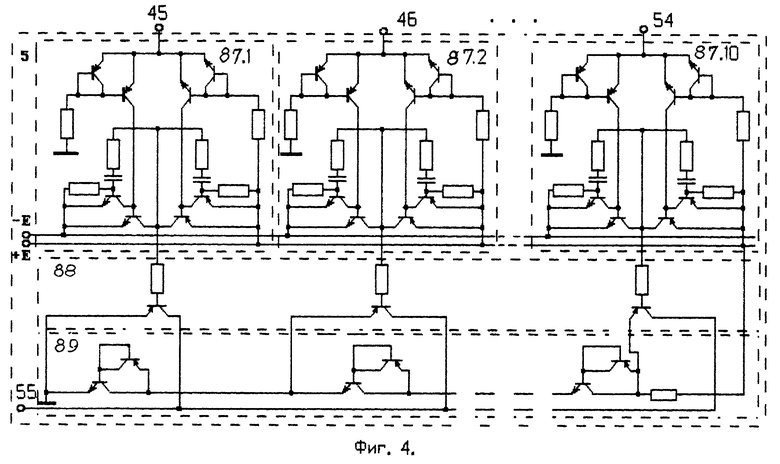

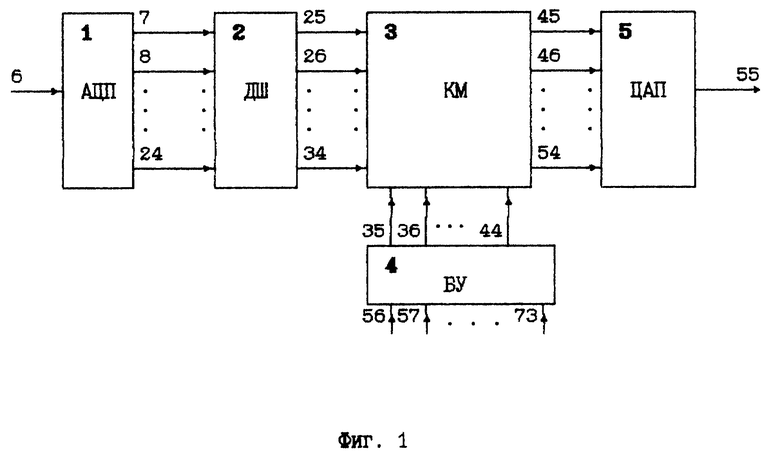

На фиг. 1 изображена структурная схема функционального преобразователя с многозначным кодированием; на фиг. 2 - функциональная схема аналого-цифрового преобразователя и дешифратора; на фиг. 3 - функциональная схема коммутатора и блока управления; фиг. 4 - принципиальная электрическая схема цифроаналогового преобразователя.

Функциональный преобразователь с многозначным кодированием (фиг. 1) содержит аналого-цифровой преобразователь (АЦП) 1, дешифратор (ДШ) 2, коммутатор (КМ) 3, блок 4 управления (БУ), цифроаналоговый преобразователь (ЦАП) 5, причем вход 6 АЦП 1 является информационным входом преобразователя, выходы 7-24 АЦП 1 подключены к соответствующим восемнадцати информационным входам дешифратора 2, выходы 25 - 34 которого подключены к соответствующим первым десяти входам коммутатора 3, вторые входы 35 - 44 коммутатора 3 соединены с десятью соответствующими выходами блока 4 управления, выходы 45 - 54 коммутатора 3 подключены к соответствующим десяти входам ЦАП 5, а выход 55 ЦАП 5 является выходом функционального преобразователя в целом, внешние входы 56 - 73 управления функционального преобразователя образуют входы блока 4 управления.

АЦП 1 (фиг. 2) содержит вход 6, который является одновременно входом устройства и объединенным информационным входом девяти компараторов 74.1 - 74.9, входы 75 - 83 опорных сигналов компараторов 74.1 - 74.9 подключены к соответствующим точкам делителя напряжения, состоящим из резисторов 84.1 - 84.9, а также выходы 7 - 24.

Дешифратор 2 (фиг. 2) содержит восемнадцать информационных входов 7 - 24, десять выходов 25 - 34 и включает в своем составе восемь двухвходовых элементов 85.1 - 85.8 И, причем первый вход ДШ 2, который является первым входом первого элемента 85.1 И, подключен к первому прямому выходу 7 АЦП 1, первый инверсный выход 8 АЦП 1 транзитом подключен к первому выходу 25 ДШ 2, второй вход первого элемента 85.1 И подключен к второму инверсному выходу 10 АЦП 1, выход первого элемента 85.1 И подключен к второму выходу 26 ДШ 2, второй вход ДШ 2, который является первым входом второго элемента 85.2 И, подключен к второму прямому выходу 9 АЦП 1, второй вход элемента 85.2 И подключен к третьему инверсному выходу 12 АЦП 1, выход элемента 85.2 И подключен к третьему выходу 27 ДШ 2, третий вход ДШ 2, который является первым входом третьего элемента 85.3 И, подключен к третьему прямому выходу 11 АЦП 1, второй вход элемента 85.3 И подключен к четвертому инверсному выходу 14 АЦП 1, выход элемента 85.3 И подключен к четвертому выходу 28 ДШ 2, четвертый вход ДШ 2, который является первым входом элемента 85.4 И, подключен к четвертому прямому выходу 13 АЦП 1, второй вход четвертого элемента 85.4 И подключен к пятому инверсному выходу 16 АЦП 1, выход элемента 85.4 И подключен к пятому выходу 29 ДШ 2, пятый вход ДШ 2, который является первым входом элемента 85.5 И, подключен к пятому прямому выходу 15 АЦП 1, второй вход пятого элемента 85.5 И подключен к шестому инверсному выходу 18 АЦП 1, выход элемента 85.5 И подключен к шестому выходу 30 ДШ 2, шестой вход ДШ 2, который является первым входом шестого элемента 85.6 И, подключен к шестому прямому выходу 17 АЦП 1, второй вход элемента 85.6 И подключен к седьмому инверсному выходу 20 АЦП 1, выход элемента 85.6 И подключен к седьмому выходу 31 ДШ 2, седьмой вход ДШ 2, который является первым входом седьмого элемента 85.7 И, подключен к седьмому прямому выходу 19 АЦП 1, второй вход седьмого элемента 85.7 И подключен к восьмому инверсному выходу 22 АЦП 1, выход элемента 85.7 И подключен к восьмому выходу 32 ДШ 2, восьмой вход ДШ 2, который является первым входом восьмого элемента 85.8 И, подключен к восьмому прямому выходу 21 АЦП 1, второй вход восьмого элемента 85.8 И подключен к девятому инверсному выходу 24 АЦП 1, выход элемента 85.8 И подключен к девятому выходу 33 ДШ 2, девятый прямой выход 23 АЦП 1 транзитом подключен к десятому выходу 34 ДШ 2.

Коммутатор 3 (фиг. 3) содержит сто двухвходовых элементов 86.1 - 86.100 И, которые образуют десять блоков 3.1 - 3.10 коммутации по десять двухвходовых элементов И в каждом, причем первые входы элементов 86.t И (t = 1 - 100) в каждом блоке 3.k (k = 1 - 10) коммутации соединены вместе и подключены к соответствующим выходам 25 - 34 ДШ 2, вторые входы первого 86.1, одиннадцатого 86.11 - девяносто первого 86.91 элементов И КМ 3 соединены вместе и подключены к первому выходу 35 БУ 4, вторые входы второго 86.2, двенадцатого 86.12 - девяносто второго 86.92 элементов И КМ 3 соединены вместе и подключены к второму выходу 36 БУ 4, вторые входы третьего 86.3, тринадцатого 86.13 - девяносто третьего 86.93 элементов И КМ 3 тоже соединены вместе и подключены к третьему выходу 37 БУ 4, вторые входы четвертого 86.4, четырнадцатого 86.14 - девяносто четвертого 86.94 элементов И КМ 3 соединены вместе и подключены к четвертому выходу 38 БУ 4, вторые входы пятого 86.5, пятнадцатого 86.18 - девяносто пятого элементов 86.95 И КМ 3 соединены вместе и подключены к пятому выходцу 39 БУ 4, вторые входы шестого 86.6, шестнадцатого 86.16 - девяносто шестого элементов 86.96 И КМ 3 соединены вместе и подключены к выходу 40 БУ 4, вторые входы седьмого 86.7 семнадцатого 86.17 - девяносто седьмого 86.97 элементов И КМ 3 соединены вместе и подключены к седьмому выходу 41 БУ 4, вторые входы восьмого 86.8, восемнадцатого 86.18 - девяносто восьмого 86.98 элементов И КМ 3 тоже соединены вместе и подключены к восьмому выходу 42 БУ 4, вторые входы девятого 86.9, девятнадцатого 86.19 - девяносто девятого 86.99 элементов И КМ 3 соединены вместе и подключены к девятому выходу 43 БУ 4, вторые входы десятого 86.10, двадцатого 86.20 - сотого 86.100 элементов И КМ 3 соединены вместе и подключены к десятому выходу 44 БУ 4, выходы первого 86.1, одиннадцатого 86.11 - девяносто первого 86.91 элементов И КМ 3 соединены вместе и образуют первый выход 45 КМ 3, выходы второго 86.2, двенадцатого 86.12 - девяносто второго 86.92 элементов И КМ 3 соединены вместе и образуют второй вход 46 КМ 3, выходы третьего 86.3, тринадцатого 86.13 - девяносто третьего 86.93 элементов И КМ 3 также объединены вместе и образуют третий выход 47 КМ 3, выходы четвертого 86.4, четырнадцатого 86.14 - девяносто четвертого 86.94 элементов И КМ 3 соединены вместе и образуют четвертый выход 48 КМ 3, выходы пятого 86.5, пятнадцатого 86.15 - девяносто пятого 86.95 элементов И КМ 3 соединены вместе и образуют пятый выход 49 КМ 3, выходы шестого 86.6, шестнадцатого 86.16 - девяносто шестого 86.96 элементов И КМ 3 соединены вместе и образуют шестой выход 50 КМ 3, выходы седьмого 86.7, семнадцатого 86.17 - девяносто седьмого 86.97 элементов И КМ 3 соединены вместе и образуют седьмой выход 51 КМ 3, выходы восьмого 86.8, восемнадцатого 86.18 - девяносто восьмого 86.98 элементов И КМ 3 тоже соединены вместе и образуют восьмой выход 52 КМ 3, выходы девятого 86.9, девятнадцатого 86.19 - девяносто девятого 86.99 элементов И КМ 3 соединены вместе и образуют девятый выход 53 КМ 3, выходы десятого 86.10, двадцатого 86.20 - сотого 86.100 элементов И КМ 3 соединены вместе и образуют десятый выход 54 КМ 3.

БУ 4 (фиг. 3), по аналогии с ДШ 2, содержит восемнадцать входов 56 - 73, которые являются внешними входами управления функционального преобразователя, десять выходов 35 - 44 и восемь двухвходовых элементов 85.9 - 85.16 И, причем первый инверсный вход 57 управления подключен транзитом к первому выходу 35 БУ 4, первый вход первого элемента 85.9 и БУ 4 подключен к первому прямому входу 56 управления функционального преобразователя, а второй вход первого элемента 85.9 И подключен к второму инверсному входу 59 управления, выход первого элемента 85.9 И подключен к второму выходу 36 БУ 4, первый вход второго элемента 85.10 И БУ 4 подключен к второму прямому входу 58 управления функционального преобразователя, а второй вход второго элемента 85.10 И БУ 4 подключен к третьему инверсному входу 61 управления, выход второго элемента 85.10 И подключен к третьему выходу 37 БУ 4, первый вход третьего элемента 85.11 И БУ 4 подключен к третьему прямому входу 60, а второй вход третьего элемента 85.11 И БУ 4 подключен к четвертому инверсному входу 63 управления, выход третьего элемента 85.11 И подключен к четвертому выходу 38 БУ 4, четвертый вход БУ 4, который является первым входом четвертого элемента 85.12 И БУ 4, подключен к четвертому прямому входу 62 управления функционального преобразователя, а второй вход четвертого элемента 85.12 И подключен к пятому инверсному входу 65 управления, выход четвертого элемента 85.12 И подключен к пятому выходу 39 БУ 4, пятый вход БУ 4, который является первым входом пятого элемента 85.13 И БУ 4, подключен к пятому прямому входу 66 управления, второй вход пятого элемента 85.13 И подключен к шестому инверсному входу 67, выход элемента И подключен к шестому выходу 40 БУ 4, шестой вход БУ 4, который является первым входом шестого элемента 85.14 И, подключен к шестому прямому входу 66 управления, второй вход шестого элемента 85.14 И подключен к седьмому инверсному входу 69, выход элемента 85.14 И подключен к седьмому выходу 41 БУ 4, седьмой вход БУ 4, который является первым входом седьмого элемента 85.15 И, подключен к седьмому прямому входу 68 управления, второй вход седьмого элемента 85.15 И подключен к восьмому инверсному выходу 71, выход элемента 85.15 И подключен к восьмому выходу 42 БУ 4, восьмой вход БУ 4, который является первым входом восьмого элемента 85.16 И, подключен к восьмому прямому входу 70 управления, второй вход восьмого элемента 85.16 И подключен к девятому инверсному входу 71, выход элемента 85.16 И подключен к девятому выходу 43 БУ 4, девятый прямой вход 72 транзитом подключен к десятому выходу 44 БУ 4.

ЦАП 5 (фиг. 4) содержит десять схем управления 87.1 - 87.10, линейку 88 транзисторных биполярных колючей и десятизвенный транзисторный делитель 89 напряжения, причем входы схем 87.1 - 87.10 управления подключены к выходам 45 - 54 КМ 3, а выходы 55 ЦАП 5 является выходом преобразователя.

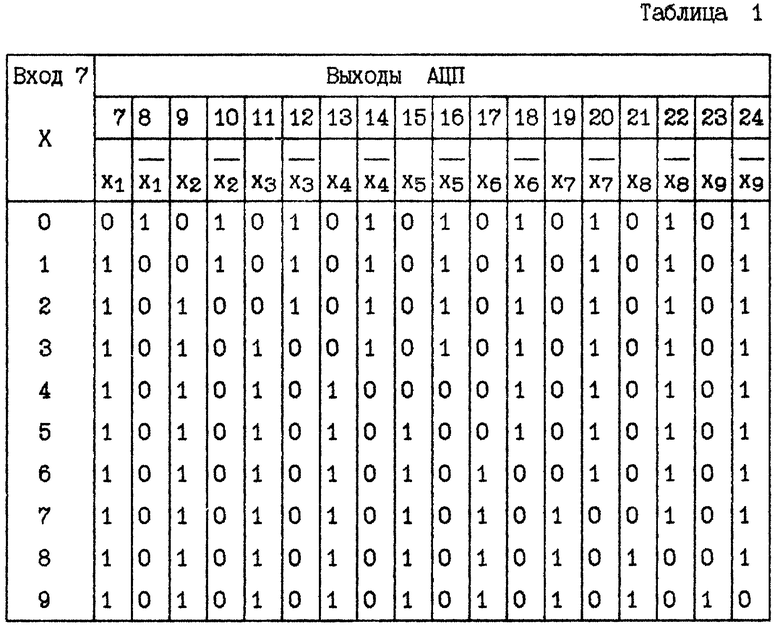

В исходном состоянии на вход 6 ЦАП 1 (див. фиг. 1) поступает нулевой начальный сигнал. При этом на выходах 7 - 24 АЦП 1 обеспечиваются следующие сигналы: <01 01 01 01 01>. При поступлении на вход 6 сигнала логической "1" на выходах 7 - 24 имеем <10 01 01 01 01>, а логической "2" - <10 10 01 01 01>,..., логической "9"- <10 10 10 10 10 10 10 10 10>, то есть на соответствующие входы ДШ 2 поступают (табл. 1) парафазные сигналы от компараторов 74.1 - 74.9 (см. фиг. 2) АЦП 1.

Теория и практика искусственного интеллекта (Шабанов-Кушнаренко Ю.П. Теория интеллекта. Математические средства. - Х.: Выща шк. Изд-во при Харьк. ун-те, 184. - 144 с.) использует понятие элемента распознавания, который при подаче на его вход букви σ вырабатывает на выходе сигналы "1". При поступлении любой другой буквы элемент распознавания вырабатывает сигнал "0", что свидетельствует о несовпадении буквы, которая поступила с требуемой буквой σ. Таким образом, здесь мы используем присвоение каждому проводнику (каждому выходу АЦП), через который поступает двузначный сигнал ("0" или "1"), определенное распознавание xσ, где σ - некоторое значение k-значного алфавита σ ∈ {0, 1, 2,...,k-1} x - k-значная переменная. Двузначные сигналы, которые поступают таким проводником (выходом), интерпретируются теперь как значения распознавания. В случае использования в качестве элемента распознавания АЦП (линейка компараторов с общим опорным делителем напряжения), реализуем элемент распознавания k-значных сигналов с одним входом и k выходами. При этом необходимо решить задачу однозначного распознавания, когда амплитуда входного k-значного сигнала превышает опорные уровни напряжения с соответствующими значениями амплитуд. Это достигается путем введения на каждом прямом выходе 7, 9, . .., 23 компараторов 74.i (i = 1...9) дополнительно двухвходовых элементов 85. j И (j = 1...8), причем к одному входу элемента 85. j И необходимо подключить прямой выход компаратора 74.n, а на второй - подать сигнал с инверсного выхода следующего компаратора 74.n+1 (см. фиг. 2). Каждый раз при срабатывании следующего n + 1 компаратора на его инверсных выходах 8, 10, . . ., 24 появится сигнал "0", который поступит на второй вход элемента 85.j И, а так как на первый вход элемента 85.j И подан сигнал "1", к соответствующим выходам 7, 9,..., 23, в результате произойдет логическое отключение прямого выхода предыдущего компаратора 74.n, предназначенного для распознавания меньшего n-го значения k-значного сигнала. Таким образом, элемент распознавания, образуемый параллельным АЦП 1 и дешифратором ДШ 2, преобразует сигналы k-значного алфавита в двузначное их представление состояний пространственных полюсов - выходов 25 - 34.

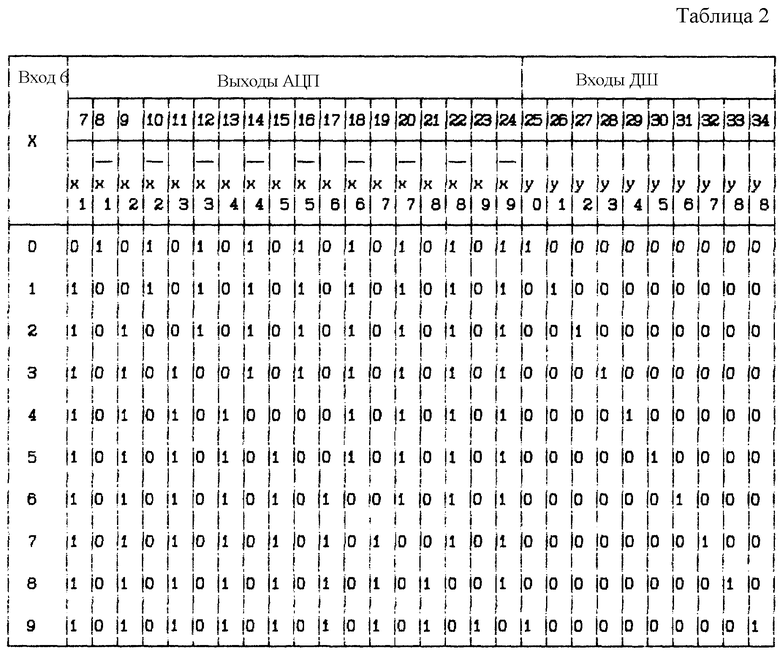

Таким образом, используя в АЦП 1 девять компараторов 76.1 - 76.9, можно распознать десять уровней 10-значного сигнала. Для распознавания нулевого сигнала при этом нет необходимости в дополнительном компараторе, поскольку инверсный сигнал с выхода 8 первого компаратора полностью соответствует тому сигналу, который должен формировать элемент распознавания "0". Сигнал распознавания "1" от компаратора 74.1 проходит через элемент 85.1 И в том случае, когда не включен компаратор 74.2, который распознает логическую "2", и происходит распознавание логической "1", то есть на вход 6 АЦП 1 поступил 10-значный сигнал с уровнем, который равен "1". Соответственно, когда на вход 6 поступает логическая "2", происходит отключение прямого выхода 7 предыдущего компаратора и на отдельный прямой выход 9 второго компаратора 74.2 находит логическая "1", которая сигнализирует о том, что состоялось распознавание логической "2". Аналогично выглядит работа всех последующих компараторов 74. i при превышении уровня входного сигнала над опорным уровнем, кроме последнего. Дело в том, что следующего более высокого уровня входного сигнала не существует, а все остальные значения меньше, поэтому отпадает необходимость отключения данного выхода под действием последующего каскада. Все описанные логические функции реализует ДШ 2 (см. фиг. 2), а логика его работы описывается таблицей истинности (табл. 2)

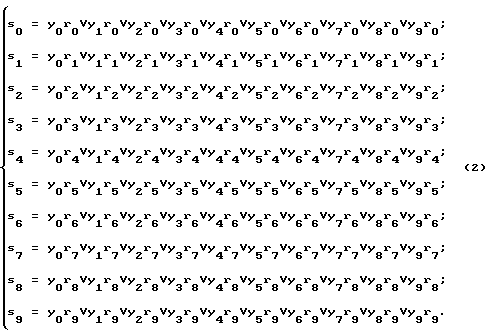

Логику работы ДШ 2 описывает следующая система уравнений:

где  - сигналы инверсных выходов 8, 10,...,24 АЦП 1; x1 - х9 - сигналы прямых выходов 7, 9,...,23 АЦП 1, & - операция конъюнкции.

- сигналы инверсных выходов 8, 10,...,24 АЦП 1; x1 - х9 - сигналы прямых выходов 7, 9,...,23 АЦП 1, & - операция конъюнкции.

Переходя к описанию роботы устройства в деталях, отметим, что здесь рассмотрен вариант реализации функционального преобразователя (фиг. 1) для значности k = 10. Поскольку преобразователь универсальный, то мощность множества функций, которые реализуются одновходовым универсальным функциональным преобразователем, равна N = Kk = 1010.

В силу универсальности функционального преобразователя десять вариантов возможных состояний пространственных выходов АЦП 1 и ДШ 2 необходимо преобразовать в 10 комбинаций управляющих сигналов для ЦАП 5. Дело в том, что в общем случае после распознавания одного из k-значных сигналов на выходах ДШ 2 получен один из k вариантов пространственных (параллельных) единичных кодов (см. табл. 2), а для формирования выходных сигналов преобразователя необходимо сопоставить каждому из k входных сигналов один из k сигналов выходной k-значной функции одной переменной, которая содержит также k значений, то есть необходимо сформировать управляющий сигнал на одном из k входов 45 - 54 ЦАП 5. К примеру, покажем ряд функций 10-значной логики одной переменной

переменная: 0 1 2 3 4 5 6 7 8 9;

инверсия: x = k - 1 - x: 9 8 7 6 5 4 3 2 1 0;

циклическое отрицание: x = x + 1(mod k): 1 2 3 4 5 6 7 8 9 0.

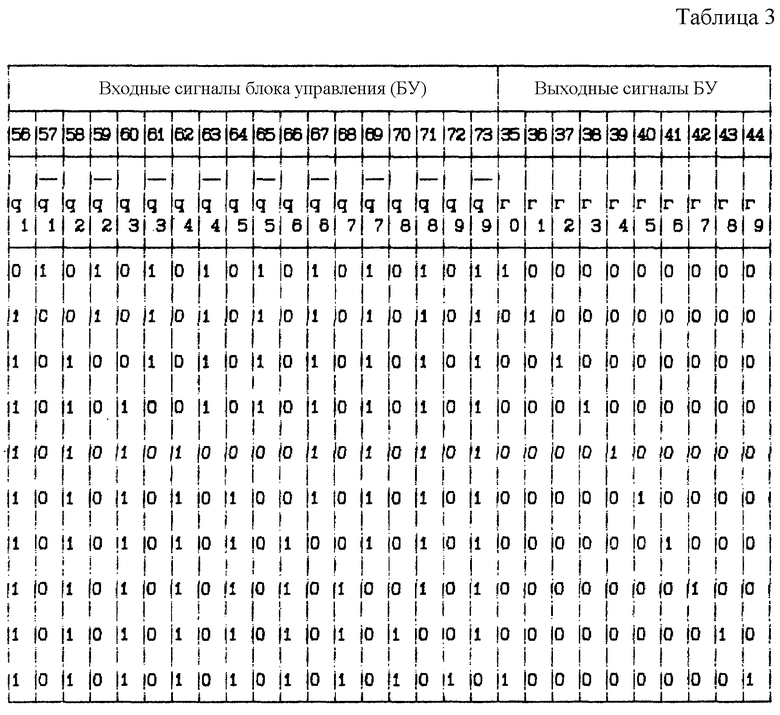

Таким образом, для пространственного варианта действия функционального преобразователя с многозначным кодированием, при k = 10, необходимо сформировать в каждом такте только один сигнал на выходе пространственной коммутационной матрицы 10 х 10, что и показано в табл. 3 для десяти выходов 45 - 54 КМ 3.

Для осуществления такого пространственного распределения в двух измерениях в преобразователь введен КМ 3, который содержит десять блоков 3.k (k = 1. . . 10) коммутации сигналов логической "1" с выходов ДШ 2. Таким образом, пространственный дешифратор 2 осуществляет вертикальное перемещение логической "1" в матрице управляющих сигналов и включает соответствующий блок коммутации 3.k (див. фиг. 3), который в свою очередь осуществляет перекоммутацию логической "1", поступившей в горизонтальном направлении с АЦП 1, в одном из k возможных вертикальных направлений для включения соответствующего из линейки 88 ключей ЦАП 5. Поскольку каждый из k ключей ЦАП 5 постоянно подключен к соответствующему ему k значению опорных сигналов, то на выход 55 преобразователя по ходу изменений значений k-значной функции на входе 6 преобразователя будут поочередно поступать значения функции, выбранной для реализации коммутатором 3 и блоком управления 4 соответственно.

Управление процессом логической перекоммутации осуществляется блоком 4 управления под влиянием внешних управляющих сигналов с входов 56 - 73. Поскольку необходимо сформировать k управляющих пространственных сигналов на входы k блоков коммутации 3.k, на вешние входы 56 - 73 блока 4 управления поступает n-разрядный параллельный код, где n = k. При таком подходе к выбору разрядности кода обычно возникает определенная избыточность, но для работы преобразователя это обстоятельство несущественно, поскольку часть возможных значений управляющего сигнала можно не использовать или использовать как избыточное для повышения помехоустойчивости. Более того, входы 56 - 73 могут быть управляемы от любого другого элемента распознавания буквы k-значного алфавита.

Для нашего примера n = 10, а это значит, что из возможных 210 используются только 10 входных сигналов следующего вида: <0000000000>, <10000000>, <11000000>, ..., <1111111111>, которые преобразуются в 10 вариантов пространственных единичных кодов: <1000000000>, <0100000000>,..., <0000000001>. Таким образом, мы снова приходим к таблице истинности (табл. 3), аналогичной табл. 2 и, соответственно, к алгоритму работы и структуре, аналогичной ДШ 2.

Возвращаясь к работе блока 3 коммутатора, необходимо отметить, что на его входы 25 - 34, 35 - 44 поступают сигналы от дешифратора 2 и блока 4 управления соответственно, обозначим эти сигналы как yo, y1,..., y9 и ro, r1, . .., r9, причем сигналы yo, y1,..., y9 от ДШ 2 осуществляют выбор блока 3. k (k = 1...10) коммутации, а сигналы ro, r1,..., r9 от ДШ 2 - выбор значения из k, которое должно быть подключено на выход 55 преобразователя. Соответствующие выходы блоков 3.k объединены вместе и образуют десять выходов 45 - 54 коммутатора 3. Использование проводного ИЛИ на выходах 45 - 54 правомерно, поскольку в каждый такт работы преобразователя активным является только один из выходов блоков 3.k коммутации. Формально работу коммутатора 3 можно описать следующей системой уравнений

где V - операция дизъюнкции.

Наконец отметим, что введение в функциональный преобразователь с многозначным кодированием коммутатора 3, который состоит из десяти блоков 3.k коммутации, каждый из которых реализован на двухвходовых элементах 86.i И а также блока управления 4, который включает в себя двухвходовые элементы 85.j И, которые образуют в пространстве структуру параллельно типа с пространственным k-значным кодированием, осуществленным за счет двоичных состояний пространственных полюсов, а также использования методов теории интеллекта для описания алгоритмов работы и структуры построения, когда k-значные числа и преобразования над ними описываются с помощью алгебры конечных предикатив, впервые позволило получить наипростейшие аналитические записи (1), (2) для описания работы основных компонентов функционального преобразователя, которые совпадают с формулами алгебры логики, но сохраняют свойства k-значного алфавита, обеспечивают параллелизм и однородность структуры и позволяют предельно экономно описать и реализовать все необходимые преобразования входного сигнала. Дело в том, что применение логических методов математического моделирования с симбиозом k-значного кодирования и двухзначных методов построения промежуточных пространственных преобразователей (ДШ, ЛМ, БУ) позволило реализовать структуру функционального преобразователя с многозначным кодированием существенно проще, чем при использовании традиционных решений, которые получают при использовании вычислительных методов алгебры логики и традиционных двоичных методов построения в базисах дизъюнктивных и конъюнктивных нормальных форм, из-за отсутствия влияния процедур учета межразрядных связей и набегания длины разрядной сетки, обеспечить однотипность и однородность внутренней структуры, существенно уменьшить аппаратурные затраты на создание преобразователя, упростить шинную коммутацию, а также повысить быстродействие за счет минимальной задержки сигналов во всех звеньях преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА ИЗОБРАЖЕНИЯ В ЭВМ | 2003 |

|

RU2256210C2 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ И СИНХРОНИЗАЦИИ ДЛЯ ОБРАБОТКИ НЕПРЕРЫВНОГО СИГНАЛА | 1990 |

|

SU1812885A1 |

| Система записи и воспроизведения видеосигнала | 1990 |

|

SU1783635A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СОБСТВЕННЫХ ЗНАЧЕНИЙ МАТРИЦ | 2000 |

|

RU2168760C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИЗОБРАЖЕНИЯ В ЭВМ | 2004 |

|

RU2267150C1 |

| Устройство для контроля качества канала связи с шумоподобными сигналами | 1989 |

|

SU1628210A1 |

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ ОДНОФАЗНОГО ЗАМЫКАНИЯ НА ЗЕМЛЮ В ЭЛЕКТРИЧЕСКОЙ СЕТИ ПЕРЕМЕННОГО ТОКА | 1995 |

|

RU2101826C1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| Устройство для ввода-вывода полутоновой информации | 1984 |

|

SU1164717A1 |

| НЕПОСРЕДСТВЕННЫЙ ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ БЕСТРАНСФОРМАТОРНЫЙ | 2022 |

|

RU2787121C1 |

Изобретение относится к автоматике, вычислительной технике и может использоваться в системах управления, а также при автоматической обработке текстовой и языковой информации. Функциональный преобразователь с многозначным кодированием состоит из аналого-цифрового преобразователя и цифроаналогового преобразователя, дешифратора, который включает в себя восемь двухвходовых элементов И, коммутатора, состоящего из десяти блоков коммутации, каждый из которых выполнен на десяти двухвходовых элементах И, а также блока управления, который включает восемь двухвходовых элементов И, причем вход аналого-цифрового преобразователя является информационным входом функционального преобразователя, а выход цифроаналогового преобразователя - его выходом, входы блока управления являются внешними входами управления. Введение в функциональный преобразователь с многозначным кодированием коммутатора и блока управления обеспечивает однородность выполнения всех узлов преобразователя и приводит к повышению технологичности устройства в процессе микроэлектронной реализации и возрастанию быстродействия, а также за счет повышения до десяти реализуемой значности обеспечивается расширение его функциональных возможностей. 4 ил., 3 табл.

Функциональный преобразователь с многозначным кодированием состоит из аналого-цифрового преобразователя, вход которого является информационным входом функционального преобразователя, и цифроаналогового преобразователя, выход которого является информационным выходом функционального преобразователя, а также дешифратора, который включает в себя двухвходовой элемент И, отличающийся тем, что в него дополнительно введены коммутатор, состоящий из десяти блоков коммутации, каждый из которых реализован на десяти двухвходовых элементах И, а также блок управления, включающий восемь двухвходовых элементов И, в дешифратор дополнительно введено семь двухвходовых элементов И, причем выходы аналого-цифрового преобразователя подключены к соответствующим восемнадцати информационным входам дешифратора, при этом первый вход дешифратора, который является первым входом первого элемента И, подключен к первому прямому выходу аналого-цифрового преобразователя, первый инверсный выход аналого-цифрового преобразователя подключен к первому выходу дешифратора, второй вход первого элемента И подключен к второму инверсному выходу аналого-цифрового преобразователя, выход первого элемента И подключен к второму выходу дешифратора, второй вход дешифратора, который является первым входом второго элемента И, подключен к второму прямому выходу аналого-цифрового преобразователя, второй вход второго элемента И подключен к третьему инверсному выходу аналого-цифрового преобразователя, выход второго элемента И подключен к третьему выходу дешифратора, третий вход дешифратора, который является первым входом третьего элемента И, подключен к третьему прямому выходу аналого-цифрового преобразователя, второй вход третьего элемента И подключен к четвертому инверсному выходу аналого-цифрового преобразователя, выход третьего элемента И подключен к четвертому выходу дешифратора, четвертый вход дешифратора, который является первым входом четвертого элемента И, подключен к четвертому прямому выходу аналого-цифрового преобразователя, второй вход четвертого элемента И подключен к пятому инверсному выходу аналого-цифрового преобразователя, выход четвертого элемента И подключен к пятому выходу дешифратора, пятый вход дешифратора, который является первым входом пятого элемента И, подключен к пятому прямому выходу аналого-цифрового преобразователя, второй вход пятого элемента И подключен к шестому инверсному выходу аналого-цифрового преобразователя, выход пятого элемента И подключен к шестому выходу дешифратора, шестой вход дешифратора, который является первым входом шестого элемента И, подключен к шестому прямому выходу аналого-цифрового преобразователя, второй вход шестого элемента И подключен к седьмому инверсному выходу аналого-цифрового преобразователя, выход шестого элемента И подключен к седьмому выходу дешифратора, седьмой вход дешифратора, который является первым входом седьмого элемента И, подключен к седьмому прямому выходу аналого-цифрового преобразователя, второй вход седьмого элемента И подключен к восьмому инверсному выходу аналого-цифрового преобразователя, выход седьмого элемента И подключен к восьмому выходу дешифратора, восьмой вход дешифратора, который является первым входом восьмого элемента И, подключен к восьмому прямому выходу аналого-цифрового преобразователя, второй вход восьмого элемента И подключен к девятому инверсному выходу аналого-цифрового преобразователя, выход восьмого элемента И подключен к девятому выходу дешифратора, девятый прямой выход аналого-цифрового преобразователя подключен к десятому выходу дешифратора, первые входы элементов И в каждом блоке коммутации соединены вместе и подключены к соответствующим выходам дешифратора, вторые входы первого, одиннадцатого, ..., девяносто первого элементов И коммутатора соединены вместе и подключены к первому выходу блока управления, вторые входы второго, двенадцатого, ..., девяносто второго элементов И коммутатора соединены вместе и подключены к второму выходу блока управления, вторые входы третьего, тринадцатого, ..., девяносто третьего элементов И коммутатора также соединены вместе и подключены к третьему выходу блока управления, вторые входы четвертого, четырнадцатого, . .., девяносто четвертого элементов И коммутатора соединены вместе и подключены к четвертому выходу блока управления, вторые входы пятого, пятнадцатого, . .., девяносто пятого элементов И коммутатора соединены вместе и подключены к пятому выходу блока управления, вторые входы шестого, шестнадцатого, ..., девяносто шестого элементов И коммутатора соединены вместе и подключены к шестому выходу блока управления, вторые входы седьмого, семнадцатого, ..., девяносто седьмого элементов И коммутатора соединены вместе и подключены к седьмому выходу блока управления, вторые входы восьмого, восемнадцатого, ... , девяносто восьмого элементов И коммутатора тоже соединены вместе и подключены к восьмому выходу блока управления, вторые входы девятого, девятнадцатого, ..., девяносто девятого элементов И коммутатора соединены вместе и подключены к девятому выходу блока управления, вторые входы десятого, двадцатого, ..., сотого элементов И коммутатора соединены вместе и подключены к выходу блока управления, выходы первого, одиннадцатого, ..., девяносто первого элементов И коммутатора соединены вместе и образуют первый выход коммутатора, выходы второго, двенадцатого, ..., девяносто второго элементов И коммутатора соединены вместе и образуют второй выход коммутатора, выходы третьего, тринадцатого, девяносто третьего элементов И коммутатора также соединены вместе и образуют третий выход коммутатора, выходы четвертого, четырнадцатого, ..., девяносто четвертого элементов И коммутатора соединены вместе и образуют четвертый выход коммутатора, выходы пятого, пятнадцатого, . . . , девяносто пятого элементов И коммутатора соединены вместе и образуют пятый выход коммутатора, выходы шестого, шестнадцатого, ..., девяносто шестого элементов И коммутатора соединены вместе и образуют шестой выход коммутатора, выходы седьмого, семнадцатого, ..., девяносто седьмого элементов И коммутатора соединены вместе и образуют седьмой выход коммутатора, выходы восьмого, восемнадцатого, ..., девяносто восьмого элементов И коммутатора тоже соединены вместе и образуют восьмой выход коммутатора, выходы девятого, девятнадцатого, ..., девяносто девятого элементов И коммутатора соединены вместе и образуют девятый выход коммутатора, выходы десятого, двадцатого, . . . , сотого элементов И коммутатора соединены вместе и образуют десятый выход коммутатора, выходы коммутатора подключены к соответствующим входам цифроаналогового преобразователя, внешние входы управления функционального преобразователя образуют входы блока управления, причем первый инверсный вход управления подключен к первому выходу блока управления, первый вход первого элемента И блока управления подключен к первому прямому входу управления функционального преобразователя, а второй вход первого элемента И подключен к инверсному второму входу управления, выход первого элемента И является вторым выходом блока управления, первый вход второго элемента И блока управления подключен к второму прямому входу управления функционального преобразователя, а второй вход второго элемента И подключен к инверсному третьему входу управления, выход второго элемента И является третьим выходом блока управления, первый вход третьего элемента И блока управления подключен к третьему прямому входу управления функционального преобразователя, а второй вход третьего элемента И подключен к инверсному четвертому входу управления, выход третьего элемента И является четвертым выходом блока управления, первый вход четвертого элемента И блока управления подключен к четвертому прямому входу управления функционального преобразователя, а второй вход четвертого элемента И подключен к пятому инверсному входу управления, выход четвертого элемента И является пятым выходом блока управления, первый вход пятого элемента И блока управления подключен к пятому прямому входу управления функционального преобразователя, а второй вход пятого элемента И подключен к инверсному шестому входу управления, выход пятого элемента И является шестым выходом блока управления, первый вход шестого элемента И блока управления подключен к шестому прямому входу управления функционального преобразователя, а второй вход шестого элемента И подключен к инверсному седьмому входу управления, выход шестого элемента И является седьмым выходом блока управления, первый вход седьмого элемента И блока управления подключен к седьмому прямому входу управления функционального преобразователя, а второй вход седьмого элемента И подключен к инверсному восьмому входу управления, выход седьмого элемента И является восьмым выходом блока управления, первый вход восьмого элемента И блока управления подключен к восьмому прямому входу управления функционального преобразователя, а второй вход восьмого элемента И подключен к инверсному девятому входу управления, выход восьмого элемента И является девятым выходом блока управления, девятый прямой вход управления соединен с десятым выходом блока управления.

| Функциональный преобразователь | 1988 |

|

SU1510077A1 |

| RU 94012059 А1, 27.12.95 | |||

| ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1989 |

|

RU2054801C1 |

| RU 2001518 С1, 15.10.93 | |||

| DE 4115081 А1, 12.11.92 | |||

| DE 19502598 А1, 14.09.95 | |||

| US 5412262 А, 02.05.95 | |||

| US 5402018 А, 28.03.95. | |||

Авторы

Даты

2000-04-20—Публикация

1997-02-04—Подача