Изобретение относится к технологии полупроводниковых приборов, в частности к технологии изготовления полупроводниковых структур, используемых для производства диодов, транзисторов, тиристоров, интегральных схем и кремниевых структур с диэлектрической изоляцией.

Для формирования полупроводниковых структур, используемых в производстве высоковольтных полупроводниковых приборов, применяют различные способы, заключающиеся в эпитаксиальном осаждении или наращивании на слаболегированную монокристаллическую подложку сильнолегированного низкоомного полупроводникового слоя, обработке поверхности осажденного полупроводникового слоя параллельно обратной поверхности монокристаллической подложки и последующем удалении до необходимой толщины монокристаллической подложки [1] [2]

Недостатком этих способов является то, что при высокотемпературных процессах происходит автолегирование рабочей стороны пластины примесями осажденного слоя.

Основным недостатком этих способов является то, что с повышением диаметра структур необходимо увеличивать толщину несущего наращиваемого поликремниевого слоя, что приводит к короблению структур, нарушению плоскопараллельности пластин за счет подпыла поликремния и снижения теплоотвода с кристаллов, полученных из этих структур.

Наиболее близким техническим решением к данному изобретению является способ изготовления полупроводниковых структур с диэлектрической изоляцией, в котором на поверхности исходной подложки, представляющей собой монокристаллическую подложку с эпитаксиальным слоем, формируют микрорельеф покрытий диэлектриком, после чего соединяют через слой с опорной кремниевой подложкой и затем удаляют часть исходной подложки со стороны, обратной рельефу, до создания отдельных монокристаллических "карманов", в которых формируют активные элементы [3]

Основными недостатками этого способа являются невозможность реализации контакта к активным элементам с обратной стороны кристаллов и плохой теплоотвод с кристаллов.

Основным техническим результатом данного изобретения является: уменьшение коробления пластин, усиление их механической прочности, снижение автолегирования.

Предложенный способ изготовления полупроводниковых структур позволяет повысить качество структур большого диаметра за счет уменьшения толщины наносимых слоев, устранения коробления структур и автолегирования рабочей поверхности из низкоомного слоя, улучшения теплоотвода с кристаллов и возможность реализации контакта к активным элементам с обратной стороны кристаллов, например, к коллекторам мощных транзисторов кремниевых структур с диэлектрической изоляцией через окна в диэлектрике на дне "карманов", а также за счет отсутствия автолегирования рабочей стороны пластины примесями осажденного низкоомного слоя.

Данный технический результат достигается тем, что в способе изготовления полупроводниковых структур сначала формируют, например, диффузией на исходной подложке низкоомный слой, соединяют его через соединительный слой стекла с опорной подложкой, изготовленной из высокоомного полупроводника или полупроводника, легированного сурьмой, затем удаляют часть монокристаллической подложки, формируют в полупроводниковой структуре активные элементы.

Низкоомный слой формируют на исходной подложке, в качестве которой используют монокристаллическую подложку с эпитаксиальным слоем, либо с микрорельефом, покрытым диэлектриком, либо с микрорельефом, частично покрытым диэлектриком, после формирования в полупроводниковой структуре активных элементов, перед разделением ее на кристаллы, удаляют опорную подложку и соединительный слой. В качестве соединительного слоя используют стекло.

Такой способ позволяет снизить коробление структур большого диаметра за счет уменьшения толщины низкоомного слоя, отпадает необходимость в нанесении и сохранении защитного покрытия, так как функции защитного покрытия выполняет опорная подложка, а соединительный слой выполняет функции буферного слоя при утонении структуры.

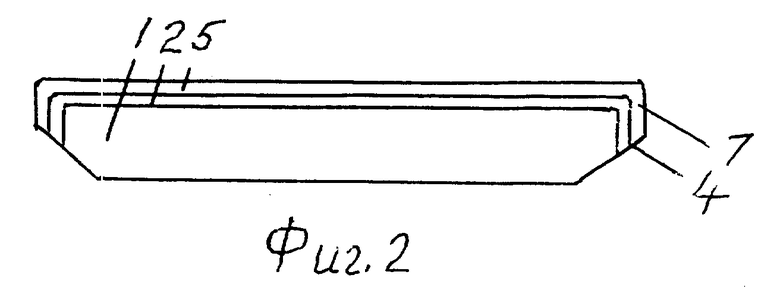

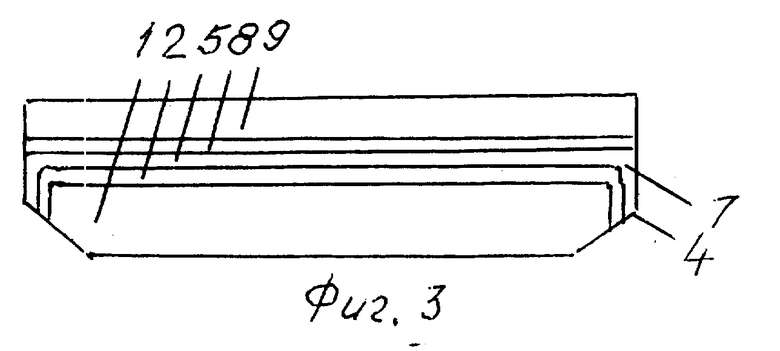

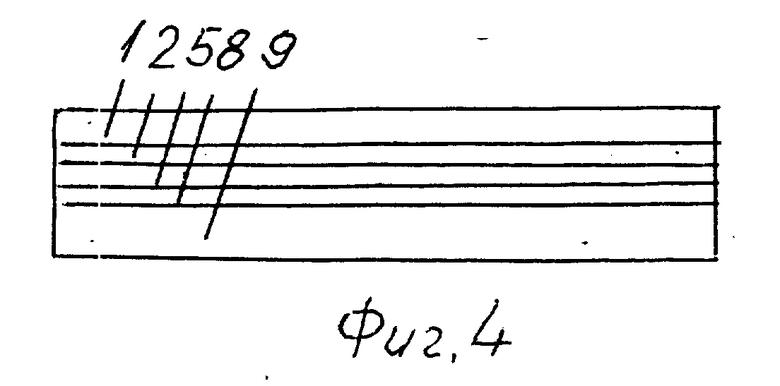

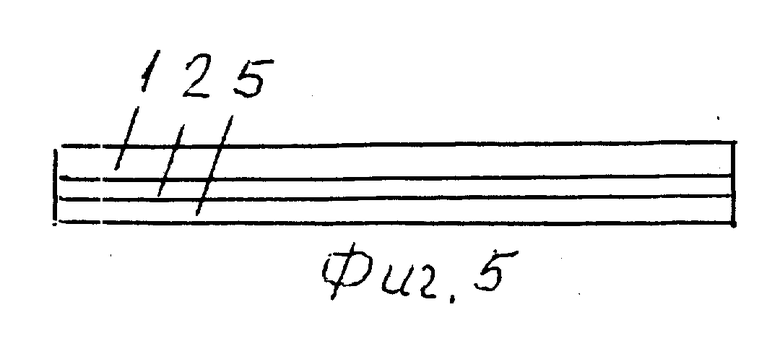

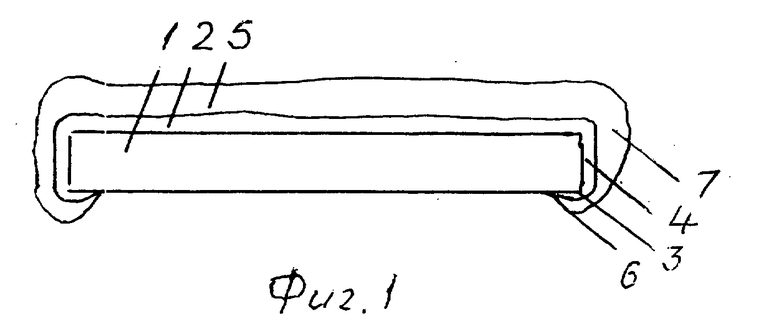

На фиг.1 представлена исходная полупроводниковая монокристаллическая подложка с монокристаллическим слоем меньшей омности и низкоомным слоем; на фиг. 2 показана подложка после снятия части низкоомного слоя и удаления подпыла (буртика) с обратной стороны; на фиг.3 монокристаллическая подложка, соединенная с опорной пластиной; на фиг.4 монокристаллическая подложка после калибровки структуры по диаметру и удаления части монокристаллической подложки параллельно опорной пластине; на фиг.5 структура после удаления опорной пластины и соединительного слоя (активные элементы не показаны).

Полупроводниковая структура имеет монокристаллическую подложку 1, первый монокристаллический слой 2, "буртик" с обратной стороны подложки от первого монокристаллического слоя 3, нарост от первого монокристаллического слоя по краю подложки 4, второй низкоомный моно- или поликристаллический слой 5, "буртик" с обратной стороны подложки от второго моно- или поликристаллического слоя 6, нарост от второго моно- или поликристаллического слоя по краю подложки 7, соединительный слой 8, опорную пластину 9.

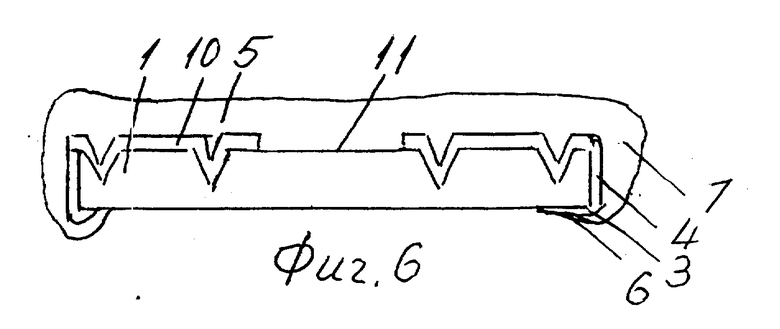

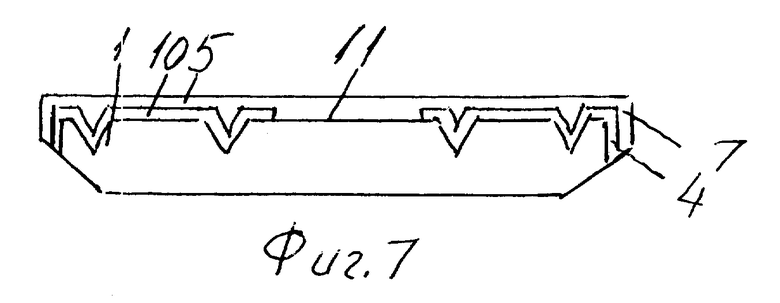

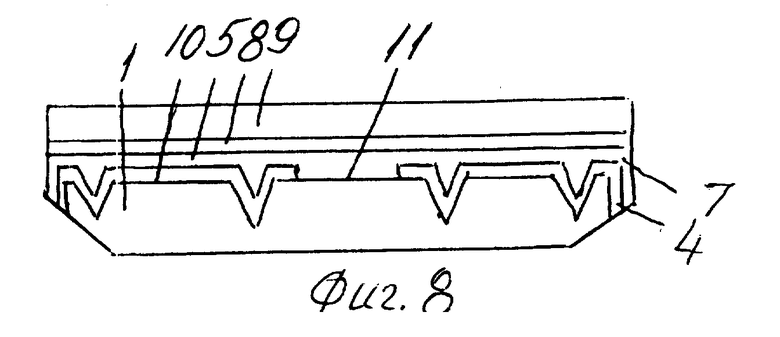

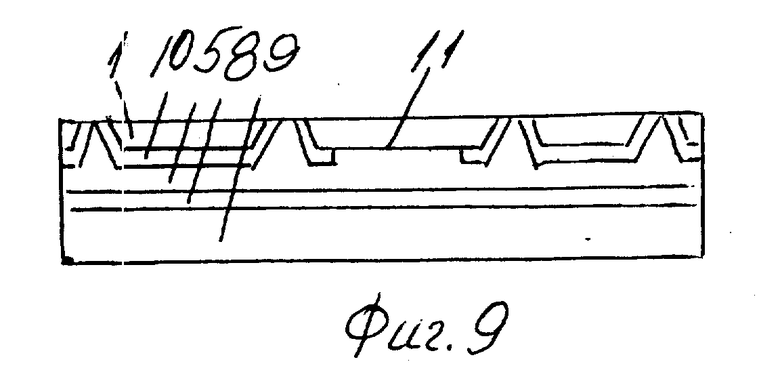

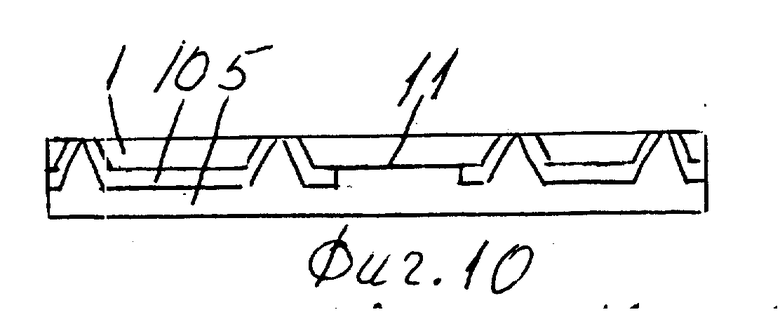

На фиг.6 представлена исходная полупроводниковая подложка с микрорельефом, частично покрытая диэлектриком, с нарощенным на ней низкоомным слоем; на фиг. 7 подложка после снятия части низкоомного слоя и удаления подпыла ("буртика") с обратной стороны; на фиг.8 подложка, соединенная с опорной подложкой; на фиг.9 полупроводниковая структура после калибровки ее по диаметру и удаления части исходной подложки параллельно опорной подложке; на фиг. 10 структура после удаления опорной подложки и соединительного слоя (активные элементы не показаны).

Полупроводниковая структура имеет исходную полупроводниковую подложку с микрорельефом 1, слой диэлектрика 10, окна в диэлектрике на дне "карманов" 11, низкоомный слой 5, "буртик" с обратной стороны подложки от нарощенного низкоомного слоя 6, нарост от низкоомного слоя по краю подложки 7, соединительный слой 8, опорную пластину 9.

Изготовление полупроводниковых структур осуществляется следующим образом.

Пример 1. На исходную плоскопараллельную монокристаллическую кремниевую подложку 1 диаметром 100 мм с удельным сопротивлением 120 ом•см, легированную фосфором, толщиной 400 мкм методом эпитаксии наносится слой 2 толщиной 20 мкм с удельным сопротивлением 20 ом•см, легированный фосфором. На этот эпитаксиальный слой наносится поликремниевый слой 5 толщиной 170 мкм, легированный фосфором, с удельным сопротивлением менее 0,01 ом•см (см.фиг.1). При нанесении этих двух слоев образуется подпыл (буртик), который удаляется на установке снятия фаски.

Так как при нанесении слоев кремния имеется разброс по толщине, то низкоомный слой сошлифовывается до 150 мкм параллельно поверхности исходной пластины, которая является базовой. Затем через слой стекла 8 толщиной 6-12 мкм присоединяется при 1200oC опорная пластина 9 толщиной 450 мкм.

После калибровки полученной структуры по диаметру исходная пластина утончается до 130 мкм.

Опорная пластина изготавливается из высокоомного кремния или кремния, легированного сурьмой, поэтому в процессе формирования полупроводниковых активных элементов отсутствует автолегирование высокоомной части структуры.

При изготовлении мощных полупроводниковых структур для улучшения теплоотвода соединительный слой и опорная пластина удаляются после формирования в полупроводниковой структуре активных элементов перед разделением ее на кристаллы.

При формировании структуры с микрорельефом для подвода контактов к коллекторам мощных транзисторов дно карманов не защищается диэлектрическим слоем, например перед травлением канавок в этих местах создаются островки нитрида кремния. После травления канавок и окисления всей пластины нитрид кремния травится в травителе, который не травит основной диэлектрический слой.

Пример 2. На исходную монокристаллическую кремниевую подложку с микрорельефом 1 диаметром 100 мм, легированную фосфором, с удельным сопротивлением 40 ом•см, толщиной 500 мкм, глубиной канавок 80 мкм и частично покрытую слоем диэлектрика 10 толщиной 3 мкм методом эпитаксии наносится поликремниевый слой 5 толщиной 220 мкм, легированный фосфором, с удельным сопротивлением менее 0,01 ом•см (см.фиг.6).

Затем на установке снятия фаски убирается подпыл "буртик", низкоомный слой сошлифовывается до 200 мкм параллельно плоской поверхности исходной пластины, которая является базовой, на станке автоматической шлифовки САШ-420. Затем через слой стекла 8 толщиной 6-12 мкм в диффузионной печи при 1200oC присоединяется опорная пластина 9 толщиной 450 мкм. После калибровки полученной структуры по диаметру исходная пластина утончается до разделения "карманов".

Изготовление полупроводниковых структур с микрорельефом, покрытым диэлектриком, аналогично приведенному выше (пример 2), только без травления окон 11 на дне "карманов".

| название | год | авторы | номер документа |

|---|---|---|---|

| СВЧ-ТРАНЗИСТОРНАЯ МИКРОСБОРКА | 1992 |

|

RU2101803C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 2004 |

|

RU2302684C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ | 1999 |

|

RU2197768C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ СВЧ ПРИБОРОВ | 2013 |

|

RU2546856C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ОГРАНИЧИТЕЛЬНОГО МОДУЛЯ НА ВСТРЕЧНО-ВКЛЮЧЕННЫХ P-I-N СТРУКТУРАХ | 2016 |

|

RU2622491C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНОГО ДМОП-ТРАНЗИСТОРА | 2000 |

|

RU2189089C2 |

| СПОСОБ ПОЛУЧЕНИЯ ДИЭЛЕКТРИЧЕСКИХ ПОКРЫТИЙ | 1980 |

|

SU940601A1 |

| СПОСОБ УПРАВЛЕНИЯ РАБОТОЙ МЕМРИСТИВНОЙ КОНДЕНСАТОРНОЙ СТРУКТУРЫ МЕТАЛЛ-ДИЭЛЕКТРИК-ПОЛУПРОВОДНИК | 2018 |

|

RU2706197C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ЭПИТАКСИАЛЬНЫХ КРЕМНИЕВЫХ СТРУКТУР | 1982 |

|

SU1056807A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРАНЗИСТОРНОЙ СВЧ LDMOS СТРУКТУРЫ | 2012 |

|

RU2515124C1 |

Использование: технология полупроводниковых приборов. Сущность изобретения: способ изготовления полупроводниковых структур включает соединение исходной подложки через соединительный слой с опорной подложкой, удаление части исходной подложки, формирование активных элементов. Со стороны соединительного слоя на исходной подложке формируют низкоомный слой, в качестве опорной подложки используют высокоомный полупроводник либо проводник, легированный сурьмой, а в качестве исходной подложки используют монокристаллическую подложку с эпитаксиальным слоем, либо с микрорельефом, покрытым диэлектриком, либо с микрорельефом, частично покрытым диэлектриком. 2 з.п. ф-лы, 10 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| FR, патент, 1446395, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| US, патент, 3428499, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Горяинов С.А | |||

| Диэлектрическая изоляция элементов интегральных схем | |||

| - М.: Сов.радио, 1975, с.39-44. | |||

Авторы

Даты

1998-01-20—Публикация

1993-03-02—Подача