Изобретение относится к информационно-измерительной технике и может быть использовано в адаптивно-адресных телеметрических системах.

Известно устройство для передачи информации в адаптивных телеметрических системах (авт. св. СССР N 302738), содержащее синхронизатор, блок сокращения избыточности, блок кодирования адреса, блок кодирования измеренного значения отсчета, блок формирования кодовой группы, блок кодирования интервалов времени, в составе триггера, двух дифференцирующих цепочек, двух диодов, двух двоичных счетчиков, элемента ИЛИ, которые соответствующим образом соединены между собой.

Недостаток устройства состоит в том, что оно имеет низкую информативность, так как обеспечивает передачу информации только одного параметра при невысоком выигрыше по числу символов сообщения в сравнении с циклической системой передачи информации.

Известно устройство для передачи информации в адаптивных телеметрических системах (авт. св. СССР N 1203568), содержащее синхронизатор, блок сокращения избыточности, блок кодирования адреса, блок кодирования измеренного значения отсчета, блок кодирования интервалов времени, блок формирования кодовый группы, которые соответствующим образом объединены между собой.

Недостаток устройства состоит в том, что оно имеет низкую информативность, так как обеспечивает одновременную передачу только одного параметра при невысоком выигрыше по числу символов сообщения в сравнении с циклической системой передачи информации.

Известно устройство для передачи информации (авт. св. СССР N 226948), содержащее анализатор информации, запоминающее устройство адреса (ЗУ адреса), запоминающее устройство информационной части (ЗУ информационной части), сумматор, синхронизатор, при атом анализатор информации подключен по входу к синхронизатору, а по выходам - к ЗУ адреса и ЗУ информационной части, соединенным по входам с синхронизатором, а по выходам - с сумматором, выход которого является выходом устройства.

Недостаток устройства состоит в том, что оно имеет низкую достоверность передачи информации и низкую информативность.

Известно устройство для передачи информации в адаптивных телеметрических системах (авт. св. СССР N 1681318), содержащее анализатор информации, блок памяти адреса, блок памяти информации, синхронизатор, блок формирования маркера, блок управления передачей, при этом информационные входы анализатора информации являются информационными входами устройства, первый, второй и третий выходы синхронизатора соединены соответственно с первыми входами блока памяти адреса, блока памяти информации и анализатора информации, первый и второй выходы которого подключены соответственно к вторым входам блока памяти адреса и блока памяти информации, выходы которых соединены соответственно с первым и вторым входами блока управления передачей, выход которого является выходом устройства, выход блока формирования маркера соединен с третьим входом блока управления передачей, второй выход анализатора информации подключен к третьим входам блока памяти адреса и блока памяти информации, четвертому входу блока управления передачей, первый выход анализатора информации соединен с пятым входом блока управления передачей и третьим входом блока памяти информации, выходы группы анализатора информации соединены с соответствующими входами группы блока памяти информации, четвертый, пятый, шестой, седьмой и восьмой выходы синхронизатора подключены соответственно к четвертым входам блока памяти адреса и блока памяти информации, первому, второму и третьему входам блока формирования маркера, девятый выход синхронизатора соединен с пятыми входами блока памяти адреса и блока памяти информации, шестым входом блока управления передачей, десятый выход синхронизатора соединен с шестыми входами блока памяти адреса и блока памяти информации, вторым входом анализатора информации, седьмым входом блока управления передачей и четвертым входом блока формирования маркера (прототип).

Недостаток устройства состоит в том, что оно имеет низкую достоверность передачи информации из-за слабой помехоустойчивости структуры кадра сообщения.

Цель изобретения - повышение достоверности передачи информации.

Указанная цель достигается тем, что в устройство для передачи информации в адаптивных, телеметрических системах, содержащее анализатор информации, информационные, входы которого являются информационными входами устройства, синхронизатор, первый выход которого соединен с первым входом измерителя времени, второй выход синхронизатора соединен, со вторым входом измерителя времени и первым входом анализатора информации, второй вход которого подключен к третьему выходу синхронизатора, первый выход анализатора информации соединен с объединенными первыми входами блока памяти адреса и блока памяти информации, второй выход анализатора информации соединен с первым входом блока управления передачей, второй и третий входы которого подключены соответственно к выходам блока памяти адреса и блока памяти информации, вторые входы которого подключены к третьим выходам анализатора информации, первый выход блока управления передачей является выходом устройства, введены блок управления маркировкой отсчетов и формированием кадров сообщений, первый, второй, третий и четвертый входы которого подключены соответственно к второму, четвертому и пятому выходам синхронизатора и четвертому выходу анализатора информации, пятые выходы которого соединены со вторыми входами блока памяти адреса, третьи входы блока памяти адреса и блока памяти информации объединены и подключены к первых выходам блока управления маркировкой отсчетов и формированием кадров сообщений, второй, третьи и четвертые выходы которого соединены соответственно с четвертым входом блока управления передачей, четвертыми входами блока памяти адреса и четвертыми входами блока памяти информации, пятые входы которого подключены к выходам измерителя времени, третий и четвертый входы которого подключены соответственно к шестому и седьмому выходам анализатора информации, второй выход блока управления передачей соединен с пятым входом блока управления маркировкой отсчетов и формированием кадров сообщений.

Анализатор информации содержит блоки сокращения избыточности, три элементы ИЛИ, аналого-цифровой преобразователь, сумматор, двоичный счетчик, дешифратор, группу элементов И, элемент И, два элемента задержки, информационный вход каждого блока сокращения избыточности является информационным входом анализатора, первый и второй выход каждого блока сокращения избыточности соединены с соответствующими входами соответственно сумматора и первого элемента ИЛИ, выход сумматора соединен с информационным входом аналого-цифрового преобразователя, выходы дешифратора подключены к входам соответствующих блоков сокращения избыточности, шестому и седьмому выходам анализатора, и входам второго элемента ИЛИ, выход которого соединен с одним входом третьего элемента ИЛИ и управляющим входом группы элементов И, информационные входы и выходы которой соединены соответственно с выходами аналого-цифрового преобразователя и третьими выходами анализатора, объединенные входы аналого-цифрового преобразователя, счетчика и первого элемента задержки являются вторым входом анализатора, установочный вход счетчика является первым входом анализатора, выход первого элемента ИЛИ соединен с вторым выходом анализатора и другим входом третьего элемента ИЛИ, выход которого и выход первого элемента задержки соединены с входами элемента И, выход которого соединен с четвертым выходом анализатора и входом второго элемента задержки, выход которого соединен с первым выходом анализатора, выходы счетчика соединены с пятыми выходами анализатора и входами дешифратора.

Синхронизатор содержит задающий генератор, три делителя частоты следования импульсов, три элемента И, два двоичных счетчика, два дешифратора и триггер, выход задающего генератора соединен с первым входом первого элемента И и входом первого делителя, выход которого соединен с первыми входами второго и третьего элементов И и входом второго делителя, выход которого соединен с первым выходом синхронизатора и входом третьего делителя, выход которого соединен с вторым выходом синхронизатора и установочным входам первого счетчика, счетный вход которого подключен к третьему выходу синхронизатора и выходу первого элемента И, второй вход которого подключен к единичному входу триггера и выходу первого дешифратора, входы которого соединены с выходами первого счетчика, выход триггера соединен с вторым входом второго элемента И, выход которого соединен с нулевым входом триггера, четвертым выходом синхронизатора и установочным входом второго счетчика, выходы которого соединены с входами дешифратора, выход которого соединен с вторым входом третьего элемента И, выход которого соединен со счетным входом второго счетчика и пятым выходом синхронизатора.

Измеритель времени содержит двоичный счетчик, регистр памяти, две группы элементов И, элементы ИЛИ, счетный вход счетчика соединен с первым входом измерителя, выходы счетчика соединены с входами регистра, установочный вход которого подключен к второму входу измерителя, выходы регистра соединены с первыми входами элементов И первой и второй групп, вторые входы элементов И каждой группы объединены и соединены соответственно с третьими и четвертым входами измерителя, выходы одноименных элементов И каждой группы попарно соединены с входами соответствующих элементов ИЛИ, выходы которых соединены с выходами измерителя.

Блок памяти адреса содержит накопительные элементы, элементы И и элемент ИЛИ, одноименные адресные входы накопительных элементов объединены и соединены с третьими входами блока, информационные входы накопительных элементов подключены к вторым входам блока, управляющие входы накопительных элементов объединены и подключены к первому входу блока, установочные входы накопительных элементов объединены и подключены к шине нулевого потенциала выходы накопительных элементов соединены с первыми входами элементов И, вторые входы которых подключены к четвертым входам блока, выходы элементов И соединены с входами элемента ИЛИ, выход которого соединен с выходом блока.

Блок памяти информации содержит группу элементов ИЛИ, накопительные элементы, элементы И, элемент ИЛИ, одноименные адресные входы накопительных элементов объединены и соединены с третьими входами блока, информационные входы накопительных элементов подключены к выходам элементов ИЛИ группы, первые и вторые входы которых подключены соответственно к вторым и пятым входам блока, управляющие входы накопительных элементов объединены и подключены к первому входу блока, установочные входы накопительных элементов объединены и подключены к шине нулевого потенциала, выходы накопительных элементов соединены с первыми входами элементов И, вторые входы которых подключены к четвертым входам блока, выходы элементов И соединены с входами элемента ИЛИ, выход которого соединен с выходом блока.

Блок управления передачей содержит триггер, элемент И и элемент ИЛИ, входы которого подключены к второму и третьему входам блока, выход элемента ИЛИ соединен с первым входом элемента И, выход которого соединен с первым выходом блока, второй вход элемента И подключен к второму выходу блока и выходу, триггера, единичный и нулевой входы которого подключены соответственно к первому и четвертому входам блока.

Блок управления маркировкой отсчетов и формированием кадров сообщений содержит двоичный реверсивный счетчик, дешифратор, регистр сдвига и три элемента И, суммирующий вход счетчика подключен к четвертому входу блока, выходы счетчика соединены с первыми выходами блока и входами дешифратора, выход которого соединен со вторым выходом блока, установочным входом регистра и первыми входами первого и второго элементов И, выход первого элемента И соединен с информационным входом регистра, выходы которого соединены соответствующим образом с третьими и четвертыми выходами блока, выход старшего разряда регистра сдвига, соединен со вторыми входами первого и второго элементов И, выход второго элемента И соединен с вычитающим входом счетчика, установочный вход которого подключен к первому входу блока, входы третьего элемента И соединены с третьим и пятым входами блока, выход третьего элемента И соединен с фазирующим входом регистра, управляющий вход которого подключен к второму, входу блока и объединен с третьим входом второго элемента И.

Вышеперечисленные отличия заявляемого технического решения, по сравнению с известными, обеспечивающие достижение поставленной цели, являются новыми и существенными, так как признаки, сходные с признаками, отличающими заявляемое решение от известных, в известных технических решениях отсутствуют и обеспечивают появление свойств, не совпадающих со свойствами, имеющимися у прототипа.

Таким обрпзом, предлагаемое устройство обладает новизной и существенными отличиями.

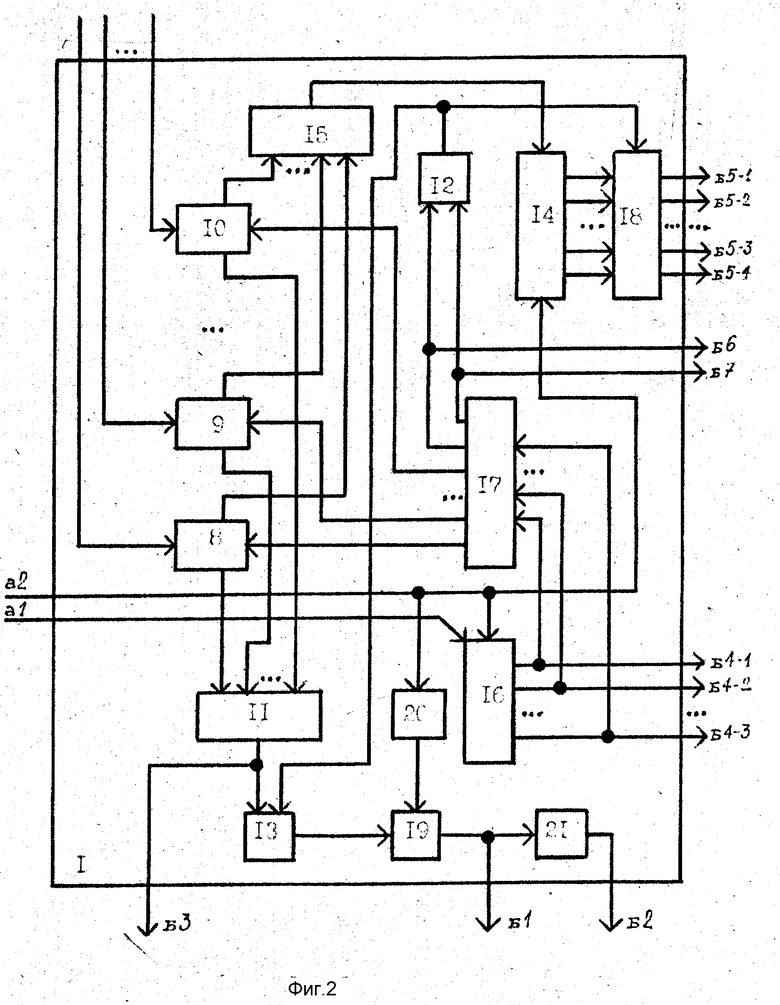

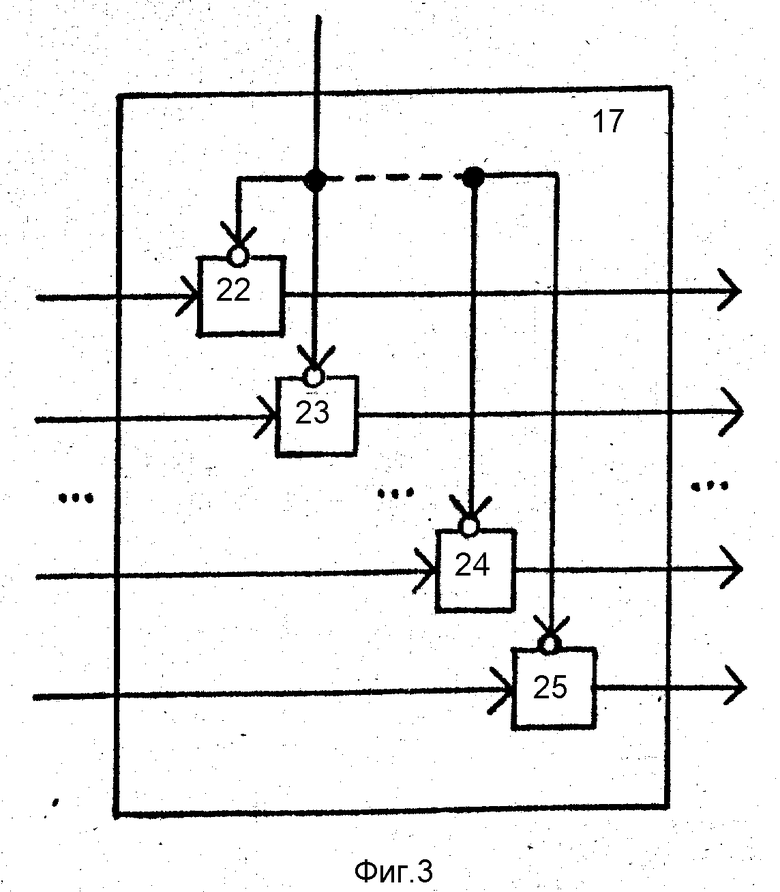

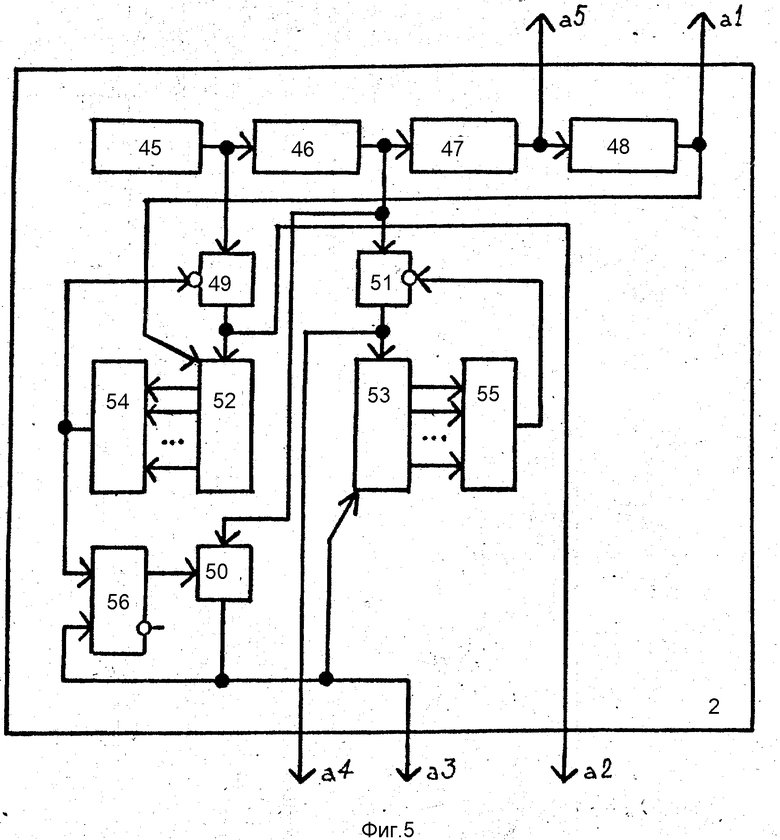

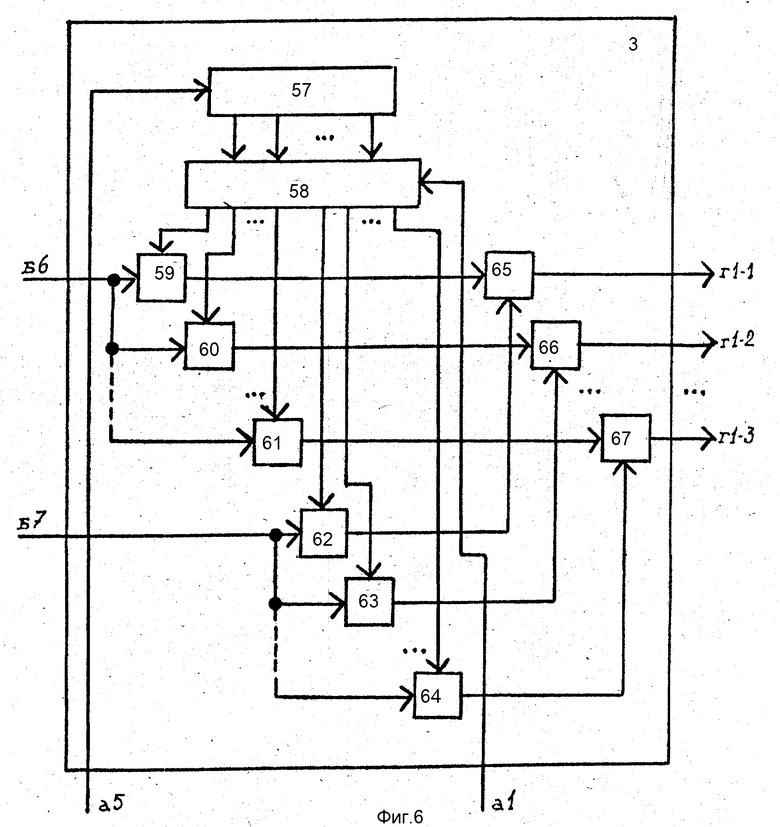

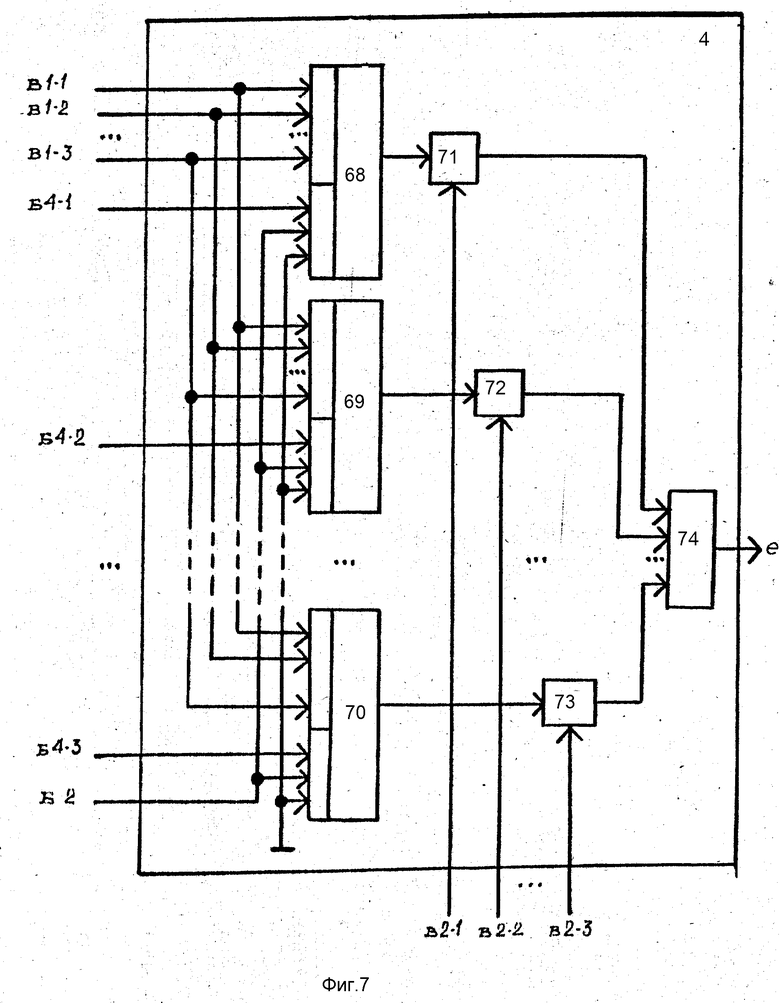

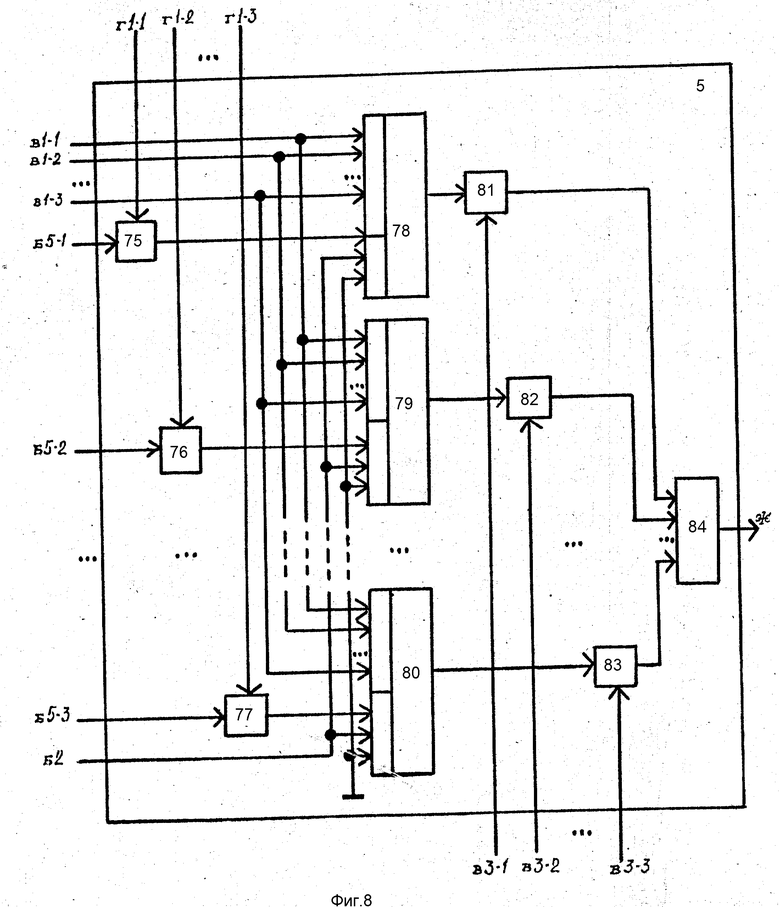

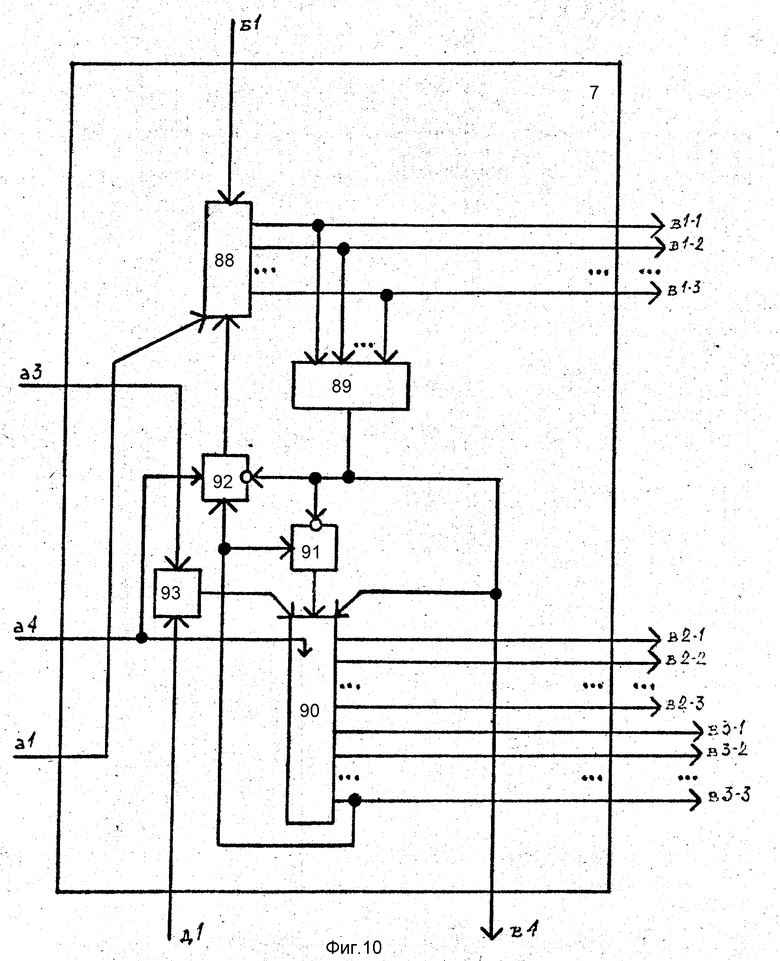

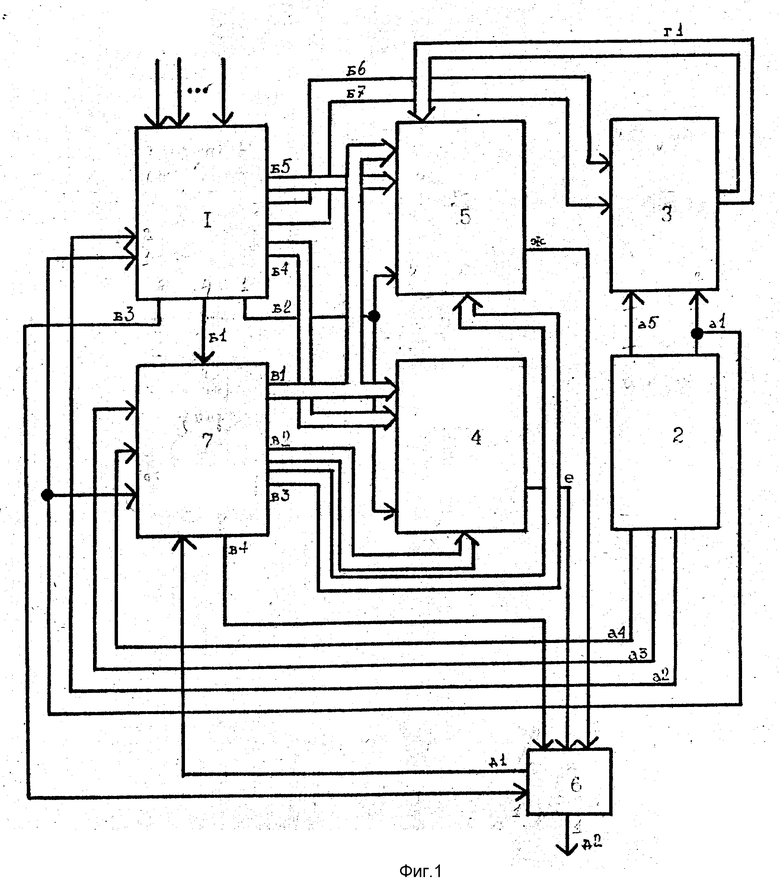

На фиг. 1 дана структурная схема устройства для передачи информации в адаптивных телеметрических системах; на фиг. 2 - функциональная схема анализатора информации; на фиг. 3 - функциональная схема группы элементов И анализатора информации; на фиг. 4 - функциональная схема блока сокращения избыточности анализатора информации; на фиг. 5 - функциональная схема синхронизатора; на фиг. 6 - функциональная схема измерителя времени; на фиг. 7 - функциональная схема блока памяти адреса; на фиг. 8 - функциональная схема блока памяти информации; на фиг. 9 - функциональная схема блока управления передачи; на фиг. 10 - функциональная схема блока управления маркировкой отсчетов и формированием кадров сообщений; на фиг. 11 - временные диаграммы, поясняющие структуру синхросигналов, выдаваемых синхронизатором; на фиг. 12 - структура выходного кадра сообщения предлагаемого устройства; на фиг. 13 - график зависимости коэффициента выигрыша по объему сигналов сообщения предлагаемого устройства по сравнению с устройством-прототипом; на фиг. 14 - графики зависимости среднего числа пораженных параметров (каналов) в кадре сообщений устройства-прототипа и предлагаемого устройства.

Устройство для передачи информации в адаптивных телеметрических системах (фиг. 1) содержит анализатор 1 информации, информационные входы которого являются информационными входами устройства, синхронизатор 2, первый выход которого соединен с первым входом измерителя 3 времени, второй выход синхронизатора 2 соединен с вторым входом измерителя 3 времени и первым входом анализатора 1 информации, второй вход которого подключен к третьему выходу синхронизатора 2, первый выход анализатора 1 информации, соединен с объединенными первыми входами блока 4 памяти адреса и блока 5 памяти информации, второй выход анализатора 1 информации соединен с первым входом блока 6 управления передачей, второй и третий входы которого подключены соответственно к выходам блока 4 памяти адреса и блока 5 памяти информации, вторые входы которого подключены к третьим выходам анализатора 1 информации, первый выход блока 6 управления передачей является выходом устройства, первый, второй, третий и четвертый входы блока 7 управления маркировкой отсчетов и формированием кадров сообщений подключены соответственно к второму, четвертому и пятому выходам синхронизатора 2 и четвертому выходу анализатора 1 информации, пятые выходы которого соединены с вторыми входами блока 4 памяти адреса, третьи входы блока 4 памяти адреса и блока 5 памяти информации объединены и подключены к первым выходах блока 7 управления маркировкой отсчетов и формированием кадров сообщений, второй, третьи и четвертые выходы которого соединены соответственно с четвертым входом блока 6 управления передачей, четвертыми входами блока 4 памяти адреса и четвертыми входами блока 5 памяти информации, пятые входы, которого подключены к выходам измерителя 3 времени, третий и четвертый входы которого подключены соответственно к шестому и пятому выходам анализатора 1 информации, второй выход блока 6 управления передачей соединен с пятым входом блока 7 управления маркировкой отсчетов и формированием кадров сообщений.

Анализатор 1 информации (фиг. 2) содержит блоки 8 - 10 сокращения избыточности, три элемента 11 - 13 ИЛИ, аналого-цифровой преобразователь 14, сумматор 15, двоичный счетчик 16, дешифратор 17, группу 18 элементов И, элемент И 19, два 20 и 21 элемента задержки, информационный вход каждого блока 8 - 10 сокращения избыточности является информационным входом анализатора 1, первый и второй выход каждого блока 8 - 10 сокращения избыточности соединены с соответствующими входами соответственно сумматора 15 и первого 11 элемента ИЛИ, выход сумматора 15 соединен с информационным входом аналого-цифрового преобразователя 14, выходы дешифратора 17 подключены к входам соответствующих блоков 8 - 10 сокращения избыточности, шестому и седьмому выходам анализатора 1, и входам второго 12 элемента ИЛИ, выход которого соединен с одним входом третьего 13 элемента ИЛИ и управляющим входом группы 18 элементов И, информационные входы и выходы которой соединены соответственно с выходами аналого-цифрового преобразователя 14 и третьими выходами анализатора 1, объединенные входы аналого-цифрового преобразователя 14, счетчика 16 и первого 20 элемента задержки являются вторым входом анализатора 1, установочный вход счетчика 16 является первым входом анализатора 1, выход первого 11 элемента ИЛИ соединен с вторым выходом анализатора 1 и другим входом третьего 13 элемента ИЛИ, выход которого и выход первого 20 элемента задержки соединены с входами элемента И 19, выход которого соединен с четвертым выходом анализатора 1 и входом второго 21 элемента задержки, выход которого соединен с первым выходом анализатора 1, выходы счетчика 16 соединены с пятыми выходами анализатора 1 и входами дешифратора 17.

Группа 18 элементов И анализатора 1 информации (фиг. 3) содержит элементы И 22 - 25, инверсные входы которых объединены и подключены к управляющему входу группы 18, прямые входы и выходы элементов И 22 - 25 соединены соответственно с входами и выходами группы 18.

Блок 8 (9 - 10) сокращения избыточности анализатора 1 информации (фиг. 4) содержит узел 26 сравнения, формирователь 27 модели сигнала, ключ 28, элемент 29 управления. Узел 26 содержит элемент 30 сравнения и пороговый элемент 31, формирователь 27 - элемент 32 памяти, ключи 33 и 34, элемент 35 задержки, элемент 29 - триггеры 36 и 37, элементы И 38 и 39, элемент 40 задержки, формирователи 41 - 43 импульсов и элемент НЕ 44.

Синхронизатор 2 (фиг. 5) содержит задающий генератор 45, три 46 - 48 делителя частоты следования импульсов, три 49 - 51 элемента И, два 52 и 53 двоичных счетчика, два 54 и 55 дешифратора и триггер 55, выход задающего генератора 45 соединен с первым входом первого 49 элемента И и входом первого 46 делителя, выход которого соединен с первыми входами второго 50 и третьего 51 элементов И и входом второго 47 делителя, выход которого соединен с первым выходом синхронизатора 2 и входом третьего 48 делителя, выход которого соединен с вторым выходом синхронизатора 2 и установочным входом первого 52 счетчика, счетный вход которого подключен к третьему выходу синхронизатора 2 и выходу первого 49 элемента И, второй вход которого подключен к единичному входу триггера 56 и выходу первого 54 дешифратора, входы которого соединены с выходами первого 52 счетчика, выход триггера 56 соединен с вторым входом второго 50 элемента И, выход которого соединен с нулевым входом триггера 56, четвертым выходом синхронизатора 2 и установочным входом второго 53 счетчика, выходы которого соединены входами дешифратора 55, выход которого соединен с вторым входом третьего 51 элемента И, выход которого соединен со счетным входом второго 53 счетчика и пятым выходом синхронизатора 2.

Измеритель 3 времени (фиг. 6) содержит двоичный счетчик 57, регистр 58 памяти, две 59 - 61 и 62 - 64 группы элементов И, элементы ИЛИ 65 - 67, счетный вход счетчика 57 соединен с первым входом измерителя 3, выходы счетчика 57 соединены с входами регистра 58, установочный вход которого подключен к второму входу измерителя 3, выходы регистра 58 соединены с первыми входами элементов И первой 59 - 61 и второй 62 - 64 групп, вторые входы элементов И каждой группы объединены и соединены соответственно с третьим и четвертым входами измерителя 3, выходы одноименных 59 и 62, 60 и 61 - 63 и 64 элементов И каждой группы попарно соединены с входами соответствующих 65 - 67 элементов ИЛИ, выходы которых соединены с выходами измерителя 3.

Блок 4 памяти адреса (фиг. 7) содержит накопительные элементы 68 - 70, элементы И 71 - 73 и элемент ИЛИ 74, одноименные адресные входы накопительных элементов 68 - 70 объединены и соединены с третьими входами блока 4, информационные входы накопительных элементов 68 - 70 подключены к вторым входам блока 4, управляющие входы накопительных элементов 68 - 70 объединены и подключены к первому входу блока 4, установочные входы накопительных элементов 68 - 70 объединены и подключены к шине нулевого потенциала, выходы накопительных элементов 68 - 70 соединены с первыми входами элементов И 71 - 73, вторые входы которых подключены к четвертым входам блока 4, выходы элементов И 71 - 73 соединены с входами элемента ИЛИ 74, выход которого соединен с выходом блока 4.

Блок 5 памяти информации (фиг. 8) содержит группу элементов ИЛИ 75 - 77, накопительные элементы 78 - 80, элементы И 81 - 83, элемент ИЛИ 84, одноименные адресные входы накопительных элементов 78 - 80 объединены и соединены с третьими входами блока 5, информационные входы накопительных элементов 78 - 80 подключены к выходам элементов ИЛИ 75 - 77 группы, первые и вторые входы которых подключены соответственно к вторым и пятым входам блока 5, управляющие входы накопительных элементов 78 - 80 объединены и подключены к первому входу блока 5, установочные входы накопительных элементов 78 - 80 объединены и подключены к шине нулевого потенциала выходы накопительных элементов 78 - 80, соединены с первыми входами элементов И 81 - 83, вторые входы которых подключены к четвертым входам блока 5, выходы элементов И 81 - 83 соединены с входами элемента ИЛИ 84, выход которого соединен с выходом блока 5.

Блок 6 управления (фиг. 9) передачей содержит триггер 85, элемент И 86 и элемент ИЛИ 87, входы которого подключены к второму и третьему входам блока 6, выход элемента ИЛИ 87 соединен с первым входом элемента И 86, выход которого соединен с первым выходом блока 6, второй вход элемента И 86 подключен к второму выходу блока 6 и выходу триггера 85, единичный и нулевой входы которого подключены соответственно к первому и четвертому входам блока 6.

Блок 7 управления маркировкой отсчетов и формированием кадров сообщений (фиг. 10) содержит двоичный реверсивный счетчик 88, дешифратор 89, регистр 90 сдвига и три 91 - 93 элемента И, суммирующий вход счетчика 88 подключен к четвертому входу блока 7, выходы счетчика 83 соединены с первыми выходами блока 7 и входами дешифратора 89, выход которого соединен с вторым выходом блока 7, установочным входом регистра 90 и первыми входами первого 91 и второго 92 элементов И, выход первого 91 элемента И соединен с информационным входом регистра 90, выходы которого соединены соответствующим образом с третьими и четвертыми выходами блока 7, выход старшего разряда регистра 90 сдвига, соединен с вторыми входами первого 91 и второго 92 элементов И, выход второго элемента И 92 соединен с вычитающим входом счетчика 88, установочный вход которого подключен к первому входу блока 7, входы третьего 93 элемента И соединены с третьим и пятым входами блока 7, выход третьего 93 элемента И соединен с фазирующим входом регистра 90, управляющий вход которого подключен к второму входу блока 7 и объединен с третьим входом второго 92 элемента И.

Работает предлагаемое устройство следующим образом.

С выхода синхронизатора 2 на входы анализатора 1 информации, измерителя 3 времени и блока 7 управления маркировкой отсчетов и формированием кадров сообщений поступает сигнал (а1) начала цикла. Затем под действием тактовых импульсов (а2), поступающих от синхронизатора 2, анализатор 1 информации поочередно опрашивает все датчики. Каждый i-ый отсчет каждого параметра сравнивается с (i + 1) отсчетом того же канала. Если величина i-ого отсчета параметра отличается от значения (i + 1) отсчета на величину, превышающую заданную разность их значений, то указанный (i + 1) отсчет считается существенным и подлежащим передаче. Если разность величин отсчетов не превосходит заданной величины, то отсчет считается несущественным и неподлежащим передаче.

В процессе поочередной проверки отсчетов всех параметров анализатор 1 формирует сигнал (б1) наличия существенных отсчетов параметров и отсчетов времени, задержанный сигнал (б2) наличия существенных отсчетов параметров и отсчетов времени и сигнал (б3) наличия существенных отсчетов параметров. Под действием импульсов (б1) блок 7 формирует условные адреса существенных отсчетов параметров в кадре. Сигналы (в1) условных адресов подаются на входы блока 4 памяти адреса и блока 5 памяти информации. Под действием импульсов (б2) по условному адресу (в1) в блок 4 записывается истинный адрес (б4) существенного отсчета, а в блок 5 значение (б5) данного существенного отсчета.

Таким образом кодовые группы, соответствующие значениям адреса существенных отсчетов параметров, записываются в порядке их поступления в блок 4 памяти адреса непосредственно одна за другой, а кодовые группы, соответствующие значениям существенных отсчетов параметров, записываются в порядке их поступления в блок 5 памяти информации также непосредственно одна за другой.

После опроса всех датчиков в анализаторе 1 под действием сигнала (б6) опроса первого полуслова времени и сигнала (б7) опроса второго полуслова времени кодовые группы значения времени, соответствующего времени поступления сигнала (а1) начала цикла в измеритель 3 времени, поступают из измерителя 3 времени (г1) в блок 5 и аналогично существенным отсчетам параметров, записываются в блок 5 памяти информации, а соответствующие им кодовые группы значений адресов записываются в блок 4 памяти адреса.

Затем синхронизатор 2 выдает на вход блока 7 управления маркировкой отсчетов и формированием кадров сообщений кадровый сигнал (а3), который переводит блок 7 в режим считывания информации из блоков 4 и 5, если в цикле опроса анализатором 1 датчиков был зафиксирован существенный отсчет хотя бы одного параметра. Признаком наличия существенных отсчетов в анализаторе 1 служит сигнал (д1) высокого уровня, формируемый блоком 6 управления передачей под действием сигнала (импульсов) (б3) наличия существенных отсчетов параметров, выдаваемого анализатором 1.

Под действием тактовых импульсов (а4), поступающих на вход блока 7 непосредственно после поступления в блок 7 кадрового сигнала (а3), блок 7 формирует серии импульсов опроса (в2) блока 4 памяти адреса и серии импульсов опроса (в3) блока 5 памяти информации. Синхронно с сериями импульсов спроса с выхода блока 7 на входы блоков 4 и 5 подаются сигналы (в1) кодовых групп соответствующих условных адресов, по которым производится считывание ранее записанной в блоки 4 и 5 информации.

Считываемые значения адреса с выхода (е) блока 4 и значения отсчетов времени или существенных отсчетов параметров с выхода (ж) блока 5 поступают на входы блока 6 управления передачей, где объединяются и с выхода (д2) блока 6 поступают на выход устройства. После окончания считывания информации, ранее записанной в блоки 4 и 5, блок 7 выдает сигнал (в4) окончания считывания, который устанавливает в блоке 6 запрет на выдачу информации на выход устройства.

С выдачей синхронизатором 2 сигнала (а1) начала цикла цикл работы устройства повторяется.

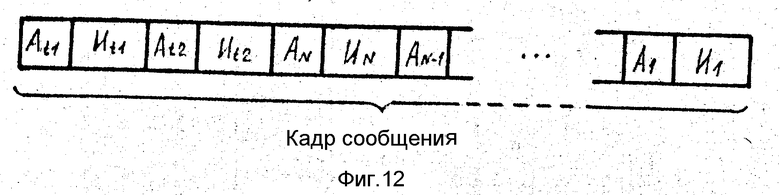

Выходной кадр сообщения (фиг. 11, д2, 12) устройства для передачи информации содержит: А - сигналы кодовых групп адресов существенных отсчетов параметров и отсчетов времени, И - сигналы кодовых групп значений существенных отсчетов параметров и отсчетов времени (Аt1, Аt2 - адреса первого и второго полуслов отсчета времени; АN, АN-1, ..., А1 - адреса отсчетов N-ого, (N - 1) - 1-ого параметров; Иt1, Иt2 - значения отсчетов первого и второго полуслов отсчета времени; ИN - И1 - значения отсчетов N-ого,..., 1-ого параметров).

В кадрах, не содержащих существенных отсчетов ни одного параметра, блок 6 запрещает выдачу сигналов сообщения на выход (д2) устройства.

Анализатор 1 работает следующим образом.

Сигнал начала цикла с первого (а1) входа анализатора 1 поступает на фазирующий вход счетчика 15 и устанавливают его в исходное состояние. Сигналы считывания информации (опроса датчиков) поступают с второго (а2) входа анализатора 1 на суммирующий вход счетчика 16, вход элемента 20 задержи и фазирующий вход аналого-цифрового преобразователя (АЦП) 14. Под действием этих импульсов с выходов дешифратора 17 последовательно подается высокий потенциал на входы блоков 8 - 10 и производит их опрос. При наличии в блоке 8 (9 - 10) существенного отсчета блок 8 (9 - 10) через сумматор 15 выдают значение (амплитуду) существенного отсчета параметра (сигнала от датчика, подключенного к входу блока 8) на вход АЦП и высокий потенциал через элемент ИЛИ 11 на выход (б3) анализатора 1 и через элемент ИЛИ 13 на вход элемента И 19.

При наличии в блоке 8 (9 - 10) несущественного отсчета блок 8 (9 - 10) через сумматор 15 на вход АЦП 14 и через элемент ИЛИ 11 на выход (б3) анализатора 1 выдает нулевые потенциалы. Задержанные импульсы элементом 20 задержки на время, достаточное для срабатывания АЦП 14, с выхода элемента 20 поступают на вход элемента И 13 и при наличии высокого потенциала на другом его входе проходят через элемент И 19 на выход (б1) анализатора 1 и на вход элемента 21 задержки. Импульсы с выхода элемента 21 задержки поступают на выход (б2) анализатора 1.

АЦП 14 преобразует сигналы, соответствующие значениям существенных отсчетов измеряемых параметров и поступающие с выхода сумматора 15 на вход АЦП 14, в двоичный код. Сигналы, соответствующие разрядам двоичного кода с выхода АЦП 14 через группу 18 элементов И, поступают на выход (б5; б5-1, - б5-3) анализатора 1.

После опроса всех датчиков (блока 10 сокращения избыточности в анализаторе 1 под действием N-го и (N + 1) тактовых импульсов формируются импульсы спроса первого (б6) и второго (б7) полуслов отсчета времени, которые выдаются на выходы (б6) и (б7) анализатора 1, через элементы ИЛИ 12 и элемент ИЛИ 13 подаются на вход элемента И 19 и с выхода элемента ИЛИ 12 подаются на вход группы 18 элементов И (фиг. 3), благодаря чему запрещается выдача сигналов с выхода АЦП 14 через группу 18 элементов И на выходы (б5: б5-1, - б5-3) анализатора 1. По мере спроса блоков 8(9 - 10) счетчик 16 формирует кодовые группы, соответствующие номерам опрашиваемых параметров. Сигналы разрядов двоичного кода с выходов считчика 16 поступают на выходы (б4: б4-1, - б4-3) анализатора 1. После выдачи импульса опроса с выхода (б7) цикл работы анализатора 1 заканчивается. С приходом сигнала начала цикла на вход (а1) анализатора 1 цикл работы анализатора 1 повторяется.

Работает блок 8(9 - 10) (фиг. 4) следующим образом.

Сигнал от датчика поступает на первый вход элемента 30 и ключа 34. На второй вход элемента 30 сравнения поступает сигнал с выхода элемента 32. Сигнал с выхода элемента 32 имеет амплитуду (уровень), соответствующую амплитуде последнего переданного существенного отсчета измеряемого параметра. По достижении сигналом с выхода элемента 30 сравнения величины, превышающей порог срабатывания порогового элемента 31 (порог срабатывания устанавливается исходя из требуемой погрешности аппроксимации измеряемого сигнала), последний выдает сигнал, который, пройдя через элемент И 38, поступает на вход формирователя 41. Формирователь 41 по переднему фронту сигнала высокого уровня, поступившего на его вход, формирует импульс, который с выхода формирователя 41 поступает на вход триггера 36, управляющий вход ключа 33 и вход элемента 35 задержки.

При поступлении импульса на вход триггера 36 последний опрокидывается и на его выходе, соединенном с входом элемента И 38, устанавливается нулевой потенциал, тем самым запрещается прохождение сигнала с выхода элемента И 30 через элемент И 38. При поступлении импульса на управляющий вход ключа 33 последний открывается и элемент 32 через ключ 33 сбрасывается (например, конденсатор памяти разряжается). После сброса элемента 32 с выхода элемента 35 задержки на управляющий вход ключа 34 поступает импульс, который открывает ключ 34, и информация о текущем значении параметра записывается в элемент 32 (например, конденсатор памяти через открытый ключ заряжается до текущего значения измеряемого сигнала, т.е. до уровня значения нового существенного отсчета). Одновременно импульс с выхода элемента 35 поступает на вход элемента 40. Импульс с выхода элемента 40 поступает на входы триггеров 36 и 37. Триггер 36 возвращается в исходное состояние, триггер 37 опрокидывается. На выходе триггера 37 устанавливается нулевой потенциал, тем самым запрещается прохождение сигнала от блока 26 через элемент И 38 до тех пор, пока значение нового существенного отсчета не считается из блока 8 (9 - 10). Одновременно на выходе триггера 37 устанавливается высокий потенциал, который разрешает прохождение импульсов спроса блока 8 (9 - 10), поступающих на вход формирователя 42. Первых импульс опроса, поступивший на вход формирователя 42 после опрокидывания триггера 37, обостряется по переднему фронту Формирователем 42, проходит через элемент И 39 и поступает на вход формирователя 43, который расширяет входной импульс до длительности импульсов, поступающих на вход формирователя 42. Широкий импульс с выхода формирователя 43 поступает на вход элемента НЕ 44, управляющий вход ключа 28 и выход блока 8 (9 - 10) в качестве сигнала признака наличия существенного отсчета. Ключ 28 открываются и сигнал, соответствующий уровню существенного отсчета, с выхода элемента 32 памяти выдается на выход блока 8(9 - 10). По окончание импульса, действующего на входе элемента НЕ 44, на выходе элемента НЕ 44 устанавливается высокий потенциал, фронт нарастания которого возвращает триггер 37 в исходное состояние.

После этого цикл работы блока 8(9 - 10) повторяется.

Работает синхронизатор 2 (фиг. 5) следующим образом.

Задающий генератор 45 формирует тактовые импульсы, которые с выхода генератора 45 поступают на вход делителя 46 частоты следования импульсов и на вход первого 49 элемента И. Импульсы с выхода первого 46 делителя частоты поступают на вход второго 47 делителя частоты и на вход третьего 51 элемента И. Импульсы с выхода второго 47 делителя частоты поступают на первый выход (а5) синхронизатора 2 и на вход третьего 48 делителя частоты. С выхода третьего 48 делителя частоты на второй выход (а1) синхронизатора 2 и на фазирующий вход счетчика 52 поступают импульсы - сигналы начала цикла.

Под действием сигнала начала цикла счетчик 52 устанавливается в нулевое состояние (сбрасывается). На выходе дешифратора 54 устанавливается нулевой потенциал, который разрешает прохождение импульсов с выхода генератора 45 через элемент И 49. Импульсы с выхода элемента И 49 поступают на третий выход (а2) синхронизатора 2 и на суммирующий вход счетчика 52. Счетчик 52 ведет счет числа импульсов, выданных синхронизатором на третий выход (а2). После выдачи (N + З) импульсов на выход (а2) срабатывает дешифратор 54, который дешифрует заданное двоичное число (N + 3), установившееся в счетчике 52. Сигнал высокого уровня с выхода дешифратора 54 запрещают дальнейшее прохождение импульсов с выхода генератора 45 через элемент И 49 и опрокидывает триггер 56. На выходе триггера 56, соединенном с входом элемента И 50, устанавливается высокий потенциал, который разрешает прохождение импульсов с выхода делителя 45 через элемент И 50. Первый же прошедший через элемент И 50 импульс возвращает триггер 56 в исходное состояние, фазирует счетчик 52 и поступает на четвертый выход (а3) синхронизатора 2. Дальнейшее прохождение импульсов через элемент И 50 запрещается. Сигнал низкого уровня с выхода дешифратора 55 поступает на вход элемента И 51 и разрешает прохождение импульсов с выхода делителя 46 через элемент И 51 на пятый выход (а4) синхронизатора 2 и суммирующий вход счетчика 53. Счетчик 53 ведет счет числа импульсов, поступивших на пятый выход (а4) синхронизатора 2. После выдачи [(N + 2)(na + nu)] импульсов в счетчике 53 оказывается зафиксировано соответствующее двоичное число, которое дешифруется дешифратором 55. На выходе дешифратора 55 устанавливается высокий потенциал, который запрещает дальнейшее прохождение импульсов через элемент И 51. На этом цикл работы синхронизатора 2 заканчивается.

С выдачей делителем 45 сигнала (импульса) начала цикла цикл работы синхронизатора 2 повторяется.

Работает измеритель 3 времени (фиг. 6) следующим образом.

Счетчик 57 ведет счет импульсов, поступающих на его суммирующий вход (а5). Обнуление счетчика 57 происходит по его переполнению. Цикл работы измерителя 3 начинается по приходу на управляющий вход регистра 58 с входа (а1) измерителя 3 сигнала (импульса) начала цикла. При этом в регистре 58 записывается кодовая комбинация, соответствующая числу импульсов, сосчитанных счетчиком 57 с момента его последнего обнуления до момента прихода импульса на управляющий вход регистра 58. Затем последовательно на входы (б6) и (б7) поступают сигналы (импульсы) считывания информации из измерителя 3. Под действием этих сигналов, сигналы кодовой группы, записанной ранее в регистр 58, считываются на элементах И 59 - 61 и 62 - 64 и через элементы ИЛИ 65 - 67 выдаются на выход (г1: г1-1 - г-3) измерителя 3 времени.

С приходом на управляющий вход регистра 58 импульса цикл работы измерителя 3 времени повторяется.

Работает блок 4 памяти адреса (фиг. 7) следующим образом.

Под действием импульсов, поступавших на управляющие входы (б2) накопительных элементов 68 - 70, производится запись информации (1 или О) в зависимости от уровней сигналов, поступающих на их информационные входы (б4: б4-1, - б4-2) (информация (1 или О) разрядов, составляющих код (значение) адреса существенного отсчета параметра), в ячейки памяти с адресами, определяемыми уровнями сигналов, действующих на адресных входах (в1: в1-1, - в1-3) элементов 68 - 70.

По окончании записи информации в блок 4 производится ее считывание из блока 4. Считывание производится путем последовательного опроса выходов накопительных элементов 68 - 70 через элементы И 71 - 73 импульсами с входов (в2: в2-1, - в2-3). Разряды (1 и О), составляющие код (значение) адреса существенного отсчета параметра, с выходов элементов И 71 - 73 через элемент ИЛИ 74 поступают на выход (е) блока 4. Считывание производится из ячеек памяти с адресами, определяемыми уровнями сигналов, действующих на адресных входах (в1: в1-1, - в1-3) элементов 68 - 70.

Работает блок 5 памяти информации (фиг. 8) следующим образом.

Под действием импульсов, поступающих на управляющие входы (б2) накопительных элементов 78 - 80, производится запись информации (1 или 0) в зависимости от уровней сигналов, поступающих на их информационные входы через элементы ИЛИ 75 - 77 с входов (б5: б5-1, - б5-3) или (г1: г1-1, - г1-3) (информация (1 или 0) разрядов, составляющих код (значение) существенного отсчета параметра - входы (б5: б5-1, - б5-3) и код (значение) отсчета времени - входы (г1: г1-1, - г1-3), в ячейки памяти с адресами, определяемыми уровнями сигналов, действующих на адресных входах (в1: в1-1, - в1-3) элементов 78 - 80.

По окончании записи информации в блок 5 производится ее считывание из блока 5. Считывание производится путем последовательного опроса выходов накопительных элементов 78 - 80 через элементы И 81 - 83 импульсами с входов (б3: б3-1, - б3-3). Разряды (1 или 0), составляющие код (значение) отсчета времени, с выходов элементов И 81 - 83 через элемент ИЛИ 84 поступают на выход (ж) блока 5. Считывание производится из ячеек памяти с адресами, определяемыми уровнями сигналов, действующих на адресных входах (в1: в1-1, - в1-3) элементов 78 - 80.

Работает блок 6 управления передачей (фиг. 9) следующим образом.

Сигнал (импульс) с входа (в4) блока 6 устанавливает триггер 85 в нулевое состояние. На выходе триггера 85, соединенном с входом элемента И 86 и выходом (д1) блока 6, устанавливается нулевой потенциал, тем самым запрещается прохождение сигналов с другого входа элемента И 86 через последний на выход (д2) блока 6. Если после сигнала начала цикла в анализаторе 1 информации не выделяется ни одного существенного отсчета измеряемых параметров, то сигналы на его выход (б3) анализатора 1 не проходят и соответственно не поступают через вход (б2) блока 6 на единичный вход триггера 85. Если после сигнала начала цикла в анализаторе 1 информации выделяется хотя бы один существенный отсчет измеряемых параметров, то на выход (б3) анализатора 1 выдается импульс, который через вход (б3) блока 6 поступает на единичный вход триггера 85. Триггер 85 опрокидывается и на его единичном выходе, соединенном с входом элемента И 86 и выходом (д1) блока 6, устанавливается высокий потенциал, чем разрешается прохождение сигналов через элемент И 86 с входов (е) и (ж) блока 5 на выход (д2) блока 6. С приходом импульса на вход (в4) блока 6 цикл его работы повторяется.

Работает блок 7 управления маркировкой отсчетов и формированием кадров сообщений (фиг. 10) следующим образом.

На вход (а1) блока 7 поступает от синхронизатора 2 сигнал (импульс) начала цикла, который проходит на установочный вход счетчика 88 и устанавливает его в нулевое состояние. Затем, по мере опроса анализатора 1, на вход (б1) блока 7 поступают сигналы (импульсы), характеризующие наличие существенных отсчетов параметров и отсчетов времени. Импульсы с входа (б1) проходят на суммирующий вход счетчика 88. Счетчик 88 ведет подсчет в двоичном коде числа импульсов, поступивших на его счетный вход. Таким образом формируется условный адрес существенных отсчетов параметров и отсчетов времени, значение истинных адресов и значений которых записываются в блоки памяти 4 и 5. Коды условных адресов выдаются на выход (в1: в1-1, - в1-3) блока 7. После окончания опроса анализатора 1 на вход (а3) блока 7 поступает от синхронизатора 2 кадровый сигнал (импульс), который при наличии высокого потенциала на входе (д1) блока 7 проходит через элемент И 93 на фазирующий вход регистра 90 сдвига. В регистр записываются кодовая комбинация 100 - 0. Затем на вход (а4) блока 7 поступают от синхронизатора 2 тактовые импульсы, под действием которых в регистре 90 происходит сдвиг ранее записанной кодовой комбинации. На выходы (в2: в2-1, - в2-3) и (в3: в3-1, - в3-3) блока 7 с выходов регистра 90 выдаются стробы (импульсы) опроса блоков 4 и 5. После выдачи строба опроса с выхода (в3-3) блока 7 очередным тактовым импульсом с входа (а4) блока 7, пришедшим на вход элемента И 92 и синхронизирующий вход регистра 90 уменьшается значение двоичного кода в счетчике 88 и возобновляется запись в регистр 90 кодовой комбинации 100 - 0. После этого цикл выдачи стробов опроса блоков 4 и 5 с выходов (в2: в2-1, - в2-3) и (в3: в3-1, - в3-3) продолжается. После установления в счетчике 88 кодовой комбинации 00 - 0 срабатывает дешифратор 89, который выдает высокий потенциал который поступает на выход (в4) блока 7, запрещает прохождение сигналов через элементы И 91 и 92, а фронт нарастания уровня сигнала с выхода дешифратора 89 сбрасывает регистр 90 в нулевое состояние 00 - 0. С поступлением на вход (а4) блока 7 сигнала начала цикла от синхронизатора 2 цикл работы блока 7 повторяется.

Основные параметры работы предлагаемого устройства определяются следующими соотношениями:

Длительность одного цикла работы устройства

T ≥ Ta + T4 + Tc

где T ≤ T0 - период контроля (опроса) одного параметра (датчика);

- период контроля (опроса) одного параметра (датчика);

Fm - максимальная граничная частота спектра самого активного параметра, контролируемого устройством;

Ta = (N + 3)•T2 - время (длительность) анализа (опроса) всех параметров и времени анализатором 1;

F2 = 1/T2 - частота следования импульсов с выхода (а2) синхронизатора 2;

N - число контролируемых параметров устройством;

Tc = (N + 2)(na + nu)•T4 - максимальное время (длительность) передачи кадра сообщения, выдаваемого устройством;

F4 = 1/T4 - частота следования импульсов с выхода (а4) синхронизатора 2;

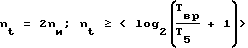

na ≥ <log2(N + 2)> - число разрядов кодовой группы адреса одного отсчета параметров и времени;

<. . . > - операция округления до ближайшего целого сверху (например, <3,01> = 4);

nu - число разрядов кодовой группы значения отсчета (существенного отсчета) параметров и времени;

число разрядов кодовой группы значения отсчета времени (двух полуслов отсчета времени);

Tвр - максимальный мерный временной интервал однозначного измерения измерителем 3 времени;

T5 = 1/F5 - необходимая точность измерения времени;

F5 - частота импульсов с выхода (а5) синхронизатора 2.

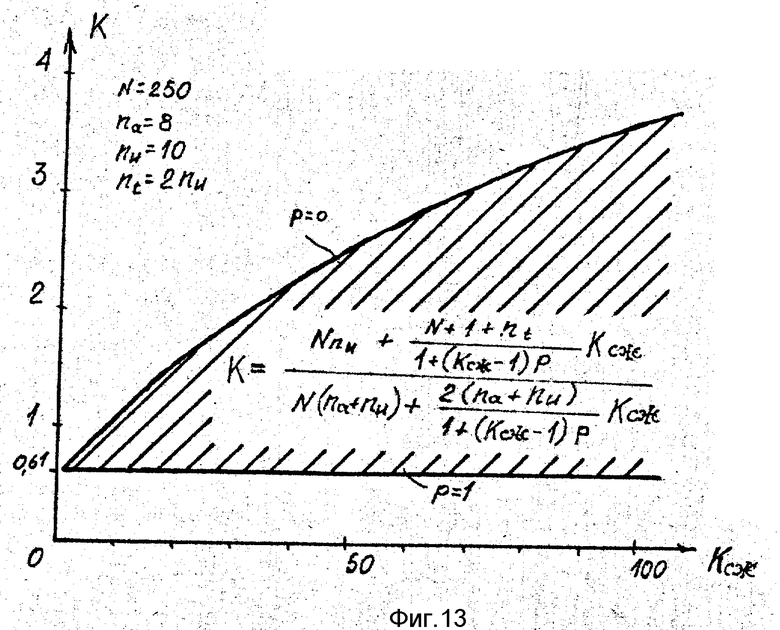

Для иллюстрации преимуществ предлагаемого устройства по сравнению с устройством-прототипом найдем зависимость коэффициента выигрыша предлагаемого устройства по отношению к устройству-прототипу по числу символов сообщения (собственно реальных коэффициентов сжатия объема сигналов сообщения) от коэффициента сжатия информации.

Воспользуемся соотношениями:

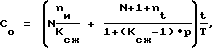

объем сообщения устройства-прототипа

где Kсж - средний коэффициент сжатия информации;

P - вероятность того, что при изменении уровня любого измеряемого параметра одновременно изменяются уровни остальных измеряемых параметров (коэффициент коррекции измеряемых параметров);

t - интервал измерения.

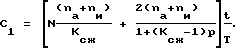

объем сообщения предлагаемого устройства

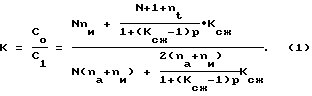

Коэффициент выигрыша по числу символов сообщения предлагаемого устройства по сравнению с устройством-прототипом

В качестве конкретного примера на фиг. 13 приведен график зависимости коэффициента выигрыша согласно формулы (1) при нижней границе K = K(Kсж, p = 0) и верхней границе K = K(Kсж, p = 1) и значениях N = 250, na = 8, nu = 10, nt = 2nu. График (фиг. 13) наглядно иллюстрирует преимущество предлагаемого устройства по сравнению с известным (устройством-прототипом).

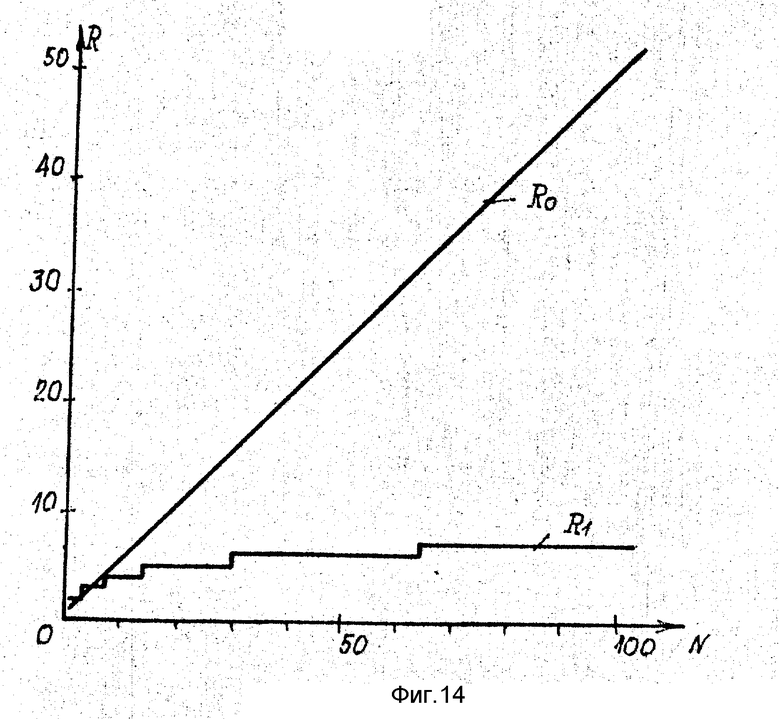

Для иллюстрации преимуществ по достоверности передачи информации предлагаемого устройства по сравнению с устройством-прототипом оценим помехоустойчивость структур их кадров сообщений.

Помехоустойчивость структуры кадра, сообщения характеризуется чувствительностью к искажению составляющих кадра сообщения: адресной части, информационной части и временной части.

Появление ошибки в адресной части приводит к потере отсчета для данного параметра и появлению ложного отсчета для параметра, адрес которого совпадает с трансформированным адресом.

Появление ошибки в информационной части приводит к искажению значения кода отсчета данного параметра.

Появление ошибки во временной части приводит к неправильному расположению отсчета параметра на временной оси.

Помехоустойчивость структур кадров сообщений предлагаемого устройства и устройства-прототипа, в части касающейся информационной и временной частей одинакова, так как суммарное количество разрядов кода значений отсчетов всех параметров и суммарное количество разрядов кода отсчетов времени соответственно в кадрах сообщений одинаково.

Помехоустойчивость структур кадров сообщений предлагаемого устройства и устройства-прототипа различна, так как суммарное количество разрядов адресов параметров в кадрах сообщений различно, а также адресные части имеют различную структуру.

В качестве меры сравнительной помехоустойчивости структур рассматриваемых кадров сообщений в части касающейся адресных частей введем показатель "число пораженных параметров (каналов)" как сумму числа параметров, в которых потеряны отсчеты, и числа параметров, в которых появились ложные отсчеты.

Для полных кадров сообщений, т.е. при Kсж = 1, при интенсивности помех, вызывающих искажение только одного разряда адресной части в кадре сообщения устройства-прототипа, среднее число пораженных параметров в кадре сообщения:

для устройства-прототипа

для предлагаемого устройства

R1 = 1,5 <log2(N + 2)> (3)

На фиг. 14 приведены графики зависимостей среднего числа пораженных параметров (каналов) в кадре сообщения устройства-прототипа (2) и предлагаемого устройства (3), которые наглядно иллюстрируют преимущества по достоверности передачи информации предлагаемого устройства по сравнению с устройством-прототипом из-за более высокой помехоустойчивости структуры кадра сообщения предлагаемого устройства.

Как видно из вышеизложенного, заявляемое устройство для передачи информации в адаптивных телеметрических системах обладает новизной, существенными отличиями и при использовании дает положительный эффект.

Экономический эффект может быть получен как следствие от использования предлагаемого технического решения в связи с повышением достоверности передачи информации и информативности устройства, что позволяет сократить время, повысить качество проведения исследований и испытаний различных объектов, сократить количество испытываемых объектов, необходимых для набора статистики их надежности и правильности функционирования при требуемой достоверности полученных результатов.

Изобретение относится к информационно-измерительной технике и может быть использовано в адаптивно-адресных телеметрических системах. Технический результат заключается в повышении достоверности передачи информации, который достигается за счет того, что устройство содержит амортизатор информации, синхронизатор, измеритель времени, блоки памяти адреса и информации, блок управления передачей и блок управления маркировкой отсчетов и формированием кадров сообщений, а также соответствующие связи между блоками устройства, разработана конструкция блоков устройства. Повышение достоверности передачи информации обеспечивается более высокой помехоустойчивостью структуры кадра сообщения предлагаемого устройства. 7 з.п. ф-лы, 14 ил.

| SU, авторское свидетельство, 1681318, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1998-01-27—Публикация

1995-03-07—Подача