Фиг. i

Изобретение относится к электросвязи и может быть использовано в телеметрических системах.

Цепь изобретения - повышение дос- топерностн устройства.

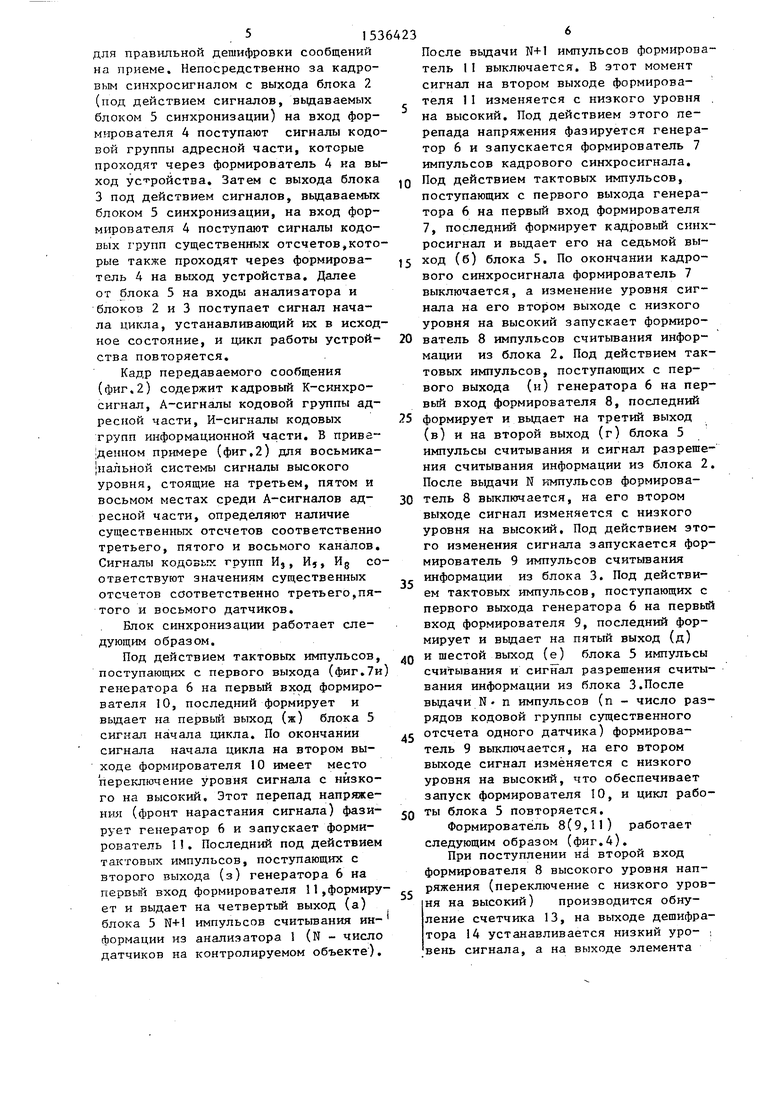

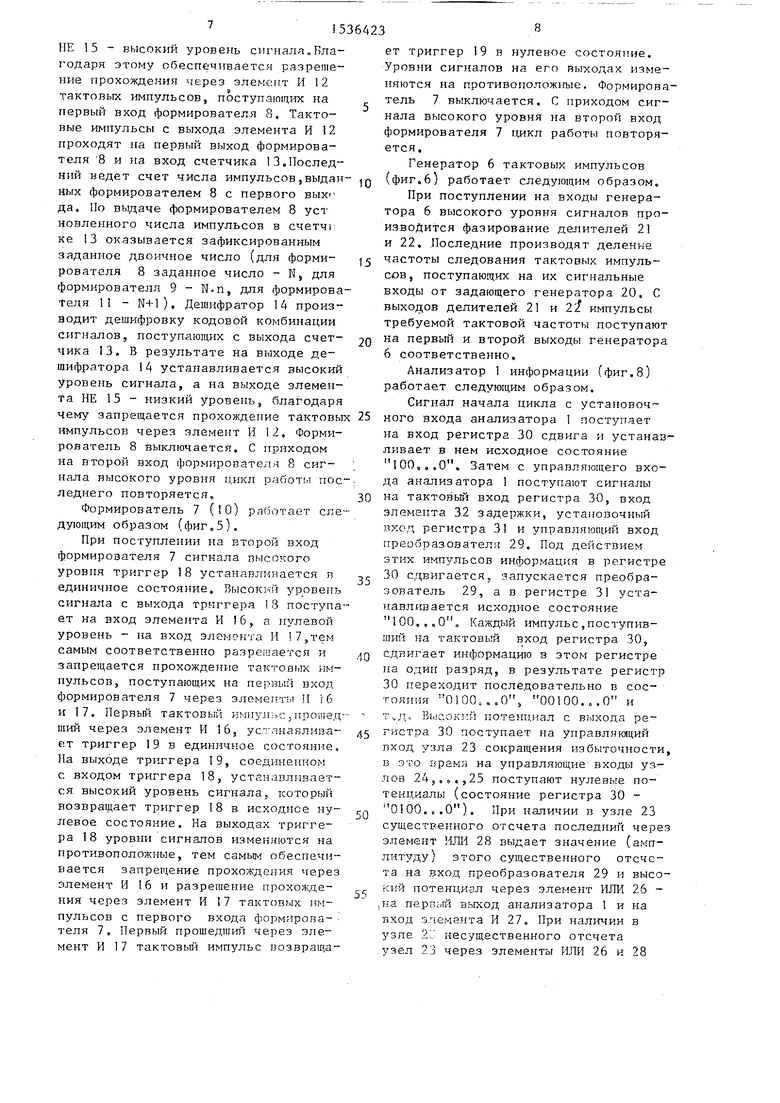

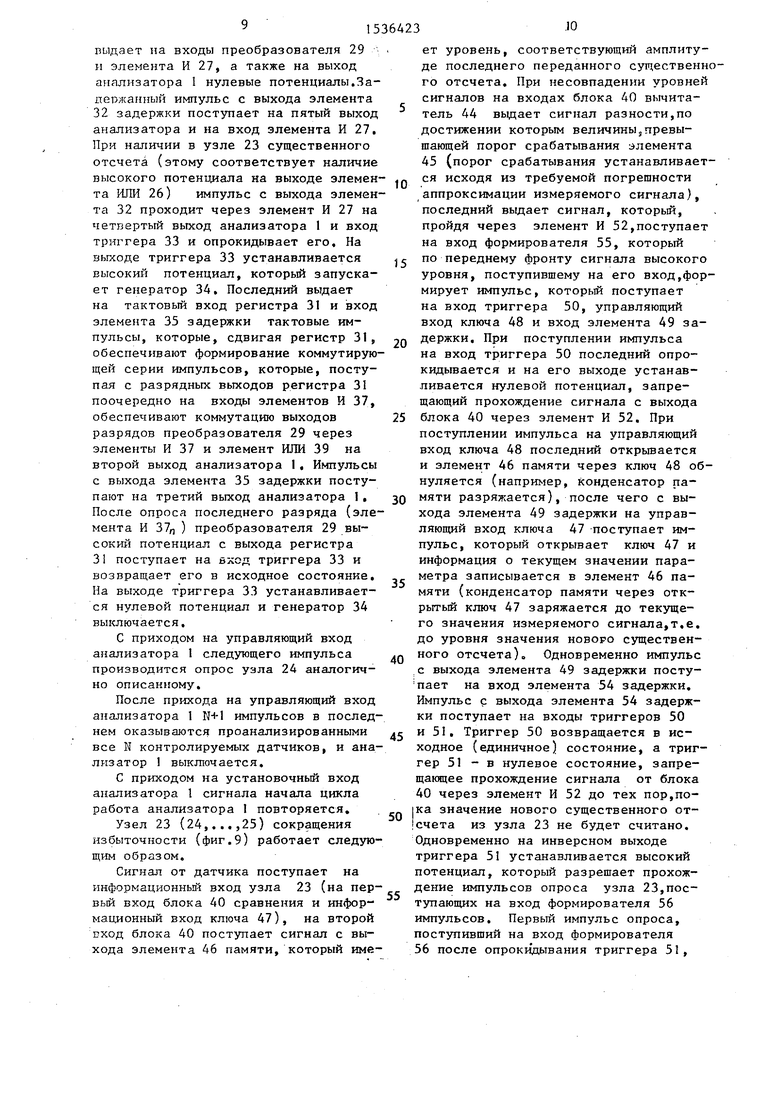

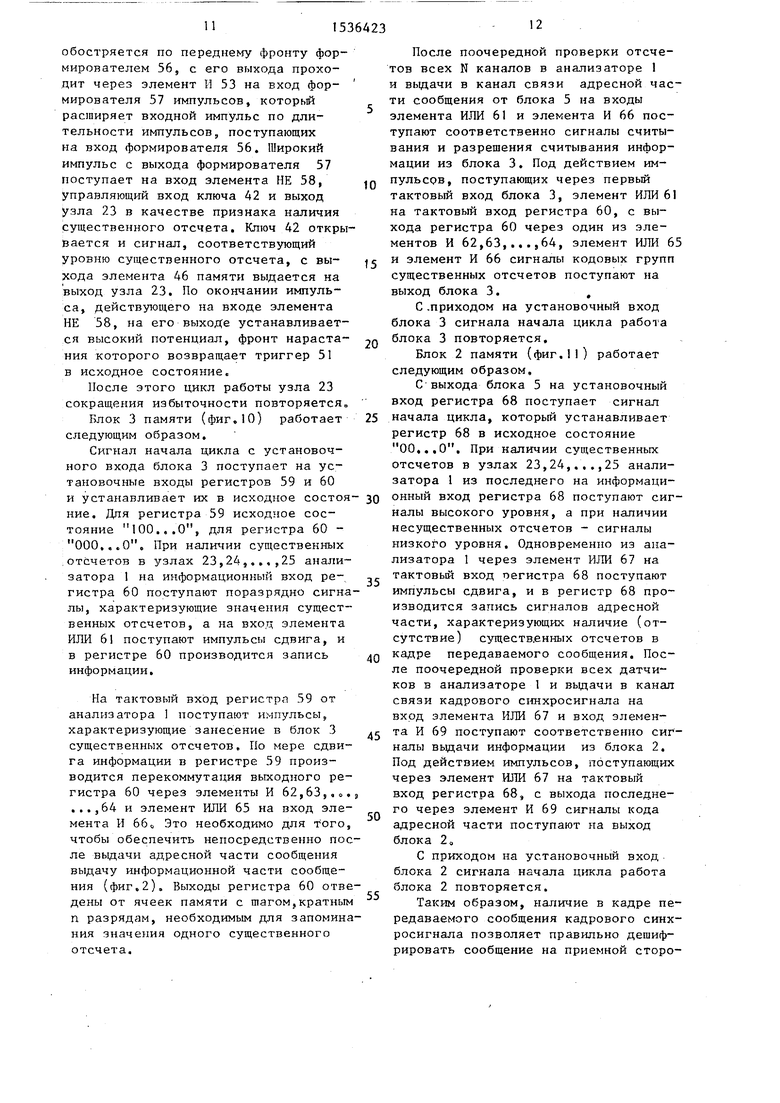

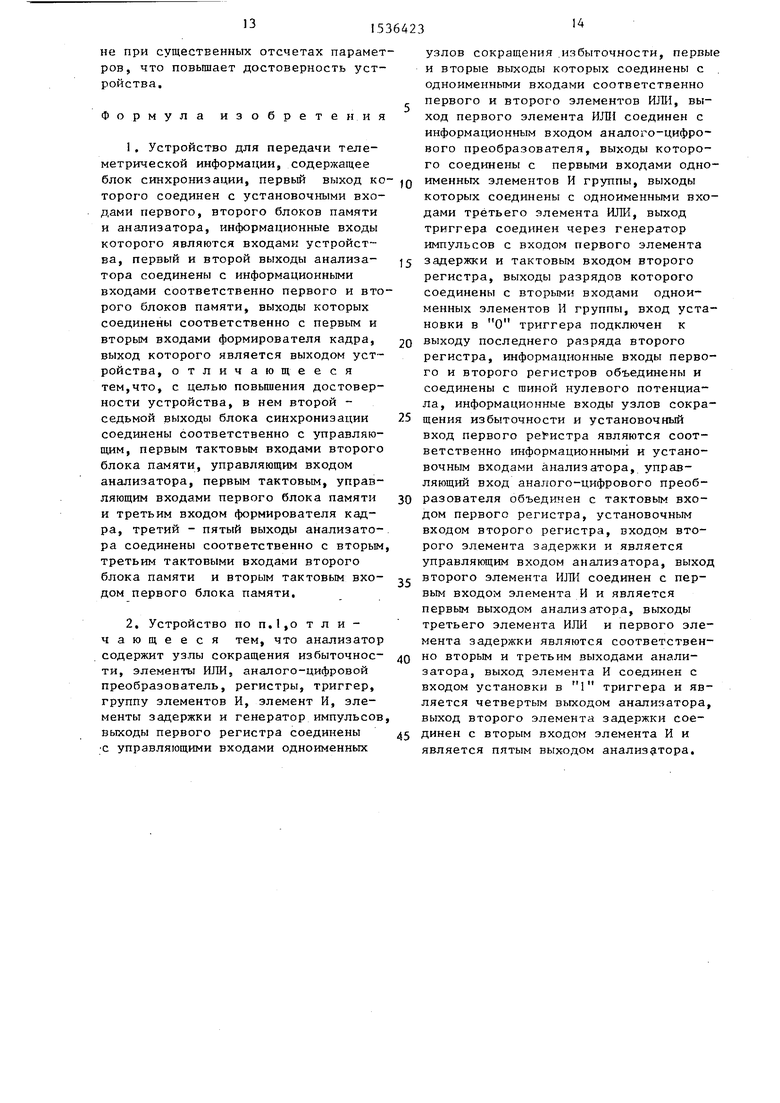

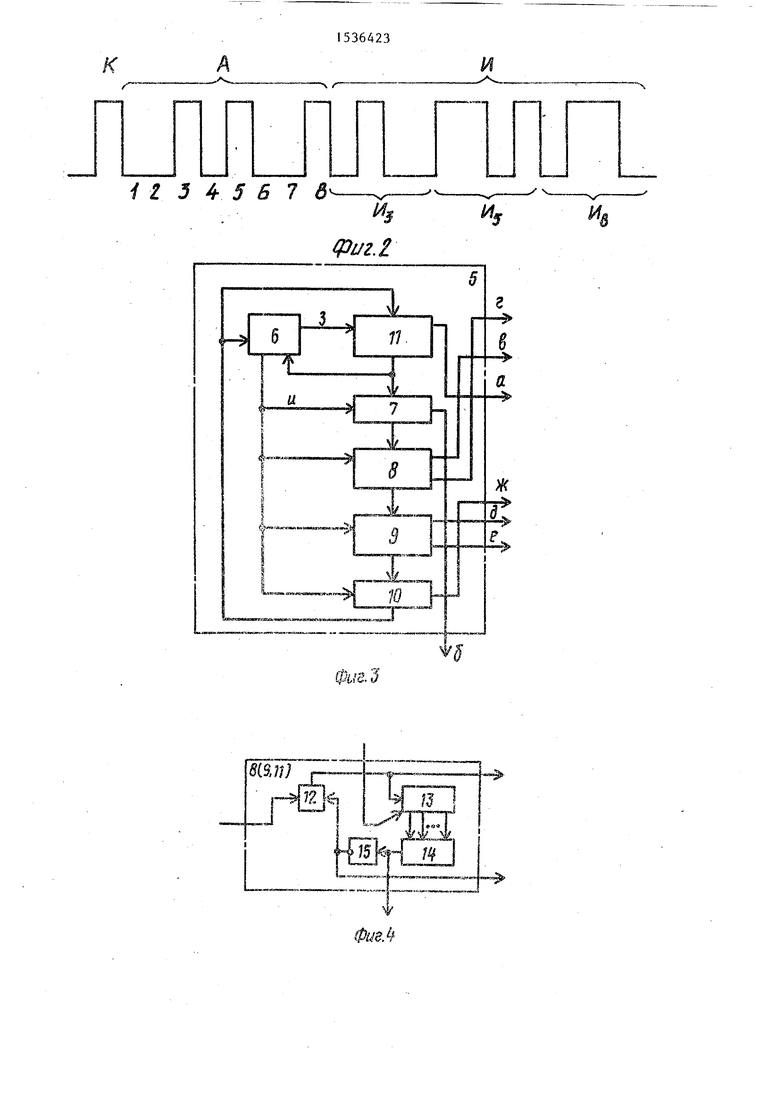

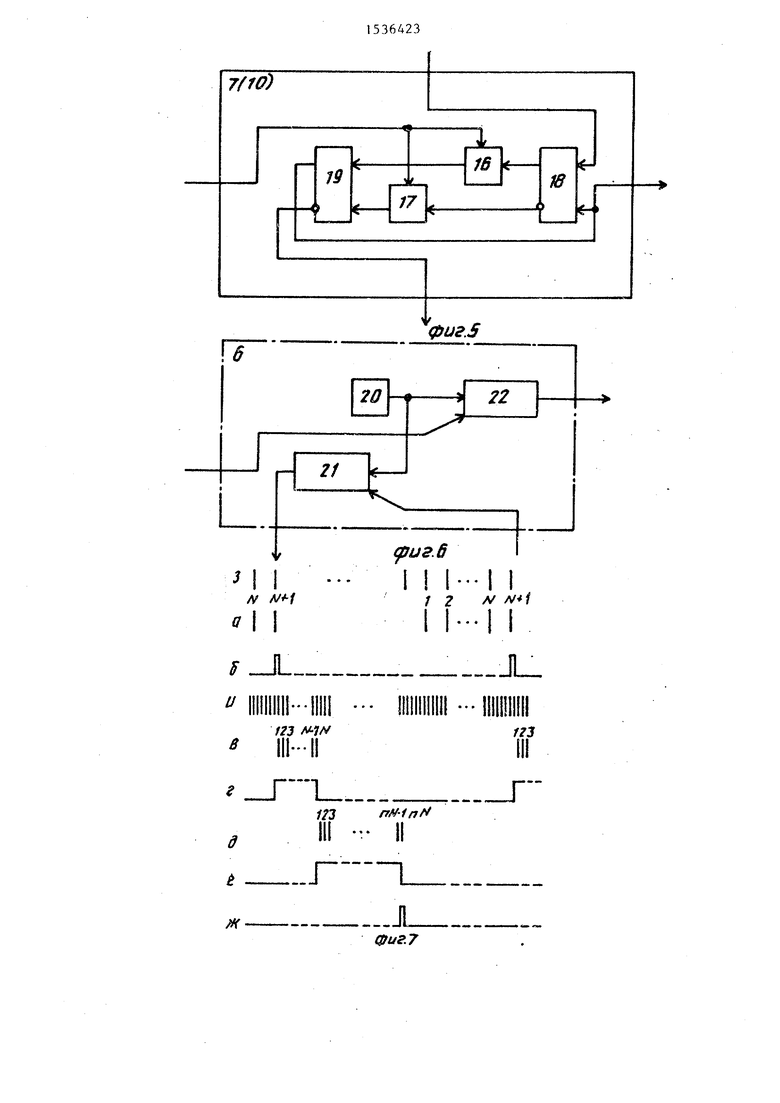

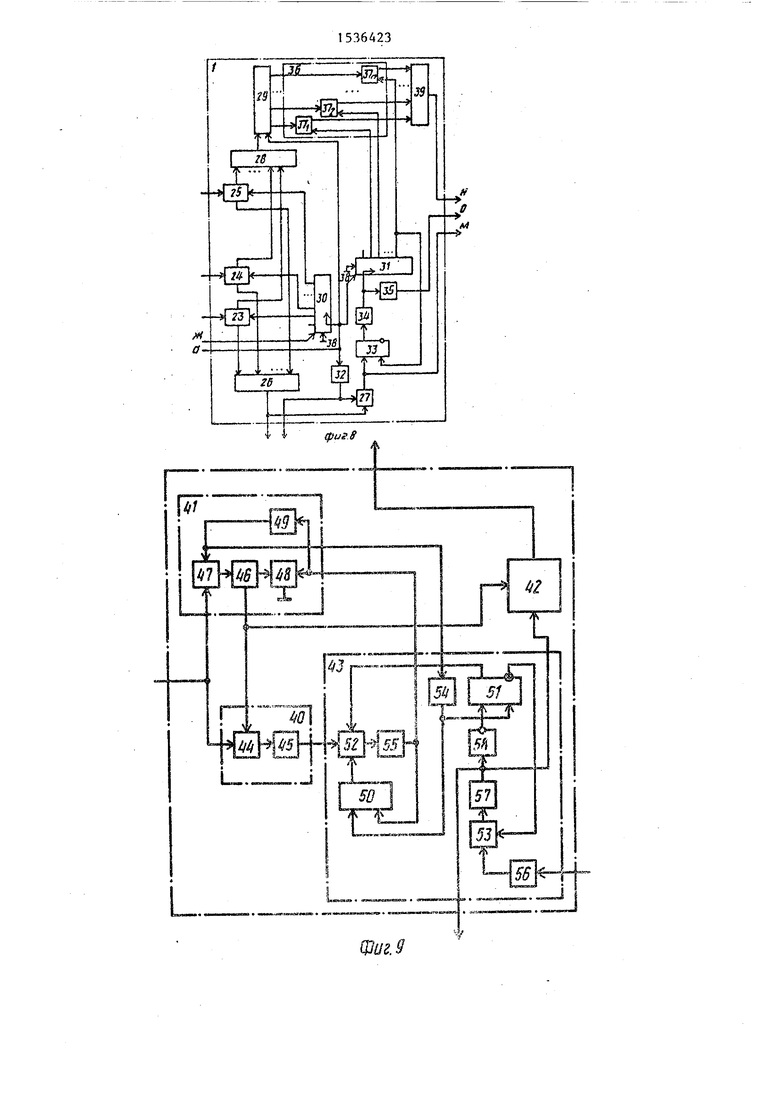

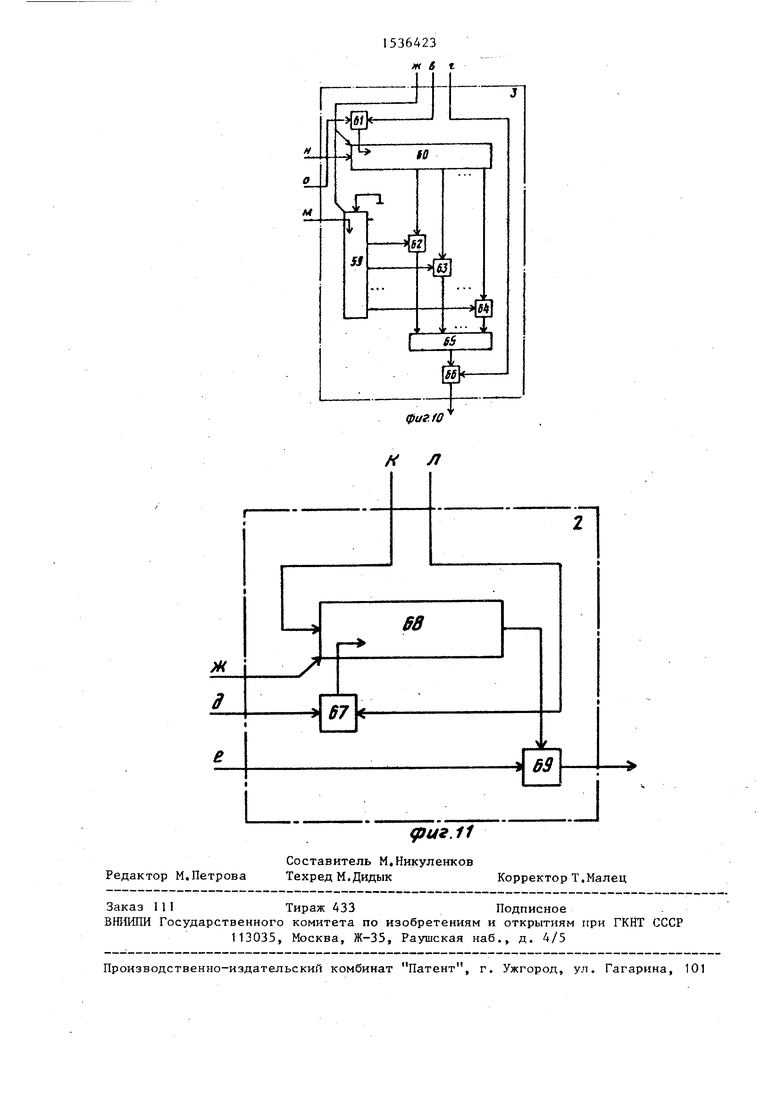

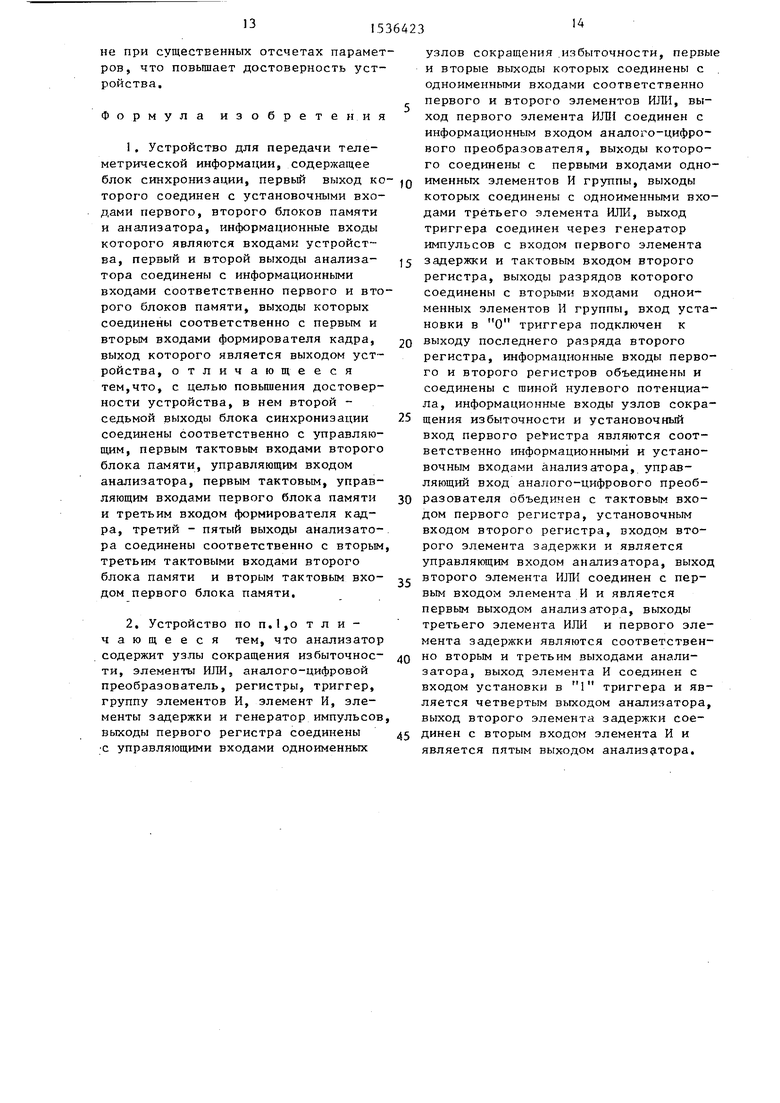

На фиг.1 представлена функциональная схема устройства; на фиг, 2 - структура кадра передаваемого сообщения; на фиг. 3 - функциональная схема блока синхронизации; на фиг.4 - функциональная схема формирователя импульсов; на фиг. 5 - функциональная схема формирователя импульсов; на фиг.6 - функциональная схема гене- раторл тактоных импульсов; на фиг.7 - временные диаграммы, поясняющие работу блока синхронизации; на фиг.8 - функциональная схема анализатора информации; на фиг.9 - функциональная схема учла сокращения избыточности; на фиг.10 - функциональная схема второго блока оперативной памяти инфор мации; на фиг. 11 - функциональная схема первого блока оперативной памяти адреса.

Устройство содержит (фпг.1) анализатор 1 информации, первый блок 2 оперативной памяти адреса, второй блок 3 оперативной памяти информации, формирователь 4 кадра (элемент ИЛИ) и блок 5 синхронизации.

Блок 5 синхронизации содержит (фиг.З) генератор 6 тактовых импульсов и формирователи 7-11 импульсов

Формирователь 8(9,1l) импульсов содержит (фиг.А) элемент И 12, счетчик 13 импульсов, дешифратор 14 и элемент НЕ 15„

Формирователь 7(10) импульсов содержит (фиг.5) элементы И 16 и 17 и триггер, 18 и 1 9„

Генератор 6 тактовых импульсов содержит (фиг.6) задающий генератор 20 и делители 21 и 22 частоты следования импульсов.

Анализатор 1 информации содержит (фиг.8) узлы 23,24,..,,25 сокращения избыточности информации, второй элемент ИЛИ 26, элемент И 27, первый элемент ИЛИ 28, аналого-цифровой преобразователь 29, первый 30 и второй 31 регистры сдвига, второй элемент 32 задержки, триггер 33,управляемый генератор 34 тактовых импульсов, первый элемент 35 задержки, группу 36 элементов И 37, -37Л , шину 38 нулевого потенциала и третий элемент ИЛИ 39.

,

10

20

25

30

35

40

45

50

55

Узел 23(24,25) сокращения избыточности содержит (фиг.9) блок 40 сравнения, формирователь 41 модели сиг- | нала, ключ 42, блок 43 управления. Блок 40 сравнения содержит вычита- тель 44 и пороговый элемент 45. Формирователь 41 модели сигналов содержит элемент 46 аналоговой памяти (конденсатор), ключи 47 и 48 и элемент 49 задержки. Блок 43 управления содержит триггеры 50 и 5 элементы И 52 и 53, элемент 54 задержки, формирователи 55 - 57 импульсов и элемент НЕ 58.

Второй блок 3 оперативной памяти информации содержит (фиг.10) регистры 59 и 60 сдвига, элемент ИЛИ 61, элементы И 62,63,...,64, элемент ИЛИ 65 и элемент И 66„

Первый блок 2 оперативной памяти адреса содержит (фиг.1l) элемент ИЛИ 67, регистр 68 сдвига и элемент И 69.

Устройство работает следующим образом.

Анализатор 1 информации под действием сигналов, поступающих от блока 5 синхронизации, поочередно опрашивает все датчики. Каждый i-й отсчет каждого датчика сравнивается с (i+l)-M отсчетом того же датчика.

Если величина параметра превышает заданную разность их значений, то указанный отсчет (i+l) считается существенным и подлежащим передаче„ Если разность величин отсчетов не превосходит заданной величины, то отсчет считается несущественным и передаче не подлежит.

В процессе поочередной проверки

отсчетов всех N датчиков блок 2 формирует адресную часть, составленную из последовательности N символов единиц и нулей. Существенным отсчетам в адресной части соответствуют сигналы высокого уровня, а несущественным отсчетам - низкого. Кодовые группы, соответствующие значениям существенных отсчетов, записываются в порядке их поступления в блок 3 непосредственно одна за другой.

После опроса всех N датчиков устройство формирует сигнал телеметрического кадра сообщения (фиг.2), При этом блок 5 синхронизации выдает на вход формирователя 4 кадровый синхросигнал, который проходит на выход устройства и служит точкой отсчета

дня правильной дешифровки сообщений на приеме. Непосредственно за кадровым синхросигналом с выхода блока 2 (под действием сигналов, выдаваемых блоком 5 синхронизации) на вход формирователя 4 поступают сигналы кодовой группы адресной части, которые проходят через формирователь 4 ка выход устройства. Затем с выхода блока 3 под действием сигналов, выдаваемых блоком 5 синхронизации, на вход формирователя 4 сигналы кодовых трупп существенных отсчетов,которые также проходят через формирователь 4 на выход устройства. Далее от блока 5 на входы анализатора и блоков 2 и 3 поступает сигнал начала цикла, устанавливающий их в исходное состояние, и цикл работы устройства повторяется.

Кадр передаваемого сообщения (фиг.2) содержит кадровый К-скнхро- сигнал, А-сигналы кодовой группы адресной части, И-сигналы кодовых групп информационной части. В приведенном примере (фиг,2) для восьмика- ,113/1 ьной системы сигналы высокого уровня, стоящие на третьем, пятом и восьмом местах среди А-сигналов адресной части, определяют наличие существенных отсчетов соответственно третьего, пятого и восьмого каналов. Сигналы кодовых групп И,, И,, И8 соответствуют значениям существенных отсчетов соответственно третьего,ля- того и восьмого датчиков.

Блок синхронизации работает следующим образом.

Под действием тактовых импульсов, поступающих с первого выхода (фиг.7и генератора 6 на первый вход формирователя 10, последний формирует и выдает на первый выход (ж) блока 5 сигнал начала цикла. По окончании сигнала начала цикла на втором выходе формирователя 10 имеет место переключение уровня сигнала с низкого на высокий. Этот перепад напряжения (фронт нарастания сигнала) фазирует генератор 6 и запускает форми- ропатель . Последний под действием тлкговых импульсов, поступающих с второго «ыхода (з) генератора 6 на г.срвый вход формирователя 1 1 ,формирует и выдает на четвертый выход (а) блока 5 N+1 импульсов считывания инФормации из анализаторэ I (N - число датчиков на контролируемом объекте).

0

После выдачи N+1 импульсов формирователь 1I выключается. В этот момент сигнал на втором выходе формирователя 1I изменяется с низкого уровня на высокий. Под действием этого перепада напряжения фазируется генератор 6 и запускается формирователь 7 импульсов кадрового синхросигнала. Под действием тактовых импульсов, поступающих с первого выхода генератора 6 на первый вход формирователя 7, последний формирует кадровый синхросигнал и выдает его на седьмой вы5 ход (б) блока 5. По окончании кадрового синхросигнала формирователь 7 выключается, а изменение уровня сигнала на его втором выходе с низкого уровня на высокий запускает формиро0 ватель 8 импульсов считывания информации из блока 2. Под действием тактовых импульсов, поступающих с первого выхода (и) генератора 6 на первый вход формирователя 8, последний

5 формирует и выдает на третий выход (в) и на второй выход (г) блока 5 импульсы считывания и сигнал разрешения считывания информации из блока 2. После выдачи N импульсов формирователь 8 выключается, на его втором выходе сигнал изменяется с низкого уровня на высокий. Под действием этого изменения сигнала запускается формирователь 9 импульсов считывания информации из блока 3. Под действием тактовых импульсов, поступающих с первого выхода генератора 6 на первый вход формирователя 9, последний формирует и выдает на пятый выход (д)

0 и шестой выход (е) блока 5 импульсы считывания и сигнал разрешения считывания информации из блока 3.После выдачи N- n импульсов (п - число разрядов кодовой группы существенного

с отсчета одного датчика) формирователь 9 выключается, на его втором выходе сигнал изменяется с низкого уровня на высокий, что обеспечивает запуск формирователя 10, и цикл работы блока 5 повторяется.

Формирователь 8(9,11) работает следующим образом (фиг.4).

При поступлении на1 второй вход формирователя 8 высокого уровня напряжения (переключение с низкого уровня на высокий) производится обнуление счетчика 13, на выходе дешифратора 14 устанавливается низкий уровень сигнала, а на выходе элемента

0

5

0

5

НЕ 15 - высокий уровень сигнниа, Благодаря этому обеспечивается разрешение прохождения ч .реэ элемент И 12 тактовых импульсов, поступающих на первый вход формирователя 8. Тактовые импульсы с выхода элемента И 12 проходят на первый выход формирователя 8 и на вход счетчика 13.Последний ведет счет числа импульсов,выданных формирователем 8 с первого вых да. По выдаче формирователем 8 уст новленного числа импульсов в счетч ко 13 окатывается зафиксированным заданное двоичное число (для формирователя 8 заданное число - N, для формирователя 9 - N.n, для формирователя 11 - N+1). Дешифратор 14 производит дешифровку кодовой комбинации сигналов, поступающих с выхода счетчика 13. В результате на выходе дешифратора 14 устанавливается высокий уровень сигнала, а на выходе элемента НЕ 15 - низкий уровень, благодаря

Ю

15

20

8

ет триггер 19 р нулевое состояние. Уровни сигналов на его выходах пзме- ннются на противоположные. Формирователь 7 выключается. С приходом сигнала высокого уровня на второй вход формирователя 7 цикл работы повторяется.

Генератор 6 тактовых импульсов (фиг.6) работает следующим образом.

При поступлении на входы генератора 6 высокого уровня сигналов производится фазирование делителей 21 и 22. Последние производят делечье частоты следования тактовых импульсов, поступающих на их сигнальные входы от задающего генератора 20. С выходов делителей 21 и 22 импульсы требуемой тактовой частоты поступают на первый и второй выходы генератора 6 соответственно.

Анализатор 1 информации фиг. 8) работает следующим образом.

Сигнал начала никла с установоч

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Устройство для селекции изображений | 1991 |

|

SU1837335A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| ИЗМЕРИТЕЛЬ СПЕКТРАЛЬНЫХ ПАРАМЕТРОВ РАДИОСИГНАЛОВ | 2005 |

|

RU2279098C1 |

| Телевизионный пеленгатор | 1989 |

|

SU1670805A1 |

| Преобразователь телевизионных стандартов | 1987 |

|

SU1506591A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

Изобретение относится к электросвязи и может использоваться в телеметрических системах. Устройство осуществляет циклический опрос датчиков и формирование кадра передаваемого сообщения, состоящего из кадрового синхросигнала, адресной части и информационной части, что обеспечивает повышение достоверности устройства. Устройство содержит анализатор 1 информации, блок 2 оперативной памяти адреса, блок 3 оперативной памяти информации, формирователь 4 кадра и блок 5 синхронизации. 1 з.п. ф-лы, 11 ил.

30

чему запрещается прохождение тактовых 25 ного входа анализатора 1 поступает импульсов через -элемент И 12. Формирователь 8 выключается. С приходом на второй вход формирователя Я сигнала высокого уровня цикл рнГнп . последнего повторяется.

Формирователь 7 (10) рчоота г следующим образом (фиг.5).

При поступлении на второй вход формирователя 7 сигнала высокого уровня триггер 18 устанавливается в единичное состояние. 5ысок ч уровень сигнала с выхода триггера 1 В пос гупа- ет на вход элемента И 1Ь, а пулевой уровень - на вход элем м; ui И 1 7 тем

35

на вход регистра 30 сдвига и устана ливает в нем исходное состояние 100,..0. Затем с управляющего вхо дя анализатора 1 поступают сигналы на тактовый вход регистра 30, вход элемента 32 задержки, установочный ччс. ; регистра 31 и управляющий вход лрс1 бт азователч 29, Под действием Г Тих нмп /льсов информация в регистр Ю гдт пгается, запускается преобра- «ор-атель 29, а в регистре 31 устанавливается исходное состояние 100.,, О, аждый импульс ,поступивший на такгошлй вход регистра 30, сдвигает информацию в этом регистре пл один разряд, я результате регист 30 переходит последовательно в сос- г Oi )0« . .0, 00100. ..О и -, , :н,ч-,|, , потенциал с выходч регистр, 30 поступает на управляющий нход /ша 23 сокращения избыточност )io fip::N./i на упрапляюцпе входы уз U li 2ч,,,,,25 поступают нулевые по- тенг.иалы (состояние регистра 30 0100...О). При наличии в узле 23 сущее1 репного отсчета последний чер эпенснт МПИ 2.8 выдает значение (амп литуду) этого существенного отсче та на пход преобразователя 29 и выс г 1-й потенциал через эпемент ИЛ11 26 нл п.-р-. й ьыход анализатора 1 и на ьход .-.рчта И 27. При наличии в учлр аесущестпенного отсчета узел , через элементы ИЛИ 2Ь л 28

и им:одif

Vi- Цсамым соответственно разрешается запрещается прохождение тактовых пульсов, поступающих на перным в; формирователя 7 через злеми 1 11 и 17. Первый тактовьг HMIIVIP ,npf ший через элемент И 16, ус aiiai;jr,ma- ет триггер 19 в единичное состояние. На выходе триггера 19, соединенном с входом триггера 18, устан. ся высокий уровень сигнала, который возвращает триггер 18 в исходное пулевое состояние. На выходах триггера 18 уровни сигналов изменяются на противоположные, тем самым обеспечивается запрещение прохождения через элемент И 16 и разрешение прохождения через элемент И 17 тактовых импульсов с первого входа формирователя 7. Первый прошедший чере элемент И 17 тактовый импульс возвраща0

5 ного входа анализатора 1 поступает

5

5

на вход регистра 30 сдвига и устанавливает в нем исходное состояние 100,..0. Затем с управляющего входя анализатора 1 поступают сигналы на тактовый вход регистра 30, вход элемента 32 задержки, установочный ччс. ; регистра 31 и управляющий вход лрс1 бт азователч 29, Под действием Г Тих нмп /льсов информация в регистре Ю гдт пгается, запускается преобра- «ор-атель 29, а в регистре 31 устанавливается исходное состояние 100.,, О, аждый импульс ,поступивший на такгошлй вход регистра 30, сдвигает информацию в этом регистре пл один разряд, я результате регистр 30 переходит последовательно в сос- г Oi )0« . .0, 00100. ..О и -, , :н,ч-,|, , потенциал с выходч регистр, 30 поступает на управляющий нход /ша 23 сокращения избыточности, )io fip::N./i на упрапляюцпе входы уз- U li 2ч,,,,,25 поступают нулевые по- тенг.иалы (состояние регистра 30 0100...О). При наличии в узле 23 сущее1 репного отсчета последний через эпенснт МПИ 2.8 выдает значение (амплитуду) этого существенного отсчета на пход преобразователя 29 и высо- г 1-й потенциал через эпемент ИЛ11 26 - нл п.-р-. й ьыход анализатора 1 и на ьход .-.рчта И 27. При наличии в учлр аесущестпенного отсчета узел , через элементы ИЛИ 2Ь л 28

пи/пет на входы преобразователя 29 и элрмрнта И 27, а также на выход анализатора I нулевые потенциалы.За- ггч/ланный импульс с выхода элемента 32 задержки поступает на пятый выход анализатора и на вход элемента И 27. При наличии в узле 23 существенного отсчета (этому соответствует наличие высокого потенциала на выходе элемента ИЛИ 26) импульс с выхода элемента 32 проходит через элемент И 27 на четвертый выход анализатора I и вход триггера 33 и опрокидывает его. На выходе триггера 33 устанавливается В1 1сокий потенциал, который запускает генератор 34. Последний выдает на тактовый вход регистра 31 и вход элемента 35 задержки тактовые импульсы, которые, сдвигая регистр 31, обеспечивают формирование коммутирующей серии импульсов, которые, поступая с разрядных выходов регистра 31 поочередно на входы элементов И 37, обеспечивают коммутацию выходов разрядов преобразователя 29 через элементы И 37 и элемент ИЛИ 39 на второй выход анализатора 1. Импульсы с выхода элемента 35 задержки поступают на третий выход анализатора 1. После опроса последнего разряда (элемента И 37„ ) преобразователя 29 высокий потенциал с выхода регистра 31 поступает на вход триггера 33 и во лращает его в исходное состояние. На выходе триггера 33 устанавливается нулевой потенциал и генератор 34 выключается.

С приходом на управляющий вход анализатора 1 следующего импульса производится опрос учла 24 аналогично описанному.

После прихода на управляющий вход анализатора 1 IJ+1 импульсов в последнем оказываются проанализированными все И контролируемых датчиков, и анализатор выключается.

С приходом на установочный вход анализатора 1 сигнала начала цикла работа анализатора 1 повторяется.

Узел 23 (24,...,25) сокращения избыточности (фиг.9) работает следую- Щ1гм образом.

Сигнал от датчика поступает на ннфопмационныи вход узла 23 (на пер- ши вход блока 40 сравнения и информационный вход ключа 47), на второй гход блока 40 поступает сигнал с выхода элемента 46 памяти, который име

10

15

20

25

6423Ю

ет уровень, соответствующий амплитуде последнего переданного существенного отсчета. При несовпадении уровней сигналов на входах блока 40 вычита- тель 44 выдает сигнал разности,по достижении которым величины,превышающей порог срабатывания элемента 45 (порог срабатывания устанавливается исходя из требуемой погрешности аппроксимации измеряемого сигнала), последний выдает сигнал, который, пройдя через элемент И 52,поступает на вход формирователя 55, который по переднему фронту сигнала высокого уровня, поступившему на его вход,формирует импульс, который поступает на вход триггера 50, управляющий вход ключа 48 и вход элемента 49 задержки. При поступлении импульса на вход триггера 50 последний опрокидывается и на его выходе устанавливается нулевой потенциал, запрещающий прохождение сигнала с выхода блока 40 через элемент И 52. При поступлении импульса на управляющий вход ключа 48 последний открывается и элемент 46 памяти через ключ 48 обнуляется (например, конденсатор памяти разряжается), после чего с выхода элемента 49 задержки на управляющий вход ключа 47 поступает импульс, который открывает ключ 47 и информация о текущем значении параметра записывается в элемент 46 памяти (конденсатор памяти через открытый ключ 47 заряжается до текущего значения измеряемого сигнала,т.е. до уровня значения нового существенного отсчета). Одновременно импульс с выхода элемента 49 задержки поступает на вход элемента 54 задержки. Импульс с выхода элемента 54 задержки поступает на входы триггеров 50 и 51. Триггер 50 возвращается в исходное (единичное) состояние, а триггер 51 - в нулевое состояние, запрещающее прохождение сигнала от блока 40 через элемент И 52 до тех пор,пока значение нового существенного отсчета из узла 23 не будет считано. Одновременно на инверсном выходе триггера 51 устанавливается высокий потенциал, который разрешает прохождение импульсов опроса узла 23,поступающих на вход формирователя 56 импульсов. Первый импульс опроса, поступивший на вход формирователя 56 после опрокидывания триггера 51,

30

35

40

45

50

55

обостряется по переднему фронту формирователем 56, с его выхода проходит через элемент И 53 на вход формирователя 57 импульсов, который расширяет входной импульс по длительности импульсов, поступающих на вход формирователя 56. Широкий импульс с выхода формирователя 57 поступает на вход элемента НЕ 58, управляющий вход ключа 42 и выход учла 23 в качестве признака наличия существенного отсчета. Ключ 42 открывается и сигнал, соответствующий уровню существенного отсчета, с вы- хода элемента 46 памяти выдается на выход узла 23. По окончании импульса, действующего на входе элемента НЕ 58, на его выходе устанавливается высокий потенциал, фронт нараста- ния которого возвращает триггер 51 в исходное состояние.

После этого цикл работы узла 23 сокращения избыточности повторяется.

Клок 3 памяти (фиг.Ю) работает следующим образом.

Сигнал начала цикла с установочного входа блока 3 поступает на установочные входы регистров 59 и 60 и устанавливает их в исходное состоя ние. Для регистра 59 исходное состояние 100...О, для регистра 60 - 000,,.О. При наличии существенных отсчетов в узлах 23,24,...,25 анализатора 1 на информационный вход ре- гистра 60 поступают поразрядно сигналы, характеризующие значения существенных отсчетов, а на вход элемента ИЛИ 61 поступают импульсы сдвига, и в регистре 60 производится запись информации.

На тактовый вход регистра 59 от анализатора 1 поступают импульсы, характеризующие занесение в блок 3 существенных отсчетов. По мера сдвига информации в регистре 59 производится перекоммутация выходного регистра 60 через элементы И 62,63,.. ...,64 и элемент ИЛИ 65 на вход элемента И 66 Это необходимо для того, чтобы обеспечить непосредственно после выдачи адресной части сообщения выдачу информационной части сообщения (фиг.2). Выходы регистра 60 отведены от ячеек памяти с тагом,кратным п разрядам, необходимым для запоминания значения одного существенного отсчета.

Q

5

0 г 0

,-

0

5

После поочередной проверки отсчетов всех N каналов в анализаторе 1 и выдачи в канал связи адресной части сообщения от блока 5 на входы элемента ИЛИ 61 и элемента И 66 поступают соответственно сигналы считывания и разрешения считывания информации из блока 3. Под действием импульсов, поступающих через первый тактовый вход блока 3, элемент ИЛИ 61 на тактовый вход регистра 60, с выхода регистра 60 через один из элементов И 62,63,...,64, элемент ИЛИ 65 и элемент И 66 сигналы кодовых групп существенных отсчетов поступают на выход блока 3.,

С .приходом на установочный вход блока 3 сигнала начала цикла работа блока 3 повторяется.

Блок 2 памяти (фиг.П) работает следующим образом.

С выхода блока 5 на установочный вход регистра 68 поступает сигнал начала цикла, который устанавливает регистр 68 в исходное состояние 00...О. При наличии существенных отсчетов в узлах 23,24,...,25 анализатора 1 из последнего на информационный вход регистра 68 поступают сигналы высокого уровня, а при наличии несущественных отсчетов - сигналы низкого уровня. Одновременно из анализатора 1 через элемент ИЛИ 67 на тактовый вход пегистра 68 поступают импульсы сдвига, и в регистр 68 производится запись сигналов адресной части, характеризующих наличие (отсутствие) существенных отсчетов в кадре передаваемого сообщения. После поочередной проверки всех датчиков в анализаторе 1 и выдачи в канал связи кадрового синхросигнала на вход элемента ИЛИ 67 и вход элемента И 69 поступают соответственно сигналы выдачи информации из блока 2. Под действием импульсов, поступающих через элемент ИЛИ 67 на тактовый вход регистра 68, с выхода последнего через элемент И 69 сигналы кода адресной части поступают на выход блока 2о

С приходом на установочный вход блока 2 сигнала начала цикла работа блока 2 повторяется.

Таким образом, наличие в кадре передаваемого сообщения кадрового синхросигнала позволяет правильно дешифрировать сообщение на приемной стороне при существенных отсчетах параметров, что повышает достоверность устройства.

Формула изобретения

I. Устройство для передачи телеметрической информации, содержащее

бЛОК СИНХрОНИЗаЦИИ, ПЕРВЫЙ ВЫХОД КО

торого соединен с установочными входами первого, второго блоков памяти и анализатора, информационные входы которого являются входами устройства, первый и второй впходы анализа- тора соединены с информационными входами соответственно первого и второго блоков памяти, выходы которых соединены соответственно с первым и вторым входами формирователя кадра, выход которого является выходом устройства, отличающееся тем,что, с целью повышения достоверности устройства, в нем второй - седьмой выходы блока синхронизации соединены соответственно с управляющим, первым тактовым входами второго блока памяти, управляющим входом анализатора, первым тактовым, управляющим входами первого блока памяти и третьим входом формирователя кадра, третий - пятый выходы анализатора соединены соответственно с вторым третьим тактовыми входами второго блока памяти и вторым тактовым входом первого блока памяти.

.отличающееся тем, что анализатор содержит уэпы сокращения избыточное- ти, элементы ИЛИ, аналого-цифровой преобразователь, регистры, триггер, группу элементов И, элемент И, элементы задержки и генератор импульсов, выходы первого регистра соединены с управляющими входами одноименных

JQ

0 5 0

5

0 $

узлов сокращения избыточности, первые и вторые выходы которых соединены с одноименными входами соответственно первого и второго элементов ИЛИ, выход первого элемента ИЛИ соединен с информационным входом аналого-цифрового преобразователя, выходы которого соединены с первыми входами одноименных элементов И группы, выходы которых соединены с одноименными входами третьего элемента ИЛИ, выход триггера соединен через генератор импульсов с входом первого элемента задержки и тактовым входом второго регистра, выходы разрядов которого соединены с вторыми входами одноименных элементов И группы, вход установки в О триггера подключен к выходу последнего разряда второго регистра, информационные входы первого и второго регистров объединены и соединены с гаиной нулевого потенциала, информационные входы узлов сокращения избыточности и установочный вход первого регистра являются соответственно информационными и установочным входами анализатора, управляющий вход аналого-цифрового преобразователя объединен с тактовым входом первого регистра, установочным входом второго регистра, входом второго элемента задержки и является управляющим входом анализатора, выход второго элемента ИЛИ соединен с первым входом элемента И и является первым выходом анализатора, выходы третьего элемента ИЛИ и первого элемента задержки являются соответственно вторым и третьим выходами анализатора, выход элемента И соединен с входом установки в I триггера и является четвертым выходом анализатора, выход второго элемента задержки соединен с вторым входом элемента И и является пятым выходом анализатора.

К

А

i I 3 4 5 Б 7 6

И

ил

ИА

фиг. 6

ФигМ

7f1&

19

ГГ

21

I l

/v /VA/

I I

.

123

111-11

гп

in

III

...г

ГТ#

...J

18

фиг.5

22

(риг. 6

11 ii i

; 2 /v

-I I

-Jl

т

III

ГТ#-1п#

II

...JL

Фиг

H- ифГяТ- - -ж-1 -

т

ii

L.

фГяТ- -ж-1 -

т

Ж

Фиг. 9

Составитель М.Никуленков Редактор М.Петрова Техред М.ДидыкКорректор Т.Малец

-- - -- - - -- - - - - ---- - --- - - - - - - - - - - - - - - - -- - - - - -- - -- - -----..-. .-.1-.

Заказ 111Тираж ДЭЗПодписное

ВНИИЛИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 1130J5, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

J

фиг.11

| Устройство для сокращения избыточности информации | 1983 |

|

SU1100634A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Авторское свидетельство СССР № 226948, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1990-01-15—Публикация

1988-04-11—Подача