Изобретение относится к микроэлектронике, а именно к технологии изготовления СИ на биполярных вертикальных PNP транзисторах.

В последние 30 лет в технологии кремниевых биполярных схем применялись в основном NPN транзисторы главным образом потому, что электроны имеют более высокую подвижность, чем дырки. Однако исследования Дель-Адамо и др. [1] показали, что подвижность дырочных неосновных носителей, описывающая транспортировку дырок в базе PNP прибора в два раза выше, чем у дырок, являющихся основными носителями. Это означает, что собственное быстродействие NPN и PNP приборов является в принципе сопоставимым.

Однако до недавнего времени функционирование PNP транзисторов было хуже чем ожидалось, главным образом из-за ограничений, вызываемых высоким коллекторным сопротивлением. Но после того, как и эти ограничения были преодолены путем создания высоколегированных p+ скрытых слоев, PNP транзисторы получили широкое распространение в ИС на комплексных биполярных транзисторах и КБиКМОП.

Известен способ формирования вертикального PNP транзистора в БиКМОП технологии [2] включающий формирование скрытого коллектора p+ типа проводимости PNP транзистора, электрически изолированного от подложки p-типа проводимости с помощью охватывающего его скрытого слоя n- типа проводимости, создание скрытых слоев n+ типа проводимости для последующей изоляции PNP транзистора и формирования скрытого коллектора NPN транзистора, осаждение эпитаксиального слоя p- типа, создание боковой изоляции транзистора встречной диффузией примеси n+ типа проводимости, формирование базы n- типа проводимости и создание эмиттера p+ типа проводимости.

Недостатком данного способа является "врезание" базовой области в скрытый коллектор PNP транзистора, что вызвано распространением скрытого коллектора p+ типа проводимости к поверхности в процессе создания боковой изоляции диффузией, существенно увеличивающим паразитную емкость перехода база-коллектор, и, что важно, снижающим быстродействие ИС.

Известны технические решения, позволяющие уменьшить вышеуказанный недостаток PNP транзистора, создаваемый длительными температурными обработками, в результате использования низкотемпературных методов формирования боковой изоляции диэлектриком.

Наиболее близким техническим решением к предлагаемому изобретению является технология создания вертикального самосовмещенного PNP транзистора [1] включающая создание скрытого слоя p+ типа в подложки n- типа проводимости имплантацией примесей германия и бора, с предварительной аморфизацией кремния с помощью германия, устраняющего после отжига дефекты структуры, осаждение эпитаксиального слоя, формирование щелевой изоляции заполненной поликремнием, формирование на поверхности участков изолирующего диэлектрика вокруг будущих областей базы и коллектора транзистора, формирование области глубокого коллектора, создание базовой области n- типа проводимости, формирование эмиттера p+ типа проводимости и создание контактов к областям транзистора.

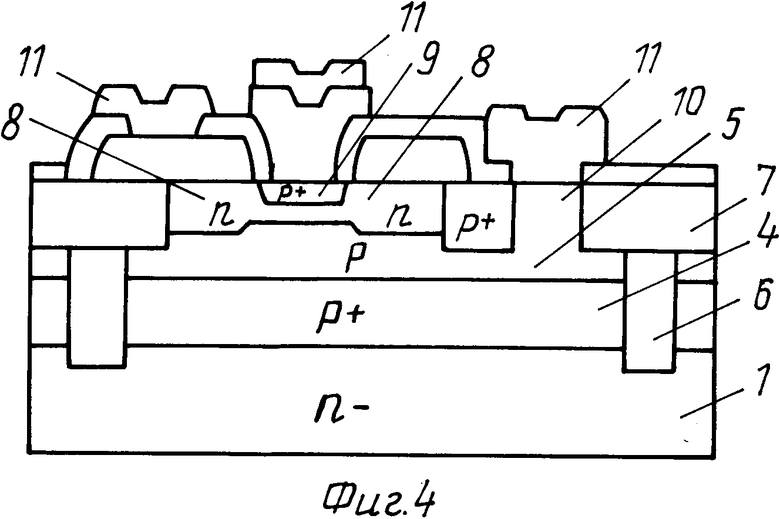

На фиг. 1-4 представлены основные этапы изготовления транзистора по способу в соответствии с прототипом со скрытым коллектором, получаемым методом имплантации примесей.

На фиг. 1 представлен разрез структуры после имплантации больших доз германия, в процессе которой происходит аморфизация 2 области кремния 1 на глубине предполагаемой последующей имплантации бора; на фиг. 2 разрез структуры после имплантации бора 3 в аморфную область кремния 2; на фиг.3 - разрез структуры после термического отжига, вызывающего твердофазную рекристаллизацию и обеспечивающую создание бездефектного скрытого коллектора p+ типа проводимости 4; на фиг.4 разрез структуры после эпитаксиального осаждения слоя p- типа проводимости 5, формирования щелевой изоляции 6, создания участков изолирующего диэлектрика на поверхности 7, формирования коллекторной области 10, формирования базовых областей n типа проводимости 8, создания эмиттера 9 p+ типа проводимости, формирования контактов к области транзистора 11.

Однако указанный способ технически сложен в исполнении и предусматривает необходимость последовательного проведения процессов имплантации примесей двух типов, что удлиняет технологический цикл изготовления изделия за счет большего количества операций, что в свою очередь увеличивает стоимость изделия и снижает выхода годных.

Целью настоящего изобретения является повышение процента выхода годных ИС и снижение их стоимости за счет формирования бездефектного p+ скрытого коллектора в одном процессе имплантации в результате выполнения имплантированной примесью одновременно функций аморфизации кремния и легирования до требуемого уровня поверхностного сопротивления.

Поставленная цель достигается за счет того, что в способе создания вертикального PNP транзистора в составе ИС, включающем формирование в подложке кремния аморфизированного приповерхностного слоя в месте будущего расположения скрытых слоев p+ типа проводимости, легирование приповерхностного слоя примесью p- типа проводимости, рекристаллизацию и отжиг аморфизированного слоя, осаждение эпитаксиального слоя, формирование боковой изоляции, создания диэлектрика на поверхности, формирование коллекторной области, создание базовой области транзистора, формирование эмиттера, аморфизацию приповерхностного слоя и его легирование примесью p-типа проводимости в месте будущего расположения скрытых слоев p+ типа проводимости проводят в одном процессе имплантации примесью BF2, рекристаллизуют и отжигают аморфизированный слой, осаждают эпитаксиальный слой, формируют боковую изоляцию, создают диэлектрик на поверхности, формируют коллекторную область, создают базовую область транзистора, формируют эмиттер.

Таким образом, отличительными признаками предлагаемого изобретения является то, аморфизацию приповерхностного слоя и его легирования примесью p-типа проводимости в месте будущего расположения скрытых слоев p+ типа проводимости производят в одном процессе имплантации примесей BF2, рекристаллизуют и отжигают аморфизированный слой, осаждают эпитаксиальный слой, формируют боковую изоляцию, создают диэлектрик на поверхности, формируют коллекторную область, создают базовую область транзистора, формируют эмиттер.

Проведенные патентные исследования показали, что совокупность признаков предлагаемого изобретения является новой, что доказывает новизну заявляемого способа. Кроме того, патентные исследования показали, что в литературе отсутствуют данные, показывающие влияния отличительных признаков заявляемого изобретения на достижение технического результата, что подтверждает изобретательский уровень предлагаемого способа.

Данная совокупность отличительных признаков позволяет решить поставленную задачу.

Указанное выполнение предлагаемого способа приводит к тому, что в одном процессе имплантации производится одновременно и аморфизация кремния и легирование примесью для создания скрытого коллектора, что при последующих рекристаллизации и отжиге аморфизированного слоя происходит устранение дефектов структуры в области скрытого коллектора.

В данном способе существенно упрощается процесс формирования скрытого коллектора, так как нет необходимости совмещать аморфизированную область, создаваемую имплантацией германия, и распределение примеси для создания скрытого коллектора это выполняется автоматически.

Существенно сокращается и упрощается техпроцесс создания скрытого коллектора, поскольку не требуется сложный дорогостоящий процесс имплантации германия.

Такая совокупность отличительных признаков позволяет сократить технологический цикл, уменьшить количество операций в способе создания транзистора и обеспечить тем самым повышение процента выхода годных и снижение стоимости изделия.

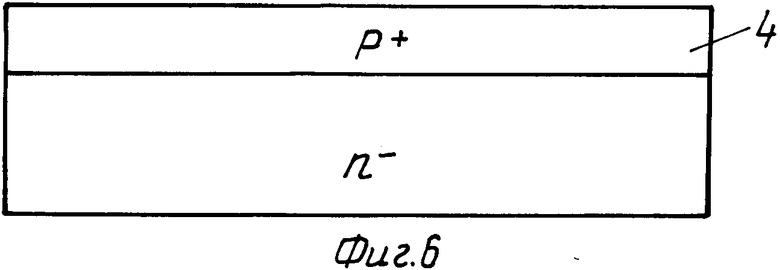

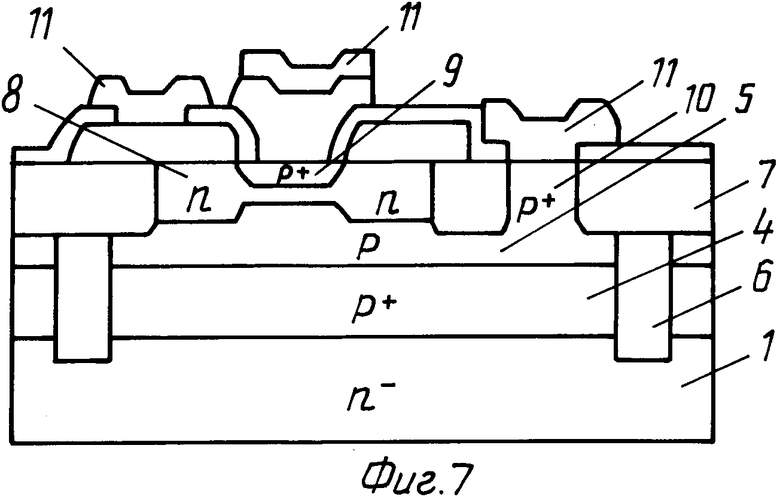

На фиг. 5-7 представлены основные этапы изготовления транзистора по предлагаемому способу.

На фиг. 5 представлен разрез структуры после имплантации BF2 с дозой выше уровня аморфизации (более 5•10 см2), на фиг. 6 разрез структуры после рекристаллизации аморфизированного слоя и отжига дефектов и перераспределение примеси в скрытом коллекторе, на фиг. 7 разрез структуры после осаждения эпитаксиального слоя p- типа проводимости, формирование боковой изоляции, в данном случае щели заполненной поликремнием, формирования диэлектрика на поверхности, формирования коллекторной области, создания базовой области транзистора и формирования эмиттера.

Пример. В монокристаллической подложке N-типа проводимости (rv=10 Ом•см) формируют скрытый коллектор имплантацией BF2 с дозой 5•10 см2 с энергиями 40 и 120 кэВ, отжигают его вначале при 600oC в атмосфере водорода, а затем при 1100oC в атмосфере азота, осаждают эпитаксиальный слой p типа проводимости (rv= 0,3 Ом•см) толщиной 1,75 мкм. Эпитаксиальный слой маскируют двухслойным покрытием из окисла кремния и нитрида кремния толщиной 3000  и 1500

и 1500  соответственно. Методами фотолитографии и ПХТ травления вскрывают окна в маскирующем слое нитрида кремния и двуокиси кремния, проводят травление канавок в кремнии на глубину 6,0 мкм, шириной 1,5 мкм. Формируют на стенках канавок слой диэлектрика 500

соответственно. Методами фотолитографии и ПХТ травления вскрывают окна в маскирующем слое нитрида кремния и двуокиси кремния, проводят травление канавок в кремнии на глубину 6,0 мкм, шириной 1,5 мкм. Формируют на стенках канавок слой диэлектрика 500  осаждают слой нитрида кремния 0,15 мкм и слой толстого поликремния толщиной 2,5 мкм с последующей его планаризацией до слоя нитрида кремния на поверхности. Удаляют с поверхности слой нитрида кремния и двуокиси кремния, формируют диэлектрик на поверхности вокруг базовых и коллекторных областей, через маску фоторезиста в соответствующем месте имплантируют бор с дозой 150 мккул/см2 для создания глубокого коллектора, осаждают слой поликремния толщиной 0,25 мкм, легируют поликремний фосфором с дозой 500 мккул/см2 с энергией 50 кэВ, осаждают на поликремний слой диэлектрика 0,3 мкм при 730 oC, обтравливают методами фотолитографии и ПХТ травления пятаки поликремния над базовой областью с одновременным травлением окна под эмиттер, осаждают и обтравливают RIT травлением с горизонтальных участков диэлектрик толщиной 0,3 мкм, формируют боковой диэлектрик на торцах поликремния (спейсеры), в эмиттерные окна формируют активную базу имплантацией фосфора с дозой 3 мккул/см2, осаждают второй слой поликремния 0,15 мкм, легируют его бором с дозой 500 мккул/см2 с энергией 20 кэВ и в процессе отжига формируют одновременно базу и эмиттер транзистора при 900oC.

осаждают слой нитрида кремния 0,15 мкм и слой толстого поликремния толщиной 2,5 мкм с последующей его планаризацией до слоя нитрида кремния на поверхности. Удаляют с поверхности слой нитрида кремния и двуокиси кремния, формируют диэлектрик на поверхности вокруг базовых и коллекторных областей, через маску фоторезиста в соответствующем месте имплантируют бор с дозой 150 мккул/см2 для создания глубокого коллектора, осаждают слой поликремния толщиной 0,25 мкм, легируют поликремний фосфором с дозой 500 мккул/см2 с энергией 50 кэВ, осаждают на поликремний слой диэлектрика 0,3 мкм при 730 oC, обтравливают методами фотолитографии и ПХТ травления пятаки поликремния над базовой областью с одновременным травлением окна под эмиттер, осаждают и обтравливают RIT травлением с горизонтальных участков диэлектрик толщиной 0,3 мкм, формируют боковой диэлектрик на торцах поликремния (спейсеры), в эмиттерные окна формируют активную базу имплантацией фосфора с дозой 3 мккул/см2, осаждают второй слой поликремния 0,15 мкм, легируют его бором с дозой 500 мккул/см2 с энергией 20 кэВ и в процессе отжига формируют одновременно базу и эмиттер транзистора при 900oC.

Пример, описанный выше, является частным случаем, в котором используется предлагаемый способ.

Предлагаемый способ может использоваться с другим методом боковой изоляции, например диэлектриком по типу изопланара, с транзистором, выполненным не по самосовмещенной технологии, без поликремния, по созданию комплементарных биполярных PNP и NPN транзисторов, по созданию КБиКМОТ транзисторов, везде где требуется создание скрытого коллектора с p+ типом проводимости с низким уровнем дефектности.

Литература

1. Pong-Fei Lu et al "The Design and Optimization of High Perfomance Double Poly Self-Aligned PNP Technology" IEEE Transactions on Electron. Devices v.38, N 6, 1991.

2. Патент США N 4855244, кл. H 01 L 21/265, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ БИКМОП СТРУКТУР | 1995 |

|

RU2106039C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИКМОП ПРИБОРА | 1998 |

|

RU2141148C1 |

| БИКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1996 |

|

RU2106719C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИПОЛЯРНОГО ТРАНЗИСТОРА | 1995 |

|

RU2099814C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИПОЛЯРНОГО ТРАНЗИСТОРА | 1995 |

|

RU2110868C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИКМОП СТРУКТУРЫ | 1998 |

|

RU2141149C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КОМПЛЕМЕНТАРНЫХ ВЕРТИКАЛЬНЫХ БИПОЛЯРНЫХ ТРАНЗИСТОРОВ В СОСТАВЕ ИНТЕГРАЛЬНЫХ СХЕМ | 2003 |

|

RU2244985C1 |

| БиКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2003 |

|

RU2282268C2 |

| СПОСОБ СОЗДАНИЯ СТРУКТУРЫ - КРЕМНИЙ НА ИЗОЛЯТОРЕ ДЛЯ СБИС (ВАРИАНТЫ) | 1998 |

|

RU2149481C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ АВТОМАСШТАБИРУЕМОЙ БИКМОП СТРУКТУРЫ | 2003 |

|

RU2234165C1 |

Использование: технология ИС на биполярных вертикальных PNP транзисторах. Сущность изобретения: способ изготовления вертикального PNP транзистора в составе ИС включает амортизацию приповерхностного слоя и его легирование примесью p - типа проводимости в месте будущего расположения скрытых слоев p+ типа проводимости в одном процессе имплантации примесью BF2, рекристаллизацию и отжиг аморфизированного слоя, осаждение эпитаксиального слоя, формирование боковой изоляции, создание диэлектрика на поверхности, формирование коллекторной области, создание базовой области транзистора, формирование эмиттера. 1 з.п. ф-лы, 7 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| US, патент США, 4855244, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Pong - Fei Lu et al | |||

| The Design and Optimization of High Perfomance Double Poly Self - Aligned PNP Technology | |||

| IEEE Transactions ou Electrou Devices | |||

| Способ сужения чугунных изделий | 1922 |

|

SU38A1 |

Авторы

Даты

1998-02-27—Публикация

1995-10-23—Подача