Изобретение относится к области микроэлектроники и может быть использовано для создания интегральных схем (ИС) большой степени интеграции.

Для успешного создания таких ИС необходимо уменьшать площадь, занимаемую как активными, так и пассивными компонентами, так как выход годных ИС обратно пропорционален площади ИС.

Известен вертикальный МДП транзистор ИС [1], в котором для уменьшения площади транзистора используются проводники из поликремния либо из силицидов металлов, самосовмещенные с областями стока, истока и затвора МДП транзистора. Уменьшение площади при этом достигается за счет устранения топологического запаса, компенсирующего точность совмещения проводников с контактными окнами.

Известен вертикальный МДП транзистор ИС, который использован в качестве наиболее близкого аналога [2]. Известный транзистор используется для схем большой плотности. Область затвора транзистора располагается на вертикальных стенках канавки, а проводник к области стока размещен на изолирующем затвор слое диэлектрика в канавке и совмещен с областью стока на дне канавки.

Недостатком прототипа является отсутствие третьего проводящего слоя, самосовмещенно присоединенного к области истока транзистора. Поэтому для реализации на такой структуре МДП транзистора требуется дополнительная площадь для контактного окна к этой области структуры.

Техническим результатом изобретения является увеличение плотности упаковки структуры транзистора интегральной схемы, а также увеличение быстродействия и радиационной стойкости. Технический результат изобретения достигается за счет того, что в вертикальном МДП транзисторе интегральной схемы, содержащем полупроводниковую подложку первого типа проводимости со сформированной структурой, окруженной изолирующей областью и состоящей из верхней и нижней областей второго типа проводимости, являющимися, соответственно областями истока и стока, и расположенной между ними подзатворной области первого типа проводимости, в структуре выполнена канавка с вертикальными стенками дно которой расположено в нижней области второго типа проводимости, на боковой поверхности канавки расположен изолированный затвор, а к областям истока и стока сформированы проводники, причем проводник к области стока размещен на изолированной диэлектриком поверхности затвора и совмещен с областью стока на дне канавки, размеры канавки в плане меньше наружных размеров структуры на величину равную удвоенной толщине проводника к области истока, изолирующая область сформирована на глубину превышающую суммарную толщину областей структуры, верхняя поверхность структуры углублена относительно изолирующей области на величину превышающую толщину проводника к области истока не менее чем в 1,5 раза, проводник к области истока расположен на поверхности изолирующей области и совмещен с областью истока его торцевой поверхностью.

Уменьшение площади транзисторной структуры ИС достигается тем, что во-первых, размеры контактов в плане к областям прибора равны размерам торцевых частей проводниковых слоев, во-вторых, проводящие слои присоединены к областям прибора самосовмещенно, т.е. расстояние между ними равно толщинам диэлектрических изолирующих слоев, в- третьих, проводящий слой, являющийся затвором, не имеет горизонтально расположенного участка на дне канавки.

Таким образом, размер транзистора определяется только суммарной толщиной всех изолирующих и проводящих слоев.

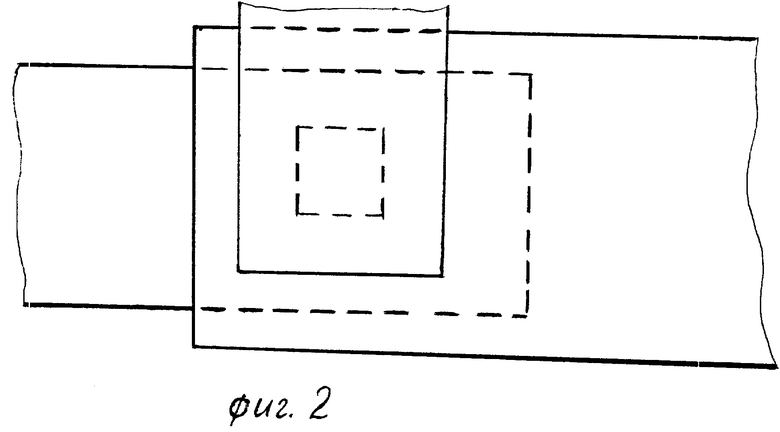

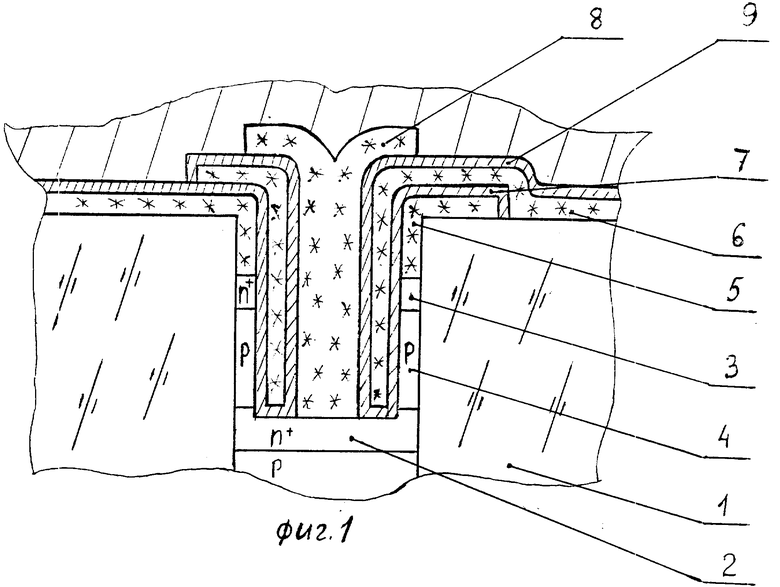

Разрез транзисторной структуры интегральной схемы по данному изобретению представлен на фиг.1. Вариант топологии транзистора приведен на фиг.2. В полупроводниковой структуре, окруженной изолирующей областью 1, расположены области стока 2 n-типа проводимости, истока 3 n-типа проводимости и подзатворная область 4 p -типа проводимости. В структуре выполнена канавка, дно которой расположено в области стока. Проводящий слой первого уровня 5 расположен на верхней и боковой поверхности изолирующей области 1 и присоединен к области истока торцевой частью. Диэлектрически изолированный проводящий слой второго уровня 6, являющийся затвором, частично расположен на проводящем слое первого уровня и примыкает к боковой вертикальной поверхности канавки. Слой диэлектрика 7 изолирует проводящий слой второго уровня от проводящего слоя первого уровня, стенок (являясь подзатворным диэлектриком) и дна канавки. Слой диэлектрика 9 изолирует проводящий слой треть его уровня от затвора.

Вертикальный МДП транзистор интегральной схемы выполнен в кремниевой пластине p-типа проводимости, в которой сформирована полупроводниковая структура, окруженная изолирующей областью 1. Верхняя поверхность структуры углублена относительно изолирующей области на 0,5 мкм. Проводник к области истока выполнен из поликристаллического кремния, легированного фосфором, толщиной 0,3 мкм.

Транзистор выполненный на данной структуре является транзистором с индуцированным каналом n-типа и работает следующим образом. Если к затвору не приложено напряжение, то транзистор закрыт. Если к затвору приложить достаточное положительное напряжение, то приповерхностный слой подзатворной области меняет тип проводимости, и, если между истоком и стоком имеется разность напряжений, канал будет проводить ток.

Описанная в данном изобретении транзисторная структура ИС может быть выполнена существующими технологическими методами. Канавка с вертикальными стенками может быть изготовлена методом плазмохимического травления, а изолирующие диэлектрические слои могут быть нанесены методом осаждения из газовой фазы.

Формирование структуры происходит в едином технологическом цикле с формированием трехслойной металлизации. В результате получается транзисторная структура ИС, размер которой определен суммарной толщиной всех изолирующих и проводящих слоев, что позволяет повысить плотность упаковки ИС, повысить радиационную стойкость и увеличить быстродействие.

ПРИМЕР.

Был изготовлен прибор на кремниевой подложке p-типа проводимости (концентрация примеси 1014 см-3, на которой были последовательно сформированы локальный скрытый слой n+-типа проводимости (концентрация примеси 1020 см-3, толщина 1,5 мкм) и эпитаксиальная пленка p-типа проводимости (концентрация примеси 1016 см-3, толщина 1,5 мкм).

С использованием планарной технологии была изготовлена щелевая изоляция активной области транзисторной структуры, глубина которой составила 3,5 мкм. Затем с использованием плазменного травления кремния было выполнено вертикальное углубление в меза-области на глубину 0,5 мкм. Для формирования поликремниевого контакта к области истока МОП транзистора были последовательно выполнены следующие технологические микроциклы:

а) осаждение слоя поликремния легированного мышьяком толщиной около 0,3 мкм с последующим осаждением на него слоя нитрида кремния толщиной 500  ,

,

б) нанесение слоя фоторезиста и его плазмохимическая планаризация до вскрытия слоя нитрида кремния, фоторезист при этом остается только в углублении,

в) селективное удаление слоя нитрида кремния с планарной поверхности при маскировании слоев расположенных в канавке оставшимся фоторезистом,

г) удаление фоторезиста и окисление слоя поликремния, немаскированного слоем нитрида на толщину 0,15 мкм,

д) плазменное анизотропное селективное к оксиду кремния удаление слоя нитрида кремния до вскрытия поликремния на дне канавки,

е) анизотропное плазмохимическое травление слоя поликремния, расположенного на дне канавки с последующим вертикальным травлением монокремния на глубину 1,5 мкм селективно к слоям оксида и нитрида кремния, маскирующим поликремний,

ж) формирование разводки первого уровня МОП транзистора выполняется с помощью фотолитографии и травления слоев окисла и поликремния на планарной поверхности структуры вне области канавки,

з) создание изоляции поликремниевой разводки первого уровня, а также подзатворного диэлектрика толщиной 300  с помощью низкотемпературного окисления открытых поверхностей монополикремния, при этом формируется кольцевая n+ область истока за счет диффузии мышьяка из первого слоя поликремния выполняющего функцию торцевого контакта к области истока.

с помощью низкотемпературного окисления открытых поверхностей монополикремния, при этом формируется кольцевая n+ область истока за счет диффузии мышьяка из первого слоя поликремния выполняющего функцию торцевого контакта к области истока.

Формирование поликремниевого электрода затвора и разводки на основе этого слоя выполняется аналогично созданию контакта к истоку. За исключение того, что после формирования электрода затвора проводится анизотропное травление слоя оксида кремния до вскрытия n+ области стока в канавке без последующего травления монокремния. Затем проводится формирование разводки второго уровня МОП транзистора с помощью фотолитографии и травления слоев окисла и поликремния на планарной поверхности структуры вне области канавки.

Для формирования контакта к области стока n+ типа на дне канавки, проводится конформное осаждение слоя легированного фосфором поликремния n+ типа проводимости с толщиной большей чем половина размера узкой части канавки, которая определяется после формирования электрода затвора.

Так при выбранных толщинах проводников с изоляцией, равных t1=t2=0,45 мкм, при исходном наименьшем размере канавке в плане равном d = 2 мкм, необходимая толщина слоя поликремния третьего уровня t3= (d-2t1- 2t2/2 и составила 0,1-0,15 мкм.

После формирования разводки поликремния третьего уровня, выполняемого аналогично созданию поликремниевой разводки первого и второго уровня, было проведено формирование контактных окон к поликремниевым проводникам и алюминиевая разводка. Эффективная длина канала изготовленного вертикального МОП транзистора составила 0,7 мкм, а площадь его активной области 4 мкм2 при минимальном литографическом размере 2 мкм.

| название | год | авторы | номер документа |

|---|---|---|---|

| БИПОЛЯРНЫЙ ТРАНЗИСТОР ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2108640C1 |

| КОМПЛЕМЕНТАРНАЯ БИПОЛЯРНАЯ ТРАНЗИСТОРНАЯ СТРУКТУРА ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2111578C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КМОП ТРАНЗИСТОРОВ С ПРИПОДНЯТЫМИ ЭЛЕКТРОДАМИ | 2006 |

|

RU2329566C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННЫХ ТРАНЗИСТОРНЫХ СТРУКТУР | 2008 |

|

RU2377691C1 |

| МАГНИТОЧУВСТВИТЕЛЬНЫЙ БИПОЛЯРНЫЙ ТРАНЗИСТОР | 1998 |

|

RU2127007C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПЛАНАРНОГО СИЛОВОГО МОП ТРАНЗИСТОРА | 2002 |

|

RU2239912C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ПЛАНАРНОГО ДВУХЗАТВОРНОГО МОП-ТРАНЗИСТОРА НА КНИ ПОДЛОЖКЕ | 2003 |

|

RU2312422C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО БиКМОП ПРИБОРА | 2005 |

|

RU2295800C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИПОЛЯРНОГО ТРАНЗИСТОРА | 2007 |

|

RU2351036C1 |

| ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ДОЛГОВРЕМЕННОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1990 |

|

RU2006965C1 |

Использование: микроэлектроника, интегральные схемы большой степени интеграции. Сущность изобретения: вертикальный МДП транзистор интегральной схемы содержит полупроводниковую подложку первого типа проводимости со сформированной на ней полупроводниковой структурой, окруженной изолирующей областью и состоящей из верхней и нижней областей второго типа проводимости, являющимися соответственно областями истока и стока, и расположенной между ними подзатворной области первого типа проводимости. В структуре выполнена канавка, дно которой расположено в нижней области второго типа проводимости, на боковой поверхности канавки расположен изолированный затвор, а размеры канавки в плане меньше размеров структуры на удвоенную толщину проводника к области истока. Верхняя поверхность структуры углублена относительно изолирующей области на ведичину, не менее чем в 1,5 превышающую толщину проводника к области истока, проводник к области истока расположен на поверхности изолирующей области и совмещен с областью истока торцевой поверхностью, а проводник к области стока размещен на изолированной диэлектриком поверхности затвора и совмещен с областью стока на дне канавки. Стенки выполнены вертикальными. 2 ил.

Вертикальный МДП-транзистор интегральной схемы, содержащий полупроводниковую подложку первого типа проводимости со сформированной структурой, окруженной изолирующей областью и состоящей из верхней и нижней областей второго типа проводимости, являющимися соответственно областями истока и стока, и расположенной между ними подзатворной области первого типа проводимости, в структуре выполнена канавка с вертикальными стенками, дно которой расположено в нижней области второго типа проводимости, на боковой поверхности канавки расположен изолированный затвор, а к областям истока и стока сформированы проводники, причем проводник к области стока размещен на изолированной диэлектриком поверхности затвора и совмещен с областью стока на дне канавки, отличающийся тем, что размеры канавка в плане меньше наружных размеров структуры на величину, равную удвоенной толщине проводника к области истока, изолирующая область сформирована на глубину, превышающую суммарную толщину областей структуры, верхняя поверхность структуры углублена относительно изолирующей области на величину, превышающую толщину проводника к области истока не менее, чем в полтора раза, проводник к области истока расположен на поверхности изолирующей области и совмещен с областью истока его торцевой поверхностью.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| US, патент, 4419810, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| US, патент 4683643, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1998-04-10—Публикация

1997-02-17—Подача