Изобретение относится к микроэлектронике и может быть использовано в полупроводниковых ИС в качестве элемента памяти.

Целью изобретения является повышение степени интеграции и надежности ячейки памяти.

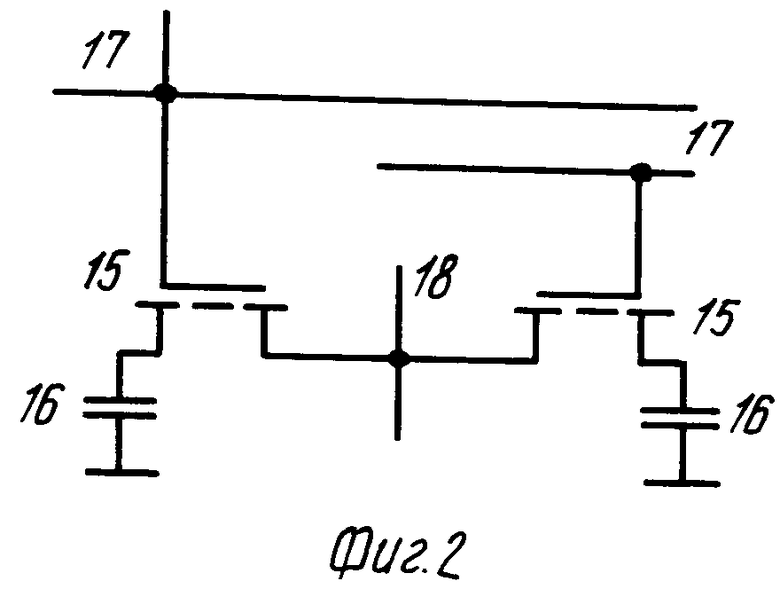

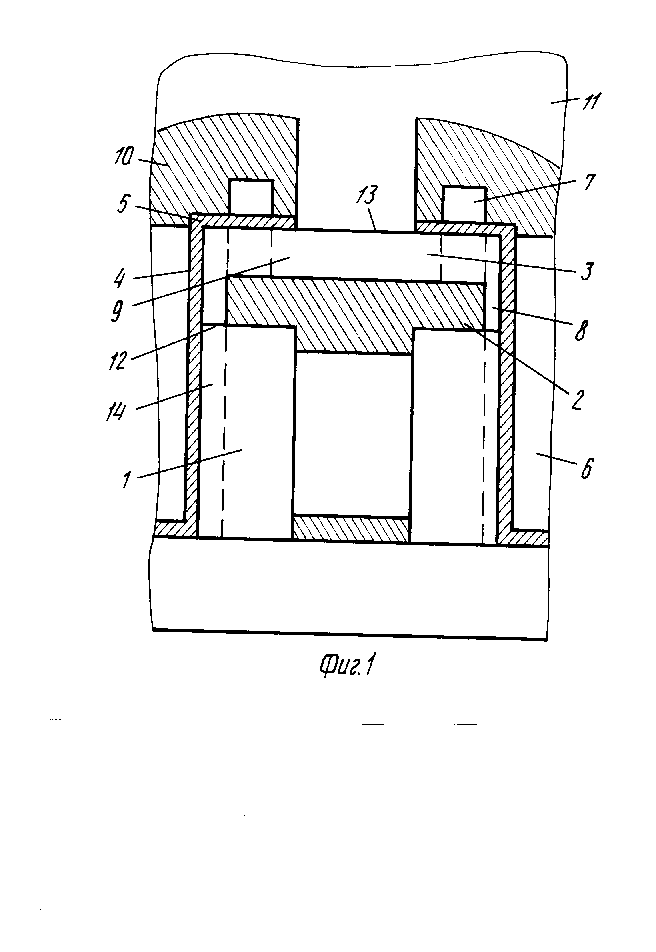

На фиг. 1 изображена структура элемента памяти; на фиг. 2 - электрическая схема.

Элемент памяти состоит из кремниевой подложки с легированным слоем 1, первого диэлектрического слоя 2 (окисел кремния), слоя 3 рекристаллизованного поликремния, третьего диэлектрического слоя (конденсаторный окисел) 4, второго диэлектрического слоя (подзатворного окисла) 5, канавок 6, заполненных поликремнием, поликремниевого затворного слоя 7, истоковой 8 и стоковой 9 областей, четвертого диэлектрического слоя 10, проводящего слоя 11, контактной области 12, области 13 контактирования между стоковой областью и проводящим слоем, сильно легированной области 14.

На фиг. 2 15 - МДП-транзистор, 16 - конденсаторы, 17 - затворы МДП-транзистора, 18 - разрядная шина.

Элемент памяти изготавливается следующим образом. В кремниевой подложке 1 формируются канавки 6 посредством селективного травления с последующим их заполнением поликремнием. Поверх осажденного слоя поликремния наносят слой нитрида кремния толщиной 0,1 мкм и с помощью фотолитографии формируют маску. Затем проводят окисление поликремния под маску нитрида кремния на величину, меньшую 1 мкм, при температуре 750oC в парах воды. После стравливания слоев Si3N4 и SiO2 проводят дополнительное окисление поликремния в режиме сильного окисления поликремния (Т = 750oC) в течение 30 мин. При этом поликремний окисляется на 0,5 мкм, а монокремний - на 0,1 мкм. Затем, стравливая SiO2 на 0,1 мкм, втравливаются области 12 к монокремнию, тем самым формируется контактная область между подложкой и рекристаллизованным поликремнием и осаждается поликремний толщиной 0,5 мкм, после чего с помощью лазерного нагрева осуществляют рекристаллизацию поликремния 3 при скоростях сканирования 20 см/с при температуре подложки 700oC и плотности мощности лазерного излучения 3,5 104Вт/см2. Далее канавки заполняются легированным поликремнием, осуществляют его стравливание на 2 мкм, после чего проводят отжиг при температуре 1000oC в течение 30 мин и формируют сильно легированную область 14 подложки с последующим удалением поликремния. Затем проводят окисление (Т = = 1000oC в течение 10 мин). При этом формируют подзатворный окисел кремния 5 и конденсаторный окисел кремния 4, в канавках осаждают поликремний толщиной 0,5 мкм и Si3N4 (0,1 мкм), после чего формируют маску и посредством вышеописанного окисления поликремния под маску формируют поликремниевый затворный слой 7 размером, меньшим 1 мкм. Формирование стоковых 9 и истоковых 8 областей осуществляют путем легирования Е = 100 кэВ. Далее формируют изоляцию (изолирующий слой 10 SiO2 толщиной 1 мкм), вскрывают контактное окно к области 13 стока посредством фотолитографии и формируют проводящий слой (металлический слой разводки) 11. (56) Вeem-Induced. Seeded hatemal Еpitaхy wеth suppressed Impritу Diffysion for athree - Dimensional Dram Cell Fabricatian. IЕЕЕ Тransadiens on election desices, vol. 36, N 2, February, 1989.

Memory Cell and Technology Issues for b4and 25GM bit one transistion cell MDSDhAM. Proc. of the IEEE, March, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИНАМИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

RU2029393C1 |

| ВЕРТИКАЛЬНЫЙ МДП-ТРАНЗИСТОР ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2108641C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СТРУКТУР КМОП БИС | 1992 |

|

RU2029414C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КМОП ТРАНЗИСТОРОВ С ПРИПОДНЯТЫМИ ЭЛЕКТРОДАМИ | 2006 |

|

RU2329566C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ПЛАНАРНОГО ДВУХЗАТВОРНОГО МОП-ТРАНЗИСТОРА НА КНИ ПОДЛОЖКЕ | 2003 |

|

RU2312422C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПЛАНАРНОГО СИЛОВОГО МОП ТРАНЗИСТОРА | 2002 |

|

RU2239912C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИС С ДВУХУРОВНЕВОЙ МЕТАЛЛИЗАЦИЕЙ | 1991 |

|

RU2022407C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА | 2010 |

|

RU2431905C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ LDMOS ТРАНЗИСТОРОВ | 2010 |

|

RU2439744C1 |

Изобретение относится к микроэлектронике и может быть использовано в полупроводниковых ИС в качестве элемента памяти. Целью изобретения является повышение степени интеграции и надежности ячейки памяти. Элемент памяти состоит из кремниевой подложки с легированным слоем 1, первого диэлектрического слоя 2, слоя 3 рекристаллизованного поликремния, третьего диэлектрического слоя 4, второго диэлектрического слоя 5, канавок 6, заполненных поликремнием, поликремниевого затворного слоя 7, истоковой 8 и стоковой 9 областей, четвертого диэлектрического слоя 10, проводящего слоя 11, контактной области 12, области 13 контактирования между стоковой областью и проводящим слоем, сильно легированной области 14. 2 ил.

ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ДОЛГОВРЕМЕННОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА, содержащий кремниевую подложку с канавками, слой поликремния, размещенный в канавках, первый диэлектрический слой, расположенный на слое поликремния и поверхности подложки, слой рекристаллизованного поликремния, образующего стоковую область, расположенный на первом диэлектрическом слое, истоковая область, расположенная на поверхности полупроводниковой подложки с примыканием к торцам первого диэлектрического и рекристаллизованного слоев и образующая проводящий контакт с подложкой, второй диэлектрический слой, расположенный на слое рекристаллизованного поликремния, третий диэлектрический слой, расположенный на поверхностях канавок, поликремниевый затворный слой, расположенный на втором диэлектрическом слое, четвертый диэлектрический слой, расположенный на поверхности поликремниевого затворного слоя, второго диэлектрического слоя и слоя поликремния, проводящий слой, расположенный на поверхностях третьего диэлектрического слоя и слоя рекристаллизованного поликремния и образующий проводящий контакт со стоковой областью, отличающийся тем, что, с целью повышения степени интеграции и надежности ячейки памяти, линейные размеры проводящего контакта между слоем рекристаллизованного поликремния и подложкой, а также слоя поликремниевого затвора выполнены на 0,1 - 0,5 мкм меньшими, чем линейные размеры проводящего контакта между стоковой областью слоя рекристаллизованного поликремния и проводящим слоем.

Авторы

Даты

1994-01-30—Публикация

1990-08-09—Подача