Изобретение относится к радиоэлектронике и может найти применение в устройствах генерирования сигналов синусоидальной формы, например, в качестве гетеродинов для преобразователей частоты или в составе синтезаторов частот килогерцового и низкочастотного диапазонов.

Аналогом предлагаемого устройства может служить "Схема для формирования синусоидальных колебаний" /1/, обеспечивающая цифровую генерацию напряжения синусоидальной формы при его апроксимации 16-ступенчатой периодической кривой и содержащая источник импульсов единицы счета fe, 4-разрядный двоичный счетчик импульсов МС 14024, логическую комбинационную схему МС 14030 из двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а также биполярный функционально-взвешенный преобразователь фазы в амплитуду на элементе МС 14051 с оконечным операционным усилителем и двумя разнополярными источниками напряжения.

Наиболее близок по технической сути к предлагаемому устройству генератор инфранизких частот /2/, содержащий генератор 1 прямоугольных импульсов единицы счета, четырехразрядный реверсивный счетчик 2 импульсов, диоды 3-6, подключающие выводы четырех весовых резисторов из набора 8-11 к (20-23)-выходам значащих разрядов счетчика импульсов, узел токов 7, включающий объединенные выводы весовых резисторов 8-11 и вывод балластного резистора 12, RS-триггер 13, обеспечивающий прямое и обратное направление счета при формировании каждой половины периода периодической кривой, счетный D-триггер 14, который, управляя коммутатором 16, последовательно переключает режимы работы операционного усилителя 15, формирующего квазисинусоиду, фильтр нижних частот 17, шину 18 выхода, резисторы 19, 20, 21 и элемент 22, служащий дешифратором нулевых состояний счетчика 2 импульсов, выходные импульсы которого задают положения нулей сигнала синусоидальной формы, формируемого аналоговой частью генератора.

В начале формирования каждого полупериода выпрямленной квазисинусоиды счетчик 2 импульсов находится в режиме прямого счета от исходного состояния 0000, которое вызвано установкой RS--триггера 13 в состояние "1" положительным импульсом, поступившим на S-вход с выхода элемента 22 ИЛИ-НЕ. В процессе счета на балластном резисторе 12 формируется ступенчато-возрастающее напряжение, соответствующее фронту полуволны квазисинусоиды, а напряжение, соответствующее спаду, - при переходе счетчика в режим обратного счета от промежуточного состояния 1000 до исходного 0000, после переключения RS-триггера 13 в состояние "0" положительным импульсом, поступившим на его R-вход с 23-выхода счетчика 2 импульсов.

Положительные импульсы, поступающие в начале каждого полупериода формируемых колебаний с выхода счетного D-триггера 14 на E-вход коммутатора 16, подключают сигнальный вывод балластного резистора 12 к неинвертирующему входу операционного усилителя 15, работающего в режиме повторителя. При этом на его выходе формируются положительные полуволны квазисинусоидальной кривой. Отрицательные же полуволны формируются на выходе операционного усилителя 15 при закрытом коммутаторе 16, когда оставшаяся половина импульсов, с сигнального выхода балластного резистора 12 управляет его инвертирующим входом с учетом действия цепи обратной связи R20/R19.

Сформированный сигнал квазисинусоидальной формы, сглаженный фильтром 17 нижних частот, поступает на шину 18 выхода устройства.

Рассмотренный прототип /2/ является устройством с ограниченным быстродействием, повышение диапазона рабочих частот которого упирается в технические ограничения, присущие реверсивному счетчику 2 импульсов с последовательной цепью элементов управления направлением счета. В такой структуре, использующей позиционный двоичный код (ПДК), при непрерывном съеме данных набором весовых резисторов 8-11 и дешифратором 22 нулевого состояния счетчика на сигнальном выводе балластного резистора 12 и выходе элемента 22 возникают коммутационные помехи малой длительности - "иголки", порождаемые явлениями сквозного переноса единицы счета в счетчике импульсов и переключениями направления счета без его останова.

Уровень названных помех заметно возрастает при необходимости использования элементной базы повышенного быстродействия, а нейтрализация из воздействия потребует дополнительных технических решений, усложняющих устройство.

Цель изобретения - повышение диапазона рабочих частот дискретно-аналогового устройства при улучшении формы генерируемых колебаний за счет исключения помех коммутации и снижения относительной доли шумов квантования.

Достижение цели опирается на специфические свойства кода Грея, используемого четырехрядным счетчиком импульсов для подсчета 32-х единичных интервалов, составляющих в сумме половину периода сигнала синусоидальной формы.

Во время прямого и отраженного циклов счета происходит формирование каждой половины квазисинусоиды, когда 7 выходов значащих разрядов счетчика импульсов поразрядно управляют семью сигнальными входами логической комбинационной структуры, которая формирует набор из восьми последовательностей импульсов, каждая из которых во время своей положительной фазы последовательно подключает к балластному резистору соответствующий функционально-взвешенный источник тока, а результат суммирования токов представляет последовательность импульсов напряжения ступенчатой формы в виде положительных полуволн выпрямленной квазисинусоиды, с шагами диокретизации, кратными π/32 , где временной интервал, соответствующий π/32 является единицей счета.

Использование синхронного счетчика импульсов в коде Грея для поразрядного управления сигнальными входами комбинационной структуры, которая формирует набор из восьми осесимметричных последовательностей импульсов, образующих своеобразную "пирамиду", и положительная фаза каждой из которых определяет время подключения соответствующего источника тока из аналоговой части устройства, обусловлено следующими соображениями:

1. Так как код Грея обладает единичным кодом расстоянием, каждое приращение единицы счета вызывает изменение состояния только одного разряда счетчика импульсов, то этим принципиально исключается возникновение помех коммутации - "иголок" на выходах элементов совпадения вследствие исключения совпадений разнополярных перепадов на их входах.

2. При подсчете 2n-ой единицы счета, поступившей на вход n-разрядного счетчика, в его структуре создаются условия для формирования сигнала переноса в предполагаемый (n+1)-й разряд, а все n младших разрядов остаются в состоянии отраженного счета при его продолжении до состояния 100...0, числовое значение которого -(2n+1-1).

Названная выше особенность кода используется четырехразрядным синхронным счетчиком импульсов для непрерывного подсчета 32-х импульсов единицы счета за время прямого и отраженного циклов счета.

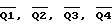

При формировании каждой полуволны квазисинусоиды с основанием в 32 единичных интервала состояние четырех значащих разрядов счетчика импульсов изменяется следующим образом: * 0000(0), * 0001(1), * 0011(2), ... прямой счет до * 1000(15), * 1000(16), далее отраженный счет от * 1000(15) до * 0000(0), где в скобках приведены числовые значения текущего состояния четырех разрядов счетчика импульсов без учета исключаемого пятого, обозначенного символом - *.

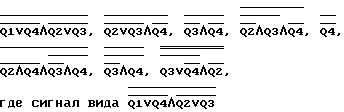

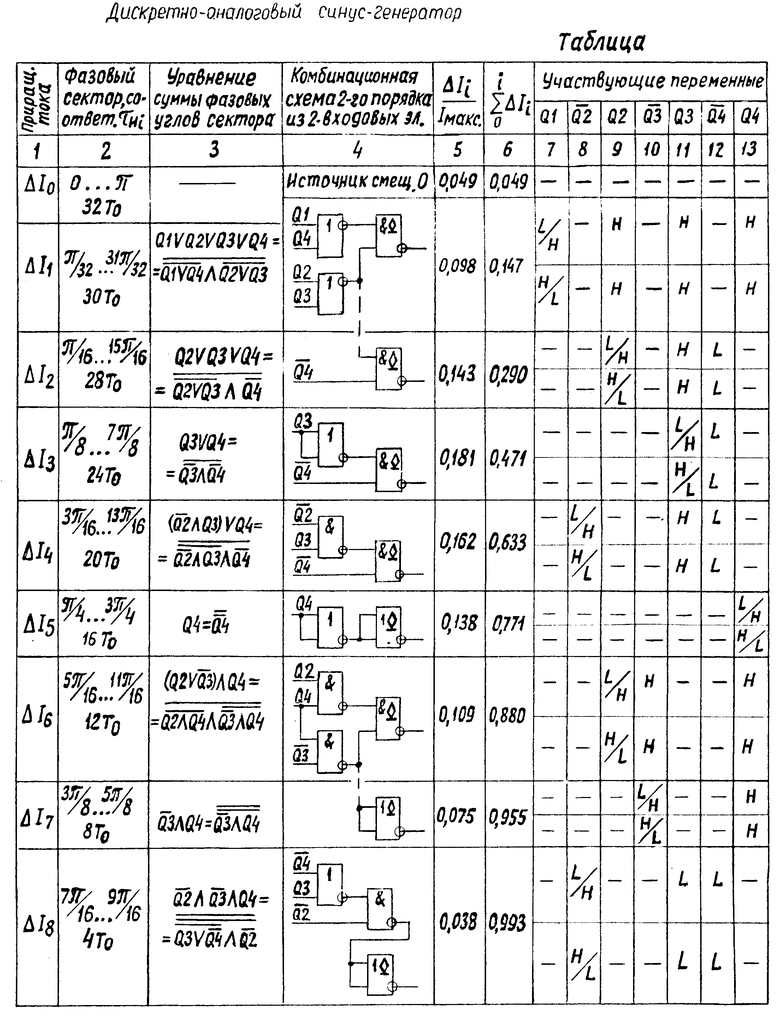

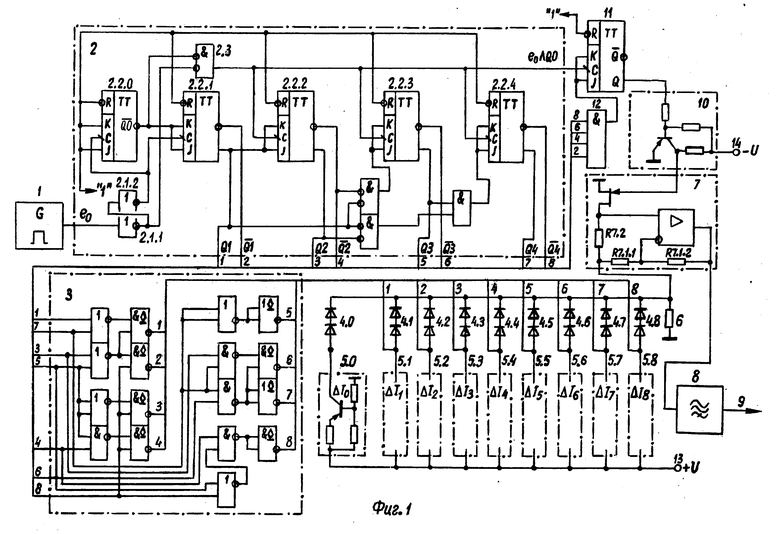

На фиг. 1 приведена электрическая принципиальная схема устройства; на фиг. 2 - временные соотношения, поясняющие ее работу; а используемые логические уравнения, расчетные количественные соотношения и логические перемещенные, участвующие в процессе дискретно-аналогового преобразования, сведены в таблицу, приводимую в описании.

Таблица включает 9 строк, в каждой из которых аргументом служит текущее приращение тока ΔIi , действующее внутри соответствующего фазового сектора полуволны формируемой квазисинусоиды.

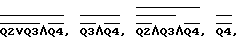

В столбце 3 таблицы приведены 8 исходных логических уравнений, описывающих каждый из фазовых секторов определенной длительности τi , а также варианты этих уравнений, преобразованные для выполнения операций только двухвходовыми элементами.

В столбце 4 таблицы приведены 8 комбинационных схем второго порядка для граничных перепадов потенциала L/H и H/L, образующих 8 положительных импульсов, составляющих "пирамиду", как практический пример реализации функций, описываемых преобразованными уравнениями столбца 3 таблицы.

Эти 8 комбинационных схем, объединенные одноименными сигнальными входами, образуют комбинационный блок логических элементов 3 (фиг. 1) второго порядка для названных перепадов потенциала с семью сигнальными входами и восьмью параллельными выходами.

Каждый из его выходов, представляющий вывод открытого коллектора транзистора оконечного элемента, который в соединении с анодом соответствующей пары диодов из параллельного набора 4.1-4.8 образует один из восьми переключателей тока, который соединен с выходом соответствующего генератора тока из параллельного набора 5.1-5.8.

Дискретно-аналоговый синус-генератор (фиг. 1) содержит генератор G 1 импульсов единицы счета, выход которого соединен с e0-входом счетчика импульсов 2, комбинационный блок логических элементов 3, который снабжен семью 1, 3, 4-8 сигнальными входами и восемью 1-8 выходами, 9 пар диодов 4.0-4.8, у каждой из которых катод первого диода соединен с анодом втором диода, 9 генераторов тока 5.0-5.8, входы которых объединены и подключены к источнику напряжения "+U" 13, балластный резистор 6, второй выход которого подключен к общей шине, коммутаторе 7, выход которого соединен со входом фильтра нижних частот 8, инвертор полярности и знака 10, ввод электропитания которого подключен к источнику напряжения "минус U" 14, управляющий JK-триггер 11 и элемент совпадения 4И 12, выход которого соединен с J и K-входами управляющего JK-триггера, Q-выход которого соединен со входом инвертора полярности и знака, выход которого соединен со вторым входом коммутатора, первый вход которого подключен к первому выводу балластного резистора и к девяти катодам, которые объединены, вторых диодов девяти 4.0-4.8 пар диодов, а анод первого диода каждой пары диодов, с первой 4.0 по девятую 4.8, соединен с выходом соответствующего генератора тока, с первого 5.0 по девятый 5.8, и выход фильтра нижних частот подключен к шине выхода 9 дискретно-аналогового синус-генератора, при этом счетчик импульсов 2 выполнен в виде четырехразрядного синхронного счетчика импульсов в коде Грея без предустановки исходного состояния и снабжен восемью  выходами значащих разрядов и e0 Λ QO-выходом синхронизации, который соединен с C-входом управляющего JK-триггера 11, а первый 1 сигнальный вход комбинационного блока логических элементов 3 соединен с Q1-выходом первого разряда счетчика импульсов, второй 7 сигнальный вход комбинационного блока логических элементов соединен с Q4-выходом четвертого разряда счетчика импульсов, третий 3 сигнальный вход комбинационного блока логических элементов соединен с Q2-выходом второго разряда счетчика импульсов, четвертый 5 сигнальный вход комбинационного блока логических элементов соединен с Q3-выходом третьего разряда счетчика импульсов, пятый 4 сигнальный вход комбинационного блока логических элементов подключен к

выходами значащих разрядов и e0 Λ QO-выходом синхронизации, который соединен с C-входом управляющего JK-триггера 11, а первый 1 сигнальный вход комбинационного блока логических элементов 3 соединен с Q1-выходом первого разряда счетчика импульсов, второй 7 сигнальный вход комбинационного блока логических элементов соединен с Q4-выходом четвертого разряда счетчика импульсов, третий 3 сигнальный вход комбинационного блока логических элементов соединен с Q2-выходом второго разряда счетчика импульсов, четвертый 5 сигнальный вход комбинационного блока логических элементов соединен с Q3-выходом третьего разряда счетчика импульсов, пятый 4 сигнальный вход комбинационного блока логических элементов подключен к  второго разряда счетчика импульсов, шестой 6 сигнальный вход комбинационного блока логических элементов подключен к

второго разряда счетчика импульсов, шестой 6 сигнальный вход комбинационного блока логических элементов подключен к  третьего разряда счетчика импульсов, седьмой 8 сигнальный вход комбинационного блока логических элементов подключен к

третьего разряда счетчика импульсов, седьмой 8 сигнальный вход комбинационного блока логических элементов подключен к  четвертого разряда счетчика импульсов, а первый, второй, третий и четвертый входы элемента совпадения 4И подключены соответственно к

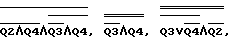

четвертого разряда счетчика импульсов, а первый, второй, третий и четвертый входы элемента совпадения 4И подключены соответственно к  выходам соответствующих разрядов счетчика импульсов, величины токов девяти генераторов тока, с первого 5.0 по девятый 5.8 в порядке перечисления, функционально взвешены в соотношении с единицей, которой соответствует максимальное значение тока синусоидальной формы, как 0,049, 0,098, 0,143, 0,181, 0,162, 0,138, 0,109, 0,075, 0,038, а комбинационный блок логических элементов выполнен в виде комбинационного блока логических элементов с восемью выходами в соответствии с выражениями

выходам соответствующих разрядов счетчика импульсов, величины токов девяти генераторов тока, с первого 5.0 по девятый 5.8 в порядке перечисления, функционально взвешены в соотношении с единицей, которой соответствует максимальное значение тока синусоидальной формы, как 0,049, 0,098, 0,143, 0,181, 0,162, 0,138, 0,109, 0,075, 0,038, а комбинационный блок логических элементов выполнен в виде комбинационного блока логических элементов с восемью выходами в соответствии с выражениями  соответствует первому 1 выходу, который подключен к выходу второго 5.1 генератора тока, сигнала вида

соответствует первому 1 выходу, который подключен к выходу второго 5.1 генератора тока, сигнала вида  соответствует второму 2 выходу, который подключен к выходу третьего 5.2 генератора тока, сигнал вида

соответствует второму 2 выходу, который подключен к выходу третьего 5.2 генератора тока, сигнал вида  соответствует третьему 3 выходу, который подключен к выходу четвертого 5.3 генератора тока, сигнал вида

соответствует третьему 3 выходу, который подключен к выходу четвертого 5.3 генератора тока, сигнал вида  соответствует четвертому 4 выходу, который подключен к выходу пятого 5.4 генератора тока, сигнал вида

соответствует четвертому 4 выходу, который подключен к выходу пятого 5.4 генератора тока, сигнал вида  соответствует пятому 5 выходу, который подключен к выходу шестого 5.5. генератора тока, сигнал вида

соответствует пятому 5 выходу, который подключен к выходу шестого 5.5. генератора тока, сигнал вида  соответствует шестому 6 выходу, который подключен к выходу седьмого 5.6 генератора тока, сигнал вида

соответствует шестому 6 выходу, который подключен к выходу седьмого 5.6 генератора тока, сигнал вида  соответствует седьмому 7 выходу, который подключен к выходу восьмого 5.7 генератора тока, сигнал вида

соответствует седьмому 7 выходу, который подключен к выходу восьмого 5.7 генератора тока, сигнал вида  соответствует восьмому 8 выходу, который подключен к выходу девятого 5.8 генератора тока.

соответствует восьмому 8 выходу, который подключен к выходу девятого 5.8 генератора тока.

Работа синус-генератора (фиг. 1 и 2) рассматривается на примере формирования одного периода колебаний квазисинусоиды (Вых.7 фиг.2) от 0 до 2π за два подсчета счетчиком импульсов 2 64-х единичных интервалов (e0 фиг. 2). Каждый из полупериодов в 32 интервала формируется при прямом счете от 0 до 16 и отраженном от 16 до второго 0 (Q1, Q2, Q3, Q4 фиг. 2).

Импульсы единицы счета с выхода генератора G1 непрерывно поступают на e0-вход четырехразрядного синхронного счетчика импульсов 2, схема которого и элементами межразрядной связи и цепью синхронизации элементов 2.2.0-2.2.4 счета как пример выполнения аналогична схеме известного счетчика импульсов, использованного в синхронном делителе частоты 3.

При формировании каждой из полуволн квазисинусоиды (Вх. 7 фиг. 2) четыре значащих разряда Q1, Q2, Q3, Q4 счетчика импульсов последовательно переходят из режима прямого в режим отраженного счета.

Примем за исходное состояние устройства, совпадающее с первым нулем положительной полуволны квазисинусоиды (Вых. 7 фиг. 2).

При поступлении на e0-вход импульса нуля счета (e0 фиг.2), одновременно на C-выход управляющего JK-триггера 11 с e0 Λ QO-выхода счетчика импульсов 2 поступает совпадающий с ним импульс синхронизации (eo Λ QO фиг. 2) с периодом следования 2T0, который переключает управляющий JK-триггер в состояние "единица" (Вых. 11 фиг. 2), так как его J и K-входы. с конца предшествовавшего отраженного цикла счета, были открыты строб-импульсом нуля (Вых. 12 фиг. 2), формируемого элементом совпадения 4И 12, когда значащие разряды Q4, Q3, Q2, Q1 счетчика импульсов в течение двух периодов счета 2•T0 находились в состоянии 0000.

Положительный импульс (Вых. 11 фиг. 2) с Q-выхода управляющего JK-триггера 11 поступает на вход инвертора полярности и знака 10, а сформированный импульс (вых. 10 фиг. 2) отрицательного уровня и полярности с его выхода поступает на второй (управляющий) вход коммутатора 7, представленного как пример выполнения известной схемой со сменой знака выходного напряжения 4 на полевом транзисторе с операционным усилителем (ОУ).

При селектировании нулевого импульса последовательности e0 Λ QO (фиг. 2) строб-импульсом нуля (Вых.12 фиг. 2) с длительностью, равной двум периодам единицы счета, когда JK-триггеры 2.2.1-2.2.4 значащих разрядов счетчика импульсов находятся в состоянии 0000, на каждом из восьми выходов 1-8 комбинационного блока логических элементов 3 присутствует потенциал насыщения малого уровня (около 0,4В). На это время заперты диоды восьми пар диодов 4.1-4.8, и на сигнальном выходе балластного резистора 6 (Вх. 7 фиг.2) присутствует только напряжение смещения нуля, создаваемое током ΔIo генератора 5.0, включенным последовательно с анодом компенсационной пары диодов 4.0, а ток ΔIi каждого и восьми генераторов тока 5.1-5.8 стекает в общую шину через насыщенный переход К-Э открытого транзистора одного из выходов 1-8 комбинационного блока логических элементов.

При поступлении на e0-вход (e0 фиг. 2) счетчика импульсов 2 первого, второго, четвертого, шестого, восьмого, десятого, двенадцатого и четырнадцатого импульсов единицы счета, синфазно, с одинаковой естественной задержкой закрываются транзисторы первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого оконечных элементов комбинационного блока логических элементов. При этом происходит ступенчатое формирование фронта первой полуволны квазисинусоиды (Вх. фиг. 2) от уровня смещенного нуля 0,049 до максимального значения 0,993 за счет последовательного подключения к балластному резистору 6 каждого из восьми 5.1-5.8 функционально-взвешенных генераторов тока ΔI1-ΔI8 при последовательном отпирании каждой из пар диодов набора 4.1-4.8.

С поступлением на e0-вход счетчика импульсов 2 шестнадцатого импульса единицы счета прекращается прямой счет и заканчивается формирование фронта первой полуволны квазисинусоиды.

Во время отраженного цикла, при поступлении четырнадцатого, двенадцатого, десятого, восьмого, шестого, четвертого, второго и первого импульсов единицы счета, в обратной последовательности открываются транзисторы оконечных элементов на 8-1 выходах комбинационного блока логических элементов, последовательно запираются пары диодов из набора 4.8-4.1, отключая от балластного резистора 6 генератор тока 5.8-5.1.

С поступлением на e0-вход счетчика импульсов синхроимпульса второго нуля заканчивается формирование первой полуволны квазисинусоиды (Вх. фиг. 2), а затем происходит формирование второй полуволны, начиная с уровня смещенного нуля отсчета амплитуды.

Обе сформированные полуволны выпрямленной квазисинусоиды с основаниями π (Вх. 7 фиг. 2) присутствуют на первом входе коммутатора 7, когда на его выходе формируется ступенчатый сигнал (Вых. 7 фиг 2) синусоидальной формы при управлении его фазой с помощью сигнала, формируемого инвертором полярности и знака 10.

В первой половины периода от 0 до π импульс (Вых. 10 фиг. 2) отрицательного уровня, поступающий с выхода инвертора полярности и знака 10 на второй (управляющий) вход коммутатора 7, выключает его полевой транзистор.

При этом к неинвертирующему входу ОУ, который переводится в режим повторителя, синхронно подключается первая полуволна выпрямленной квизисинусоиды (Вх. фиг. 2), и на выходе коммутатора (Вых. 7 фиг. 2) появляется положительная волуволна квазисинусоида.

При формировании отрицательной полуволны квазисинусоиды от π до 2π управляющий JK-триггер 11 переключается в состояние "нуль" синхроимпульсом последовательности (e0 Λ QO фиг. 2), поступавшим на C-вход в момент второго нуля.

При этом нулевой потенциал с его Q-выхода инвертируется в нулевой потенциал на выходе инвертора полярности и знака 10 (Вых.10 фиг. 2), который включает полевой транзистор коммутатора 7, подключая через насыщенный переход ИСТОК-СТОК к общей шине неинвестирующий вход ОУ.

Так как сигнальный вывод балластного резистора 6 постоянно соединен через первый резистор цепи обратной связи с инвертирующим входом ОУ, то на выходе коммутатора в этом полупериоде формируется отрицательная полуволна квазисинусоиды.

При формировании следующих периодов сигнала синусоидальной формы описанный процесс многократно повторяется.

Фильтр нижних частот 8 на выходе устройства сглаживает форму ступенчатоменяющегося квазисинусоидального напряжения, полученную в результате дискретизации и квантования.

Предлагаемый дискретно-аналоговый синус-генератор позволяет повысить диапазоны рабочих частот при улучшении формы генерируемых колебаний с периодом повторения T=64•T0, где T0 - период следования импульсов единицы счета, за счет исключения помех коммутации, порождаемых элементами счетной схемы реализованной в прототипе; обеспечения комбинационным блоком логических элементов одинаковой естественной задержки граничных перепадов L/H и H/L потенциала, ограничивающих ширину каждого из используемых фазовых секторов; использования аналоговой частью устройства известного способа дискретно-аналогового преобразования фазы в амплитуду с помощью параллельного набора из восьми переключаемых функционально-взвешенных генераторов стабильных токов с суммирующим элементом на выходе.

Литература:

1. Титце., Шек К. Полупроводниковая схемотехника: Пер. с нем. - М.: Мир, 1982, Рис.24.19, стр. 454.

2. SU, 1358062, AI, 4 H 03 B 19/12, H 03 K 4/92, В.Ф.Воропаев, генератор инфранизких частот, 621.374(88.8), 7.12.87. Бюл. N 45.

3. РФ, патент N 2037957, 6 H 03 K 23/42, Синхронный делитель частоты, В. А.Островский, 1995. Бюл. N 17, Заявка N 5065077/10 от 20.07.92 г.

4. Титце, Шенк К. Полупроводниковая схемотехника: Пер. с нем. - М.: Мир, 1982, Рис. 17.14, стр. 282.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ СРАБАТЫВАНИЯ БЛОКОВ ЗАЩИТЫ ЭЛЕКТРОПИТАНИЯ | 1992 |

|

RU2093941C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКИ УСИЛЕНИЯ | 1994 |

|

RU2089040C1 |

| СПОСОБ УПРАВЛЕНИЯ ПРЕОБРАЗОВАТЕЛЕМ ЧАСТОТЫ | 1999 |

|

RU2159497C1 |

| УСТРОЙСТВО СТАБИЛИЗАЦИИ УРОВНЯ СИГНАЛА ТЕЛЕВИЗИОННОГО ПЕРЕДАТЧИКА | 1993 |

|

RU2072636C1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ЧЕТЫРЕХФАЗНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ | 1998 |

|

RU2133550C1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ | 1999 |

|

RU2155432C1 |

| СПОСОБ УПРАВЛЕНИЯ РЕЗОНАНСНЫМ ИНВЕРТОРОМ СО ВСТРЕЧНО-ПАРАЛЛЕЛЬНЫМИ ДИОДАМИ | 1999 |

|

RU2152683C1 |

| СПОСОБ УПРАВЛЕНИЯ РЕЗОНАНСНЫМ ИНВЕРТОРОМ СО ВСТРЕЧНО-ПАРАЛЛЕЛЬНЫМИ ДИОДАМИ | 1997 |

|

RU2117378C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКИ УСИЛЕНИЯ (ВАРИАНТЫ) | 1994 |

|

RU2089039C1 |

Изобретение относится к радиоэлектронике и может найти применение в устройствах генерирования напряжения синусоидальной формы, например, в качестве гетеродинов для преобразователей частоты или в составе синтезаторов частот килогерцевого и низкочастотного диапазонов. Цель изобретения - повышение диапазона рабочих частот при улучшении формы генерируемых колебаний за счет исключения помех коммутации и снижения относительной доли шумов квантования и и дискретизации. Достижение цели опирается на специфические свойства кода Грея, используемого четырехразрядным счетчиком импульсов 2 в коде Грея для подсчета 32-х единичных интервалов, составляющих половину периода напряжения синусоидальной формы. Во время и "отраженного" циклов счета происходит формирование каждой из полуволны выпрямленной квазисинусоиды, когда 7 импульсных последовательностей с выходов четырех IK-триггеров значащих разрядов счетчика импульсов управляют сигнальными входами комбинационного блока логических элементов 3, который формирует набор из восьми импульсных последовательностей, каждая из которых во время положительной фазы подключает к балластному резистору 6 соответствующий функционально-взвешенный источник тока 5.1 - 5.8, а результат суммирования представляет последовательность импульсов выпрямленной квазисинусоиды, последовательно коммутируемых через полпериода при преобразовании в сигнал квазисинусоидальной формы. Дискретно-аналоговый синус-генератор содержит генератор G импульсов единицы счета 1, четырехразрядный счетчик импульсов 2, комбинационный блок логических элементов 3, выходы 1 - 8 восьми оконечных элементов которого соединены с анодами соответствующих пар диодов 4.1 - 4.8, образуя с ними набор из восьми переключателей тока для 8 выходов функционально-взвешенных источников тока 5.1 - 5.8, источник тока 5.0 смещения нуля с компенсационной парой диодов 4.0, балластный резистор 6, коммутатор 7, фильтр нижних частот 8, шину выхода 9, инвертор полярности и знака 10, управляющий IK-триггер 11, элемент совпадения 4И и 12 и два источника напряжения 13 и 14. 2 ил., 1 табл.

Дискретно-аналоговый синус-генератор, содержащий генератор импульсов единиц счета, выход которого соединен с l0-входом счетчика импульсов, комбинационный блок логических элементов, который снабжен семью сигнальными входами и восемью выходами, девять пар диодов, у каждой из которых катод первого диода соединен с анодом второго диода, девять генераторов тока, входы которых объединены и подключены к источнику напряжения "+U", балластный резистор, второй вывод которого подключен к общей шине, коммутатор, выход которого соединен с входом фильтра нижних частот, инвертор полярности и знака, ввод электропитания которого подключен к источнику напряжения "-U", управляющий JK-триггер и элемент совпадения 4И, выход которого соединен с J и K-входами управляющего JK-триггера, Q-выход которого соединен с входом инвертора полярности и знака, выход которого соединен с вторым входом коммутатора, первый вход которого подключен к первому выводу балластного резистора и к девяти катодам, которые объединены, вторых диодов девяти пар диодов, а анод первого диода каждой пары диодов, с первой по девятую, соединен с выходом соответствующего генератора тока, с первого по девятый, и выход фильтра нижних частот подключен к шине выхода дискретно-аналогового синус-генератора, отличающийся тем, что счетчик импульсов выполнен в виде четырехразрядного синхронного счетчика импульсов в коде Грея без предустановки исходного состояния и снабжен восемью Q1,  Q2,

Q2,  Q3

Q3  Q4

Q4  выходами значащих разрядов и l0ΛQO-выходом синхронизации, который соединен с С-входом управляющего JK-триггера, а первый сигнальный вход комбинационного блока логических элементов соединен с Q1-выходом первого разряда счетчика импульсов, второй сигнальный вход комбинационного блока логических элементов соединен с Q4-выходом четвертого разряда счетчика импульсов, третий сигнальный вход комбинационного блока логических элементов соединен с Q2-выходом второго разряда счетчика импульсов, четвертый сигнальный вход комбинационного блока логических элементов соединен с Q3-выходом третьего разряда счетчика импульсов, пятый сигнальный вход комбинационного блока логических элементов подключен к

выходами значащих разрядов и l0ΛQO-выходом синхронизации, который соединен с С-входом управляющего JK-триггера, а первый сигнальный вход комбинационного блока логических элементов соединен с Q1-выходом первого разряда счетчика импульсов, второй сигнальный вход комбинационного блока логических элементов соединен с Q4-выходом четвертого разряда счетчика импульсов, третий сигнальный вход комбинационного блока логических элементов соединен с Q2-выходом второго разряда счетчика импульсов, четвертый сигнальный вход комбинационного блока логических элементов соединен с Q3-выходом третьего разряда счетчика импульсов, пятый сигнальный вход комбинационного блока логических элементов подключен к  выходу второго разряда счетчика импульсов, шестой сигнальный вход комбинационного блока логических элементов подключен к

выходу второго разряда счетчика импульсов, шестой сигнальный вход комбинационного блока логических элементов подключен к  выходу третьего разряда счетчика импульсов, седьмой сигнальный вход комбинационного блока логических элементов подключен к

выходу третьего разряда счетчика импульсов, седьмой сигнальный вход комбинационного блока логических элементов подключен к  выходу четвертого разряда счетчика импульсов, а первый, второй, третий и четвертый входы элемента совпадения 4И подключены соответственно к

выходу четвертого разряда счетчика импульсов, а первый, второй, третий и четвертый входы элемента совпадения 4И подключены соответственно к  выходам соответствующих разрядов счетчика импульсов, величины токов девяти генераторов тока, с первого по девятый в порядке перечисления, функционально взвешены в соотношении с единицей, которой соответствует максимальное значение тока синусоидальной формы, как 0,049, 0,098, 0,143, 0,181, 0,162, 0,138, 0,109, 0,075, 0,038, а комбинационный блок логических элементов выполнен в виде комбинационного блока логических элементов с восемью выходами в соответствии с выражениями

выходам соответствующих разрядов счетчика импульсов, величины токов девяти генераторов тока, с первого по девятый в порядке перечисления, функционально взвешены в соотношении с единицей, которой соответствует максимальное значение тока синусоидальной формы, как 0,049, 0,098, 0,143, 0,181, 0,162, 0,138, 0,109, 0,075, 0,038, а комбинационный блок логических элементов выполнен в виде комбинационного блока логических элементов с восемью выходами в соответствии с выражениями

где сигнал вида

где сигнал вида  соответствует первому выходу, который подключен к выходу второго генератора тока, сигнал вида

соответствует первому выходу, который подключен к выходу второго генератора тока, сигнал вида  соответствует второму выходу, который подключен к выходу третьего генератора тока, сигнал вида

соответствует второму выходу, который подключен к выходу третьего генератора тока, сигнал вида  соответствует третьему выходу, который подключен к выходу четвертого генератора тока, сигнал вида

соответствует третьему выходу, который подключен к выходу четвертого генератора тока, сигнал вида  соответствует четвертому выходу, который подключен к выходу пятого генератора тока, сигнал вида

соответствует четвертому выходу, который подключен к выходу пятого генератора тока, сигнал вида  соответствует пятому выходу, который подключен к выходу шестого генератора тока, сигнал вида

соответствует пятому выходу, который подключен к выходу шестого генератора тока, сигнал вида  соответствует шестому выходу, который подключен к выходу седьмого генератора тока, сигнал вида

соответствует шестому выходу, который подключен к выходу седьмого генератора тока, сигнал вида  соответствует седьмому выходу, который подключен к выходу восьмого генератора тока, сигнал вида

соответствует седьмому выходу, который подключен к выходу восьмого генератора тока, сигнал вида  соответствует восьмому выходу, который подключен к выходу девятого генератора тока.

соответствует восьмому выходу, который подключен к выходу девятого генератора тока.

| Титце У., Шенк К | |||

| Полупроводниковая схемотехника./Перевод с нем | |||

| под ред.Алексенко А.Г | |||

| - М.: Мир, 1983, с.454 | |||

| SU, авторское свидетельство, 1358062, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1998-04-10—Публикация

1995-07-06—Подача