Изобретение относится к дискретной импульсной технике, а именно к специализированным пересчетным схемам, и может использоваться для формирования точных интервалов времени в устройствах различного назначения, например в синхронизаторах или генераторах дискретного множества частот.

Одним из аналогов предлагаемого устройства может служить делитель частоты с переменным коэффициентом деления с увеличенным диапазоном коэффициентов деления при сохранении быстродействия и надежности функционирования [1], содержащий асинхронный счетчик импульсов I на D-триггерах поз. 1-I,...,1-N, элементы 2-I,..., 2-N установки коэффициента деления, D-триггер 4 обнуления, первый 5 и второй буферные элементы, элемент И-НЕ 8, инвертор 9, входную шину 10, шину 11-I,...,11 -N кода управления и выходную шину 12.

Диапазон коэффициентов деления названного аналога 3,..., 2N +2, где N-количество D-триггеров счетчика 1, а коэффициент деления частоты K = M + 3, где M-десятичный эквивалент кода управления.

Другим аналогом может служить многоразрядный управляемый делитель частоты повышенного быстродействия [2], содержащий JK-триггеры 1, 2 и 3, счетчик импульсов 4, входную 5 и выходную 6 шины, шину 7 управления входами Do,..., Dn счетчика 4 и шину логического нуля "0" B.

Коэффициент деления названного устройства Kд = (6 + N), где N- десятичный эквивалент двоичного кода управления значением Kд.

Считается, что быстродействие многоразрядных счетных структур с целочисленным коэффициентом деления, отличным от целой степени основания 2, оценивается временем предустановки начальных данных счета (кода) перед очередным циклом (периодом) счета.

Предельным быстродействием, обеспечиваемым выбранной элементной базой, обладают структуры, у которых предустановка исходных данных происходит между двумя последовательными перепадами единицы счета - e0, с периодом тактовой частоты T0, а коэффициент деления равен числовому эквиваленту кода управления.

В представленных аналогах использованы специальные технические решения, вводящие запрет счета на 3 [1] и 6 [2] периодов единицы счета, для обеспечения безсбойной предустановки исходных данных, что фактически снижает потенциальное быстродействие многоразрядной структуры по предельной частоте импульсов единицы счета, обеспечиваемое техническими характеристиками элемента счета.

Наиболее близок к изобретению по построению и совокупности существенных признаков синхронный делитель частоты [3], включающий группу из N = n + 1 синхронных JK-триггеров с предустановкой по  входу, цепь элементов совпадения сквозного переноса, группу элементов совпадения межразрядной связи, цепь синхронного запуска элементов счета с инвертором и элементом совпадения инверсной логики, а также двухступенчатый дешифратор предустановки с (n -1) - входовым элементом совпадения в первой ступени и двухвходовым элементом совпадения во второй ступени с соответствующими связями.

входу, цепь элементов совпадения сквозного переноса, группу элементов совпадения межразрядной связи, цепь синхронного запуска элементов счета с инвертором и элементом совпадения инверсной логики, а также двухступенчатый дешифратор предустановки с (n -1) - входовым элементом совпадения в первой ступени и двухвходовым элементом совпадения во второй ступени с соответствующими связями.

Выбранный прототип обеспечивает любой фиксированный целочисленный коэффициент деления в пределах числовых значений от 2n-1 + 1 до 2n-1, где n-число разрядов счетчика импульсов 16, и обладает быстродействием по максимальной частоте импульсов единицы счета порядка ее паспортного значения, обеспечиваемого базовым элементом - синхронным JK-триггером с установкой по  входу.

входу.

Задача изобретения заключается в реализации многоразрядного управляемого делителя частоты импульсов единицы счета  с любым целочисленным коэффициентом деления Кд в пределах набора значений от 2n-1 + 2 до 2n -2, где n - число счетных ячеек всех разрядов делителя, а значения коэффициента деления Kд = K - в устройствах исполнения 1 и 2 или Kд = K + 1 - в устройстве исполнения 3, где K - десятичный эквивалент n- разрядного управляющего кода, соответствующий конкретной величине K дj из набора значений.

с любым целочисленным коэффициентом деления Кд в пределах набора значений от 2n-1 + 2 до 2n -2, где n - число счетных ячеек всех разрядов делителя, а значения коэффициента деления Kд = K - в устройствах исполнения 1 и 2 или Kд = K + 1 - в устройстве исполнения 3, где K - десятичный эквивалент n- разрядного управляющего кода, соответствующий конкретной величине K дj из набора значений.

Получение дополнительного качества - управления коэффициентом деления при сохранении быстродействия по минимальному дискрету единицы счета обеспечивается за счет специфики кода Грея, использования двухступенчатой схемы синхронизации JK-триггеров всех (n + 1)-го разрядов счетчика импульсов, а также за счет организации однозначной предустановки любого коэффициента деления из набора значений в момент опознания конечного состояния счетчика импульсов.

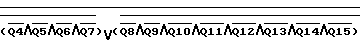

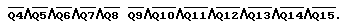

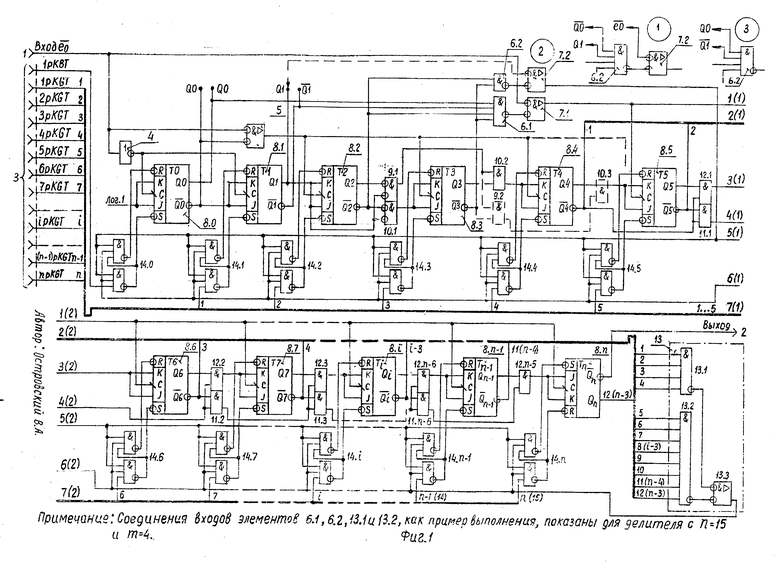

На фиг. 1 приведена с сокращениями функциональная схема многоразрядного управляемого делителя частоты как пример выполнения для конкретного Kд = 21845, при количестве синхронных JK-триггеров, соответствующем 15-ти разрядам, из которых m элементов 8.1,...,8.4 составляют группу из четырех младших разрядов, а элемент 8.0 нулевого разряда используется в режиме синхронного T-триггера.

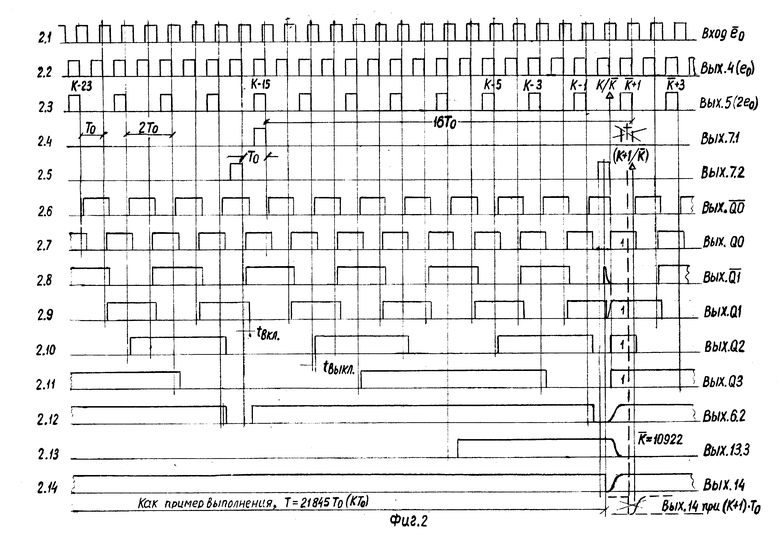

На фиг. 2 в окрестности формируемого импульса предустановки начальных данных частично показаны: последовательность 2.1 импульсов единицы счета  на входе делителя, последовательности 2.2 и 2.3 импульсов e0 и

на входе делителя, последовательности 2.2 и 2.3 импульсов e0 и  синхронизации JK-триггеров нулевого и четырех (m) младших разрядов счетчика импульсов, последовательность Вых.7.1 импульсов синхронизации одиннадцати (n - m) JK- триггеров 8.5, ...,8.n группы старших разрядов, последовательности 2.6, 2.7, 2.8, формируемые JK-триггерами нулевого 8.0 и первого 8.1 разрядов, а также последовательности 2.9 и 2.10 JK-триггеров второго 8.2 и третьего 8.3 разрядов. Приведенные последовательности импульсов поясняют формирование служебной последовательности импульсов Вых. 7.2, синхронизирующей предустановку, с периодом 16T0 и последовательности синхроимпульсов Вых. 7.1 с тем же периодом повторения и со сдвигом на один такт T0.

синхронизации JK-триггеров нулевого и четырех (m) младших разрядов счетчика импульсов, последовательность Вых.7.1 импульсов синхронизации одиннадцати (n - m) JK- триггеров 8.5, ...,8.n группы старших разрядов, последовательности 2.6, 2.7, 2.8, формируемые JK-триггерами нулевого 8.0 и первого 8.1 разрядов, а также последовательности 2.9 и 2.10 JK-триггеров второго 8.2 и третьего 8.3 разрядов. Приведенные последовательности импульсов поясняют формирование служебной последовательности импульсов Вых. 7.2, синхронизирующей предустановку, с периодом 16T0 и последовательности синхроимпульсов Вых. 7.1 с тем же периодом повторения и со сдвигом на один такт T0.

Собственно импульс предустановки Вых. 14 с периодом K • T0 формируется в конце каждого цикла деления при совпадении оконечного импульса последовательности Вых. 7.2 с импульсом Вых. 13.3 дешифратора состояния (n - m +1) значащих разрядов счетчика импульсов, или с Вых. 7.1 при коэффициенте деления Kд = (K + 1)• T0.

Растущие H и спадающие L перепады потенциала последовательностей импульсов, представленных строками 2.1, 2.2, 2.6,...,2, 14, показаны с учетом времени tвыкл. и tвкл. в предположении, что структура состоит из ТТЛШ JK-триггеров с запуском по C-входам. При этом также учтены естественные задержки формирования перепадов потенциала, вносимые другими ТТЛШ-элементами схемы.

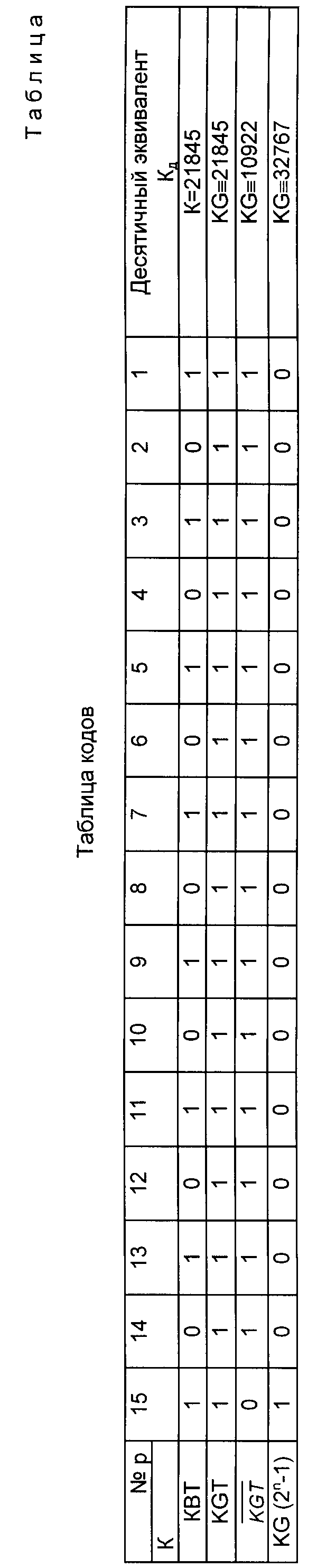

В таблице, в качестве конкретного примера выполнения, приведен 15-разрядный ("шахматный") позиционный двоичный код (ПДК), обозначенный КВТ (код бинарный периода) и определяющий выбранный период выходной последовательности импульсов  соответствующий ему 15-разрядный код Грея- KGT, дополнение последнего

соответствующий ему 15-разрядный код Грея- KGT, дополнение последнего  до числового эквивалента, соответствующего 215-1, а также десятичные эквиваленты K, KG,

до числового эквивалента, соответствующего 215-1, а также десятичные эквиваленты K, KG,  и KG названных кодов.

и KG названных кодов.

В момент предустановки, совпадающий с началом счета, в JK-триггеры 8.1,. . . ,8.4 младших разрядов и 8.5,...,8.n старших разрядов поразрядно вводится дополнение KGT до эквивалента 215-1, а JK-триггер 8.0 нулевого разряда устанавливается в состояние, соответствующее значению IpКВТ первого разряда управляющего ПДК.

Устройство (фиг.1), выполненное в виде n-разрядного синхронного счетчика импульсов в коде Грея, содержит входную 1 шину, выходную 2 шину, шину логической единицы, (n + 1)-входовую 3 шину n-разрядного управляющего кода, логический 4 инвертор, первый 5 элемент 2И-НЕ инверсной логики, JK-триггер 8.0 нулевого разряда m 8.1,...,8.4 JK-триггеров, младших разрядов, m - 3 двухвходовых 9.1 элементов совпадения первой цепи сквозного переноса, первый 9.1 из которых - второй элемент 2И-НЕ инверсной логики, m - 2 двухвходовых 10.1, 10.2 элементов совпадения межразрядной связи JK-триггеров младших разрядов, первый 10.1 из которых - третий элемент 2И-НЕ инверсной логики, (m - 1)- входовый дешифратор 6.2-7.2 с (m - 2)-входовым элементом И-НЕ в первой ступени, выход которого соединен с первым входом четвертого 7.2 элемента 2И-НЕ инверсной логики во второй ступени (m - 1) -входового дешифратора, при этом согласно изобретению в его состав введены n - m (II) 8.5,...,8.n

JK - триггеров старших разрядов так, что Q - выход m-го 8.4 JK-триггера младшего разряда с J и K-входами (m + 1)-го 8.5 JK-триггера старшего разряда, а  - выход m-го JK-триггера младшего разряда подключен к первому входу первого 11.1 элемента 2И второй цепи сквозного переноса, которая состоит из n-m-2 11.1,...,11.n-6 элементов 2И, и к первому входу первого 12.1 элемента 2И межразрядной связи JK-триггеров старших разрядов, в которую введено n-m-1 12.1, ...,12.n-5 элементов 2И, а второй вход первого 12.1 элемента 2И межразрядной связи JK-триггеров старших разрядов соединен с Q-выходом (m + 1)-го 8.5 JK-триггера старшего разряда,

- выход m-го JK-триггера младшего разряда подключен к первому входу первого 11.1 элемента 2И второй цепи сквозного переноса, которая состоит из n-m-2 11.1,...,11.n-6 элементов 2И, и к первому входу первого 12.1 элемента 2И межразрядной связи JK-триггеров старших разрядов, в которую введено n-m-1 12.1, ...,12.n-5 элементов 2И, а второй вход первого 12.1 элемента 2И межразрядной связи JK-триггеров старших разрядов соединен с Q-выходом (m + 1)-го 8.5 JK-триггера старшего разряда,  выход которого подключен ко второму входу первого 11.1 элемента 2И второй цепи сквозного переноса, выход которого соединен с первым входом второго 11.2 элемента 2И второй цепи сквозного переноса и с первым входом второго 12.2 элемента 2И межразрядной связи JK-триггеров старших разрядов, второй вход которого соединен с Q-выходом (m + 2)-го 8.6 JK-триггера старшего разряда

выход которого подключен ко второму входу первого 11.1 элемента 2И второй цепи сквозного переноса, выход которого соединен с первым входом второго 11.2 элемента 2И второй цепи сквозного переноса и с первым входом второго 12.2 элемента 2И межразрядной связи JK-триггеров старших разрядов, второй вход которого соединен с Q-выходом (m + 2)-го 8.6 JK-триггера старшего разряда  выход которого подключен ко второму входу второго 11.2 элемента 2И второй цепи сквозного переноса, а выход первого элемента 12.1 межразрядной связи JK-триггеров старших разрядов соединен с J и K-входами (m + 2)-го 8.6 JK-триггера старшего разряда, и выход i-го элемента 2И второй цепи сквозного переноса соединен с первым входом (i + 1)-го 11.3 элемента 2И второй цепи сквозного переноса и с первым входом (i + 1)-го 12.3 элемента 2И межразрядной связи JK-триггеров старших разрядов, второй вход которого соединен с Q-выходом (m + i +1)-го 8.7 JK-триггера старшего разряда,

выход которого подключен ко второму входу второго 11.2 элемента 2И второй цепи сквозного переноса, а выход первого элемента 12.1 межразрядной связи JK-триггеров старших разрядов соединен с J и K-входами (m + 2)-го 8.6 JK-триггера старшего разряда, и выход i-го элемента 2И второй цепи сквозного переноса соединен с первым входом (i + 1)-го 11.3 элемента 2И второй цепи сквозного переноса и с первым входом (i + 1)-го 12.3 элемента 2И межразрядной связи JK-триггеров старших разрядов, второй вход которого соединен с Q-выходом (m + i +1)-го 8.7 JK-триггера старшего разряда,  выход которого подключен ко второму входу (i + 1)-го 11.2 элемента 2И второй цепи сквозного переноса, выход (i + 1)-го 12.2 элемента 2И межразрядной связи соединен с J и K-входами (m + i +2)-го 8.i JK-триггера старшего разряда, а выход (n - m - 2)-го 11.n-6 элемента 2И второй цепи сквозного переноса соединен с первым входом (n - m - 1)-го 12.n-5 элемента 2И межразрядной связи JK-триггеров старших разрядов, второй вход которого соединен с Q-выходом (n - m - 1)-го 8.n-1 JK-триггера старшего разряда, а выход соединен с J и K-входами (m - n)-го 8.n JK-триггера старшего разряда, и C-выходы n-m 8.5,...,8.n JK-триггеров старших разрядов объединены и соединены с выходом пятого 7.1 элемента 2И-НЕ инверсной логики, второй вход которого соединен со входом логического 4 инвертора, со вторым входом первого 5 элемента 2И-НЕ инверсной логики и со входной 1 шиной, а первый вход пятого элемента 2И-НЕ инверсной логики соединен с выходом m-входового 6.1 элемента И-НЕ, первый вход которого подключен к Q-выходу JK-триггера 8.0 нулевого разряда, второй вход - подключен к

выход которого подключен ко второму входу (i + 1)-го 11.2 элемента 2И второй цепи сквозного переноса, выход (i + 1)-го 12.2 элемента 2И межразрядной связи соединен с J и K-входами (m + i +2)-го 8.i JK-триггера старшего разряда, а выход (n - m - 2)-го 11.n-6 элемента 2И второй цепи сквозного переноса соединен с первым входом (n - m - 1)-го 12.n-5 элемента 2И межразрядной связи JK-триггеров старших разрядов, второй вход которого соединен с Q-выходом (n - m - 1)-го 8.n-1 JK-триггера старшего разряда, а выход соединен с J и K-входами (m - n)-го 8.n JK-триггера старшего разряда, и C-выходы n-m 8.5,...,8.n JK-триггеров старших разрядов объединены и соединены с выходом пятого 7.1 элемента 2И-НЕ инверсной логики, второй вход которого соединен со входом логического 4 инвертора, со вторым входом первого 5 элемента 2И-НЕ инверсной логики и со входной 1 шиной, а первый вход пятого элемента 2И-НЕ инверсной логики соединен с выходом m-входового 6.1 элемента И-НЕ, первый вход которого подключен к Q-выходу JK-триггера 8.0 нулевого разряда, второй вход - подключен к  выходу первого 8.1 JK-триггера младшего разряда, а третий вход соединен с первым входом (m - 2)-входового 6.2 элемента И-НЕ и подключен к

выходу первого 8.1 JK-триггера младшего разряда, а третий вход соединен с первым входом (m - 2)-входового 6.2 элемента И-НЕ и подключен к  выходу второго 8.2 JK-триггера младшего разряда, j-й вход m - входового элемента И-НЕ соединен с (j-2)-м входом (m-2)-входового элемента И-НЕ и подключен к

выходу второго 8.2 JK-триггера младшего разряда, j-й вход m - входового элемента И-НЕ соединен с (j-2)-м входом (m-2)-входового элемента И-НЕ и подключен к  выходу (j - 1)-го JK-триггера младшего разряда, и m-й вход m-входового элемента И-НЕ соединен с (m-2)-м входом (m-2)-входового элемента И-НЕ и подключен к

выходу (j - 1)-го JK-триггера младшего разряда, и m-й вход m-входового элемента И-НЕ соединен с (m-2)-м входом (m-2)-входового элемента И-НЕ и подключен к  выходу (m-1)-го 8.3 JK - триггера младшего разряда, а выход четвертого 7.2 элемента И-НЕ инверсной логики соединен с объединенными первыми входами элементов 3И-НЕ n+1 14,0,... , 14. n логических пар элементов 3И-НЕ, вторые входы которых объединены и соединены с выходом (n - m + 1)-входового 13 дешифратора, n - m + 1 входов которого поразрядно подключены к Q-выходу (n - m)-го 8.n JK-триггера старшего разряда, к

выходу (m-1)-го 8.3 JK - триггера младшего разряда, а выход четвертого 7.2 элемента И-НЕ инверсной логики соединен с объединенными первыми входами элементов 3И-НЕ n+1 14,0,... , 14. n логических пар элементов 3И-НЕ, вторые входы которых объединены и соединены с выходом (n - m + 1)-входового 13 дешифратора, n - m + 1 входов которого поразрядно подключены к Q-выходу (n - m)-го 8.n JK-триггера старшего разряда, к  выходам n - m - 1 8.5,...,8.n-1 JK-триггеров старших разрядов и к

выходам n - m - 1 8.5,...,8.n-1 JK-триггеров старших разрядов и к  выходу m-го JK-триггера младшего разряда, третий вход первого элемента 3И-НЕ нулевой 14.0 логической пары элементов 3И-НЕ подключен ко входу 1рВКТ первого разряда позиционного двоичного кода n -разрядной 3 шины управляющего кода, а выход - соединен с

выходу m-го JK-триггера младшего разряда, третий вход первого элемента 3И-НЕ нулевой 14.0 логической пары элементов 3И-НЕ подключен ко входу 1рВКТ первого разряда позиционного двоичного кода n -разрядной 3 шины управляющего кода, а выход - соединен с  входом JK-триггера 8.0 нулевого разряда и с третьим входом элемента 3И-НЕ, выход которого соединен с

входом JK-триггера 8.0 нулевого разряда и с третьим входом элемента 3И-НЕ, выход которого соединен с  входом JK-триггера нулевого разряда, и третьи входы первых элементов 3И-НЕ n- 14.1, . . .,14.n логических пар элементов 3И-НЕ поразрядно подключены ко входам соответствующих разрядов кода Грея шины n-разрядного управляющего кода, а выходы первых элементов 3И-НЕ m логических пар элементов 3И-НЕ поразрядно соединены с

входом JK-триггера нулевого разряда, и третьи входы первых элементов 3И-НЕ n- 14.1, . . .,14.n логических пар элементов 3И-НЕ поразрядно подключены ко входам соответствующих разрядов кода Грея шины n-разрядного управляющего кода, а выходы первых элементов 3И-НЕ m логических пар элементов 3И-НЕ поразрядно соединены с  входами m JK-триггеров младших разрядов и с третьими входами вторых элементов 3И-НЕ, выходы которых поразрядно соединены с

входами m JK-триггеров младших разрядов и с третьими входами вторых элементов 3И-НЕ, выходы которых поразрядно соединены с  входами JK-триггеров младших разрядов, выходы первых элементов 3И-НЕ n - m - 1 логических пар элементов 3И-НЕ поразрядно соединены с

входами JK-триггеров младших разрядов, выходы первых элементов 3И-НЕ n - m - 1 логических пар элементов 3И-НЕ поразрядно соединены с  входами n - m - 1 JK-триггеров старших разрядов и с третьими входами вторых элементов 3И-НЕ, выходы которых поразрядно соединены с

входами n - m - 1 JK-триггеров старших разрядов и с третьими входами вторых элементов 3И-НЕ, выходы которых поразрядно соединены с  входами n - m - 1 JK-триггеров старших разрядов, и выход первого элемента 3И-НЕ n-й логической пары элементов 3И-НЕ соединен с

входами n - m - 1 JK-триггеров старших разрядов, и выход первого элемента 3И-НЕ n-й логической пары элементов 3И-НЕ соединен с  входом (n-m)-го 8.n JK-триггера старшего разряда и с третьим входом второго элемента 3И-НЕ, выход которого соединен с

входом (n-m)-го 8.n JK-триггера старшего разряда и с третьим входом второго элемента 3И-НЕ, выход которого соединен с  входом (n-m)-го JK-триггера старшего разряда,

входом (n-m)-го JK-триггера старшего разряда,  - выход которого подключен к выходной 2 шине, и второй вход четвертого элемента 2И-НЕ инверсной логики подключен к Q-выходу первого 8.1 JK-триггера младшего разряда.

- выход которого подключен к выходной 2 шине, и второй вход четвертого элемента 2И-НЕ инверсной логики подключен к Q-выходу первого 8.1 JK-триггера младшего разряда.

1. Работа многоразрядного управляемого делителя частоты (фиг.1 и 2) в непрерывном режиме деления рассмотрена на конкретном примере устройства с коэффициентом деления Кд=21845 при общем числе разрядов n=15 и числе младших разрядов m=4.

Импульсы единицы счета  последовательности 2.1 со входной 1 шины "Вход

последовательности 2.1 со входной 1 шины "Вход  " поступает на вход логического 4 инвертора, на первый вход первого 5 элемента 2И-НЕ инверсной логики и на вторые входы четвертого 7.2 и пятого 7.1 элементов 2И-НЕ инверсной логики, которые выполняют операции деления частоты следования отрицательных импульсов исходной последовательности

" поступает на вход логического 4 инвертора, на первый вход первого 5 элемента 2И-НЕ инверсной логики и на вторые входы четвертого 7.2 и пятого 7.1 элементов 2И-НЕ инверсной логики, которые выполняют операции деления частоты следования отрицательных импульсов исходной последовательности  по уравнению

по уравнению  где

где  инверсные состояния логических переменных a и b на каждом из входов элемента 2И-НЕ инверсной логики. Практически названная операция выполняется элементами 2 ИЛИ-НЕ прямой логики.

инверсные состояния логических переменных a и b на каждом из входов элемента 2И-НЕ инверсной логики. Практически названная операция выполняется элементами 2 ИЛИ-НЕ прямой логики.

Сформированные импульсы единицы счета e0 последовательности 2.2 с выхода логического 4 инвертора поступают на объединенные C-входы JK-триггера 8.0 нулевого разряда и первого 8.1 JK-триггера младшего разряда, а импульсы  с удвоенным периодом повторения последовательности 2.3 синхронно с импульсами четной половины последовательности 2.2 поступают на объединенные C-входы второго 8.2, третьего 8.3 и четвертого (m-го) 8.4 JK-триггеров младших разрядов.

с удвоенным периодом повторения последовательности 2.3 синхронно с импульсами четной половины последовательности 2.2 поступают на объединенные C-входы второго 8.2, третьего 8.3 и четвертого (m-го) 8.4 JK-триггеров младших разрядов.

Положительные импульсы  последовательности 2.6, с удвоенным периодом повторения поступают с

последовательности 2.6, с удвоенным периодом повторения поступают с  - выхода JK-триггера 8.0 нулевого разряда на объединенные J и K-входы первого 8.1 JK-триггера младшего разряда и на первый вход первого 6.2 четырехвходового (m-входового) элемента И-НЕ, а отрицательные импульсы последовательности 2.6 со взаимным сдвигом на период T0 последовательности e0 поступают на первый вход первого 5 элемента 2И-НЕ инверсной логики, чем обеспечивают формирование последовательности 2.3 при совпадении отрицательных импульсов

- выхода JK-триггера 8.0 нулевого разряда на объединенные J и K-входы первого 8.1 JK-триггера младшего разряда и на первый вход первого 6.2 четырехвходового (m-входового) элемента И-НЕ, а отрицательные импульсы последовательности 2.6 со взаимным сдвигом на период T0 последовательности e0 поступают на первый вход первого 5 элемента 2И-НЕ инверсной логики, чем обеспечивают формирование последовательности 2.3 при совпадении отрицательных импульсов  последовательности 2.1, которая присутствует на втором входе первого элемента 2И-НЕ инверсной логики.

последовательности 2.1, которая присутствует на втором входе первого элемента 2И-НЕ инверсной логики.

Срабатывания второго 8.2, третьего 8.3 и четвертого 8.4 JK-триггеров m-1 младших разрядов происходит при совпадении соответствующего синхроимпульса последовательности 2.3 с совпадающими импульсами межразрядной связи, поступающими на их J и K-входы непосредственно с Q-выхода первого 8.1 JK-триггера младшего разряда или после их инверсии и распределения элементами 10.1 и 10.2 межразрядной связи JK-триггеров младших разрядов и элементом 9.1 первой цепи сквозного переноса.

Последовательность 2.4 импульсов Вых.7.1 с периодом следования 16 Tо, поступает на объединенные одинадцать (n-m) C-входов пятого 8.5 (m + 1)-го, шестого 8.6,..., и пятнадцатого 8.n JK-триггеров старших разрядов синхронно с каждым шестнадцатым синхроимпульсом e0 последовательности 2.2.

Она формируется двухступенчатой парой элементов совпадения 6.1 и 7.1 в соответствии с уравнением

Срабатывания n-m 8.5-8. n JK-триггеров старших разрядов происходят при совпадении соответствующего синхроимпульса Вых. 7.1 последовательности 2.4 с импульсом межразрядной связи JK-триггеров старших разрядов шириной 16Tо, поступающими или непосредственно с Q-выхода четвертого 8.4 (m-го) JK-триггера последнего младшего разряда на J и K - входы пятого 8.5 (m + 1)-го JK-триггера первого старшего разряда, или с  выхода четвертого JK-триггера младшего разряда после их распределения n-m-1 12.1,...,12.n-5 элементами 2И межразрядной связи JK - триггеров старших разрядов и n-m-2 11.1,...,11.n-6 элементами 2И второй цепи сквозного переноса.

выхода четвертого JK-триггера младшего разряда после их распределения n-m-1 12.1,...,12.n-5 элементами 2И межразрядной связи JK - триггеров старших разрядов и n-m-2 11.1,...,11.n-6 элементами 2И второй цепи сквозного переноса.

Собственно процесс деления частоты следования импульсов  единицы счета делителем, выполненным в виде n- разрядного синхронного счетчика импульсов в коде Грея, происходит следующим образом.

единицы счета делителем, выполненным в виде n- разрядного синхронного счетчика импульсов в коде Грея, происходит следующим образом.

При предустановке исходных данных (фиг.2) в виде n-разрядного параллельного кода Грея в момент окончания предшествовавшего цикла деления и начала рассматриваемого, в пятнадцать 8.1, . ..,8.n JK-триггеров младших и старших разрядов по  и

и  - входам записывается код

- входам записывается код  дополнения 10922 коэффициента деления К-21845 до досчитываемого значения 32767. При этом JK-триггеры, с первого 8.1 по четырнадцатый 8.n-1, устанавливаются в промежуточное состояние "единица", пятнадцатый 8.n JK - триггер старшего разряда - в состояние "нуль", а JK-триггер 8.0 нулевого разряда устанавливается в состояние, соответствующее значению первого младшего двоичного IpКВТ-разряда n-разрядного управляющего кода, т.е. логической единице.

дополнения 10922 коэффициента деления К-21845 до досчитываемого значения 32767. При этом JK-триггеры, с первого 8.1 по четырнадцатый 8.n-1, устанавливаются в промежуточное состояние "единица", пятнадцатый 8.n JK - триггер старшего разряда - в состояние "нуль", а JK-триггер 8.0 нулевого разряда устанавливается в состояние, соответствующее значению первого младшего двоичного IpКВТ-разряда n-разрядного управляющего кода, т.е. логической единице.

Далее, при поступлении на вход делителя 21845 импульсов  единицы счета, состояние пятнадцати 8.1,...,8.n JK - триггеров всех n разрядов изменяется от исходного промежуточного значения

единицы счета, состояние пятнадцати 8.1,...,8.n JK - триггеров всех n разрядов изменяется от исходного промежуточного значения  до конечного KG, соответствующего 32767 единицам счета в момент прекращения счета и очередной предустановки данных.

до конечного KG, соответствующего 32767 единицам счета в момент прекращения счета и очередной предустановки данных.

В устройстве исп.1 определим, что перепадом, вызывающим очередную предустановку данных, поразрядно вводимых в шестнадцать 8.0...8.n триггеров всех разрядов, является положительный H перепад импульса Вых. 7.2 последовательности 2.5, который завершает операцию деления при любом целочисленном Кд из набора значений.

Для этого первый дешифратор 6.2-7.2, выполняющий двухступенчатую логическую операцию

формирует на выходе четвертого 7.2 элемента 2И-НЕ инверсной логики положительный импульс Вых.7.2 при совпадении отрицательного импульса, формируемого m-входовым 6.2 элементом И-НЕ, с одним из шестнадцати отрицательных импульсов  последовательности 2.1.

последовательности 2.1.

Второй дешифратор 13 за 7 периодов Tо единицы счета  до сформирования определяющего перепада H импульса Вых. 7.2 формирует на выходе шестого 13.3 элемента 2И-НЕ инверсной логики положительный импульс Вых. 13.3 в результате совпадения отрицательных импульсов с выходов первого 13.1 элемента 4И-НЕ при выполнении двухступенчатой операции над двенадцатью переменными

до сформирования определяющего перепада H импульса Вых. 7.2 формирует на выходе шестого 13.3 элемента 2И-НЕ инверсной логики положительный импульс Вых. 13.3 в результате совпадения отрицательных импульсов с выходов первого 13.1 элемента 4И-НЕ при выполнении двухступенчатой операции над двенадцатью переменными

1. При поступлении, в граничном  такте деления, последнего положительного импульса Вых. 7.2 из последовательности 2.5 на объединенные первые входы шестнадцати элементов 3И-НЕ и положительного импульса 13.3 на их вторые объединенные входы, на выходах этих элементов 3И-НЕ, выбранных из состава шестнадцати 14.0, ...,14.n логических пар элементов 3И-НЕ и поразрядно открытых в соответствии с n-разрядным управляющим кодом, формируются шестнадцать отрицательных L перепадов Вых.14, которые, поступая на определенные

такте деления, последнего положительного импульса Вых. 7.2 из последовательности 2.5 на объединенные первые входы шестнадцати элементов 3И-НЕ и положительного импульса 13.3 на их вторые объединенные входы, на выходах этих элементов 3И-НЕ, выбранных из состава шестнадцати 14.0, ...,14.n логических пар элементов 3И-НЕ и поразрядно открытых в соответствии с n-разрядным управляющим кодом, формируются шестнадцать отрицательных L перепадов Вых.14, которые, поступая на определенные  - входы шестнадцати 8.0,...,8.n JK - триггеров всех разрядов останавливают счет в рассматриваемом цикле и обеспечивают предустановку очередных данных, начиная счет в следующем цикле деления с промежуточного состояния счетных ячеек.

- входы шестнадцати 8.0,...,8.n JK - триггеров всех разрядов останавливают счет в рассматриваемом цикле и обеспечивают предустановку очередных данных, начиная счет в следующем цикле деления с промежуточного состояния счетных ячеек.

2. В устройстве исп.2 определяющим перепадом, который вызывает прекращение счета в граничном  такте деления и обеспечивает предустановку очередных данных, является отрицательный L перепад последнего в цикле деления положительного импульса с Q-выхода первого 8.1 JK - триггера младшего разряда, поступающий на второй вход четвертого 7.2 элемента 2И-НЕ инверсной логики.

такте деления и обеспечивает предустановку очередных данных, является отрицательный L перепад последнего в цикле деления положительного импульса с Q-выхода первого 8.1 JK - триггера младшего разряда, поступающий на второй вход четвертого 7.2 элемента 2И-НЕ инверсной логики.

3. В устройстве исп.3 определяющим перепадом, который вызывает прекращение счета в граничном  такте деления и предустановку очередных данных, является положительный перепад H последнего положительного импульса Вых. 7.1 последовательности 2.4, совпадающий с одиночным положительным импульсом Вых. 13.3 (2.13).

такте деления и предустановку очередных данных, является положительный перепад H последнего положительного импульса Вых. 7.1 последовательности 2.4, совпадающий с одиночным положительным импульсом Вых. 13.3 (2.13).

При таком подключении первого и второго входов первого 6.2 m-входового элемента И-НЕ целочисленный коэффициент деления будет равен K+1 единицам, где K - десятичный эквивалент управляющего кода, а период последовательности импульсов предустановки Вых.14 (2.14) становится равным (K+1) • To, и период выходной 2 последовательности импульсов "Выход", формируемый  выходом пятнадцатого 8.n JK - триггера старшего разряда, также увеличивается на один период Tо импульсов единицы счета.

выходом пятнадцатого 8.n JK - триггера старшего разряда, также увеличивается на один период Tо импульсов единицы счета.

Предлагаемый n-разрядный управляемый делитель частоты следования импульсов единицы счета  позволяет получать любой целочисленный коэффициент деления Кд из набора значений от 2n-1+2 до 2n-2 при обеспечении быстродействия по минимальному дискрету единицы счета, соизмеримого с быстродействием базового счетного элемента - синхронного JK-триггера с установкой нуля и единицы.

позволяет получать любой целочисленный коэффициент деления Кд из набора значений от 2n-1+2 до 2n-2 при обеспечении быстродействия по минимальному дискрету единицы счета, соизмеримого с быстродействием базового счетного элемента - синхронного JK-триггера с установкой нуля и единицы.

Построение делителя в виде многоразрядного двухступенчатого устройства в коде Грея позволяет также полнее реализовать технические данные элементной базы по предельной частоте следования импульсов единицы счета  что позволит, при обеспечении задаваемого быстродействия, использовать элементную базу перспективных серий, например микромощных ТТЛШ-серий, потребляющих меньшую мощность от источника электропитания.

что позволит, при обеспечении задаваемого быстродействия, использовать элементную базу перспективных серий, например микромощных ТТЛШ-серий, потребляющих меньшую мощность от источника электропитания.

Так как предлагаемый n-разрядный делитель представляет многоразрядное двуступенчатое устройство, содержащее m JK - триггеров младших разрядов и n-m JK - триггеров старших разрядов, то приводятся упрощенные практические соображения по его реализации.

1. Исходя из длительности минимального T0мин. дискрета перестройки и наибольшего Tмакс.периода (фиг.1 и 2) выходной 2 последовательности импульсов "Выход", определяются информационная емкость 2n-2 и число n основных разрядов делителя, для реализации которого выбирается необходимая элементная база с перечисленными ниже техническими данными:

максимальная частота синхронизации JK - триггера

время выключения по C-входу - tвыкл.с(tpLH);

время включения по C-входу - tвкл.C(tpHL);

время включения элемента И-НЕ - tвкл.1(tpHL);

время выключения элемента И-НЕ - tвыкл.1(tpHL);

время выключения элемента 2ИЛИ-НЕ (2И-НЕ инверсной логики) - tвыкл.2(tpLH);

время задержки распространения положительного H перепада при включении элемента 2И - tp3(tpLH).

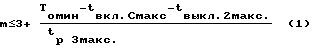

2. Число m младших разрядов делителя, ограничиваемое допустимым запаздыванием фронта отрицательного импульса C • Q-выхода первого 8.1 JK - триггера младшего разряда находится по формуле (I) с округлением в меньшую сторону для всех трех вариантов исполнения:

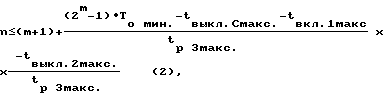

3. Полное число n JK - триггеров основных разрядов делителя, при известном числе m JK - триггеров младших разрядов, для вариантов исполнения 1 и 2 находится по формуле (2):

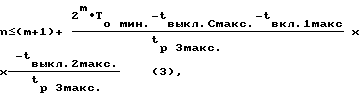

а для исполнения 3 - по формуле (3):

Примечание. Если число n, полученное по формулам (2) и (3), окажется меньше требуемого п.1, то необходимо перейти на элементную базу с повышенным быстродействием, что вызовет увеличение числа m JK-триггеров младших разрядов, пересчитанного по формуле (I).

В устройствах исп. 1 (или исп.3) начало предустановки вызывается положительным H перепадом последнего в каждом цикле деления положительного импульса Вых. 7.2 (или Вых. 7.1) последовательностей 2.5 (или 2.4), а процессы предустановки поддерживаются за счет естественного запаздывания отрицательного перепада с выхода первого 6.2 m-входового элемента И-НЕ, а также суммой естественных задержек положительного перепада с выхода 13.3 шестого элемента 2И-НЕ инверсной логики из состава второго дешифратора.

В устройстве исп.2 начало предустановки вызывается отрицательным L перепадом последнего в цикле деления положительного импульса с Q - выхода первого JK - триггера младшего разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| ЖДУЩИЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1993 |

|

RU2047939C1 |

| ДИСКРЕТНО-АНАЛОГОВЫЙ СИНУС-ГЕНЕРАТОР | 1995 |

|

RU2108657C1 |

| УСТРОЙСТВО ДЛЯ ВЫЯВЛЕНИЯ АСИНХРОННОГО РЕЖИМА ЭЛЕКТРОПЕРЕДАЧИ | 1993 |

|

RU2064727C1 |

| СХЕМА УСКОРЕННОГО ПЕРЕНОСА (ВАРИАНТЫ) | 1999 |

|

RU2155371C1 |

| СХЕМА УСКОРЕННОГО ПЕРЕНОСА (ВАРИАНТЫ) | 1999 |

|

RU2149443C1 |

| УСТРОЙСТВО ДЛЯ ВЫЯВЛЕНИЯ АСИНХРОННОГО РЕЖИМА ЭЛЕКТРОПЕРЕДАЧИ | 1993 |

|

RU2064726C1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ЧЕТЫРЕХФАЗНЫМ ШАГОВЫМ ДВИГАТЕЛЕМ | 1998 |

|

RU2133550C1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СЕЙСМОРАЗВЕДОЧНАЯ СИСТЕМА | 1994 |

|

RU2107312C1 |

Устройство относится к дискретной импульсной технике и может использоваться для формирования точных интервалов времени в изделиях различного назначения. Техническая задача изобретения заключается в реализации n-разрядного управляемого делителя частоты импульсов единицы счета с любым целочисленным коэффициентом деления в пределах набора значений от 2n+1 + 2 до 2n - 2, которая решается за счет выполнения делителя в виде синхронного счетчика импульсов в коде Грея при использовании двухступенчатой схемы синхронизации JK-триггеров всех разрядов. Многоразрядный управляемый делитель частоты содержит (n + 1)-входовую шину n-разрядного управляющего кода, логический инвертор, 6 элементов 2И-НЕ инверсной логики, n + 1 JK-триггеров, m - 3 двухвходовых элементов совпадения первой цепи сквозного переноса, m - 2 двухвходовых элементов совпадения межразрядной связи JK-триггеров младших разрядов, два дешифратора, n - m - 2 элементов 2И второй цепи сквозного переноса n - m - 1 элементов 2И межразрядной связи JK-триггеров старших разрядов, четыре элемента И-НЕ, n + 1 логических пар элементов 3И-НЕ. 2 ил., 1 табл.

Многоразрядный управляемый делитель частоты, выполненный в виде n - разрядного синхронного счетчика импульсов в коде Грея, содержащий входную шину, выходную шину, шину логической единицы, (n + 1) - входовую шину n - разрядного управляющего кода, логический инвертор, первый элемент 2И - НЕ инверсионной логики, JK - триггер нулевого разряда, m JK - триггеров младших разрядов, m - 3 двухвходовых элементов совпадения первой цепи сквозного переноса, первый из которых - второй элемент 2И - НЕ инверсной логики, m - 2 двухвходовых элементов совпадения межразрядной связи JK - триггеров младших разрядов, первый из которых - третий элемент 2И - НЕ инверсной логики, (m - 1) - входовый дешифратор с (m - 2) - входовым элементом И - НЕ в первой ступени, выход которого соединен с первым входом четвертого элемента 2И -НЕ инверсной логики во второй ступени (m - 1) - входового дешифратора, отличающийся тем, что в его состав введены n - m JK - триггеров старших разрядов так, что Q - выход m-го JK - триггера младшего разряда соединен с J и K - входами (m + 1)-го JK - триггера старшего разряда, а  выход m-го JK - триггера младшего разряда подключен к первому входу первого элемента 2И второй цепи сквозного переноса, которая состоит из n - m - 2 элементов 2И, и к первому входу первого элемента 2И межразрядной связи JK - триггеров старших разрядов, в которую введено n - m - 1 элементов 2И, а второй вход первого элемента 2И межразрядной связи JK - триггеров старших разрядов соединен с Q - выходом (m + 1)-го JK - триггера старшего разряда,

выход m-го JK - триггера младшего разряда подключен к первому входу первого элемента 2И второй цепи сквозного переноса, которая состоит из n - m - 2 элементов 2И, и к первому входу первого элемента 2И межразрядной связи JK - триггеров старших разрядов, в которую введено n - m - 1 элементов 2И, а второй вход первого элемента 2И межразрядной связи JK - триггеров старших разрядов соединен с Q - выходом (m + 1)-го JK - триггера старшего разряда,  выход которого подключен ко второму входу первого элемента 2И второй цепи сквозного переноса, выход которого соединен с первым входом второго элемента 2И второй цепи сквозного переноса и с первым входом второго элемента 2И межразрядной связи JK - триггеров старших разрядов, второй вход которого соединен с Q - выходом (m + 2)-го JK - триггера старшего разряда,

выход которого подключен ко второму входу первого элемента 2И второй цепи сквозного переноса, выход которого соединен с первым входом второго элемента 2И второй цепи сквозного переноса и с первым входом второго элемента 2И межразрядной связи JK - триггеров старших разрядов, второй вход которого соединен с Q - выходом (m + 2)-го JK - триггера старшего разряда,  выход которого подключен ко второму входу второго элемента 2И второй цепи сквозного переноса, а выход первого элемента 2И межразрядной связи JK - триггеров старших разрядов соединен с J и K - входами (m + 2)-го JK - триггера старшего разряда, и выход i-го элемента 2И второй цепи сквозного переноса соединен с первым входом (i + 1)-го элемента 2И второй цепи сквозного переноса и с первым входом (i + 1)-го элемента 2И межразрядной связи JK - триггеров старших разрядов, второй вход которого соединен с Q - выходом (m + i + 1)-го JK - триггера старшего разряда,

выход которого подключен ко второму входу второго элемента 2И второй цепи сквозного переноса, а выход первого элемента 2И межразрядной связи JK - триггеров старших разрядов соединен с J и K - входами (m + 2)-го JK - триггера старшего разряда, и выход i-го элемента 2И второй цепи сквозного переноса соединен с первым входом (i + 1)-го элемента 2И второй цепи сквозного переноса и с первым входом (i + 1)-го элемента 2И межразрядной связи JK - триггеров старших разрядов, второй вход которого соединен с Q - выходом (m + i + 1)-го JK - триггера старшего разряда,  выход которого подключен ко второму входу (i + 1)-го элемента 2И второй цепи сквозного переноса, выход (i + 1)-го элемента 2И межразрядной связи соединен с J и K - входами (m + i + 2)-го JK - триггера старшего разряда, а выход (n - m - 2)-го элемента 2И второй цепи сквозного переноса соединен с первым входом (n - m - 1)-го элемента 2И межразрядной связи JK - триггеров старших разрядов, второй вход которого соединен с Q - выходом (n - m - 1)-го JK - триггера старшего разряда, а выход соединен с J и K - входами (n - m )-го JK - триггера старшего разряда, и C - входы n - m JK - триггеров старших разрядов объединены и соединены с выходом пятого элемента 2И - НЕ инверсной логики, второй вход которого соединен со входом логического инвертора, со вторым входом первого элемента 2И - НЕ инверсной логики и со входной шиной, а первый вход пятого элемента 2И - НЕ инверсной логики соединен с выходом m - входового элемента И - НЕ, первый вход которого подключен к Q выходу JK - триггера нулевого разряда, второй вход подключен к

выход которого подключен ко второму входу (i + 1)-го элемента 2И второй цепи сквозного переноса, выход (i + 1)-го элемента 2И межразрядной связи соединен с J и K - входами (m + i + 2)-го JK - триггера старшего разряда, а выход (n - m - 2)-го элемента 2И второй цепи сквозного переноса соединен с первым входом (n - m - 1)-го элемента 2И межразрядной связи JK - триггеров старших разрядов, второй вход которого соединен с Q - выходом (n - m - 1)-го JK - триггера старшего разряда, а выход соединен с J и K - входами (n - m )-го JK - триггера старшего разряда, и C - входы n - m JK - триггеров старших разрядов объединены и соединены с выходом пятого элемента 2И - НЕ инверсной логики, второй вход которого соединен со входом логического инвертора, со вторым входом первого элемента 2И - НЕ инверсной логики и со входной шиной, а первый вход пятого элемента 2И - НЕ инверсной логики соединен с выходом m - входового элемента И - НЕ, первый вход которого подключен к Q выходу JK - триггера нулевого разряда, второй вход подключен к  выходу первого JK - триггера младшего разряда, а третий вход - соединен с первым входом (m - 2)-входового элемента И - НЕ и подключен к

выходу первого JK - триггера младшего разряда, а третий вход - соединен с первым входом (m - 2)-входового элемента И - НЕ и подключен к  выходу второго JK - триггера младшего разряда, j-й вход m - входового элемента И - НЕ соединен с (j - 2)-м входом (m - 2)-входового элемента И - НЕ и подключен к

выходу второго JK - триггера младшего разряда, j-й вход m - входового элемента И - НЕ соединен с (j - 2)-м входом (m - 2)-входового элемента И - НЕ и подключен к  выходу (j - 1)-го JK - триггера младшего разряда, и m-й вход m - входового элемента И - НЕ соединен с (m - 2)-м входом (m - 2)-входового элемента И - НЕ и подключен к

выходу (j - 1)-го JK - триггера младшего разряда, и m-й вход m - входового элемента И - НЕ соединен с (m - 2)-м входом (m - 2)-входового элемента И - НЕ и подключен к  выходу (m - 1)-го JK - триггера младшего разряда, а выход четвертого элемента 2И - НЕ инверсной логики соединен с объединенными первыми входами элементов 3И - НЕ n + 1 логических пар элементов 3И - НЕ, вторые входы которых объединены и соединены выходом (n - m + 1)-входового дешифратора, n - m + 1 входов которого поразрядно подключены к Q - выходу (n - m)-го JK - триггера старшего разряда, к

выходу (m - 1)-го JK - триггера младшего разряда, а выход четвертого элемента 2И - НЕ инверсной логики соединен с объединенными первыми входами элементов 3И - НЕ n + 1 логических пар элементов 3И - НЕ, вторые входы которых объединены и соединены выходом (n - m + 1)-входового дешифратора, n - m + 1 входов которого поразрядно подключены к Q - выходу (n - m)-го JK - триггера старшего разряда, к  выходам n - m - 1 JK - триггеров старших разрядов и к

выходам n - m - 1 JK - триггеров старших разрядов и к  выходу m-го JK - триггера младшего разряда, третий вход первого элемента 3И - НЕ нулевой логической пары элементов 3И - НЕ подключен ко входу 1рВКТ первого разряда позиционного двоичного кода n - разрядной шины управляющего кода, а выход - соединен с

выходу m-го JK - триггера младшего разряда, третий вход первого элемента 3И - НЕ нулевой логической пары элементов 3И - НЕ подключен ко входу 1рВКТ первого разряда позиционного двоичного кода n - разрядной шины управляющего кода, а выход - соединен с  входом JK - триггера нулевого разряда и с третьим входом второго элемента 3И - НЕ, выход которого соединен с

входом JK - триггера нулевого разряда и с третьим входом второго элемента 3И - НЕ, выход которого соединен с  входом JK - триггера нулевого разряда, и третьи входы первых элементов 3И - НЕ n логических пар элементов 3И - НЕ поразрядно подключены ко входам соответствующих разрядов кода Грея шины n - разрядного управляющего кода, а выходы первых элементов 3И - НЕ m логических пар элементов 3И - НЕ поразрядно соединены с

входом JK - триггера нулевого разряда, и третьи входы первых элементов 3И - НЕ n логических пар элементов 3И - НЕ поразрядно подключены ко входам соответствующих разрядов кода Грея шины n - разрядного управляющего кода, а выходы первых элементов 3И - НЕ m логических пар элементов 3И - НЕ поразрядно соединены с  входами JK - триггеров младших разрядов и с третьими входами вторых элементов 3И - НЕ, выходы которых поразрядно соединены с

входами JK - триггеров младших разрядов и с третьими входами вторых элементов 3И - НЕ, выходы которых поразрядно соединены с  входами m JK - триггеров младших разрядов, выходы первых элементов 3И - НЕ n - m - 1 логических пар элементов 3И - НЕ поразрядно соединены с

входами m JK - триггеров младших разрядов, выходы первых элементов 3И - НЕ n - m - 1 логических пар элементов 3И - НЕ поразрядно соединены с  входами n - m - 1 JK - триггеров старших разрядов и с третьими входами вторых элементов 3И - НЕ, выходы которых паразрядно соединены с

входами n - m - 1 JK - триггеров старших разрядов и с третьими входами вторых элементов 3И - НЕ, выходы которых паразрядно соединены с  входами n - m - 1 JK - триггеров старших разрядов, и выход первого элемента 3И - НЕ n-й логической пары элементов 3И - НЕ соединен с

входами n - m - 1 JK - триггеров старших разрядов, и выход первого элемента 3И - НЕ n-й логической пары элементов 3И - НЕ соединен с  входом (n - m)-го JK - триггера старшего разряда и с третьим входом второго элемента 3И - НЕ, выход которого соединен с

входом (n - m)-го JK - триггера старшего разряда и с третьим входом второго элемента 3И - НЕ, выход которого соединен с  входом (n - m)-го триггера старшего разряда,

входом (n - m)-го триггера старшего разряда,  выход которого подключен к выходной шине, и второй вход четвертого элемента 2И - НЕ инверсной логики подключен к Q - выходу первого JK - триггера младшего разряда.

выход которого подключен к выходной шине, и второй вход четвертого элемента 2И - НЕ инверсной логики подключен к Q - выходу первого JK - триггера младшего разряда.

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| Делитель частоты с переменным коэффициентом деления | 1989 |

|

SU1691958A1 |

| Многоразрядный управляемый делитель частоты | 1988 |

|

SU1529443A1 |

| Способ деления периодов следования импульсных сигналов | 1985 |

|

SU1651352A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ МОЩНОСТИ | 1999 |

|

RU2164007C1 |

Авторы

Даты

1998-09-20—Публикация

1996-07-10—Подача