Изобретение относится к аналого-цифровым преобразователям (АЦП) и может быть использовано в вычислительных системах, сигнал-процессорах и любых других устройствах, где требуется аналого-цифровое преобразование.

Известно устройство [1] для аналого-цифрового преобразования, содержащее 2n компараторов, 2n источников опорного напряжения и шифратор, переводящий унитарный позиционный 2n разрядный код с выходов компараторов в n-разрядный двоичный код (n - количество разрядов в коде АЦП). Это устройство имеет самое малое среди АЦП время τ преобразования, определяемое лишь суммой времени t1, необходимого для срабатывания одного компаратора и времени t2 срабатывания шифратора

τ>t1+t2 (1)

Однако этот АЦП обладает и самыми высокими среди АЦП аппаратурными затратами, требуя наличия 2n компараторов, 2n источников разных опорных напряжений и logn (2n) ступенчатого шифратора, состоящего из (2n- 1)/(n-1) n - разрядных шифраторов.

Наиболее близким к изобретению является устройство [2] для аналого-цифрового преобразования, содержащее (n-1) последовательно соединенных элементов аналоговой памяти, n компараторов, n регистров, шину синхронизации и шину измеряемого сигнала, причем шина измеряемого сигнала соединена с первым входом первого компаратора и со входом первого из последовательно соединенных элементов аналоговой памяти, выход каждого из которых подключен к первому входу (i+1)-го компаратора, выход i-го компаратора соединен с D-входом i-го разряда i-го регистра, выходы разрядов i-го регистра подключены к D-входам одноименных разрядов (i+1)-го регистра, входы синхронизации регистров соединены с шиной синхронизации, выходы n-го регистра являются выходами устройства, а на второй вход первого компаратора подается опорный аналоговый сигнал.

Однако это устройство обладает высокими аппаратурными затратами и невысокой точностью (высокой погрешностью преобразования), связанной с тем, что в каждом элементе аналоговой памяти, выполненном в виде аналогового регистра, происходит не только запоминание сигнала, поданного на его вход, но и вычисление разности между входным сигналом и опорным. Высокие аппаратурные затраты обусловлены необходимостью наличия в составе аналогового регистра элементов, выполняющих эти процедуры (сумматоры с инверсным входом) и элементов, выполняющих коммутацию на выход аналогового регистра либо входного сигнала, либо разности между ним и опорным сигналом. Низкая точность обусловлена тем, что погрешность Δout выходного сигнала Aout аналогового регистра содержит в себе погрешность Δref, внесенную при вычислении разности, погрешность Δc коммутации и погрешность Δm, внесенную элементом аналоговой памяти

Δout≤ Δref+Δc+Δm.

При последовательном соединении n звеньев суммарная погрешность данного устройства составит

Δ = nΔout≤n(Δref+Δc+Δm). (2)

Задачей изобретения является уменьшение аппаратурных затрат и повышение точности (уменьшение погрешности) аналого-цифрового преобразования.

Задача решается тем, что в устройство введено (n-1) цифроаналоговых преобразователей, при этом входы i-го цифроаналогового преобразователя соединены с выходами i-го регистра, выход i-го цифроаналогового преобразователя подключен к второму входу (i+1)-го компаратора.

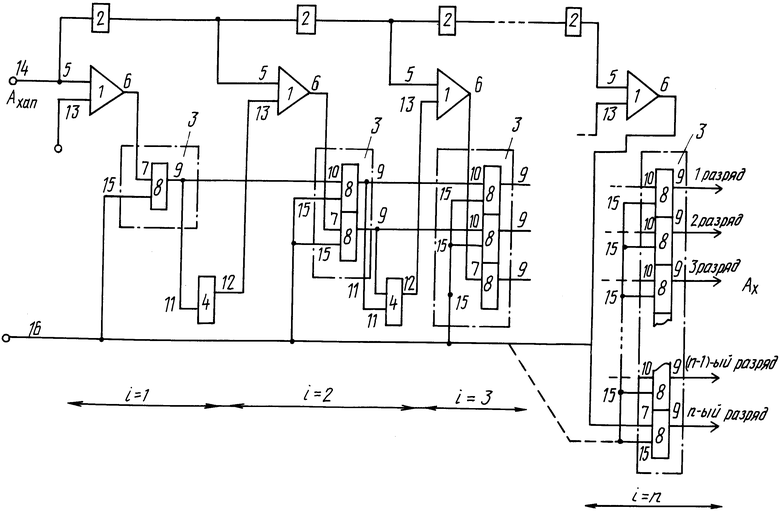

На чертеже представлена блок-схема устройства для аналого-цифрового преобразования.

Устройство содержит n аналоговых компараторов 1, (n-1) последовательно соединенных элементов 2 аналоговой памяти, n регистров 3 и (n-1) цифроаналоговых преобразователей 4, причем i-тый регистр 3 содержит i разрядов. Выход i-го элемента 2 аналоговой памяти подключен к первому входу 5 (i+1)-го компаратора, выход 6 i-го компаратора 1 соединен с D-входом 7 i-го триггера 8 i-го регистра 3 (этот триггер 8 в этом регистре 3 является триггером старшего разряда). Выходы 9 триггеров 8 разрядов i-го регистра 3 подключены к D-входам 10 триггеров одноименных разрядов (i+1)-го регистра 3 и к i входам 11 i-го цифроаналогового преобразователя 4, выход 12 которого подсоединен к второму входу 13 (i+1)-го компаратора 1. К входу 5 первого компаратора 1 подключена шина 14 измеряемого сигнала, входы 15 синхронизации всех регистров 3 соединены с шиной 16 синхронизации, а выходы 9 последнего n-го регистра 3 являются выходами устройства.

Устройство работает следующим образом.

На вход 14 устройства подается аналоговый сигнал Ax, сопровождаемый последовательностью синхронизирующих сигналов CЗ на шине 16.

Первый (i=1) из компараторов 1 сравнивает Ax, поступивший на его первый вход 5, с поданным на его второй вход 13 опорным аналоговым сигналом B1 = Amax/2, где Amax - максимально возможное значение измеряемого сигнала.

Выходной бинарный сигнал C1 на выходе 6 первого компаратора 1 определяется следующей функцией:

Таким образом, через время t1 единичный сигнал на выходе 6 компаратора 1 будет свидетельствовать о том, что старший двоичный символ ax1 в кодовом отображении сигнала

Ax= ∑ axi2n-i

равен единице.

Сигнал CЗ с шины 16 синхронизации поступает на входы 15 синхронизации всех регистров 3 с частотой F = 1/T, (причем T >t1) и инициирует запись состояния C1 выхода 6 первого компаратора 1 в первый регистр 3 (состоящий лишь из одного триггера 8) и запись Ax в первый элемент 2 аналоговой памяти;

i-й цифроаналоговый преобразователь 4 формирует из кода (b1b2...bj...bi) состояния i-го регистра 8 аналоговую величину

Bi= (Amax/2n)∑ bj2n-j,

где

bi+1= 1 всегда;

i-й компаратор 1 сравнивает сигнал Ax, поступающий на его вход 5 с выхода (i-1)-го элемента 2 аналоговой памяти, с поданным на его вход 13 с выхода 12 (i-1)-го цифроаналогового преобразователя 4 опорным аналоговым сигналом

Bi= (Amax/2n)∑ bj2n-j.

Выходной бинарный сигнал Ci i-го компаратора 1 определяется функцией

Таким образом, через время t1 единичный сигнал на выходе 6 i-го компаратора 1 будет свидетельствовать о том, что i-й двоичный символ axi в кодовом отображении сигнала

Ax= ∑ axi2n-i

равен единице, нулевой же сигнал на выходе 5 i-го компаратора 1 будет свидетельствовать о том, что axi= 0.

Сигнал CЗ 16 поступает на входы 15 синхронизации всех регистров 3 с частотой F = 1/T (причем T > t1) и инициирует запись состояния Ci выхода 6 i-го компаратора 1 в старший i-й триггер 8 i-го регистра 3 (состоящего из i триггеров) и запись Ax в i-й элемент 2 аналоговой памяти. В остальные (i-1) младшие разряды i-го регистра 3 переписываются состояния триггеров 8 предыдущего (i-1)-го регистра 3.

Таким образом, в каждый момент времени t в i-ом элементе 2 аналоговой памяти будет записано аналоговое значение сигнала Axan(t-iT), поданного на вход 14 устройства (t-iT) секунд ранее, то есть i тактов ранее, а в соответствующем i-м регистре 3 будут записаны i старших разрядов этого аналогового сигнала Axan(t-iT).

В частности, в последнем n-ом регистре 3 будет записан двоичный n-разрядный код Ax(t-nT) аналогового сигнала Axan(t-nT), поданного на вход 14 устройства n тактов (то есть nT секунд) ранее.

Время τ = T между двумя последовательными различными подачами сигнала на вход 14 устройства, то есть мертвое время устройства, не может быть меньше, чем длительность t1 срабатывания компаратора 1 с длительностью t3 переключения регистра 3 и длительностью t4 срабатывания цифроаналогового преобразователя 4

T > t1 + t3 + t4 (3)

Погрешность, возникающая на выходе элемента аналоговой памяти составляет τ, следовательно суммарная погрешность преобразования без учета погрешности, вносимой компараторами составит

Δ = nΔm, (4) (3).

что заведомо меньше, чем погрешность прототипа (2).

Предлагаемое устройство может быть выполнено в виде микросхемы и позволит создать быстродействующий, но аппаратурно экономичный аналого-цифровой преобразователь с мертвым временем, пропорциональным лишь однократному времени уравновешивания, так же как в параллельном АЦП, но с количеством элементов пропорциональным (а не экспоненциально зависящим) количеству разрядов.

В частности, при применении для быстрого преобразования большого количества (порядка 107) аналоговых сигналов в 10-разрядный код оно позволит уменьшить аппаратурные затраты (по сравнению с параллельным АЦП, например микросхемой фирмы Analog Devices, которая была применена в отсутствии предлагаемого устройства) примерно в 210/10 = 102,4 раза.

Источники информации

1. Якубовский С. В. и др. Аналоговые и цифровые интегральные микросхемы. Справочное пособие.- М.: Радио и связь, 1985, с. 353-354.

2. Патент Великобритании N 2145889, кл. H 03 M 1/38, 1985.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Устройство для акустических исследований скважин в процессе бурения | 1982 |

|

SU1108196A1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИЙ МОМЕНТОВ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1998 |

|

RU2178202C2 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| АДАПТИВНЫЙ ЛАЗЕРНЫЙ ДОПЛЕРОВСКИЙ ЛОКАТОР | 1990 |

|

RU2012013C1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2000 |

|

RU2171543C1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Анализатор спектра | 1987 |

|

SU1633366A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных и измерительных системах. Цель изобретения - повышение точности. Устройство содержит аналоговые компараторы, элементы аналоговой памяти, регистры, цифроаналоговые преобразователи и D-триггеры. 1 ил.

Устройство для аналого-цифрового преобразования, содержащее n-1 последовательно соединенных элементов аналоговой памяти, n компараторов, n регистров, шину синхронизации и шину измеряемого сигнала, причем шина измеряемого сигнала соединена с первым входом первого компаратора и входом первого из последовательно соединенных эелементов аналоговой памяти, выход каждого из которых подключен к первому входу (i + 1)-го компаратора, выход i-го компаратора соединен с D-входом i-го разряда i-го регистра, выходы разрядов i-го регистра подключены к D-входам одноименных разрядов (i + 1)-го регистра, входы синзронизации регистров соединены с шиной синхронизации, выходы n-го регистра являются выходами устройства, а на второй вход первого компаратора подается опорный аналоговый сигнал, отличающееся тем, что в устройство введено n - 1 цифроаналоговых преобразователей, при этом входы i-го цифроаналогового преобразователя соединены с выходами i-го регистра, выход i-го цифроаналогового преобразователя подключен к второму входу (i + 1)-го компаратора.

| Якубовский С.В | |||

| и др | |||

| Аналоговые и цифровые интегральные микросхемы: Справочное пособие | |||

| - М.: Радио и связь, 1985, с.353 - 354 | |||

| EP, патент, 224359, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| DE, заявка, 3619013, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| US, патент, 5014057, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| US, патент, 3641562, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| GB, патент, 2145889, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1998-08-10—Публикация

1995-07-13—Подача