11

Изобретение относится к измерительной технике и предназначено для измерений большого числа аналоговых динамических сигналов.

Цель изобретения - уменьшение полного времени преобразования устройства путем адаптивного формирования порядка следования цифровых эквивалентов измеряемых сигналов.

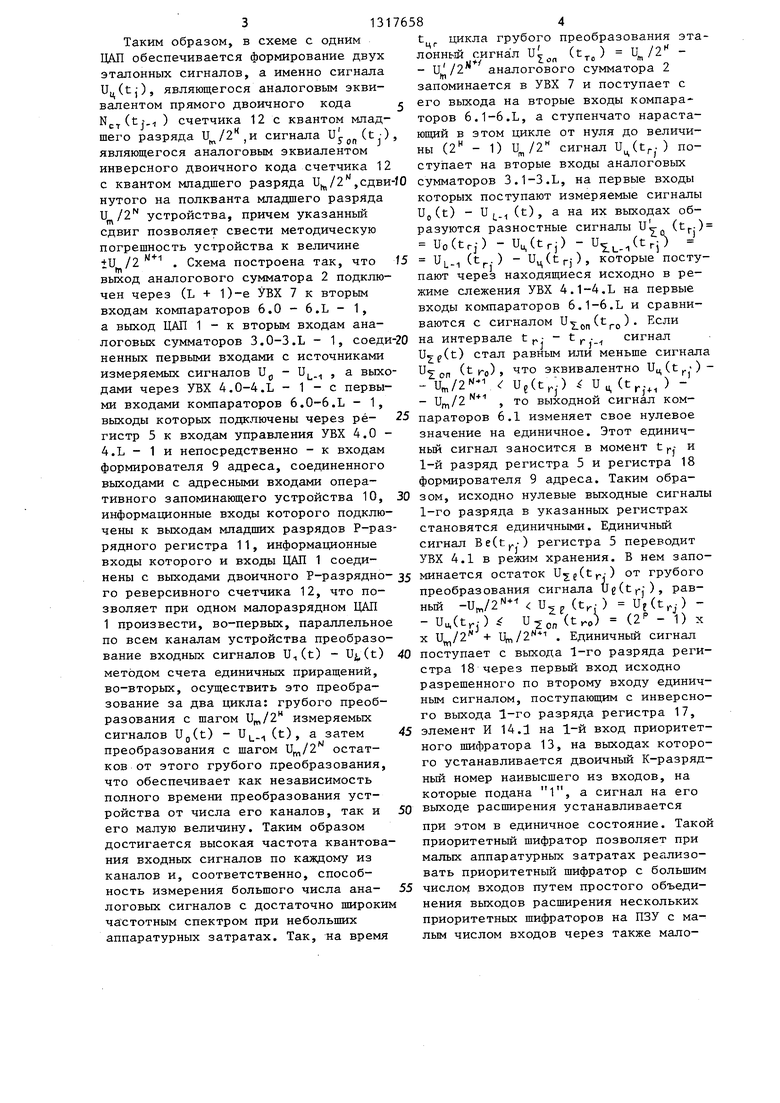

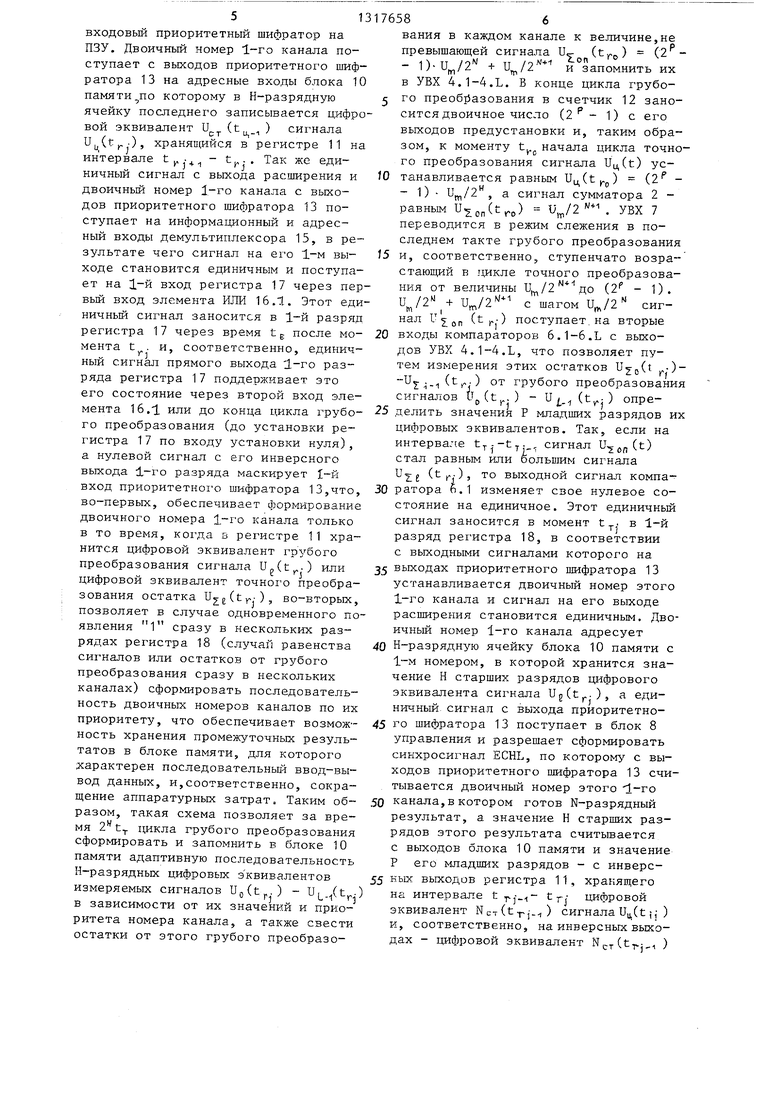

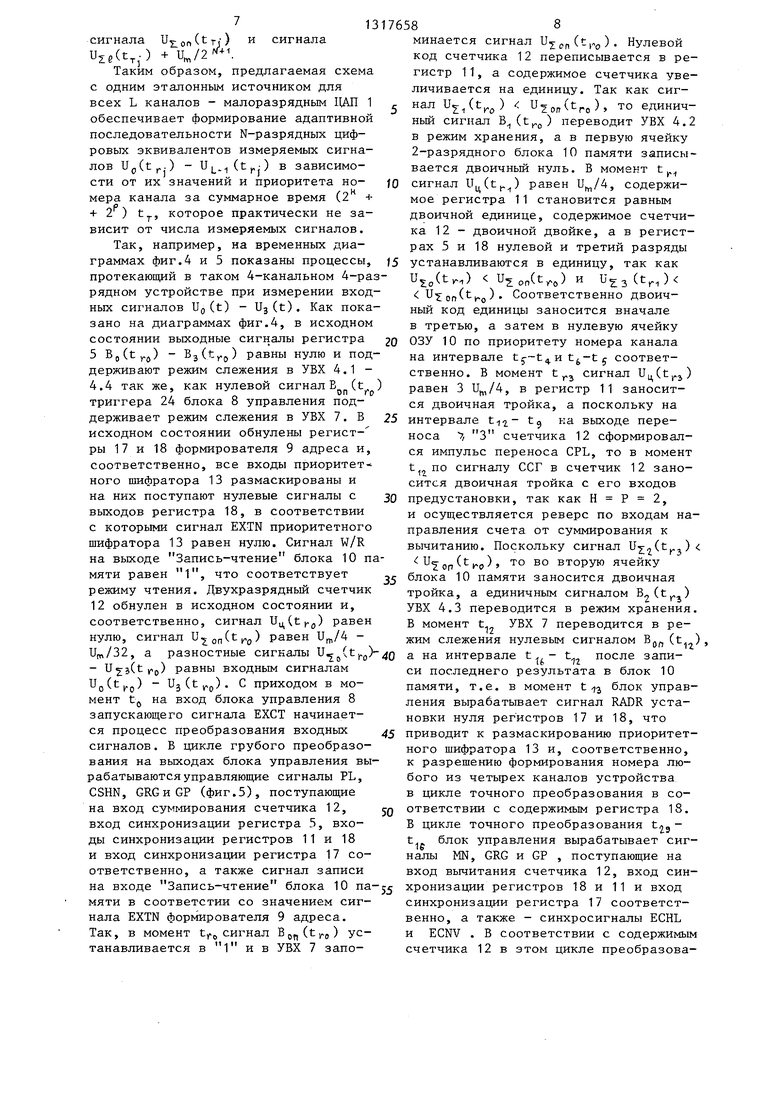

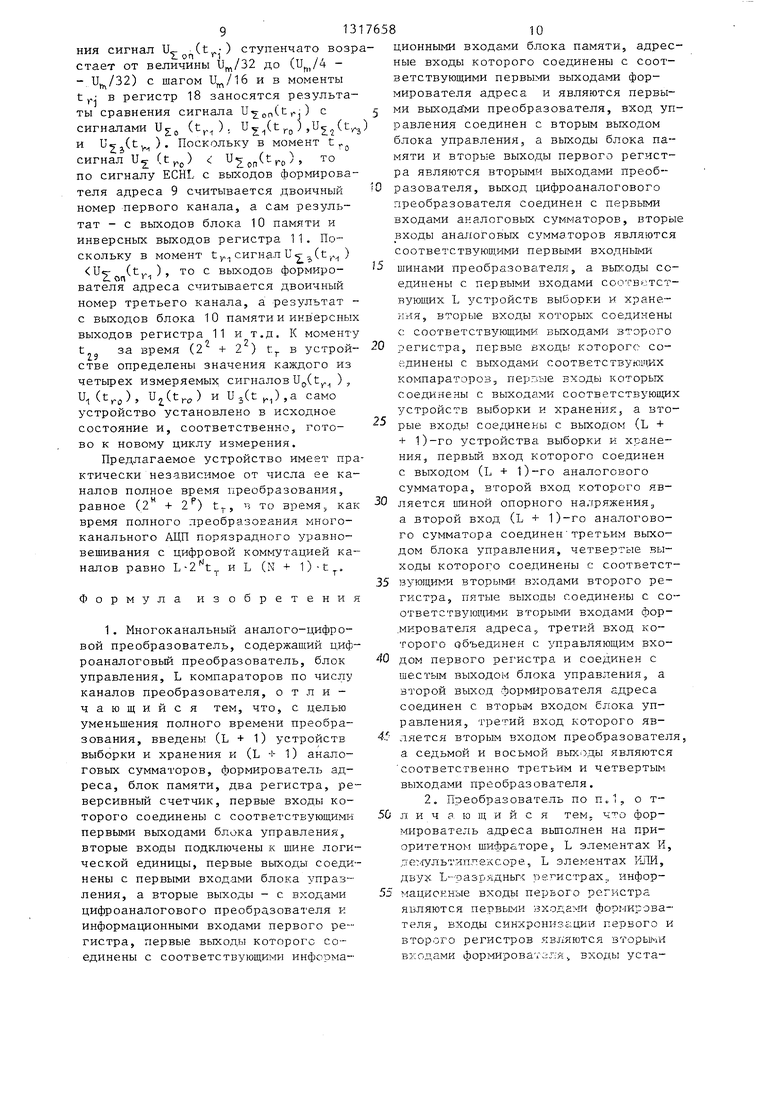

На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема формирователя адреса на фиг.З - схема блока управления; на фиг.А и 5 - временные диаграммы, поясняющие работу устройства и блока управления соответственно.

Устройство содержит Р-разрядный цифроаналоговый преоСразователь 1, аналоговый сумматор 2 с коэффициентом передачи 2 и аналоговые сумматоры 3.0-3.L с единичными коэффициентами передачи, устройства 4.0 - 4.L выборки-хранения (УБХ), L-разряд ный регистр 5, L аналоговых компараторов 6.0-6.L, (L + 1) УВХ 7, блок 8 управления, формирователь 9 адреса, блок 10 памяти емкостью 2 Н разрядных слов, Р-разрядньш регистр 11 и реверсивный счетчик 12.

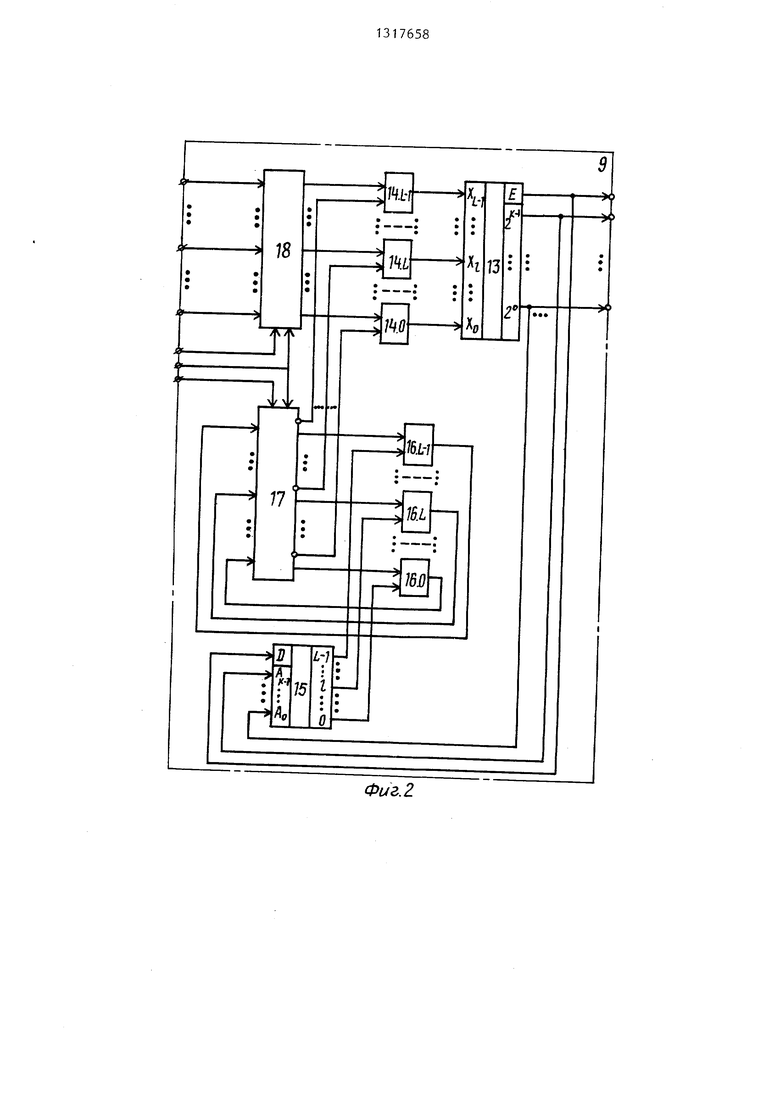

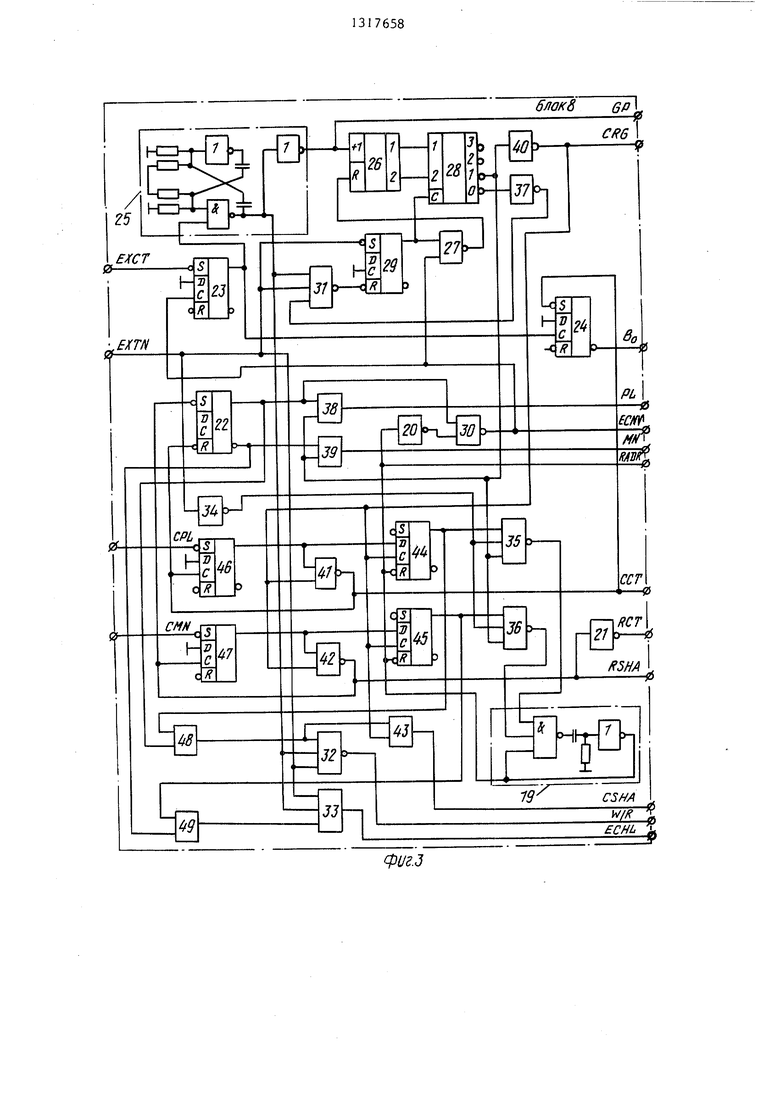

Формирователь 9 адреса содержит L-входовый приоритетный шифратор 13 элементы И 14.0-14,,L, демультиплек- сор 15, элементы ИЛИ 16.0-16.L и L- разрядные регистры 17 и 18. Блок управления содержит одновибратор 19, элементы НГг 20 и 21, D-триггеры 22 - 24, тактовый генератор 25, счетчик 26 импульсов, элемент И-НЕ 27, де- мультиплексор 28, D-триггер 29, элементы И-НЕ 30-32, элемент И 33, элемент НЕ 34, элементы И-НЕ 35 и 36-, элемент НЕ 37, элементы И 38 и 39, элемент НЕ 40, элементы И-НЕ 41 и 42 элемент И 43, D-триггеры 44-47, элементы ИЛИ 48 и 49.

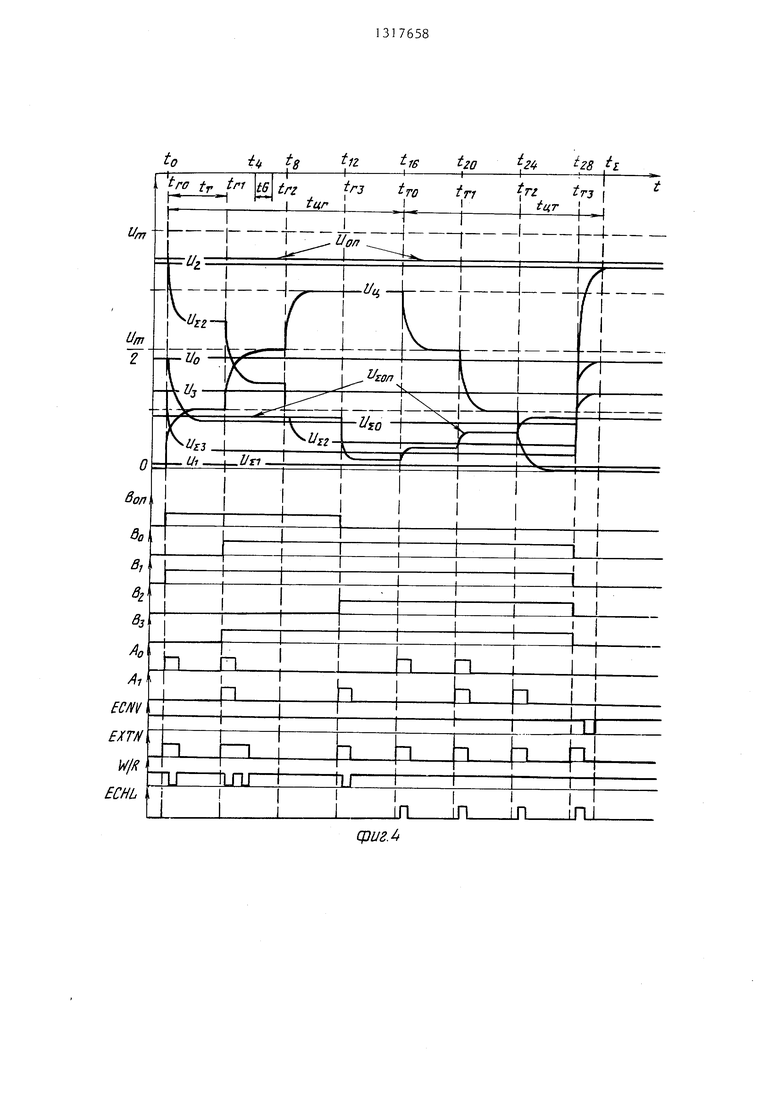

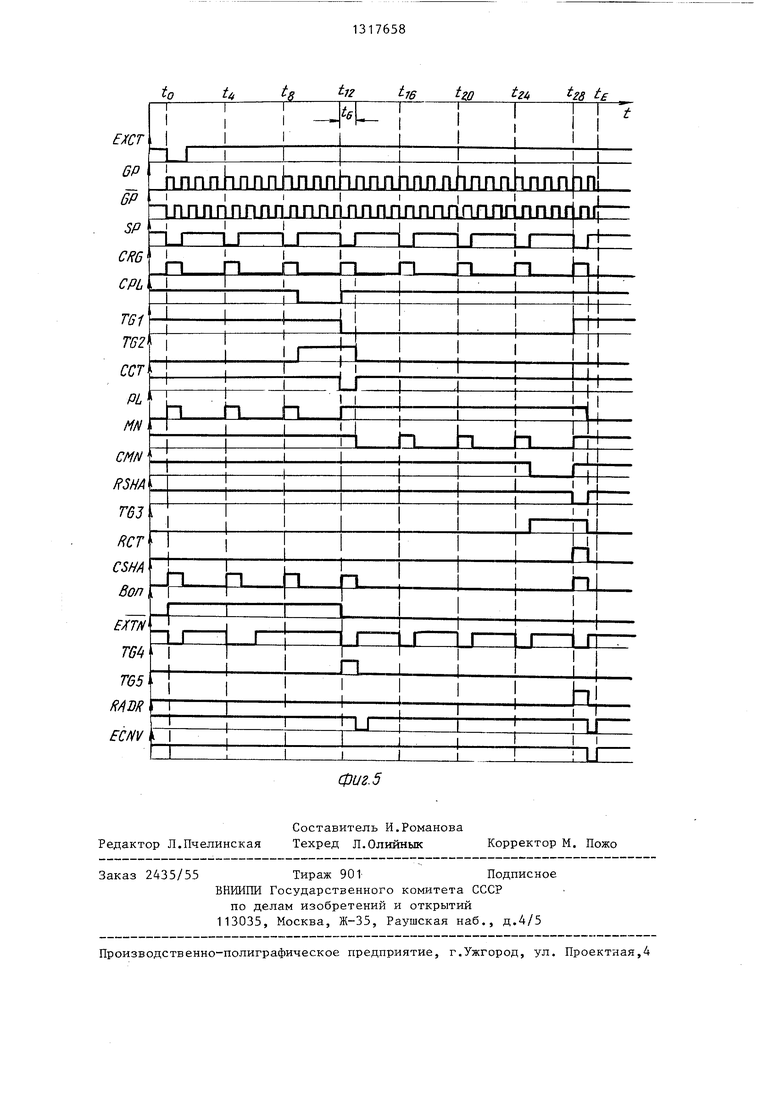

На временных диаграммах показаны величины: t - время одного такта преобразования; Гцг и tцт - время цикла грубо1 о и точного преобразования соответственно; U ,„ - амплитудньш диапазон устройства; UOH величина опорного сигнала; 11 - Ua - сигналы на первых входах аналоговых сумматоров 3.0 - 3.3; - сигналы на первых входах компараторов - 6.3; 1-U 1 - сигнал на вторых входах компараторов 6.0 - 6.3; Uu, - сигнал на входе цифроаналогового преобразователя 1; Bj - БЗ - сигналы на вко

82

дах управления УВХ 4.0 - 4.3; сигнал на входе управления УБХ 7 (фиг.4) и на инверсном выходе триггера 24 (фиг.5); Ад и А - сигналы на

адресных -входах блока 10; W/R - сигнал на входе Запись-чтение блока 10; EXTN - сигнал на выходе готовности формирователя 9 адреса; ECHL - сигнал на выходе элемента И 33; t- моменты времени выработки переднего фронта импульса на прямом выходе тактового генератора 25 (i 0,1,...,29); t. и t,- - моменты стробирования регистра |1 в циклах соответственно

грубого и точно1 о преобразования (j 0,1,.,.,3); tg - момент окончания полного цикла преобразования; tg - величина периода импульсов тактового генератора 25; ЕХСТ - сигнал на вхо, установки 1 триггера 23; GP и GP - сигналы соответственно на прямом и инверсном выходах генератора 25; SP - сигнал, на первом выходе демуль- типлексора 28; CPG - сигнал на выходе

инвертора 40; CPL и CMN - сигналы на входах установки 1 триггеров 46 и 47 соответственно; TG1, TG2, TG3, TG4 и TG5 - сигналы на прямых выхода:;; триггеров 22,46,47,44 и 45 соответственно; ССТ, RCT, PL и MTJ - сигналы на выходах схем 41, 21, 38 и 39 соответственно; EXTN - сигнал на выходе инвертора 34; RADR - сигнал на выходе одновибратора 20; ECNV - сигнал на выходе элемента И-НЕ 30.

Устройство работает следующим обазом.

На первый вход аналогового сумматора 2 поступает опорный сигнал Upn , авный (2f) - 1/2 и„, и на его второй вход поступает выходной сигал Uu,(t) 1Ш1 1, равный U,j(t-) NcTCtj-, ) и,„/2 , а на выходе суматора 2 образуется разностный сигал ), равный

55

Uon - U(tp. 2 50 (и„/2 - и ) -р

- N,(t,-., )-и„/2 N,,(t.., )-и„/2

Nr1

где N (t .. ) - двоичное содержимое счетчика 12; ,--- инверсия двоичного числа NCT (t;-i ) .

313176584

Таким образом, в схеме с однимt цикла грубого преобразования эта- ЦАП обеспечивается формирование двухлонный сигнал U эталонных сигналов, а именно сигнала- аналогового сумматора 2 U(t,-), являющегося аналоговым экви-запоминается в УВХ 7 и поступает с валентом прямого двоичного кода выхода на вторые входы компара- Nj. (tj-.i ) счетчика 12 с квантом млад-торов 6.1-6.L, а ступенчато нараста- шего разряда ,и сигнала ),ющий в этом цикле от нуля до величи- являющегося аналоговым эквиалентомны (2 - 1) сигнал U(t. ) по- инверсного двоичного кода счетчика 12ступает на вторые входы аналоговых с квантом младшего разряда ,сдви-10сумматоров 3.1-3.L, на первые входы нутого на полкванта младшего разрядакоторых поступают измеряемые сигналы и„/2 устройства, причем указанньшU(,(t) - U -1 выходах об- сдвиг позволяет свести методическуюразуются разностные сигналы () погрешность устройства к величине Uo(trj) - U(trj) - L-- . Схема построена так, что 15 U. (t,..) - Uц(tгj), которые посту- выход аналогового сумматора 2 подклю-пают через находящиеся исходно в ре- чен через (L + 1)-е УВХ 7 к вторымжиме слежения УВХ 4.1-4,L на первые входам компараторов 6.0 - 6.L - 1,входы компараторов 6.1-6.L и сравни- а выход ЦАП 1 - к вторым входам ана-ваются с сигналом , (t ) . Если логовых сумматоров 3.0-3.L - 1, соеди-20на интервале tp- - t . сигнал ненных первыми входами с источникамиU2;p(t) стал равным или меньше сигнала измеряемых сигналов U, - U,. , а выхо- оп ( го) что эквивалентно Vu()- дами через УВХ 4.0-4.L - 1 - с первы-- Un, ) U ц (t . ) - ми входами компараторов 6.0-6.L - 1,- , то выходной сигнал ком- выходы которых подключены через рё- 25параторов 6.1 изменяет свое нулевое гистр 5 к входам управления УВХ 4.0 -значение на единичное. Этот единич- 4.L - 1 и непосредственно - к входамный сигнал заносится в момент t f..- и формирователя 9 адреса, соединенного1-й разряд регистра 5 и регистра 18 выходами с адресными входами опера-формирователя 9 адреса. Таким обра- тивного запоминающего устройства 10, 30зом, исходно нулевые выходные сигналы информационные входы которого подклю-1-го разряда в указанных регистрах чены к выходам младших разрядов Р-раз-становятся единичными. Единичный рядного регистра 11, информационныесигнал Be() регистра 5 переводит входы которого и входы ЦАП 1 соеди-УВХ 4.1 в режим хранения. В нем запо- нены с выходами двоичного Р-разрядно-35минается остаток () от грубого го реверсивного счетчика 12, что по-преобразования сигнала UgCtf-;), рав- зволяет при одном малоразрядном ЦАПный (t,-) U{() - 1 произвести, во-первых, параллельное- ) . I) по всем каналам устройства преобразо-х + Цт, . Единичный сигнал вание входных сигналов U, (t) - Uji,(t) 40поступает с выхода 1-го разряда реги- методом счета единичных приращений,стра 18 через первый вход исходно во-вторых, осуществить это преобра-разрешенного по второму входу единич- зование за два цикла: грубого преоб-ным сигналом, поступающим с инверсно- разования с шагом измеряемыхго выхода 1-го разряда регистра 17, сигналов U(,(t) - UL (t) , а затем 45элемент И 14.1 на 1-й вход приоритет- преобразования с шагом остат-ного шифратора 13, на выходах которо- ков от этого грубого преобразования,го устанавливается двоичный К-разряд- что обеспечивает как независимостьный номер наивысшего из входов, на полного времени преобразования уст-которые подана 1, а сигнал на его ройства от числа его каналов, так и 50выходе расширения устанавливается его малую величину. Таким образомпри этом в единичное состояние. Такой достигается высокая частота квантова-приоритетный шифратор позволяет при ния входных сигналов по каждому измалых аппаратурных затратах реализо- каналов и, соответственно, способ-вать приоритетньш шифратор с большим ность измерения большого числа ана- 55числом входов путем простого объеди- логовых сигналов с достаточно широкимнения выходов расширения нескольких частотным спектром при небольшихприоритетных шифраторов на ПЗУ с ма- аппаратурных затратах. Так, на времялым числом входов через также мало513

входовый приоритетный шифратор на ПЗУ. Двоичный номер 1-го канала поступает с выходов приоритетного шифратора 13 на адресные входы блока 10 памяти .,по которому в Н-разрядную ячейку последнего записывается цифровой эквивалент U ( ) сигнала U,j(), хранящийся в регистре 11 на

интервале t . - t.

Так же единичный сигнал с выхода расширения и двоичный номер 1-го канала с выходов приоритетного шифратора 13 поступает на информационный и адресный входы демультиплексора 15, в результате чего сигнал на его 1-м выходе становится единичным и поступает на 1-й вход регистра 17 через первый вход элемента ИЛИ 16.1. Этот единичный сигнал заносится в 1-й разряд регистра 17 через время tg после момента t. и, соответственно, единичный сигнал прямого выхода 1-го разряда регистра 17 поддерживает это его состояние через второй вход элемента 16.1 или до конца цикла грубого преобразования (до установки регистра 17 по входу установки нуля), а нулевой сигнал с его инверсного выхода JL-ro разряда маскирует 1-й вход приоритетнох о шифратора 13,что, во-первых, обеспечивает формирование двоичного номера канала только в то время, когда в регистре 11 хранится цифровой эквивалент грубого преобразования сигнала U() или цифровой эквивалент точного преобразования остатка Uj-gCty--), во-вторых, позволяет в случае одновременного появления 1 сразу в нескольких разрядах регистра 18 (случай равенства сигналов или остатков от грубого преобразования сразу в нескольких каналах) сформировать последовательность двоичных номеров каналов по их приоритету, что обеспечивает возможность хранения промежуточных результатов в блоке памяти, для которого характерен последовательный ввод-вывод данных, и,соответственно, сокращение аппаратурных затрат. Таким образом, такая схема позволяет за время цикла грубого преобразования сформировать и запомнить в блоке 10 памяти адаптивную последовательность Н-разрядных цифровых э квивалентов измеряемых сигналов U(,(t|,.) - U|.(t. в зависимости от их значений и приоритета номера канала, а также свести остатки от этого грубого преобразо86

вания в каждом канале к величине,не превышаюш;ей сигнапа U (гс (2 -1) + и°запомнить их в УВХ 4.1-4.L. В конце цикла грубого преобразования в счетчик 12 заносится двоичное число ( 1) с его выходов предустановки и, таким образом, к моменту t начала цикла точного преобразования сигнала U4(t) устанавливается равным Uц() (2 -1) - , а сигнал сумматора 2 - равным U,,( IJJ2 . УВХ 7 переводится в режим слежения в последнем такте грубого преобразования

и, соответственно, ступенчато возрастающий в .цикле точного преобразования от величины (2 - 1). с шагом сигнал (rf) поступает, на вторые

входы компараторов 6.1-6.L с выходов УВХ 4.1-4.L, что позволяет путем измерения этих остатков U2;5(t О-Uj-.(t.) от грубого преобразования сигналов Up(t,) - и (ь,л; ) опре- делить значения Р младших разрядов их

цифровых эквивалентов. Так, если на интервале t. ,, сигнал ) стал равным или большим сигнала U j-g (t|.), то выходной сигнал компа30 ратора 6.1 изменяет свое нулевое состояние на единичное. Этот единичный сигнал заносится в момент t.. в 1-й разряд регистра 18, в соответствии с выходными сигналами которого на

выходах приоритетного шифратора 13 устанавливается двоичный номер этого 1-го канала и сигнал на его выходе расширения становится единичным. Двоичный номер 1-го канала адресует

40 Н-разрядную ячейку блока 10 памяти с 1-м номером, в которой хранится значение Н старших разрядов цифрового эквивалента сигнала Ug(t.), а единичный сигнал с выхода приоритетно45 го шифратора 13 поступает в блок 8 управления и разрешает сформировать синхросигнал ECHL, по которому с выходов приоритетного шифратора 13 считывается двоичный номер этого l-ro

50 канала, в котором готов N-разрядный результат, а значение Н старших разрядов этого результата считывается с выходов блока 10 памяти и значение Р его младших разрядов - с инверс55 кых выходов регистра 11, хранящего

на интервале 1:

цифровой

Г)-1 -г/

эквивалент Nc-r (t i-j.., ) сигнала Un(t;; ) и, соответственно, на инверсных выходах - цифровой эквивалент ( , )

сигнала U gnCtr,-) и сигнала ,.) +

Таким образом, предлагаемая схема с одним эталонным источником для всех L каналов - малоразрядным 11АЛ 1 обеспечивает формирование адаптивной последовательности N-разрядных цифровых эквивалентов измеряемых сигналов Uj,(t.) - UL.i() в зависимости от их значений и приоритета номера канала за суммарное время (2 н- + 2 ) t, которое практически не зависит от числа измеряемых сигналов.

Так, например, на временных диа-п

граммах фиг.4 и 5 показаны процессы, jf устанавливаются в единицу, так как протекающий в таком 4-канальном 4-раз- ) .) и b,(t, ) рядном устройстве при измерении входных сигналов Ug(t) - из(t). Как показано на диаграммах фиг.4, в исходном состоянии выходные сигналы регистра 20 5 B(,(ty,) - BjCtyj,) равны нулю и поддерживают режим слежения в УВХ 4.1 - 4.4 так же, как нулевой сигнал В(t ) триггера 24 блока 8 управления и ) . Соответственно двоичный код единицы заносится вначале в третью, а затем в нулевую ячейку ОЗУ 10 по приоритету номера канала на интервале соответственно. В момент t 3 сигнал Uц(t,..J равен 3 , в регистр 11 заносится двоичная тройка, а поскольку на держивает режим слежения в УВХ 7. В 25 интервале tg на вькоде переисходном состоянии обнулены регистры 17 и 18 формирователя 9 адреса и, соответственно, все входы приоритетного шифратора 13 размаскированы и на них поступают нулевые сигналы с выходов регистра 18, в соответствии с которыми сигнал EXTN приоритетного шифратора 13 равен нулю. Сигнал W/R на выходе Запись-чтение блока 10 памяти равен 1, что соответствует режиму чтения. Двухразрядный счетчик 12 обнулен в исходном состоянии и, соответственно, сигнал ицСе.,) равен нулю, сигнал U gnCtj) равен носа 7, 3 счетчика 12 сформировал ся импульс переноса CPL, то в момен сигналу ССГ в счетчик 12 зано сится двоичная тройка с его входов

30 предустановки, так как Н Р 2,

и осуществляется реверс по входам н правления счета от суммирования к вычитанию. Поскольку сигнал Uj( и j, (t ) , то во вторую ячейку

35 блока 10 памяти заносится двоичная тройка, а единичным сигналом УВХ 4.3 переводится в режим хранени В момент t, УВХ 7 переводится в ре жим слежения нулевым сигналом Вд (

и„/32, а разностные сигналы .,-40 а на интервале t - t - () равны входным сигналам

) - ). С приходом в момент tg на вход блока управления 8 запускающего сигнала ЕХСТ начинается процесс преобразования входных сигналов. В цикле грубого преобразования на выходах блока управления вырабатываются управляющие сигналы PL, CSHN, СКСиСР (фиг.5), поступающие на вход суммирования счетчика 12, вход синхронизации регистра 5, входы синхронизации регистров 11 и 18 и вход синхронизации регистра 17 соответственно, а также сигнал записи

после записи последнего результата в блок 10 памяти, т.е. в момент блок упра ления вырабатывает сигнал RADR уста новки нуля регистров 17 и 18, что

45 приводит к размаскированию приорите ного шифратора 13 и, соответственно к разрешению формирования номера лю бого из четырех каналов устройства в цикле точного преобразования в со

JQ ответствии с содержимым регистра 18 В цикле точного преобразования t. блок управления вырабатывает си налы MN, GRG и GP , поступающие на вход вычитания счетчика 12, вход си

на входе Запись-чтение блока 10 na-j хронизации регистров 18 и 11 и вход

синхронизации регистра 17 соответстмяти в соответстии со значением сигнала EXTN формирователя 9 адреса. Так, в момент t игнал .,,) устанавливается в

венно, а также - синхросигналы ECHL и ECNV . В соответствии с содержимым счетчика 12 в этом цикле преобразова176588

минается сигнал Uj(tp). Нулевой код счетчика 12 переписывается в регистр 11, а содержимое счетчика увеличивается на единицу. Так как сиг- 2 нал U(t|) ; U offCtpo), то единичный сигнал B(t) переводит УВХ 4.2 в режим хранения, а в первую ячейку 2-разрядного блока 10 памяти записывается двоичный нуль. В момент t 10 сигнал ) равен , содержимое регистра 11 становится равным двоичной единице, содержимое счетчика 1 2 - двоичной двойке, а в регистрах 5 и 18 нулевой и третий разряды

-п

устанавливаются в единицу, так как ) .) и b,(t, )

: и ) . Соответственно двоичный код единицы заносится вначале в третью, а затем в нулевую ячейку ОЗУ 10 по приоритету номера канала на интервале соответственно. В момент t 3 сигнал Uц(t,..J равен 3 , в регистр 11 заноситноса 7, 3 счетчика 12 сформировался импульс переноса CPL, то в момент сигналу ССГ в счетчик 12 заносится двоичная тройка с его входов

предустановки, так как Н Р 2,

и осуществляется реверс по входам направления счета от суммирования к вычитанию. Поскольку сигнал Uj() и j, (t ) , то во вторую ячейку

блока 10 памяти заносится двоичная тройка, а единичным сигналом ) УВХ 4.3 переводится в режим хранения. В момент t, УВХ 7 переводится в режим слежения нулевым сигналом Вд (1-

а на интервале t - t

а на интервале t - t

после записи последнего результата в блок 10 памяти, т.е. в момент блок управления вырабатывает сигнал RADR установки нуля регистров 17 и 18, что

приводит к размаскированию приоритетного шифратора 13 и, соответственно, к разрешению формирования номера любого из четырех каналов устройства в цикле точного преобразования в соответствии с содержимым регистра 18. В цикле точного преобразования t. блок управления вырабатывает сигналы MN, GRG и GP , поступающие на вход вычитания счетчика 12, вход синвенно, а также - синхросигналы ECHL и ECNV . В соответствии с содержимым счетчика 12 в этом цикле преобразования сигнал Uy (t,- ) ступенчато возрстает от величины до ( - -.) с шагом и в моменты

П

в регистр 18 заносятся результаты сравнения сигнала of,(t t-j) с

сигналами Uj- (t,,), U,(t,),U(t,

,., ). Поскольку в момент t,,

) .),

то

сигнал и (t у,

по сигналу ECHL с выходов формирователя адреса 9 считывается двоичный номер первого канала, а сам результат - с выходов блока 10 памяти и инверсных выходов регистра 11. Поскольку в момент ty, сигнал , ) и (t ) , то с выходов формирователя адреса считывается /двоичный номер третьего канала, а результат - с выходов блока 10 памяти и инв ерсных выходов регистра 11 и т,д, К моменту t за время (2 + 2 ) t в устройстве определены значения каждого из четырех измеряемых; сигналов UpCt ), и (t ) , U(tf.(, ) и и jCt ) ,а само устройство установлено в исходное состояние и, соответственно, готово к новому циклу измерения.

Предлагаемое устройство имеет практически независимое от числа ее каналов полное время преобразования, равное (2 +2 ) t, в то время, как время полного преобразования многоканального АЦП порязрадного уравновешивания с цифровой коммутацией каналов равно и L (N + 1)-t..

Формула изобретения

1. Многоканальный аналого-цифровой преобразователь, содержащий циф- роаналоговый преобразователь, блок управления, L компараторов по числу каналов преобразователя, отличающийся тем, что, с целью уменьшения полного времени преобразования, введены (L + 1) устройств выборки и хранения и (L -i- 1) аналоговых сумматоров, формирователь адреса, блок памяти, два регистра, реверсивный счетчик, первые входы которого соединены с соответствующими первыми выходами блока управления, вторые входы подключены к шине логической единицы, первые выходы соединены с первыми входами блока управления, а вторые выходы - с входами цифроаналогового преобразователя к информационными входами первого ре-- гистра, первые выходы которого соединены с соответствующими информа-

зра131765810

ционными входами блока памяти, адрес0

5

0

ные входы которого соединены с соответствующими первы:ми выходами формирователя адреса и являются первыми выхода ми преобразователя, вход управления соединен с вторым выходом блока управления, а выходы блока памяти и вторь;е выходы первого регистра являются вторыми выходами преоб-- 0 разователя, выход цифроаналогового преобразователя соединен с первыми входами аналоговых сумматоров, вторые входы аналоговых сумма.торов являются соответствуюп1,ими первыми входными 5 Бшнами преобразователя, а выходы соединены с первыми входами соответствующих L устройств выборки и хранения, вторые входы которых соединены с соответствующими выходами второго регистра, первые входь которого соединены с вьЕходами соответствую1 1,их компараторов, первые входы которых соединены с выходами соответствуюи нх устройств выборки и хранения, а вторые входы соединены с выходоъ; (L + + 1)-го устройства выборки и хранения, первый вход которого соединен с выходом (L + 1)-го аналогового сумматора, второй вход которого является шиной опорного напряжения5 а второй вход, (L + 1)-го аналогового сумматора соединен третьим выходом блока управления, четвертые выходы которого соединены с соответствующими вторыми входами второго регистра, пятые выходы соединены с соответствующими вторыми входами фор- .мирователя адреса., третий вход которого объединен с управляющим входом первого регистра и соединен с шестым выходом блока управления, а второй выход формирователя адреса соединен с вторым входом блока управления, третий вход которого яв- 4.5- ляется вторым входом преобразователя, а седьмой и восьмой выходы являются соответственно третьим и четвертым выходами преобразователя,

2. Преобразователь по ., о т- л и ч а. ю щ и и с я тем. что формирователь адреса вьтолнен на приоритетном шифраторе, L элементах К, де.-гультиплексоре, L элементах РШИ, . L- разрядньГ С регистрах., информационные входы первого регистра являются первьЕми входами формирователя, входы синхронизации первого и

второго регистров являются ВТОРЫ1 1И

входами формирова г;;ля,, входы уста35

40

50

новки в О являются третьим входом формирователя, а выходы первого регистра соединены с первьми входами соответствующих элементов И, вторые входы которых соединены с инверсными выходами второго регистра, а выходы - с соответствующими входами приоритетного шифратора, выходы которого являются соответственно первым и вторым выходом формирователя и подключены к соответствующим адреным входам и информационному входу демультиплексора соответственно,выходы которого соединены с первыми входами соответствующих элe feнтoв ИЛИ, вторые входы которых соединены с соответствующими прямыми выходами второго регистра, инфотзмапионные вхды которого соединены с выходами соответствующих элементов ИЛИ соответственно.

3. Преобразователь по n.l, отличающийся тем, что блок управления выполнен на тактовом генераторе, счетчике импульсов, пяти элементах НЕ, демультиплексоре. семи D-триггерах, восьми элементах И-НЕ, четырех элементах И. двух элементах 11ПИ, одновибраторе, выход которого соединен с R-входами первого и второго D-триггеров, входом первого элемента НЕ, выход которого соединен с первым входом первого элемента И-НЕ, выход которого соединен с С-входом третьего D-триггера, первым входом второго элемента И-НЕ и является восьмым выходом блока, пятыми выходами которого являются выходы одновибратора и тактового генератора, первый выход последнего из которых соединен с входом суммирования счетчика импульсов, вход установки нуля которого соединен с выходом второго элемента И-НЕ, второй вход которого объединен с входом синхронизации демультиплексора и соединен с прямым выходом четвертого D-триггера, С-вход которого соединен с общей шиной, о-вход объединен с первыми входами третьего и четвертого элементов И-НЕ, первым входом первого элемента И, входом второго элемента НЕ и является вторым входом блока, первыми выходами которого являются выходы второго и третьего элементов И, пятого элемента И-НЕ и третьего элемента НЕ, вход последнего из которых объединен с С-входом пятого D-триггера, S-входом шестого D-тpиг

гера, подключен к выходу шестого элемента И-НЕ, первый вход которого объединен с D-входом первого D-триггера и соединен с прямым выходом пятого D-триггера, S-вход которого и S-вход седьмого D-триггера являются первыми входами блока, четвертыми выходами которого являются выход шестого элемента И-НЕ и четвертого элемента

И, первый вход которого объединен с С-входами первого и второго D-триггеров, вторым входом шестого элемента И-НЕ, первым входом пятого элемента И-НЕ, соединен с выходом четвертого элемента НЕ и шестым выходом блока, седьмым выходом которого является выход первого элемента И-НЕ, второй вход которого объединен с вторыми входами третьего и четвертого

элементов И-НЕ и подключен к второму выходу тактового генератора, вход которого объединен с С-входом восьмого D-триггера и подключен к прямому выходу третьего D-триггера, D-вход соединен с общей шиной, а S-вход является третьим входом блока, третьим выходом которого является инверсный выход восьмого D-триггера, D-вход которого соединен с общей шиной, а

S-вход соединен с выходом пятого элемента И-НЕ, второй вход которого объединен с D-входом второго D-триггера и соединен с прямым выходом седьмого D-триггера, D-вход которого и D-вход

пятого D-триггера соединены с общей , а С-вход объединен с R-BXO- дом шестого D-триггера и соединен с выходом пятого элемента И-НЕ, прямой выход шестого D-триггера соединен с

первыми входами второго элемента И и первого элемента ИЛИ и вторым входом первого элемента И-НЕ, а инверсный выход шестого D-триггера соединен с первыми входами второго элемента

ИЛИ и третьего элемента И-НЕ, второй вход которого объединен с вторым входом третьего элемента И-НЕ, первыми входами седьмого и восьмого элементов ИЛИ-НЕ, входом четвертого элемекта НЕ и соединен с первым выходом демультиплексора, второй выход которого через пятый элемент НЕ соединен с третьим входом третьего элемента И-НЕ, выход которого соединен с RЕходом четвертого D-триггера, прямой выход которого соединен с информационным входом демультиплексора, адресные входы которого соединены с соответствующими выходами счетчика им13131

пульсов, вторые входы седьмого и восьмого элементов И-НЕ соединены с выходом второго элемента НЕ, а третьи входы объединены с вторыми входами первого и второго элементов ИЛИ соответственно и подключены к прямым выходам второго и первого Б-триггеров, а выходы седьмого и восьмого элемен765814

тов И-НЕ соединены с первьм и вторым входами одновибратора, выходы первого и второго элементов ИЛИ соединены соответственно с третьими

с входами четвертого и первого элементов И-НЕ, выход четвертого элемента И-НЕ является вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Устройство для ввода информации | 1981 |

|

SU964625A1 |

| Устройство контроля | 1985 |

|

SU1291931A1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1987 |

|

SU1453397A1 |

| Многоканальный аналого-цифровой процессор | 1983 |

|

SU1120375A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| Многоканальное устройство для включения резервных радиостанций | 1990 |

|

SU1748299A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

Изобретение относится к измерительной технике и предназначено для измерений большого числа динамических сигналов. Цель изобретения - уменьшение полного времени преобразования - достигается тем, что в многоканальный аналого-цифровой преобразователь, содержащий цифроаналоговый преобразователь, блок управления и цо числу каналов преобразования компараторы, введены устройства выборки-хранения и аналоговые сумматоры, формирователь адреса, блок памяти, два регистра и реверсивный счетчик. 2 з.п. ф-лы, 5 ил. со о: ел 00

(риг.1

Фиг.г

CSHA У

CHir

to

tiz

re tzo 2 iz8 pi

| Балакай В.Г | |||

| и др | |||

| Интегральные схемы АЦП и ЦАП | |||

| - М.: Энергия,1978 | |||

| Гнатек Ю.Р | |||

| Справочник по цифро- аналоговым и аналого-цифровым преобразователям | |||

| -М.:Радио и связь, 1982, с.425, рис.5.93. |

Авторы

Даты

1987-06-15—Публикация

1985-10-29—Подача