Изобретение относится к области электронной техники и в частности к интегральным схемам.

Известна интегральная схема в виде кристалла с балочными выводами (Моряков О. С. , Сборка, серия "Технология полупроводниковых приборов и изделий микроэлектроники", кн. 9, М.: Высшая школа, 1990, с. 38-42). Особенностью балочных выводов является то, что примерно, на 2/5 своей длины выводы крепятся на лицевой поверхности кристалла, а на 3/5 - выходят за габарит кристалла. Балочные выводы имеют толщину от 13 до 25 мкм (в зависимости от их длины) и состоят в основном из золота. Благодаря этому интегральная схема монтируется как пайкой, так и сваркой.

Изготовление известной интегральной схемы включает следующие основные операции:

изготовление интегральных схем в составе полупроводниковой подложки, включая выводы;

селективное осаждение золота и образование балочных выводов;

уменьшение толщины полупроводниковой подложки с обратной стороны;

разделение полупроводниковой подложки на кристаллы травлением.

Однако интегральная схема в виде кристалла с балочными выводами является дорогой и нуждается в герметизации. Кроме того, балочные выводы при транспортировке и монтаже деформируются и обламываются. Все это привело к тому, что в настоящее время от кристаллов с балочными выводами повсеместно отказываются.

Изобретение направлено на устранение вышеуказанных недостатков и получение интегральной схемы, которая надежно загерметизирована, обладает меньшими размерами, большей механической прочностью и быстродействием.

Поставленная цель достигается тем, что в интегральной схеме согласно изобретению полупроводниковый кристалл соединен всей своей лицевой поверхностью с диэлектрической платой, в полупроводниковом кристалле и диэлектрической плате выполнены выемки, расположенные соответственно под и над выводами полупроводникового кристалла, на который нанесено герметизирующее диэлектрическое покрытие.

При этом толщина полупроводникового кристалла составляет 5 - 20 мкм. Выемки выполняют в центральной области концевой части выводов.

Диэлектрическая подложка изготовлена из влагостойкого стекла, соответствующего материалу полупроводникового кристалла по коэффициенту теплового расширения.

Согласно способу изготовления интегральной схемы, на лицевую сторону полупроводниковой подложки приклеивают диэлектрическую плату, утонение полупроводниковой подложки осуществляют до 5 - 20 мкм, а при разделении полупроводниковой подложки на кристаллы удаляют полупроводниковый материал под выводами с образованием выемок, на поверхность кристаллов наносят герметизирующее диэлектрическое покрытие, удаляют материал диэлектрической платы с образованием выемок над выводами и разделением диэлектрической платы на интегральные схемы.

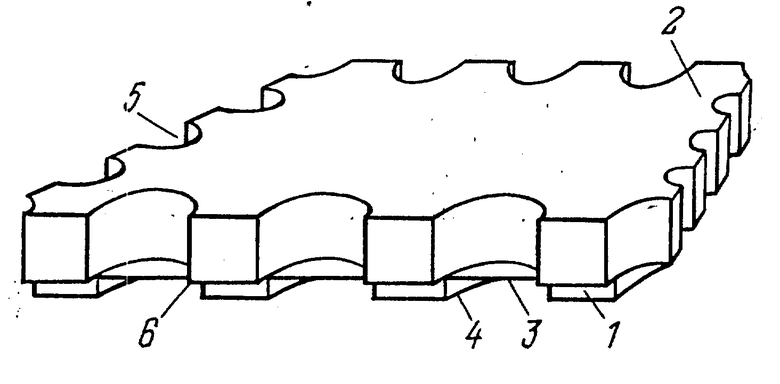

Интегральная схема, изображенная на чертеже, содержит полупроводниковый кристалл 1, диэлектрическую плату 2, выводы 3 и диэлектрическую пленку 4. В диэлектрической плате имеются выемки 5, открывающие центральные области концевой части выводов кристалла.

В кристалле, имеющем толщину от 5 до 20 мкм, выполнены выемки 6. Лицевой стороной кристалл и его выводы, полностью выходящие за его габариты соединены, например, при помощи клея, с диэлектрической платой, выполненной из влагостойкого стекла толщиной 100 мкм. С обратной стороны кристалл, в том числе с торцов, покрыт диэлектрической пленкой, которая частично заходит на диэлектрическую плату и выводы кристалла (кроме внешнего края). Диэлектрическая пленка имеет толщину 1 - 2 мкм и может быть выполнена, например, из позитивного фоторезиста. Таким образом, диэлектрические плата и пленка надежно герметизируют кристалл.

Интегральную схему согласно изобретению изготавливают следующим образом.

Вначале интегральные схемы изготавливают в составе полупроводниковой подложки. При этом контактные площадки, например, размером 100х100 мкм и выполненные из алюминия, располагают строго по периметру интегральной схемы. Расстояние между контактными площадками соседних интегральных схем на полупроводниковой подложке сокращают до 20 мкм.

После контроля годности интегральных схем на лицевую сторону полупроводниковой подложки приклеивают диэлектрическую плату (например, из стекла). Толщина подложки составляет 100 мкм. Клей влагостойкий и вакуумноплотный. Его толщина не превышает 10 мкм.

Затем единую полупроводниковую подложку закрепляют на технологическую подложку диэлектрической платой вниз и механически сошлифовывают полупроводниковую подложку до толщины 25 мкм. Далее плазмохимическим способом удаляют еще 5 мкм. Поверхность полупроводниковой подложки маскируют, оставляя свободными промежутки между интегральными схемами и над контактными площадками. Стандартным плазмохимическим способом в этих местах травят полупроводниковый материал. Поверхность полупроводниковой подложки повторно маскируют и удаляют диэлектрическую изоляцию над контактными площадками. При необходимости контактные площадки химически покрывают другими металлами или сплавами, например, никелем. Пленка фоторезиста не удаляется и служит надежным герметиком.

Наконец, диэлектрическую плату разделяют на интегральные схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Контактирующее устройство для контроля кристаллов СВЧ монолитных интегральных схем | 1986 |

|

SU1415476A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ ТРЕХМЕРНОГО МОДУЛЯ | 2012 |

|

RU2498454C1 |

| Мощная гибридная интегральная схема СВЧ-диапазона | 2023 |

|

RU2817537C1 |

| МОЩНАЯ ГИБРИДНАЯ ИНТЕГРАЛЬНАЯ СХЕМА СВЧ-ДИАПАЗОНА | 2005 |

|

RU2298255C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРЕХМЕРНОГО МНОГОКРИСТАЛЬНОГО МИКРОМОДУЛЯ | 2005 |

|

RU2299497C2 |

| МОЩНАЯ ГИБРИДНАЯ ИНТЕГРАЛЬНАЯ СХЕМА СВЧ-ДИАПАЗОНА | 2011 |

|

RU2458432C1 |

| ПОЛУПРОВОДНИКОВЫЙ ГАЗОВЫЙ СЕНСОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1998 |

|

RU2143678C1 |

| ГИБРИДНАЯ ИНТЕГРАЛЬНАЯ СХЕМА СВЧ-ДИАПАЗОНА | 2005 |

|

RU2302056C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ГИБРИДНОЙ ИНТЕГРАЛЬНОЙ СХЕМЫ СВЧ-ДИАПАЗОНА | 2009 |

|

RU2417480C1 |

| МОЩНАЯ ГИБРИДНАЯ ИНТЕГРАЛЬНАЯ СХЕМА СВЧ-ДИАПАЗОНА | 2009 |

|

RU2390071C1 |

Использование: в микроэлектронике. Сущность изобретения: интегральная схема содержит полупроводниковый кристалл с выводами, имеющимися на его лицевой поверхности по периметру, диэлектрическую плату, на которой смонтирован полупроводниковый кристалл, соединенный своими выводами с диэлектрической платой, причем полупроводниковый кристалл присоединен к диэлектрической плате своей лицевой поверхностью. В полупроводниковом кристалле и диэлектрической плате выполнены выемки, расположенные соответственно под и над выводами полупроводникового кристалла, на который нанесено герметизирующее диэлектрическое покрытие. Способ изготовления интегральной схемы заключается в уменьшении толщины полупроводниковой подложки с обратной стороны до толщины 5-20 мкм, проводят разделение подложки на кристаллы, причем при разделении подложки на кристаллы удаляют материал полупроводниковый им диэлектрической подложек над и под выводами кристалла с образованием выемок. 2 с.и 3 з.п. ф-лы, 1 ил.

Авторы

Даты

1998-08-10—Публикация

1994-08-11—Подача