Настоящее изобретение относится к схеме для селективного возбуждения строк элементов изображения в дисплее на жидких кристаллах и, в частности, к схеме драйвера селекции строк, использующего тонкопленочные транзисторы, размещенные на подложке жидкокристаллического дисплея.

Устройства отображения, использующие дисплеи на жидких кристаллах или иные подобные устройства, содержат тонкопленочные МОП-транзисторы на стеклянной подложке. В настоящее время практически все коммерчески доступные активные матричные жидкокристаллические дисплеи являются несканируемыми.

Несканируемый активный матричный жидкокристаллический дисплей требует один внешний проводник на каждую линию столбца и строки. Например, драйвер прямого сопряжения линий для черно-белого дисплея 768 х 1024 компьютера XGA потребовал бы 1792 проводников. Потребность в таком большом числе проводников в драйвере дисплея представляет главную проблему, которая становится еще более серьезной с увеличением разрешения дисплеев и сложности их конструкций. Двумя основными путями решения этой проблемы являются сокращение требуемого числа входных проводников и интеграция схем драйвера, таких как сдвиговые регистры и ключевые схемы с фиксацией состояния непосредственно на подложку дисплея.

В патенте США N 5034735 описано устройство возбуждения, использующее по два транзистора на строку элементов изображения для формирования сигналов селекции и деселекции (отмены селекции) с последовательного адресования их посредством транзисторных управляющих ключевых схем. Эти транзисторы могут быть сформированы в виде тонкопленочных транзисторов на стеклянной подложке вместе с переключающей схемой 43, блоком генерации переключающего сигнала 41, шиной сканирующего сигнала селекции 411 и шиной сканирующего сигнала деселекции 412.

В патенте США N 5157386 описана схема возбуждения активного матричного жидкокристаллического дисплея с M строками и N столбцами цифровыми видеоданными из K бит. Аналоговый ключ, имеющий открытое и закрытое состояния, получает напряжение видеосигнала и управляющий сигнал и селективно выдает на выход напряжение видеосигнала на каждый столбец в ответ на управляющий сигнал. Эта схема, однако, не является схемой селективного возбуждения строк дисплея.

В патенте США N 5113181 описано дисплейное устройство, содержащее множество элементов изображения, упорядоченных в строки и столбцы. Раскрыто выполнение демультиплексора драйвера данных.

Вышеуказанные патенты США характеризуют собой наилучшие известные заявителю технические решения-аналоги. Практически все другие коммерчески доступные активные матричные жидкокристаллические дисплеи являются несканируемыми.

Настоящее изобретение решает указанные выше проблемы путем использования интегральной схемы драйвера селекции строк. Функция новой схемы драйвера селекции строк аналогична функции сдвигового регистра.

Предложена схема для использования в жидкокристаллическом дисплее, который имеет первое множество столбцов элементов изображения и второе множество строк элементов изображения, выполненных на подложке, например, из стекла. Схема содержит множество схем драйвера селекции строк соответственно числу строк элементов изображения, электрически возбуждающих строки элементов изображения. Схемы драйвера селекции строк размещены на стеклянной подложке со столбцами и строками элементов изображения. Выход каждой из схем драйвера селекции строк соединен с соответствующей линией строки элементов изображения и с последующей схемой драйвера селекции строк в качестве схода возбуждения. Переключающее устройство, внешнее по отношению к жидкокристаллическому дисплею, имеет проводники, электрически соединенные со схемами драйвера селекции строк, причем число проводников много меньше, чем число строк элементов изображения. В одном из примеров число проводников уменьшено с 240 до 10.

Следовательно, задачей настоящего изобретения является снижение стоимости изготовления и повышение надежности за счет исключения необходимости монтажа интегральных схем на отдельной подложке.

Дополнительной задачей изобретения является создание новой схемы возбуждения цепей драйвера селекции, которая может быть непосредственно интегрирована на подложку дисплея. Благодаря этому исключаются затраты на создание периферийных интегральных схем и гибридный узел, необходимые для несканируемых активных матричных жидкокристаллических дисплеев. Эти и другие особенности изобретения будут понятны из последующего детального описания с cсылками на чертежи, на которых представлено следующее:

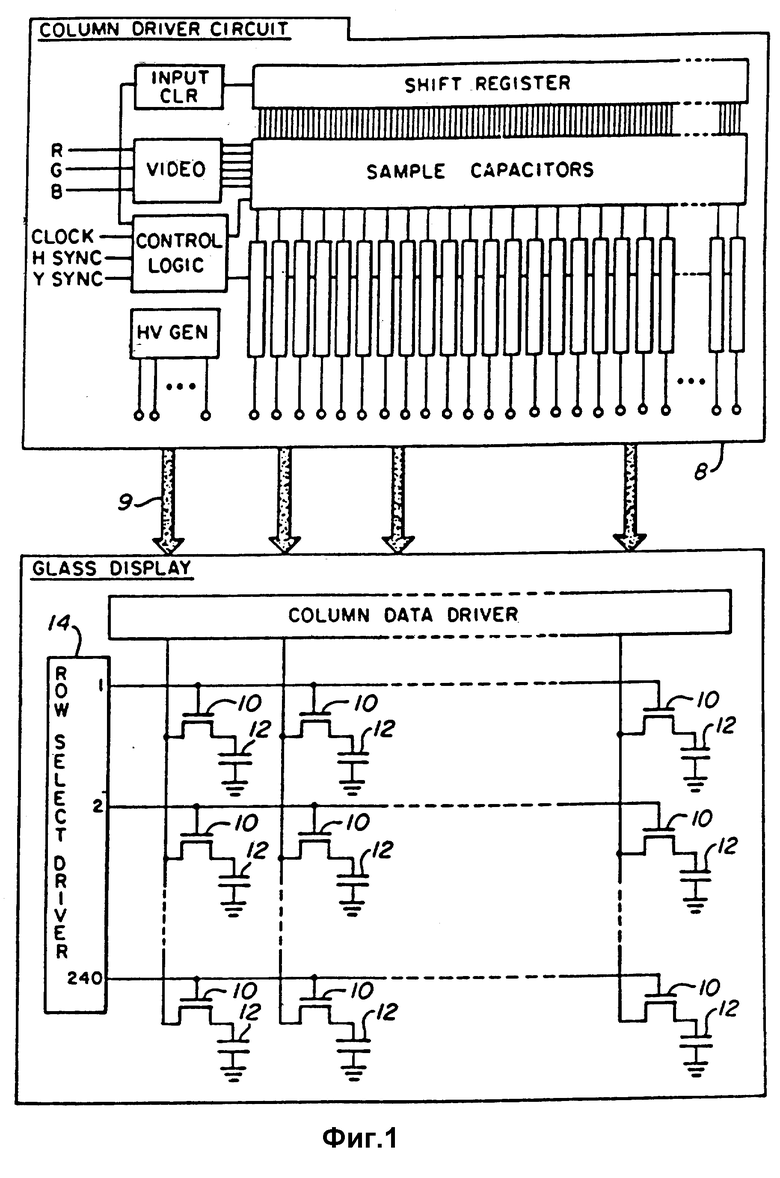

Фиг. 1 - блок-схема цепи, в которой может быть использована схема драйвера селекции строк, соответствующая настоящему изобретению;

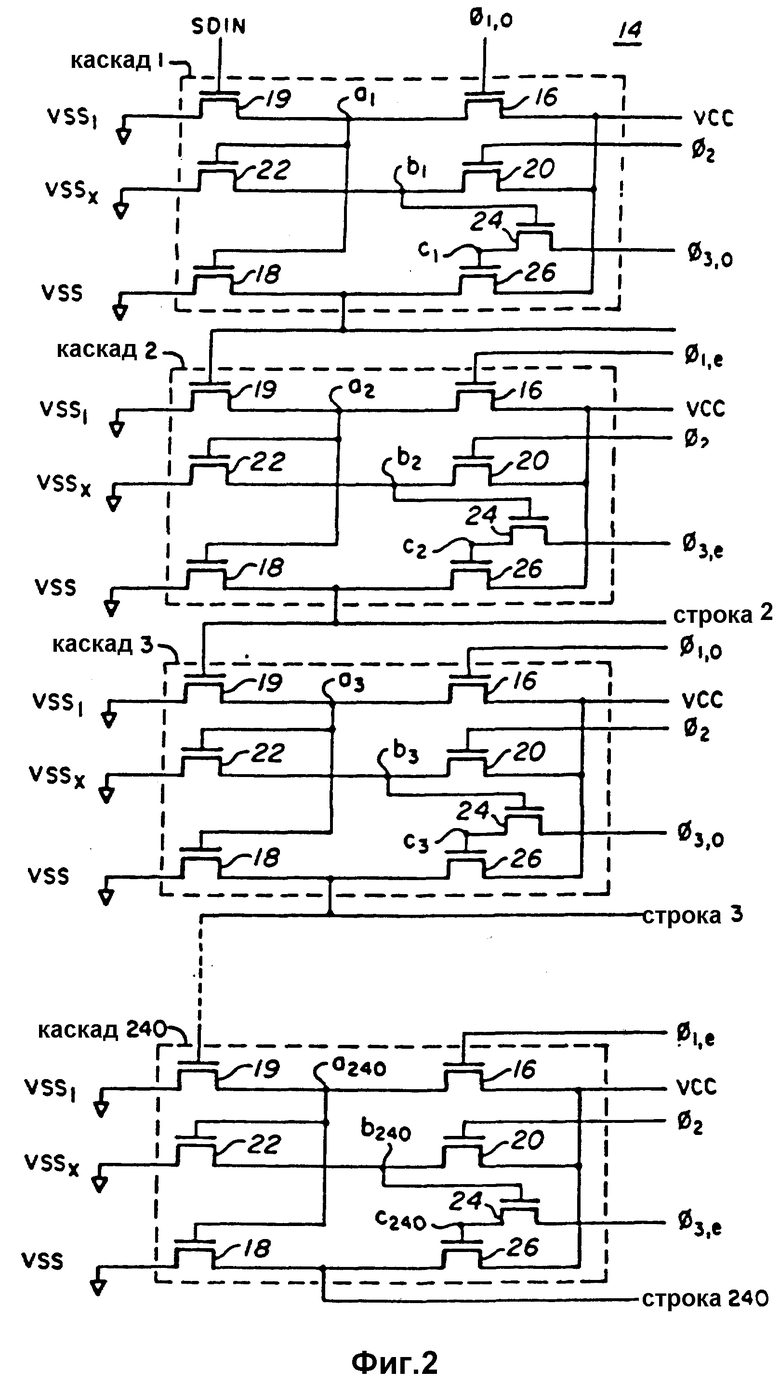

Фиг. 2 - схема устройства, соответствующего настоящему изобретению;

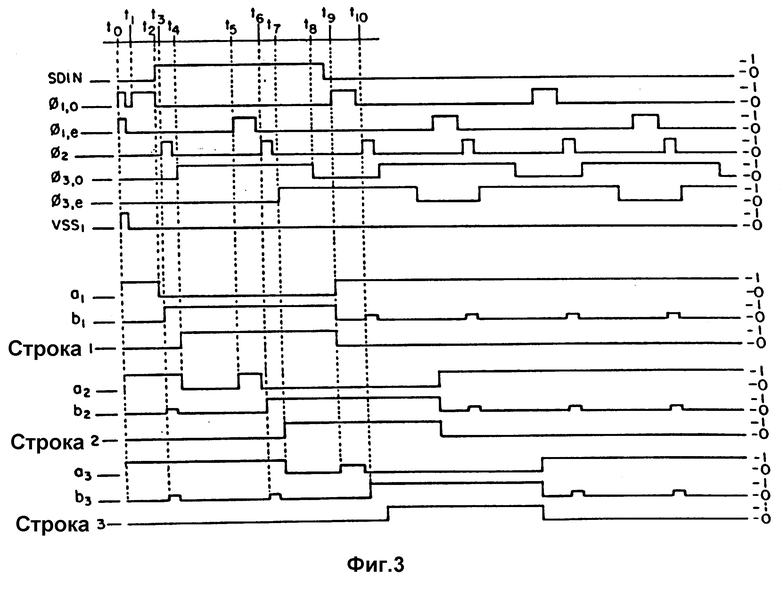

Фиг. 3 - временная диаграмма входных и выходных сигналов в схемах по фиг. 2;

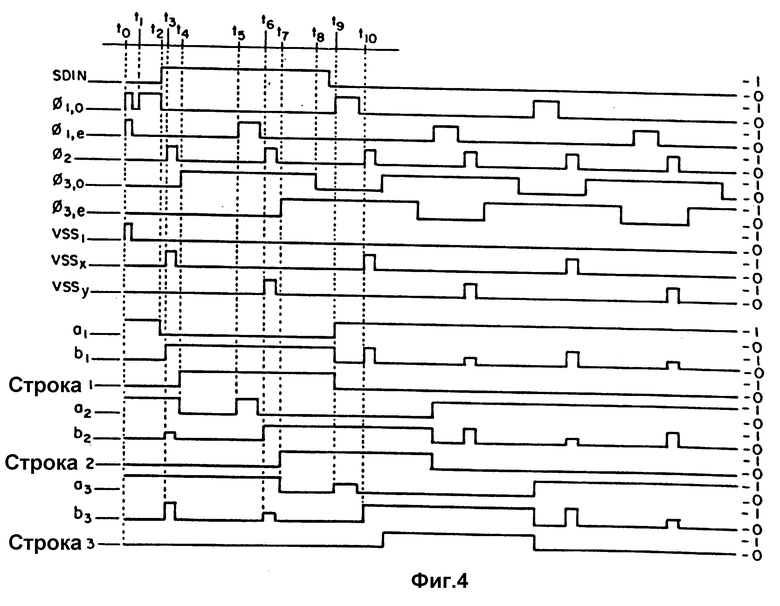

Фиг. 4 - альтернативная временная диаграмма входных и выходных сигналов в схемах по фиг. 2, когда VSSx во всех четных каскадах заменен дополнительной псевдо-землей, VSSy;

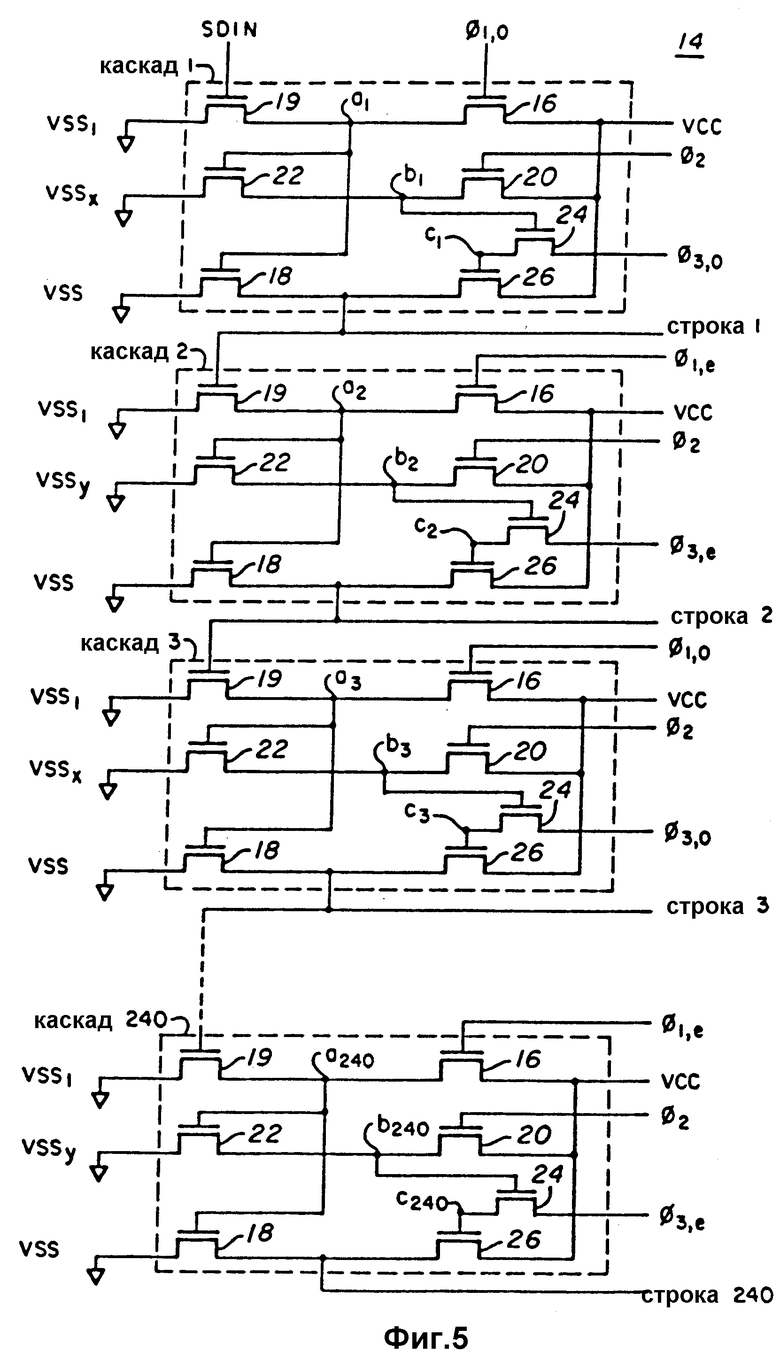

Фиг. 5 - схема альтернативного варианта выполнения изобретения для случая, когда VSSx во всех четных каскадах заменена VSSy.

Настоящее изобретение будет описано на примере дисплея с 384 х 240 элементами изображения цветного портативного телевизионного приемника. Блок-схема, показанная на фиг. 1, детально описана в совместно поданной заявке N 971721 от 3 ноября 1992 г. на "Схему драйвера данных для жидкокристаллического дисплея", которая приведена здесь для ссылки. Блок 14, обозначенный как драйвер селекции строк, характеризует собой настоящее изобретение и показан как взаимосвязанный только с первыми двумя строками и с последней строкой транзисторов элементов изображения 10 и конденсаторов 12. Схема драйвера селекции строк 14 соединена с переключающим устройством или логическим блоком управления в схеме управления 8 выключения дисплея, как пояснено в вышеуказанной заявке. Проводники 9 связывают переключающее устройство или логический блок управления со схемой драйвера селекции строк 14 на дисплее. Детальное построение схемы драйвера селекции строк, соответствующего настоящему изобретению, показано на фиг. 2.

Следует иметь в виду, что хотя схема селекции драйвера строк 14 показана только на одной стороне стеклянной подложки дисплея на фиг. 1, она может также включать вторую идентичную схему драйвера селекции строк, соединенную с линиями строк элементов изображения на противоположной стороне стеклянной подложки дисплея. Эта вторая схема драйвера селекции строк позволит обеспечить избыточность и повысить эффективность диагностики схемы при осуществлении обслуживания.

В схеме драйвера селекции строк 14 имеется 240 идентичных схемных каскадов. Каждый схемный каскад выделен пунктирным прямоугольником и обозначен соответственно как каскад 1, каскад 2, каскад 3 и т.д. до каскада 240. Все каскады c 3-го по 240-й идентичны. Схема селекции драйвера строк 14 предпочтительно изготавливается на тонкопленочных транзисторах, выполненных на подложке жидкокристаллического дисплея, и предназначена для генерации сигналов сканирования дисплея путем включения и выключения выделенных строк транзистора 10 элементов изображения.

Настоящее изобретение, в частности, нацелено на сокращение числа внешних проводников для соединения со схемами драйвера селекции, например, с 240 до 10 в рассматриваемом случае. Эта схема решает указанную проблему использования тонкопленочных транзисторов, имеющих невысокие рабочие характеристики, такие как низкая мобильность, неравномерность пороговых напряжений, сдвиг пороговых напряжений, а также проблему непосредственного их размещения на стеклянной подложке.

Как показано на фиг. 2, схема драйвера селекции строк 14 разделена на нечетные и четные каскады. Каждый каскад предпочтительно содержит 7 транзисторов. Выход каскада 1 соединен с входом каскада 2 и с линией первой строки транзисторов 10 элементов изображения. Выход каскада 2 соединен с входом каскада 3 и с линией второй строки элементов изображения и т.д. до каскада 240. На все каскады поступает общий или первый тактовый сигнал Ф2, на все нечетные каскады поступают второй и четвертый тактовые управляющие сигналы Ф1,о и Ф3,о соответственно, а на все четные каскады поступают третий и пятый тактовые управляющие сигналы Ф1,е и Ф3,е соответственно. Все каскады соединены с общим источником питания VCC, общим заземлением VSS и общими псевдозаземлениями VSSx и VSS1. Шестой или тактовый сигнал сдвига SDIN поступает на первый каскад схемы драйвера селекции 14. Таким образом, входная шина 9 с переключающего устройства или логического блока управления в схеме управления обеспечивает передачу сигналов: Ф1,о, Ф1,е, Ф2, Ф3,о, Ф3,е, VCC, VSS, VSSx и VSS1. Следовательно, потребуется только 10 проводников для обеспечения управления 240 схемами драйвера селекции строк, как будет пояснено далее.

На фиг. 3 представлены формы тактовых управляющих сигналов. Период тактового сигнала Ф2, т.е. интервал времени от начала одного импульса сигнала Ф2 до начала следующего импульса этого же сигнала, в данном примере равен интервалу времени сканирования строк в телевизионной системе, соответствующей стандартам Национального комитета по телевизионным системам (США), равному примерно 63 мкс. Другие тактовые сигналы, а именно: Ф1,о, Ф3,о, Ф1,е и Ф3,е имеют период в два раза больший, чем период сигнала Ф2. Выход каждого каскада, т. е. ряд 1, ряд 2, ряд 3,... ряд 240 соединен с рядом линии управления дисплейными элементами изображения, как показано на фиг. 1.

Видеоинформация поступает в систему, показанную на фиг. 1, по одной строке в каждый данный момент времени. Специалисту в данной области техники должно быть ясно, что низкая подвижность тонкопленочных резисторов, показанных на фиг. 1, может привести к недостаточности времени для осуществления селекции строки за один период строчной развертки, в данном примере 63 мкс. Поэтому для достижения более продолжительного времени селекции строки для обеспечения заряда или разряда конденсаторов 12 элементов изображения соответствующая последующая строка реально возбуждается раньше, чем снято возбуждение с предыдущей строки. Однако обеспечивается получение лишь одной строки информации за каждый период, поскольку лишь одна строка элементов изображения синхронизируется в каждый строчный период. Такой режим работы определяется как "преселекция строк". Преимущество данной новой схемы драйвера селекции строк, описываемой здесь, состоит в уменьшении числа внешних проводников. В данном примере число проводников уменьшено с 240 до 10. Такое уменьшение числа проводников в свою очередь существенно упрощает сборку и компоновку жидкокристаллического дисплея за счет значительного уменьшения числа внешних проводников. Хотя новая схема требует использования семи транзисторов на каскад, транзисторы имеют весьма малые размеры и просты в изготовлении на стеклянной подложке. В результате данная новая схема драйвера селекции строк снижает стоимость изготовления вследствие значительного сокращения числа соединений с проводниками на стеклянной подложке.

Как показано на фиг. 2 и на временной диаграмме на фиг. 3, в начале работы по линиям подачи тактовых сигналов Ф1,о и Ф1,е в момент времени t0 подаются импульсы инициализации, которые отпирают транзистор 16 во всех каскадах, при этом все каскады заряжаются в точках a1, a2, ... a240 до уровня напряжения, примерно равного VCC - Vt (логическая "1"), где Vt - пороговое напряжение транзистора 16. В этом состоянии напряжение в точках от a1 до a240 всех каскадов обуславливает переход транзисторов 18 всех каскадов в проводящее состояние, в результате все сканируемые строки от строки 1 до строки 240 разряжаются до уровня общего заземления VSS (логический "0"). Следует заметить, что тактовый сигнал Ф1,о, возникающий в момент времени t1 и продолжающийся до момента времени t2, не оказывает влияния на схему драйвера селекции строк 14, поскольку он приходит после импульса сигнала инициализации и все строки находятся на уровне "земли" (логический "0").

В момент времени t2 сигнал SDIN переходит в состояние высокого уровня, в результате транзистор 19 каскада 1 отпирается, разряжая точку a1 первого каскада до уровня VSS1, т.е. логического "0". Затем в момент времени t3 сигнал Ф2 переходит в состояние высокого уровня (логическая "1"), отпирая транзистор 20 во всех каскадах, в результате чего в точке b1 создается уровень логической "1".

Точки b2 ... b240 будут иметь уровень напряжения близкий к VSSx, так как в момент времени t3 только в точке a1 имеет место уровень логического "0", обусловленный импульсом SDIN, в то время как в точках a2 ... a240 сохраняется уровень логической "1". Это вызывает отпирание транзисторов 20 и 22 в каскадах с 2 до 240, а поскольку транзистор 22 выполнен намного большим, чем транзистор 20, предпочтительнее в отношении 10:1, точки b1 ... b240 будут переведены на уровень напряжения, близкий к VSSx. Различие в размерах транзисторов 20 и 22 является важным фактором, поскольку большие физические размеры транзистора 22 обеспечивают меньшее падение напряжения на транзисторе 22 в сравнении с транзистором 20 и поэтому гарантируют более стабильную работу схемных каскадов, как известно специалистам в данной области техники. После того, как импульс Ф2 возвратится на уровень логического "0", только точка b1 останется на уровне логической "1", поскольку в точке a1 логический "0", который приводит к запиранию транзисторов 22 и 18 в каскаде 1, но в любых других каскадах.

В момент времени t4 сигнал Ф3,о возрастает до уровня VCC, вызывающего заряд точки c1 до уровня логической "1", поскольку логическая "1" в точке b1 отпирает транзистор 24 только в первом каскаде. Как только сигнал Ф3 перейдет на уровень логической "1", транзистор 26 только в каскаде 1 перейдет в открытое состояние, заряжая строку 1 до уровня логической "1". В течение периода времени, когда строка 1 находится на уровне логической "1", все транзисторы 10 элементов изображения в строке 1 (фиг. 1) находятся в открытом состоянии.

Спустя интервал времени 63 мкс с момента времени t1, в момент времени t5, линии подачи сигнала Ф1,е переходят в состояние высокого уровня, что приводит к отпиранию транзисторов 16 во всех четных каскадах и к заряду точек a2, a4, a6,... a240 до уровня логической "1". В это время строка 1 находится в состоянии логической "1", отпирающем транзистор 19 в каскаде 2, так что точка a2 возвращается на уровень логического "0" вскоре после того, как сигнал Ф1, е возвращается в состояние высокого уровня в момент времени t6, отпирая транзисторы 20 во всех каскадах и переводя при этом точки b1 и b2 в состояние логической "1", в то время как в точках b3 ... b240 будет напряжение, близкое к VSSx. В этот момент точки a1 и a2 имеют логический "0", а точки a3 . . . a240 - логическую "1", так что внутренние точки b1 и b2 сохраняют состояние логической "1" после возвращения сигнала Ф2 на уровень логического "0". В момент времени t7 сигнал Ф3,е переходит на уровень VCC и точка c2 при этом заряжается до уровня логической "1", так как точка b2, сохраняя состояние логической "1", отпирает транзистор 24 каскада 2. И в свою очередь точка c2 обуславливает отпирание транзистора 26 каскада 2 и заряд строки 2 до уровня логической "1", тем самым вызывая отпирание всех транзисторов 10 элементов изображения строки 2.

В момент времени t9, спустя 126 мкс после момента времени t1 линия подачи сигнала Ф1,о переходит в состояние высокого уровня, тем самым отпирая транзистор 16 во всех нечетных каскадах, кроме каскада 3, и вызывая заряд всех точек с нечетными номерами a1 ... a239 до уровня логической "1", кроме точки a3. Точка a3 будет находиться на промежуточном уровне напряжения между VCC и VSS. Это объясняется тем, что в момент времени t9 транзисторы 16 и 19 переведены в открытое состояние сигналом Ф1,о и сигналом строки 2. Точка a3 возвратится на уровень VSS1 вскоре после того, как сигнал Ф1,о возвратится на уровень логического "0". Как только точка a1 окажется на уровне логической "1", транзистор 18 каскада 1 откроется, тем самым обуславливая разряд строки 1 до уровня логического "0", следовательно, строка 1 в этот момент деселектирована.

Управляющие и тактовые сигналы на протяжении оставшегося периода времени кадра будут обеспечивать селектирование и деселектирование сканируемых строк с 3 по 240, последовательно, точно так, как описано выше.

Следует отметить, что, как известно специалистам в данной области техники, при нормальной работе импульсы инициализации между моментами t0 и t1 не требуются, так как первый кадр отображаемой информации игнорируется. Это объясняется тем, что первый кадр отображаемой информации проходится очень быстро и не оказывает отрицательного влияния на выходное изображение.

Предпочтительным является то, что питающая мощность VCC, в связи с вышеописанным и с уровнями напряжений линий псевдозаземления VSS1 и VSSx, а также уровень напряжения заземления VSS должны регулироваться в соответствии со схемой формирования сигналов данных. Предпочтительно, чтобы все напряжения линии заземления были отделены одно от другого для снижения шумов, вводимых схемой. Например, если используется схема инверсии столбцов, то следует выбрать VCC равным от 15 до 25 В, а уровни напряжения заземления тогда будут от -10 до -0 В.

Специалистам в данной области техники должно быть ясно, что длительность импульсов всех вышеупомянутых управляющих и тактовых сигналов определяется в соответствии с временным режимом работы. Размеры тонкопленочных транзисторов должны оптимизироваться в соответствии с требуемыми характеристиками.

Работа схемы драйвера селекции строк, выполненной согласно изобретению, была описана выше для интервала строчного сканирования 63 мкс в дисплее с 380 х 240 элементами изображения, сопряженном с телевизионной системой, соответствующей стандарту НТСЦ. Следует иметь в виду, что это является лишь одним из возможных примеров осуществления изобретения и возможны другие варианты его осуществления и другие временные схемы, входящие в объем настоящего изобретения. Например, жидкокристаллические дисплеи иные, чем для ТВ систем, или дисплея с более высоким разрешением также могут быть выполнены в соответствии с изобретением.

При условии, что все основные синхронизирующие сигналы и управляющие сигналы уровней напряжения формируются интегральными схемами, внешними по отношению к стеклянной подложке, данная схема обеспечивает удобство и гибкость оптимизации системы отображения изображений. Кроме того, ввиду простоты эксплуатации этой схемы обеспечивается высокий уровень выхода годных изделий в процессе производства.

Таким образом, схема, показанная на фиг. 1 и 2, предназначена для использования с жидкокристаллическими дисплеями, содержащими первое множество столбцов элементов изображения и второе множество строк элементов изображения на подложке. Схема содержит множество схем драйвера селекции строк 14, включающего каскады с 1 по 240, что соответствует числу строк элементов изображения. Они электрически возбуждают строки элементов изображения. Схемы драйвера селекции строк размещены на подложке жидкокристаллического дисплея, и каждая из них формирует выходной сигнал,подаваемый на соответствующую строку элементов изображения и на последующую схему драйвера селекции строк в качестве возбуждающего входного сигнала. Переключающие средства или логические средства управления в схеме управления 8, внешней по отношению к жидкокристаллическому дисплею, содержат проводники 9, электрически соединенные со схемами драйвера селекции строк 14 для обеспечения подачи первого тактового сигнала (Ф2) на все схемы драйвера селекции строк 14, второго тактового сигнала (Ф1, о) на все нечетные схемы драйвера селекции строк, третьего тактового сигнала (Ф1,е) на все четные схемы драйвера селекции строк, четвертого тактового сигнала (Ф3, о) на все нечетные схемы драйвера селекции строк, пятого тактового сигнала (Ф3,е) на все четные схемы драйвера селекции строк и шестого тактового сигнала (SDIN) только на первую схему драйвера селекции строк, при этом шесть тактовых сигналов обеспечивают формирование выходного сигнала с каждой схемы драйвера селекции строк так, чтобы осуществлялось последовательное возбуждение каждой строки элементов изображения. Очевидно, что число внешних проводников (с переключающих средств или логических средств) в схеме управления 8 меньше, чем число строк элементов изображения. С учетом линий заземления и псевдозаземления потребуется лишь 10 управляющих линий от средств переключения для обеспечения управления всеми 240 схемами драйвера селекции строк, как пояснено выше.

Каждая из схем драйвера селекции строк содержит множество тонкопленочных транзисторов, выполненных на стеклянной подложке и взаимосвязанных для обеспечения последовательного возбуждения каждой строки элементов изображения.

Как пояснено выше, первый каскад схем драйвера селекции строк возбуждает первую строку элементов изображения в течение первого предварительного определенного интервала времени. Второй соседний каскад схем драйвера селекции строк возбуждает последующую строку элементов изображения в течение второго предварительно определенного интервала времени до окончания первого предварительно определенного интервала времени, так что обеспечивается более продолжительное время селекции строки, в течение которого каждая строка заряжает или разряжают элементы изображения соответствующей строки элементов изображения.

Также очевидно, что выходной сигнал с каждой схемы драйвера селекции строк не только возбуждает соответствующую строку элементов изображения, но и действует как сигнал сдвига для последующей схемы драйвера селекции строк. Каждая схема драйвера селекции строк содержит первую группу взаимосвязанных транзисторов 16 и 18 для приема одного из тактовых сигналов (Ф1,о, Ф1,е) для формирования логического "0" на соответствующей строке элементов изображения и логической "1" в первой внутренней точке a1, a, ... a240. Вторая группа взаимосвязанных транзисторов 19, 20 и 22 получает сигнал сдвига, сигнал SDIN или сигнал строки от предыдущей схемы драйвера селекции строк и первый тактовый сигнал Ф2 и формирует логический "0" в выбранной первой внутренней точке a и логическую "1" в выбранной второй внутренней точке b. Третья группа взаимосвязанных транзисторов 24 и 26 соединена с первой и второй группами транзисторов для приема сигнала логической "1" во второй точке b1 и одного из тактовых сигналов (Ф3,о, Ф3,е) для формирования сигнала логической "1" только на строке элементов изображения, соответствующей схеме драйвера селекции строк, имеющей логический "0" в первой внутренней точке a1. Поскольку выходной сигнал каждой схемы драйвера селекции строк для соответствующей ей строки представляет собой логический "0" и этот сигнал также служит входным сигналом для последующего каскада, только каскад 1 имеет логический "0" в первой внутренней точке a1, когда в первый раз появляется сигнал сдвига SDIN.

Каждая последующая схема драйвера селекции строк работает аналогичным образом, при этом выходной сигнал предшествующего каскада является эквивалентным сигналом "сдвига", подобным входному сигналу SDIN для первого каскада. Все последующие каскады остаются в запертом состоянии, пока они не примут выходной сигнал предыдущего каскада, и в этот момент времени вновь повторяется вышеописанный цикл работы.

Предлагаемая схема обеспечивает возбуждение первой строки элементов изображения в течение первого предварительно определенного интервала времени, причем каждая последующая схема драйвера селекции строк возбуждает соответствующую строку элементов изображения в течение второго предварительно определенного интервала времени до окончания первого предварительно определенного интервала времени, так что обеспечивается более продолжительное время селекции строк, требуемое каждой строке на заряд и разряд элементов изображения, соответствующей строки элементов изображения. Как показано на временной диаграмме на фиг. 3, сигналы U2, VSSx и U3 тактируются так, что селекция последующей строки осуществляется, когда предшествующая строка еще находится в возбужденном состоянии. Таким образом, хотя интервал времени между импульсами Ф2 равен 63 мкс, период возбуждения строк имеет в два раза большую длительность, что видно из фиг. 3.

Схему драйвера селекции строк 14, показанную на фиг. 2, можно также рассматривать как M блоков возбуждения строк, размещенных на подложке, каждый из которых формирует выходной сигнал. Каждый выходной сигнал подается на соответствующую строку элементов изображения и на последующий блок возбуждения строк. Переключающее устройство или управляющий логический блок в блоке управления 8, внешнем по отношению к дисплею, обеспечивает подачу инициализирующего тактового сигнала (SDIN) только на схему возбуждения первой строки. Они также обеспечивают подачу общих тактовых сигналов (Ф1,о, Ф1,е, Ф2, Ф3, о и Ф3, е) на все схемы возбуждения строк. Выходной сигнал каждого из блоков с 1-го по (M-1)-й служит инициализирующим тактовым сигналом для последующей схемы возбуждения, так что общее число соединений между переключающим устройством и дисплеем равно числу общих тактовых сигналов и инициализирующих тактовых сигналов для схемы возбуждения первой строки.

Таким образом, предлагается новая схема драйвера селекции строк для жидкокристаллического дисплея, использующего тонкопленочные МОП-транзисторы, выполненные на стеклянной подложке собственно дисплея, позволяющая сократить число входных проводников как для подачи управляющих сигналов, так и для подачи сигналов напряжений, с некоторого определенного числа, например 240, до 10. Поэтому преимущество заявленной схемы драйвера состоит в уменьшении числа внешних проводников и в эффективном решении проблем сборки и компоновки жидкокристаллического дисплея с тонкопленочными транзисторами, обусловленных ограничениями на шаг соединительных проводников.

Кроме того, поскольку дисплейная система получает свою видеоинформацию по одной строке в каждый данный момент времени, а также вследствие низкой подвижности тонкопленочных транзисторов, время селекции строки, равное, например, 63 мкс, может оказаться недостаточным. Поэтому для достижения более продолжительного времени селекции строки, требуемого на заряд или разряд конденсатора элемента изображения, настоящее изобретение осуществляет селекцию двух строк в каждый данный момент времени, но синхронизирует только одну строку информации за строчный период. Такой режим работы определяется как преселекция строки.

Вышеописанный пример осуществления изобретения предназначен для использования с обычными тонкопленочными транзисторами, которые имеют весьма малый ток утечки в запертом состоянии (примерно 0,1 пА на каждый микрон ширины канала). Схема, показанная на фиг. 2, может быть усовершенствована для обеспечения больших допусков по току утечки путем видоизменения схемы, как показано на фиг. 5. Однако ввиду того, что спустя время t8 транзистор 24 каскада 1 должен быть заперт на остальную часть длительности кадра, в точке c1 вследствие утечки с транзистора 24 может накопиться достаточный заряд, который обусловит некоторую проводимость транзистора 26. Это может вызвать нежелательные эффекты, такие как шумы в выходном сигнале строки 1. Аналогичным образом нежелательные эффекты могут возникнуть и в выходных сигналах других строк ввиду накопления заряда в точках c1 ... c240.

Для улучшения контроля утечки во внутренних точках c1 ... c240 и исключения нежелательных эффектов, обусловленных накоплением заряда в точках c1 ... c240, схема, показанная на фиг. 2, может быть модифицирована путем замены VSSx на дополнительное отдельное напряжение псевдозаземления VSSy во всех четных каскадах, как показано на фиг. 5. Кроме того, временная диаграмма, показанная на фиг. 4, в связи с использованием дополнительного напряжения псевдозаземления VSSy обеспечивает попеременный перевод VSSx и VSSy в состояние высокого уровня на каждый импульс Ф2, который разряжает точки c1 ... c240 на каждый другой импульс Ф2, т.е. на каждый другой строчный период. Таким образом, в точках c не накапливается заряд, который обусловил бы проводящее состояние транзисторов 26.

Хотя изобретение было описано в связи с предпочтительным примером его осуществления и альтернативным примером, это не должно ограничивать объем изобретения такими конкретными его формами, а напротив, предусматривается включение подобных альтернатив, модификаций и эквивалентных решений в объем изобретения, определяемый пунктами формулы изобретения.

Схема для использования с дисплеем, имеющим первое число столбцов элементов изображения и второе число строек элементов изображения на подложке. Схема (каскады 1-240) содержит множество схем драйвера селекции строк соответственно числу строк элементов изображения, для электрического возбуждения строк элементов изображения. Схема драйвера селекции строк размещена на подложке жидкокристаллического дисплея и выход каждого из схем драйвера селекции строк электрически соединен с соответствующей строкой элементов изображения и с последующей схемой драйвера селекции строк в качестве возбуждающего входа. Переключающее устройство (8), внешнее по отношению к жидкокристаллическому дисплею, имеющее проводники (9), электрически соединенные со схемами драйвера селекции строк (каскады 1 - 240), обеспечивает электрическое переключение схем драйвера селекции строк (каскады 1-240), так что осуществляется последовательное возбуждение каждой из строк элементов изображения, что и является достигаемым техническим результатом. Описан также соответствующий способ селекции строк элементов изображения. 1 н. и 6 з.п. ф-лы, 5 ил.

| WO, патент, 9110225, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1998-10-27—Публикация

1993-11-26—Подача