Область техники, к которой относится изобретение

Настоящее изобретение относится к жидкокристаллическому устройству отображения, имеющему монолитный драйвер затвора, и к способу его возбуждения.

Уровень техники

Обычно жидкокристаллическое устройство отображения с активной матрицей содержит жидкокристаллическую панель, которая включает в себя две подложки с жидкокристаллическим слоем, размещенным между ними. На одной из двух подложек множество линий шины затвора (линий сигналов сканирования) и множество линий шины истока (линий видеосигналов) размещаются в матрице, и предусмотрено множество участков формирования пикселов, размещаемых в матрице, надлежащим образом соответствующих пересечениям между множеством линий шины затвора и множеством линий шины истока. Каждый участок формирования пикселов включает в себя, к примеру, тонкопленочный транзистор (TFT) в качестве переключающего элемента, имеющего контактный вывод затвора, соединенный с линией шины затвора, которая проходит через соответствующее пересечение, и контактный вывод истока, соединенный с линией шины истока, которая проходит через это пересечение, и пиксельную емкость для сохранения пиксельного значения. Дополнительно, другая из двух подложек содержит общий электрод, который является противоэлектродом, предусмотренным так, что он совместно используется посредством множества участков формирования пикселов. Жидкокристаллическое устройство отображения с активной матрицей также содержит драйвер затвора (схему возбуждения линии сигналов сканирования) для возбуждения множества линий шины затвора и драйвер истока (схему возбуждения линии видеосигналов) для возбуждения множества линий шины истока.

Хотя видеосигналы, указывающие пиксельные значения, передаются через линии шины истока, линии шины истока не могут передавать видеосигналы, указывающие пиксельные значения для нескольких линий, в одно время (одновременно). Следовательно, видеосигналы записываются последовательно по линиям в пиксельные емкости в участках формирования пикселов, размещаемых в матрице. Соответственно, драйвер затвора конфигурирован посредством сдвигового регистра, имеющего множество каскадов, так что множество линий шины затвора последовательно выбирается в течение заданного периода.

В этом жидкокристаллическом устройстве отображения, зачастую возникает ситуация, когда дисплей не сразу очищается, и изображение, к примеру послеизображение, остается, даже когда пользователь выключает питание. Это обусловлено тем, что путь для того, чтобы разряжать заряды, сохраненные в пиксельных емкостях, блокируется, когда питание устройства выключается, и остаточные заряды накапливаются на участках формирования пикселов. Дополнительно, включение питания устройства в то время, когда остаточные заряды накапливаются на участках формирования пикселов, может приводить к ухудшению визуального качества, к примеру, возникновению мерцаний вследствие замещенных примесей, являющихся результатом остаточных зарядов.

Далее, в качестве технологий, чтобы уменьшать накопление остаточных зарядов посредством выключения питания, предложены различные технологии, как описано ниже. Публикация нерассмотренной заявки на патент Японии № 2004-45785 раскрывает изобретение жидкокристаллического устройства отображения, дающего возможность разрядки остаточных зарядов на всех участках формирования пикселов посредством задания всех линий шины затвора в выбранное состояние (включенное состояние), когда питание выключается. Опубликованная международная заявка № WO 2007/007768 раскрывает изобретение жидкокристаллического устройства отображения, дающего возможность запирающему потенциалу (потенциалу сигнала, который должен подаваться на контактный вывод затвора переключающего элемента на участке формирования пикселов, когда переключающий элемент выключается) быстро достигать потенциала земли, когда питание выключается. Публикация нерассмотренной заявки на патент Японии № 2007-11346 раскрывает изобретение жидкокристаллического устройства отображения, выполненного с возможностью уменьшения длительности разрядки остаточных зарядов посредством увеличения запирающего потенциала так, что он превышает потенциал земли, когда питание выключается.

Документы уровня техники

Патентные документы

Патентный документ 1. Публикация нерассмотренной заявки на патент Японии № 2004-45785

Патентный документ 2. Опубликованная международная заявка № WO 2007/007768

Патентный документ 3. Публикация нерассмотренной заявки на патент Японии № 2007-11346

Раскрытие изобретения

Задачи, решаемые изобретением

В последние годы, в жидкокристаллическом устройстве отображения с использованием жидкокристаллической панели на a-Si TFT (жидкокристаллической панели с использованием аморфного кремния для полупроводникового слоя тонкопленочного транзистора), предоставление драйверов затвора монолитным способом становится все более распространенным. Обычно драйвер затвора зачастую монтируется в качестве кристалла IC (интегральной схемы) в периферийной области вокруг подложки, которая составляет жидкокристаллическую панель. Тем не менее, в последние годы предоставление драйвера затвора непосредственно на подложке постепенно становится популярным. Такой драйвер затвора называется, например, "монолитным драйвером затвора", и панель, имеющая монолитный драйвер затвора, называется, например, «монолитной панелью с драйвером затвора».

Тем не менее, для монолитной панели с драйвером затвора, невозможно использовать вышеописанные технологии, чтобы уменьшать накопление остаточных зарядов вследствие выключения питания. Это поясняется ниже.

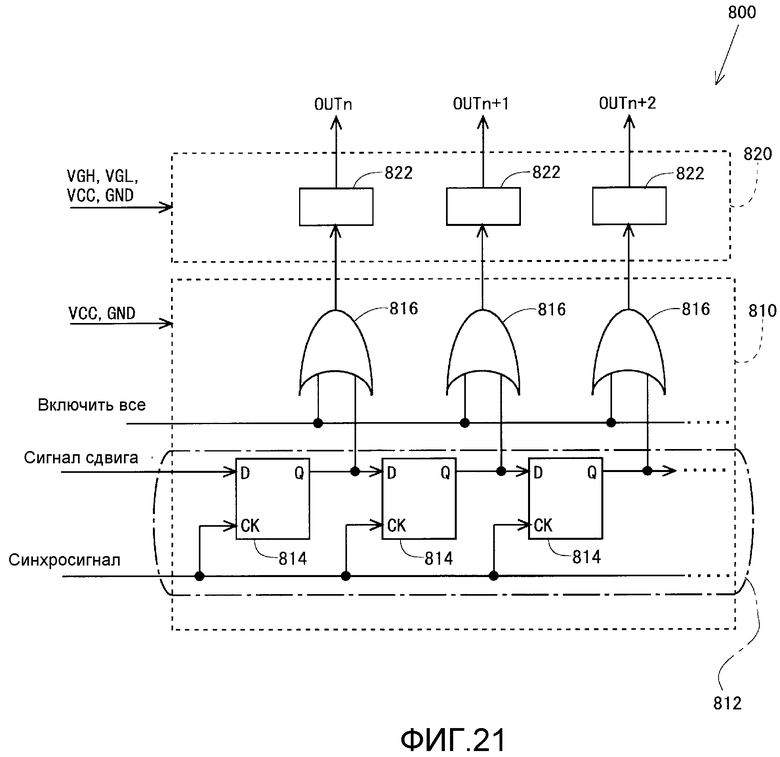

Что касается технологии, раскрытой в публикации нерассмотренной заявки на патент Японии № 2004-45785, драйвер затвора 800 в качестве IC-кристалла (далее называемого «IC драйвера затвора») обычно конфигурирован так, как проиллюстрировано на фиг. 21. IC драйвера затвора 800 конфигурирована посредством модуля 810 схемы низкого напряжения, составляющего логический модуль, и модуля 820 схемы высокого напряжения, включающего в себя схему 822 сдвига уровня, которая преобразует уровень потенциала сигнала, выводимого из логического модуля. Модуль 810 схемы низкого напряжения включает в себя сдвиговый регистр 812 и логическую схему 816 "OR". На входной контактный вывод логической схемы 816 "OR", вводится выходной сигнал из каждого каскада 814 сдвигового регистра 812 и сигнал «включить все» для управления тем, должны или нет все линии шины затвора быть в выбранном состоянии. Выходной сигнал из логической схемы 816 "OR" подвергается преобразованию потенциала посредством схемы 822 сдвига уровня. Затем, сигнал после преобразования потенциала посредством схемы 822 сдвига уровня подается в линию шины затвора в качестве сигнала сканирования. В вышеуказанной конфигурации, посредством задания логического уровня сигнала "включить все" равным высокому логическому уровню, когда питание выключается, все линии шины затвора переключаются в выбранное состояние, и остаточные заряды на всех участках формирования пикселов разряжаются.

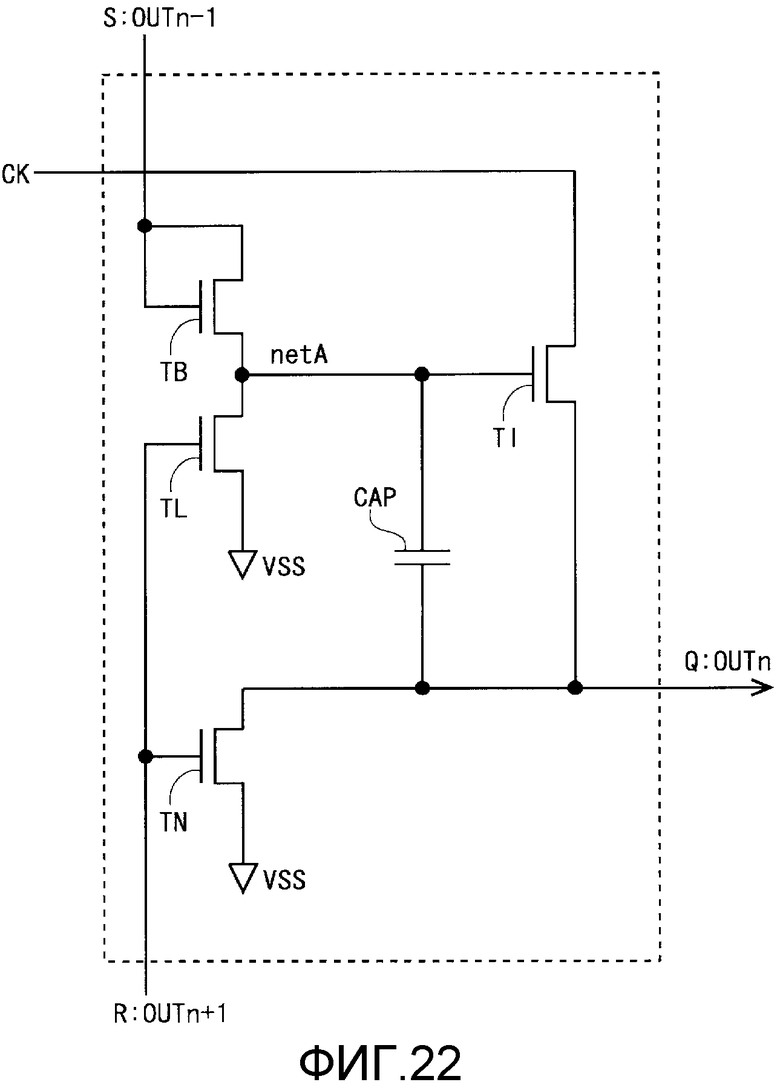

Тем не менее, в случае монолитного драйвера затвора, когда смещение постоянного тока подается на контактный вывод затвора тонкопленочного транзистора, пороговое напряжение этого тонкопленочного транзистора сдвигается. Следовательно, монолитный драйвер затвора конфигурирован триггерной схемой задания-сброса так, чтобы не подавать смещение постоянного тока на контактный вывод затвора тонкопленочного транзистора. В частности, конфигурация одного каскада схемы в сдвиговом регистре в монолитном драйвере затвора является, например, такой, как проиллюстрировано на фиг. 22. В этой конфигурации, когда выходной сигнал OUTn-1 (сигнал S задания, который описан ниже) из предыдущего каскада изменяется от низкого логического уровня к высокому логическому уровню, потенциал netA (область, в которой контактный вывод затвора тонкопленочного транзистора TI, контактный вывод истока тонкопленочного транзистора TB и контактный вывод стока тонкопленочного транзистора TL соединены друг с другом) увеличивается. После этого, когда синхросигнал CK изменяется от низкого логического уровня к высокому логическому уровню, потенциал netA дополнительно увеличивается вследствие эффекта использования компенсационной обратной связи конденсатора CAP. Вследствие этого, высокое напряжение прикладывается к контактному выводу затвора тонкопленочного транзистора TI. Как результат, на основе потенциала высокого логического уровня синхросигнала CK, потенциал выходного сигнала OUTn (сигнала Q состояния, который описан ниже) увеличивается до потенциала, при котором линии шины затвора переключаются в выбранное состояние. Здесь, схема, проиллюстрированная на фиг. 22, является схемой компенсационной обратной связи с использованием синхросигнала CK и конденсатора CAP, и предполагается, что потенциал выходного сигнала OUTn поддерживается на низком логическом уровне большую часть времени. Соответственно, схема, проиллюстрированная на фиг. 22, не содержит источник питания для формирования отпирающего потенциала (потенциала сигнала, который должен подаваться на контактный вывод затвора переключающего элемента на участке формирования пикселов, когда этот переключающий элемент переключается во включенное состояние). В частности, монолитный драйвер затвора не включает в себя средство (компонент), который переключает все линии шины затвора в выбранное состояние. Таким образом, что касается монолитной панели с драйвером затвора, невозможно использовать технологию, раскрытую в публикации нерассмотренной заявки на патент Японии № 2004-45785. Когда сдвиговый регистр работает на основе двухфазного синхросигнала, и потенциал выходного сигнала OUTn снижается до запирающего потенциала (извлекается к стороне запирающего потенциала) по мере необходимости, конфигурация одного каскада в сдвиговом регистре является, например, такой, как проиллюстрировано на фиг. 8.

Дополнительно, что касается технологии, раскрытой в опубликованной международной заявке номер WO 2007/007768, поскольку пороговое напряжение тонкопленочного транзистора в жидкокристаллической панели на a-Si TFT является высоким, остаточные заряды с участком формирования пикселов не могут разряжаться в достаточной степени, даже если запирающий потенциал достигает потенциала земли.

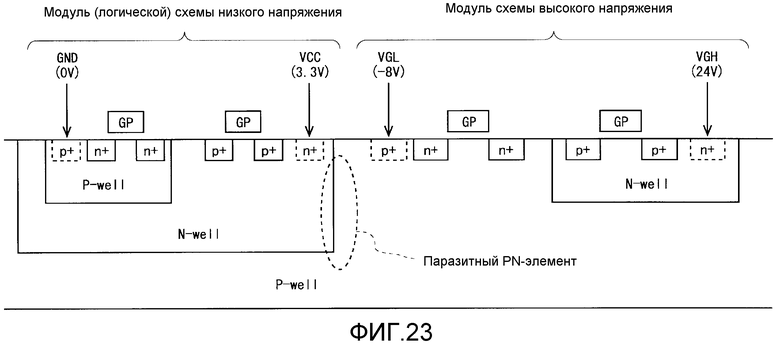

Кроме того, что касается технологии, раскрытой в публикации нерассмотренной заявки на патент Японии № 2007-11346, в IC драйвера затвора невозможно увеличивать запирающий потенциал выше потенциала земли вследствие следующих причин. Фиг. 23 является видом, иллюстрирующим соотношение потенциалов во внутренней схеме IC драйвера затвора. Значения потенциала, в частности, показанные на фиг. 23, являются просто примерами. Как можно видеть из фиг. 23, модуль (логической) схемы низкого напряжения работает между потенциалом GND земли и потенциалом VCC источника питания, а модуль схемы высокого напряжения работает между запирающим потенциалом VGL и отпирающим потенциалом VGH. Поскольку запирающий потенциал VGL ниже потенциала VCC источника питания и потенциала GND земли, в общем, только обратное напряжение возникает в паразитном PN-элементе. Следовательно, ток обычно не протекает через паразитный PN-элемент. Тем не менее, если запирающий потенциал VGL задается равным потенциалу (например, 5 В), превышающему потенциал VCC источника питания, прямое напряжение возникает в паразитном PN-элементе, и посредством этого ток протекает через него. Как результат, возникает анормальный режим работы IC драйвера затвора.

Тем временем, в IC драйвера затвора модуль вывода для сигнала сканирования конфигурирован как CMOS. В частности, IC драйвера затвора выполнена с возможностью выводить одно из отпирающего потенциала VGH и запирающего потенциала VGL из модуля вывода согласно напряжению, подаваемому в затвор CMOS. Следовательно, жидкокристаллическое устройство отображения с использованием IC драйвера затвора может поддерживать сигнал сканирования на низком логическом уровне. В отличие от этого, в монолитном драйвере затвора, один каскад в сдвиговом регистре имеет такую схемную конфигурацию, как проиллюстрировано на фиг. 8 и фиг. 22. Здесь, тонкопленочный транзистор TN переключается во включенное состояние только в течение заданного периода (периода, в течение которого одна линия шины затвора находится в выбранном состоянии) в одном периоде вертикального сканирования. Дополнительно, поскольку синхросигнал попеременно повторяется так, что он имеет высокий логический уровень и низкий логический уровень, тонкопленочные транзисторы TM и TD не поддерживаются во включенном состоянии непрерывным способом. В частности, потенциалы линий шины затвора не являются фиксированными на низком логическом уровне. Как описано выше, в монолитном драйвере затвора, хотя можно задавать запирающий потенциал VGL выше потенциала GND земли, остаточные заряды на участках формирования пикселов не разряжаются просто посредством этого.

Таким образом, задача настоящего изобретения состоит в создании жидкокристаллического устройства отображения, имеющего монолитный драйвер затвора, допускающий быстрое исключение остаточных зарядов на участках формирования пикселов, когда источник питания выключается, чтобы подавлять понижение визуального качества, когда источник питания включается.

Средство для решения задач

Первый аспект настоящего изобретения направлен на жидкокристаллическое устройство отображения, содержащее:

- множество линий видеосигналов, соответственно, для передачи множества видеосигналов, представляющих изображение, которое должно отображаться;

- множество линий сигналов сканирования, пересекающихся с множеством линий видеосигналов;

- множество участков формирования пикселов, размещаемых в матрице, надлежащим образом соответствующих пересечениям между множеством линий видеосигналов и множеством линий сигналов сканирования, причем каждый участок формирования пикселов включает в себя первый переключающий элемент и пиксельный электрод, при этом первый переключающий элемент имеет управляющий контактный вывод, соединенный с линией сигналов сканирования, проходящей через соответствующее пересечение, и первый проводящий контактный вывод, соединенный с линией видеосигналов, проходящей через соответствующее пересечение, причем пиксельный электрод соединен со вторым проводящим контактным выводом первого переключающего элемента;

- схему возбуждения линии сигналов сканирования, включающую в себя сдвиговый регистр, сконфигурированный посредством множества бистабильных схем, которые обеспечены так, что они имеют соответствие «один к одному» с множеством линий сигналов сканирования, причем сдвиговый регистр последовательно выводит импульс на основе синхросигнала, который циклически повторяет первый потенциал и второй потенциал, при этом схема возбуждения линии сигналов сканирования выполнена с возможностью избирательно возбуждать множество линий сигналов сканирования на основе импульса, выводимого из сдвигового регистра, и сформирована на подложке, идентичной подложке, на которой множество линий сигналов сканирования формируются;

- модуль определения состояния источника питания, выполненный с возможностью определять включенное/выключенное состояние источника питания, который предусмотрен внешним;

- модуль формирования опорного потенциала, выполненный с возможностью формировать опорный потенциал множества бистабильных схем; и

- линию опорного потенциала для передачи опорного потенциала, сформированного посредством модуля формирования опорного потенциала, во множество бистабильных схем, при этом:

- каждая бистабильная схема включает в себя модуль поддержания уровня потенциала для электрического соединения соответствующей линии сигналов сканирования с линией опорного потенциала, так что уровень потенциала соответствующей линии сигналов сканирования поддерживается на уровне опорного потенциала в течение периода времени, в который соответствующая линия сигналов сканирования находится в невыбранном состоянии, и

- когда отключенное состояние источника питания определяется посредством модуля определения состояния источника питания,

- модуль поддержания уровня потенциала, включенный в каждую бистабильную схему, электрически соединяет линию сигналов сканирования, соответствующую бистабильной схеме, с линией опорного потенциала, и

- модуль формирования опорного потенциала, увеличивающий уровень опорного потенциала до уровня, на котором первый переключающий элемент становится проводящим.

Согласно второму аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

- жидкокристаллическое устройство отображения дополнительно содержит модуль формирования синхросигнала, выполненный с возможностью формировать синхросигнал, при этом:

- модуль поддержания уровня потенциала, включенный в каждую бистабильную схему, включает в себя второй переключающий элемент, имеющий первый проводящий контактный вывод, соединенный с линией опорного потенциала, второй проводящий контактный вывод, соединенный с линией сигналов сканирования, соответствующей бистабильной схеме, и управляющий контактный вывод, в который подается синхросигнал, и

- когда отключенное состояние источника питания определяется посредством модуля определения состояния источника питания, модуль формирования синхросигнала задает синхросигнал равным первому потенциалу или второму потенциалу, так что второй переключающий элемент, включенный в каждую бистабильную схему, становится проводящим.

Согласно третьему аспекту настоящего изобретения, во втором аспекте настоящего изобретения,

- модуль поддержания уровня потенциала, включенный в каждую бистабильную схему, включает в себя множество вторых переключающих элементов,

- модуль формирования синхросигнала формирует множество синхросигналов, которые должны, соответственно, подаваться на управляющие контактные выводы множества вторых переключающих элементов, включенных в каждый модуль поддержания уровня потенциала, и

- когда отключенное состояние источника питания определяется посредством модуля определения состояния источника питания, модуль формирования синхросигнала задает множество синхросигналов равными первому потенциалу или второму потенциалу, соответственно, так что множество вторых переключающих элементов, включенных в каждый модуль поддержания уровня потенциала, становятся проводящими.

Согласно четвертому аспекту настоящего изобретения, в первом аспекте настоящего изобретения,

- модуль формирования опорного потенциала включает в себя схему сдвига уровня, выполненную с возможностью преобразовывать уровень потенциала заданного вводимого сигнала, тем самым подавая заданный потенциал высокого логического уровня или заданный потенциал низкого логического уровня в линию опорного потенциала, и

- схема сдвига уровня подает:

- потенциал низкого логического уровня в линию опорного потенциала в качестве опорного потенциала, когда отключенное состояние источника питания не определяется посредством модуля определения состояния источника питания, и

- потенциал высокого логического уровня в линию опорного потенциала в качестве опорного потенциала, когда отключенное состояние источника питания определяется посредством модуля определения состояния источника питания.

Пятый аспект настоящего изобретения направлен на способ возбуждения жидкокристаллического устройства отображения,

- при этом жидкокристаллическое устройство отображения содержит: множество линий видеосигналов, соответственно, для передачи множества видеосигналов, представляющих изображение, которое должно отображаться; множество линий сигналов сканирования, пересекающихся с множеством линий видеосигналов; множество участков формирования пикселов, размещаемых в матрице, надлежащим образом соответствующих пересечениям между множеством линий видеосигналов и множеством линий сигналов сканирования, причем каждый участок формирования пикселов включает в себя первый переключающий элемент и пиксельный электрод, при этом первый переключающий элемент имеет управляющий контактный вывод, соединенный с линией сигналов сканирования, проходящей через соответствующее пересечение, и первый проводящий контактный вывод, соединенный с линией видеосигналов, проходящей через соответствующее пересечение, причем пиксельный электрод соединен со вторым проводящим контактным выводом первого переключающего элемента; и схему возбуждения линии сигналов сканирования, сформированную на подложке, идентичной подложке, на которой множество линий сигналов сканирования формируются, и включающую в себя сдвиговый регистр, сконфигурированный посредством множества бистабильных схем, которые предусмотрены так, что они имеют соответствие «один к одному» с множеством линий сигналов сканирования, причем сдвиговый регистр последовательно выводит импульс на основе синхросигнала, который циклически повторяет первый потенциал и второй потенциал, при этом схема возбуждения линии сигналов сканирования выполнена с возможностью избирательно возбуждать множество линий сигналов сканирования на основе импульса, выводимого из сдвигового регистра, при этом способ содержит:

- этап определения состояния источника питания для определения включенного/выключенного состояния источника питания, который предусмотрен внешним; и

- этап формирования опорного потенциала для формирования опорного потенциала множества бистабильных схем, при этом:

- жидкокристаллическое устройство отображения дополнительно содержит линию опорного потенциала для передачи опорного потенциала, сформированного на этапе формирования опорного потенциала, во множество бистабильных схем, и

- когда отключенное состояние источника питания определяется на этапе определения состояния источника питания,

- линия сигналов сканирования, соответствующая каждой бистабильной схеме, и линия опорного потенциала электрически соединены, и

- уровень опорного потенциала увеличивается до уровня, на котором первый переключающий элемент становится проводящим на этапе формирования опорного потенциала.

Согласно шестому аспекту настоящего изобретения, в пятом аспекте настоящего изобретения,

- способ дополнительно содержит этап формирования синхросигнала для формирования синхросигнала, при этом:

- каждая бистабильная схема включает в себя второй переключающий элемент, имеющий первый проводящий контактный вывод, соединенный с линией опорного потенциала, второй проводящий контактный вывод, соединенный с линией сигналов сканирования, соответствующей бистабильной схеме, и управляющий контактный вывод, в который подается синхросигнал, и

- когда отключенное состояние источника питания определяется на этапе определения состояния источника питания, синхросигнал задается равным первому потенциалу или второму потенциалу, так что второй переключающий элемент, включенный в каждую бистабильную схему, становится проводящим на этапе формирования синхросигнала.

Согласно седьмому аспекту настоящего изобретения, в шестом аспекте настоящего изобретения,

- каждая бистабильная схема включает в себя множество вторых переключающих элементов,

- множество синхросигналов, которые должны, соответственно, подаваться на управляющие контактные выводы множества вторых переключающих элементов, включенных в каждую бистабильную схему, формируются на этапе формирования синхросигнала, и

- когда отключенное состояние источника питания определяется на этапе определения состояния источника питания, множество синхросигналов задаются равными первому потенциалу или второму потенциалу, так что множество вторых переключающих элементов, включенных в каждую бистабильную схему, становятся проводящими на этапе формирования синхросигнала.

Согласно восьмому аспекту настоящего изобретения, в пятом аспекте настоящего изобретения,

- способ дополнительно содержит этап преобразования уровня для преобразования уровня потенциала заданного вводимого сигнала, чтобы подавать заданный потенциал высокого логического уровня или заданный потенциал низкого логического уровня в линию опорного потенциала, и

- на этапе преобразования уровня,

- когда отключенное состояние источника питания не определяется на этапе определения состояния источника питания, уровень потенциала вводимого сигнала преобразуется в потенциал низкого логического уровня, и

- когда отключенное состояние источника питания определяется на этапе определения состояния источника питания, уровень потенциала вводимого сигнала преобразуется в потенциал высокого логического уровня.

Преимущества изобретения

Согласно первому аспекту настоящего изобретения, каждая из бистабильных схем, конфигурирующих сдвиговый регистр в схеме возбуждения линии сигналов сканирования, содержит модуль поддержания уровня потенциала, выполненный с возможностью поддерживать уровень потенциала линии сигналов сканирования, которая соответствует бистабильной схеме, равным опорному потенциалу в течение периода времени, в который линия сигналов сканирования должна быть в невыбранном состоянии. Затем, при определении отключенного состояния источника питания, модуль поддержания уровня потенциала электрически соединяет линию сигналов сканирования с линией опорного потенциала (для передачи опорного потенциала). Дополнительно, когда отключенное состояние источника питания определяется, уровень опорного потенциала увеличивается до уровня, на котором переключающий элемент, предусмотренный для каждого участка формирования пикселов, становится проводящим. Вследствие этого, каждая линия сигналов сканирования переключается в выбранное состояние, и переключающий элемент, предусмотренный для каждого участка формирования пикселов, становится проводящим. Следовательно, когда источник питания выключается, остаточные заряды на участках формирования пикселов быстро разряжаются. Как результат, можно подавлять понижение визуального качества вследствие остаточных зарядов на участках формирования пикселов, когда источник питания затем включается.

Согласно второму аспекту настоящего изобретения, модуль поддержания уровня потенциала используется в качестве компонента для переключения каждой линии сигналов сканирования в выбранное состояние, когда отключенное состояние источника питания определяется, и этот модуль поддержания уровня потенциала реализуется посредством переключающего элемента, который обычно предусмотрен для того, чтобы поддерживать потенциал линии сигналов сканирования на уровне опорного потенциала. Следовательно, можно относительно легко реализовывать жидкокристаллическое устройство отображения, обеспечивающее преимущество, идентичное преимуществу согласно первому аспекту настоящего изобретения.

Согласно третьему аспекту настоящего изобретения, в жидкокристаллическом устройстве отображения, содержащем схему возбуждения линии сигналов сканирования, имеющую сдвиговый регистр, который работает на основе множества синхросигналов, остаточные заряды на участках формирования пикселов быстро разряжаются, когда источник питания выключается, и понижение визуального качества, когда источник питания затем включается, подавляется.

Согласно четвертому аспекту настоящего изобретения, потенциал выходного сигнала из схемы сдвига уровня подается в качестве опорного потенциала через линию опорного потенциала в каждую из бистабильных схем, конфигурирующих сдвиговый регистр. Следовательно, можно легко задавать уровень опорного потенциала, подаваемого в бистабильную схему, переменным и переключать линию сигналов сканирования в выбранное состояние посредством увеличения уровня опорного потенциала, когда линия сигналов сканирования электрически соединена с линией опорного потенциала посредством модуля поддержания уровня потенциала. Тем временем, в жидкокристаллическом устройстве отображения с использованием монолитного драйвера затвора (схемы возбуждения линии сигналов сканирования, сформированной на подложке, идентичной подложке, на которой формируются линии сигналов сканирования), схема сдвига уровня обычно обеспечена вне панели. Следовательно, не обязательно увеличивать число схемных компонентов и т.п., даже если выходной сигнал из схемы сдвига уровня используется для опорного потенциала, и реализовывать жидкокристаллическое устройство отображения, допускающее быстрое исключение остаточных зарядов на участках формирования пикселов, когда источник питания выключается, при небольших затратах.

Краткое описание чертежей

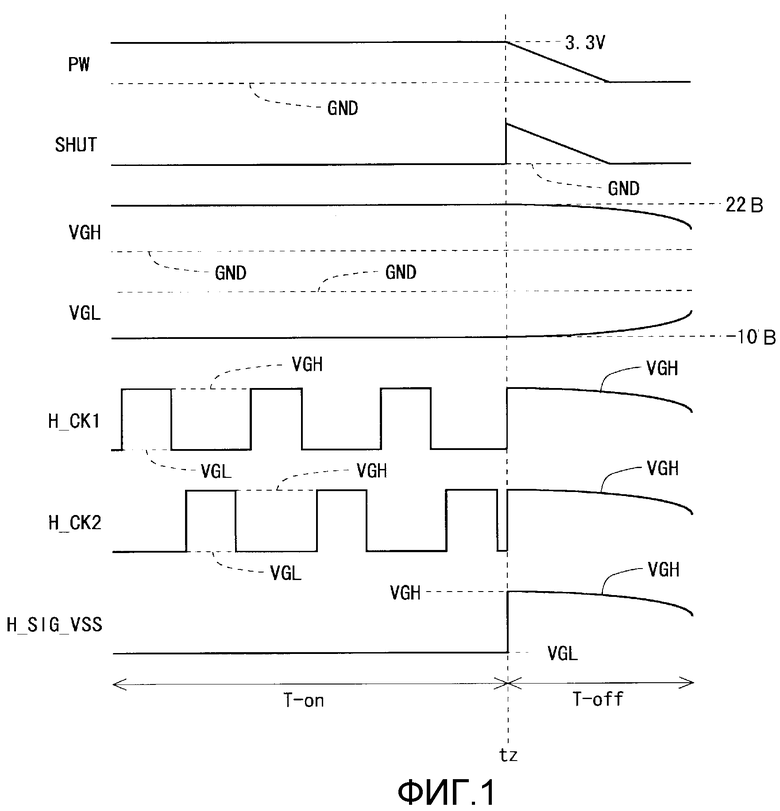

Фиг. 1 является схемой форм сигналов для иллюстрации работы, когда источник питания выключен в жидкокристаллическом устройстве отображения с активной матрицей согласно первому варианту осуществления настоящего изобретения.

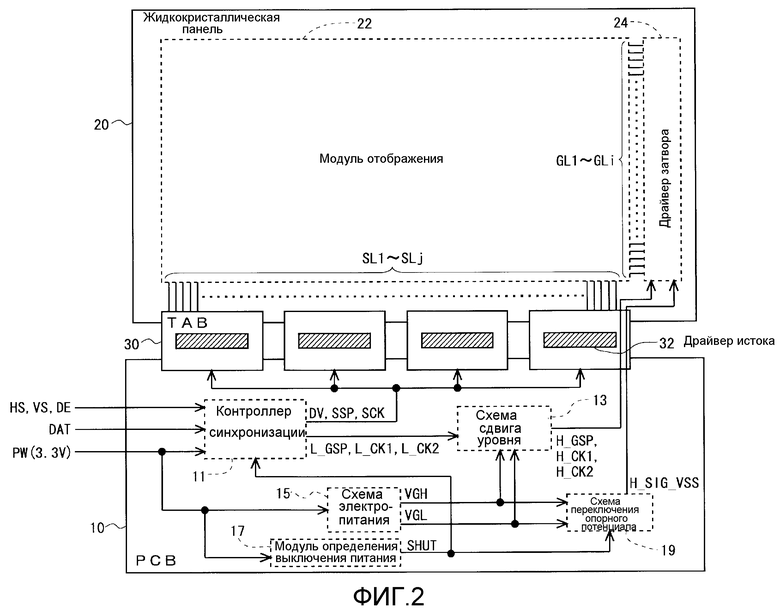

Фиг. 2 является блок-схемой, иллюстрирующей общую конфигурацию жидкокристаллического устройства отображения согласно первому варианту осуществления.

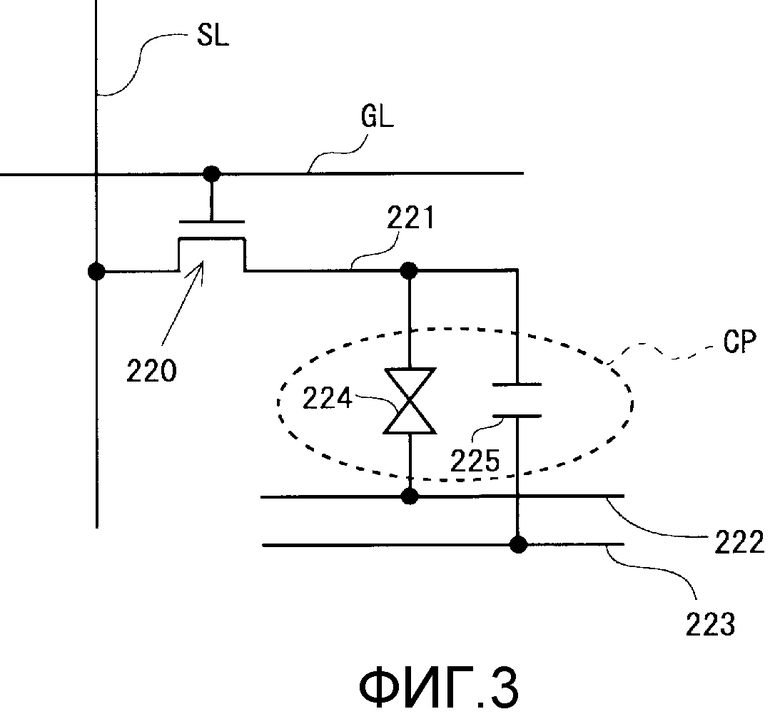

Фиг. 3 является принципиальной схемой, иллюстрирующей конфигурацию участка формирования пикселов согласно первому варианту осуществления.

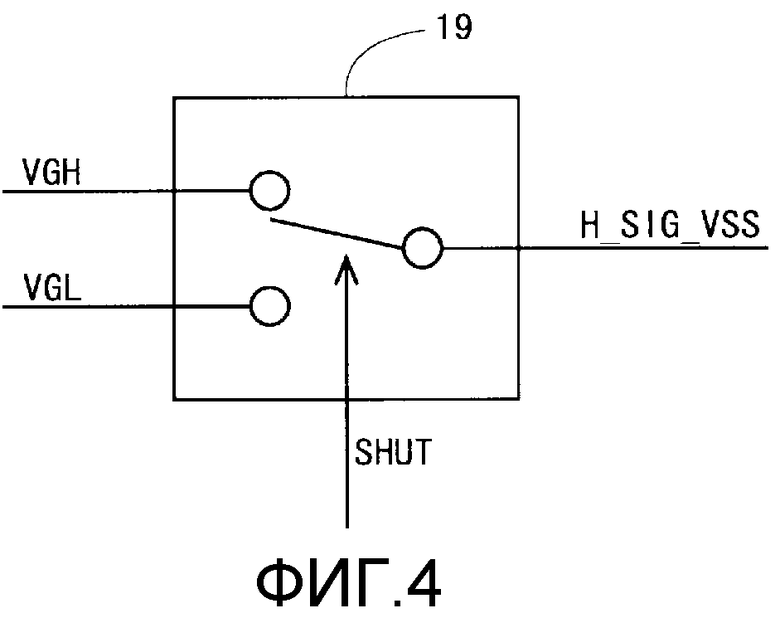

Фиг. 4 является схемой, иллюстрирующей конфигурацию схемы переключения опорного потенциала согласно первому варианту осуществления.

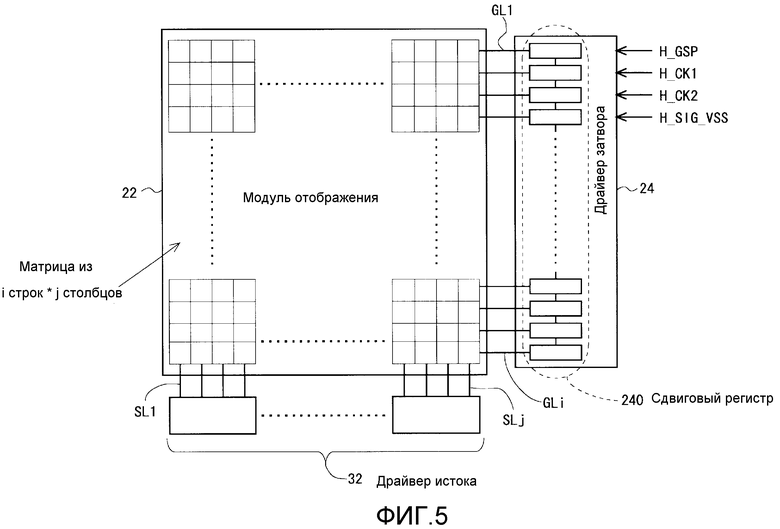

Фиг. 5 является блок-схемой для иллюстрации конфигурации драйвера затвора согласно первому варианту осуществления.

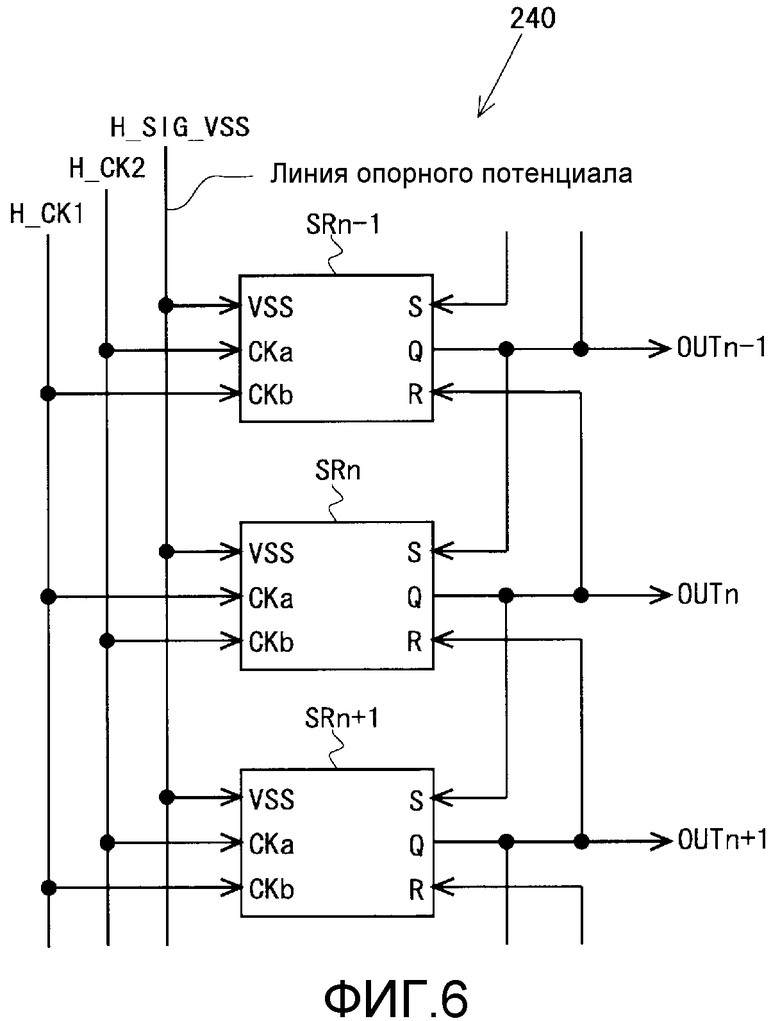

Фиг. 6 является блок-схемой, иллюстрирующей конфигурацию сдвигового регистра в драйвере затвора согласно первому варианту осуществления.

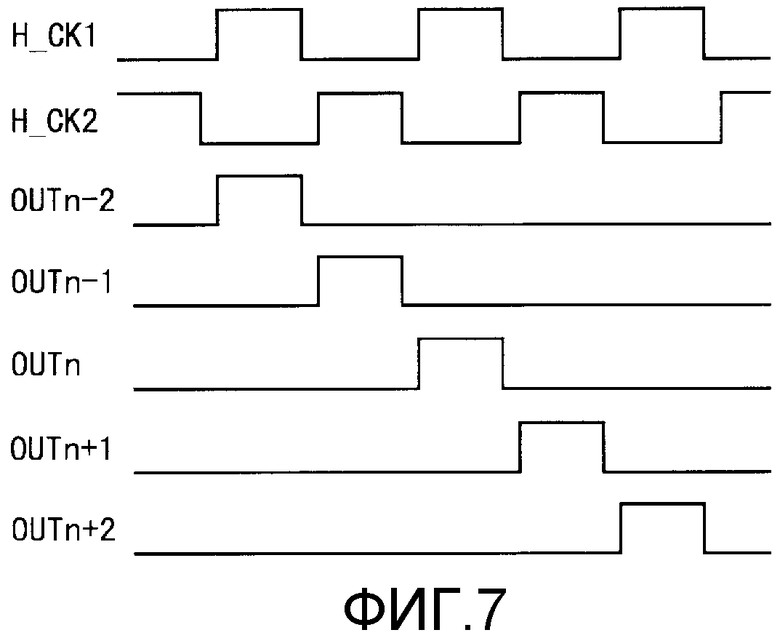

Фиг. 7 является схемой форм сигналов для иллюстрации работы драйвера затвора согласно первому варианту осуществления.

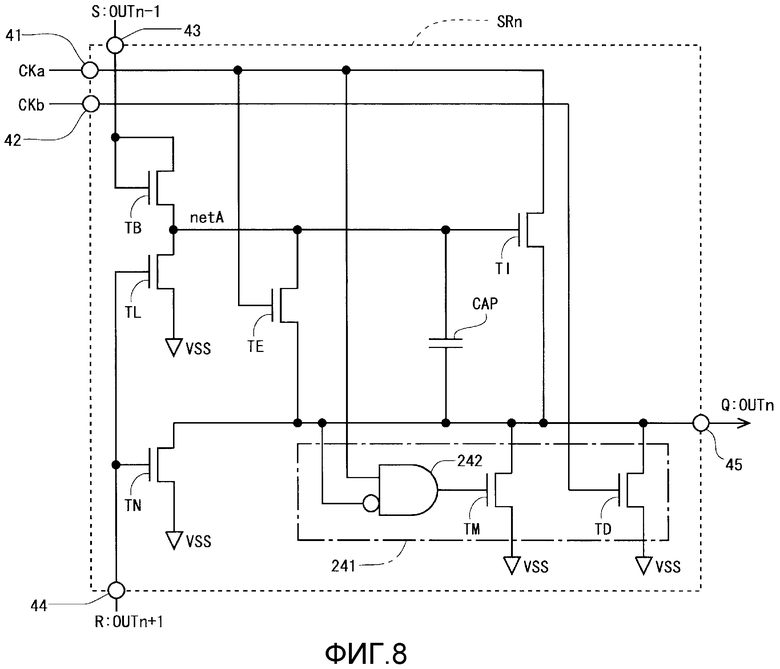

Фиг. 8 является принципиальной схемой, иллюстрирующей конфигурацию бистабильной схемы, включенной в сдвиговый регистр согласно первому варианту осуществления.

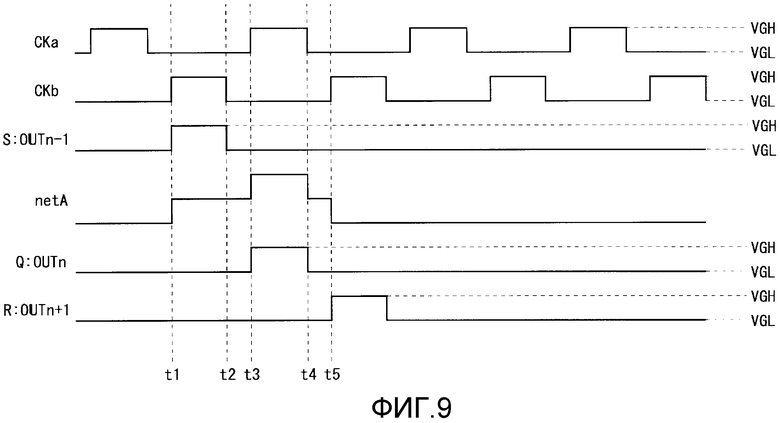

Фиг. 9 является схемой форм сигналов для иллюстрации работы бистабильной схемы согласно первому варианту осуществления.

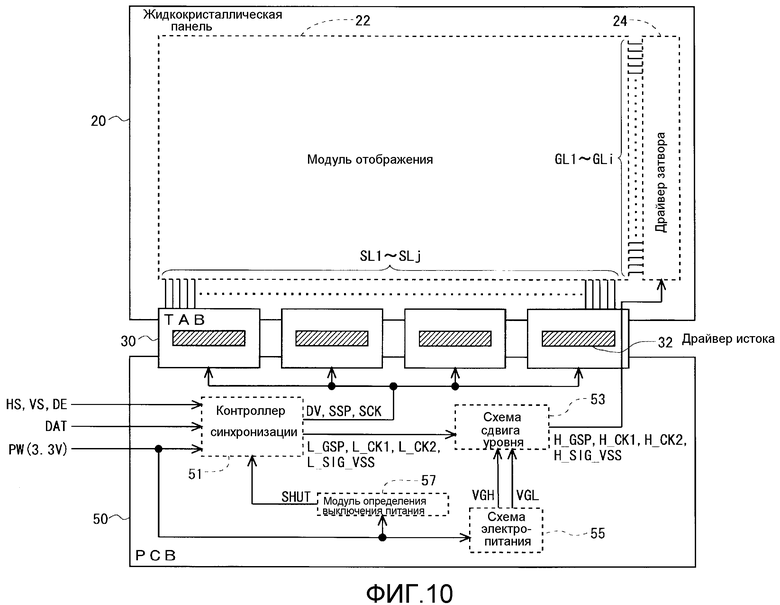

Фиг. 10 является блок-схемой, иллюстрирующей общую конфигурацию жидкокристаллического устройства отображения согласно второму варианту осуществления настоящего изобретения.

Фиг. 11 является схемой для иллюстрации преимуществ согласно второму варианту осуществления.

Фиг. 12 является схемой для иллюстрации преимуществ согласно второму варианту осуществления.

Фиг. 13 является схемой для иллюстрации модифицированных примеров второго варианта осуществления.

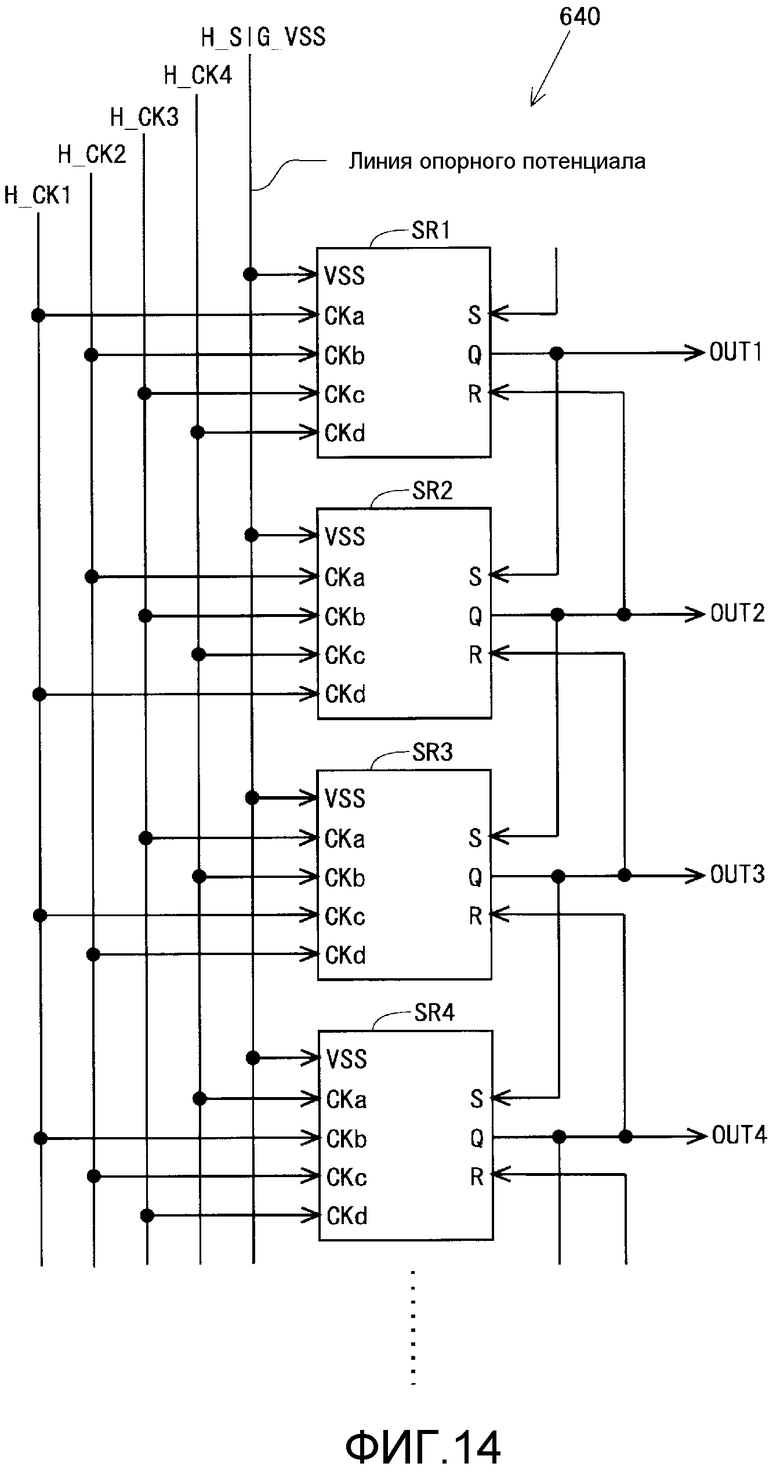

Фиг. 14 является блок-схемой, иллюстрирующей пример конфигурации сдвигового регистра, работающего на основе четырехфазных синхросигналов.

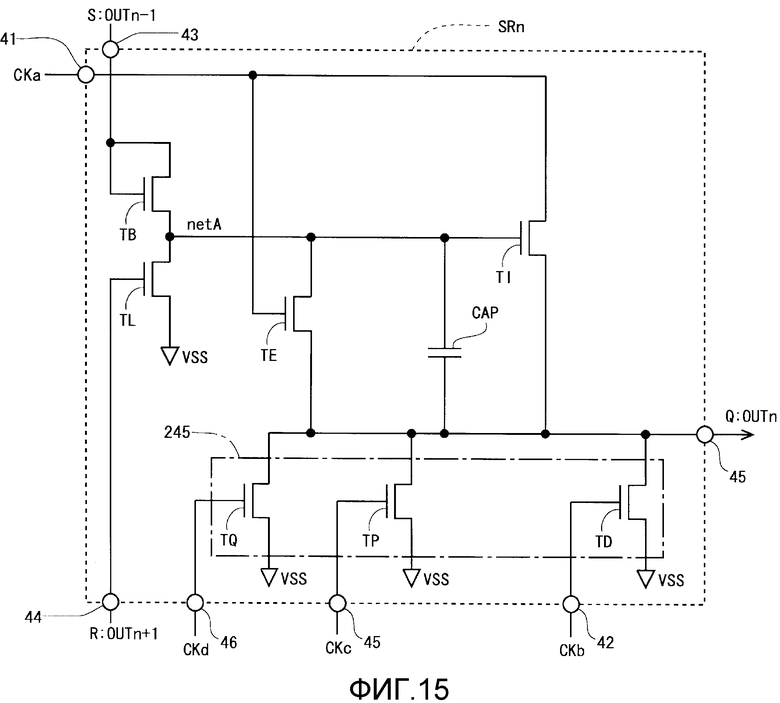

Фиг. 15 является принципиальной схемой, иллюстрирующей конфигурацию бистабильной схемы, включенной в сдвиговый регистр, работающий на основе четырехфазных синхросигналов.

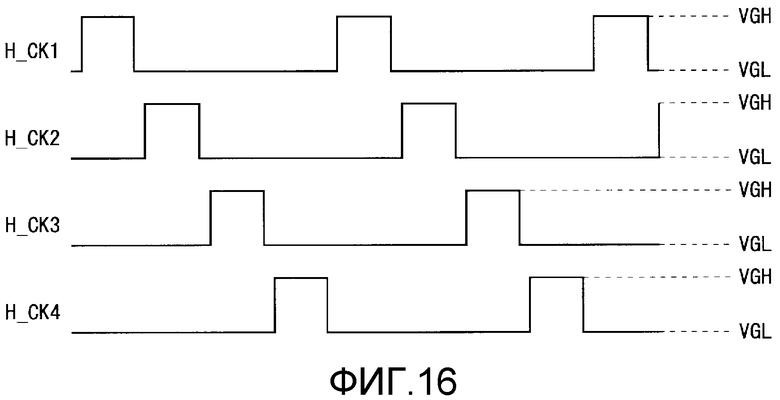

Фиг. 16 является схемой форм сигналов четырехфазных синхросигналов.

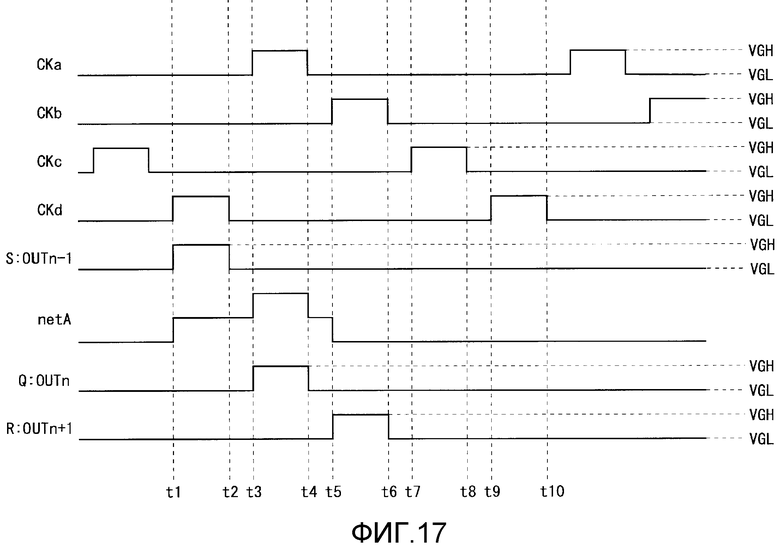

Фиг. 17 является схемой форм сигналов для иллюстрации работы бистабильной схемы, включенной в сдвиговый регистр, работающий на основе четырехфазных синхросигналов.

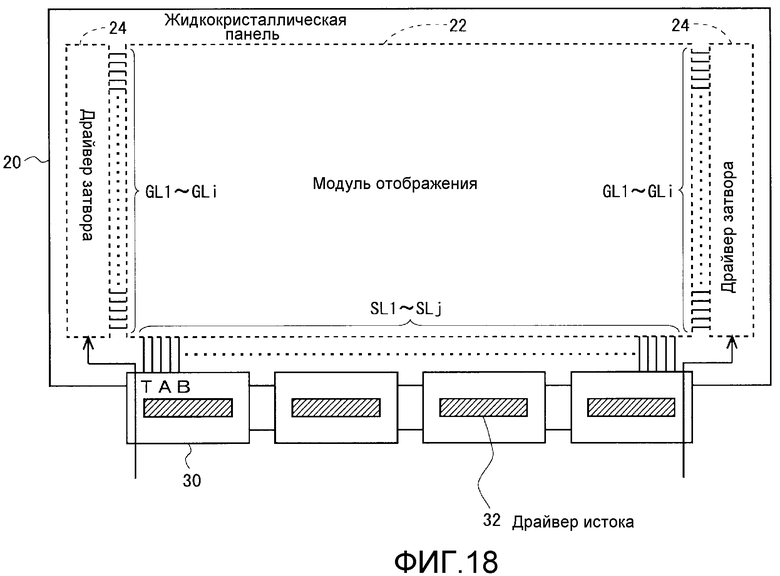

Фиг. 18 является блок-схемой для иллюстрации жидкокристаллического устройства отображения, имеющего драйверы затвора с обеих сторон модуля отображения.

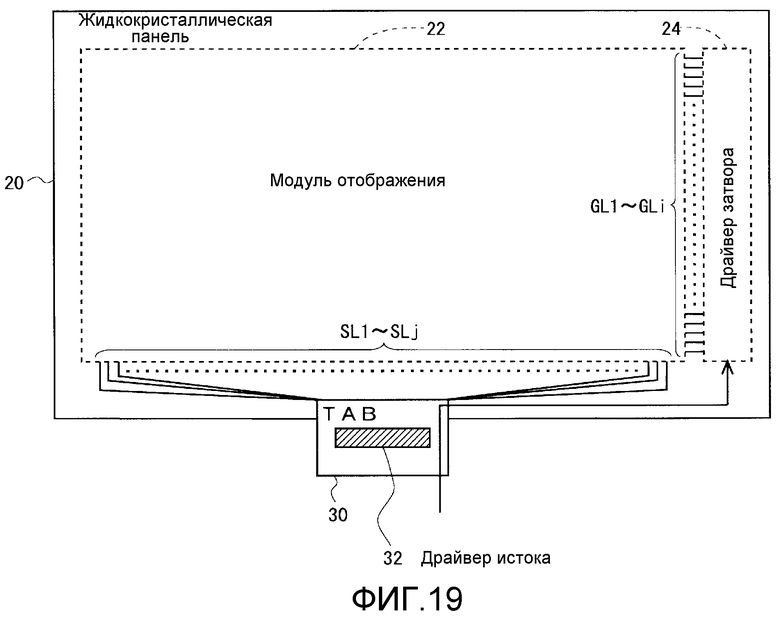

Фиг. 19 является блок-схемой для иллюстрации жидкокристаллического устройства отображения, в которой драйвер истока конфигурирован одним IC-кристалла.

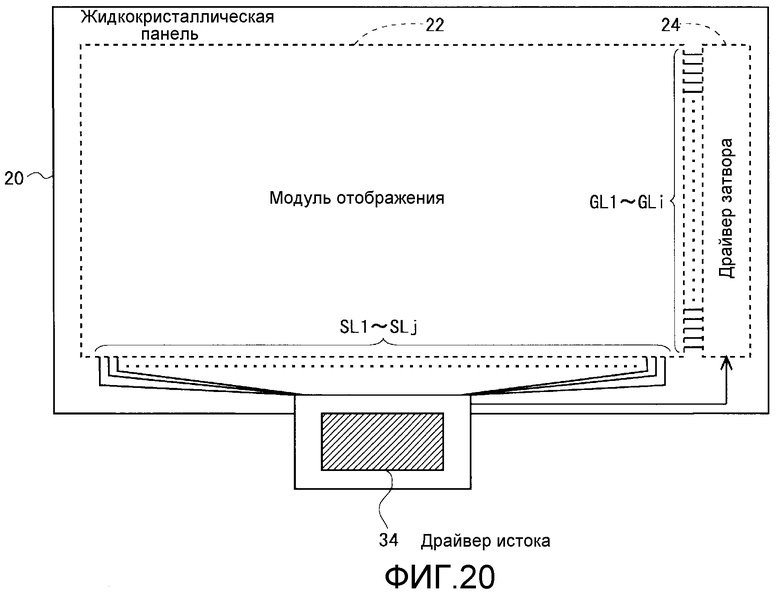

Фиг. 20 является блок-схемой для иллюстрации жидкокристаллического устройства отображения, имеющего однокристальный драйвер.

Фиг. 21 является блок-схемой, иллюстрирующей общую конфигурацию IC драйвера затвора.

Фиг. 22 является принципиальной схемой, иллюстрирующей конфигурацию одного каскада в сдвиговом регистре в монолитном драйвере затвора.

Фиг. 23 является видом для иллюстрации соотношения потенциалов во внутренней схеме IC драйвера затвора.

Осуществление изобретения

Варианты осуществления согласно настоящему изобретению далее описаны со ссылкой на прилагаемые чертежи.

1. Первый вариант осуществления

1.1. Общая конфигурация и работа

Фиг. 2 является блок-схемой, иллюстрирующей общую конфигурацию жидкокристаллического устройства отображения с активной матрицей согласно первому варианту осуществления настоящего изобретения. Как показано на фиг. 2, это жидкокристаллическое устройство отображения конфигурировано жидкокристаллической панелью 20, PCB (печатной платой) 10 и TAB (автоматизированной сборкой кристаллов на ленточном носителе) 30, соединенной с жидкокристаллической панелью 20 и с PCB 10.

Жидкокристаллическая панель 20 содержит модуль 22 отображения для отображения изображения. Модуль 22 отображения включает в себя множество (j) линий SL1-SLj шины истока (линий видеосигналов), множество (i) линий GL1-GLi шины затвора (линий сигналов сканирования) и множество (i * j) участков формирования пикселов, предусмотренных, соответственно, согласно пересечениям между линиями SL1-SLj шины истока и линиями GL1-GLi шины затвора. Фиг. 3 является принципиальной схемой, иллюстрирующей конфигурацию участка формирования пикселов. Ссылаясь на фиг. 3, каждый участок формирования пикселов включает в себя тонкопленочный транзистор (TFT) 220, имеющий контактный вывод затвора (управляющий контактный вывод), соединенный с линией GL шины затвора, которая проходит через соответствующее пересечение, и контактный вывод истока (первый проводящий контактный вывод), соединенный с линией SL шины истока, которая проходит через соответствующее пересечение, пиксельный электрод 221, соединенный с контактным выводом стока (вторым проводящим контактным выводом) тонкопленочного транзистора 220, общий электрод 222 и электрод 223 вспомогательной емкости, которые предусмотрены так, что они совместно используются множеством участков формирования пикселов, емкость 224 жидкого кристалла, сформированную посредством пиксельного электрода 221 и общего электрода 222, и вспомогательную емкость 225, сформированную посредством пиксельного электрода 221 и электрода 223 вспомогательной емкости. Дополнительно, пиксельная емкость CP формируется посредством емкости 224 жидкого кристалла и вспомогательной емкости 225. Затем напряжение, указывающее пиксельное значение, сохраняется в пиксельной емкости CP на основе видеосигнала, который контактный вывод истока тонкопленочного транзистора 220 принимает из линии SL шины истока, когда контактный вывод затвора каждого тонкопленочного транзистора 220 принимает активный сигнал сканирования из линии GL шины затвора.

Как проиллюстрировано на фиг. 2, в жидкокристаллической панели 20, драйвер 24 затвора для возбуждения линий GL1-GLi шины затвора также формируется. В частности, драйвер 24 затвора формируется монолитно поверх стеклянной подложки, которая составляет жидкокристаллическую панель 20. TAB 30 содержит драйвер 32 истока, в форме IC-кристалла, для возбуждения линий SL1-SLj шины истока. На PCB 10 формируются контроллер 11 синхронизации, схема 13 сдвига уровня, схема 15 электропитания, модуль 17 определения выключения питания и схема 19 переключения опорного потенциала. В последующем описании, потенциал, рассматриваемый в качестве опорного, когда сдвиговый регистр, включенный в драйвер 24 затвора, работает, упоминается как "опорный потенциал" (следует отметить, что этот потенциал является переменным в этом варианте осуществления).

В жидкокристаллическое устройство отображения внешним образом подаются синхронизирующие сигналы, такие как сигнал HS горизонтальной синхронизации, сигнал VS вертикальной синхронизации и сигнал DE разрешения передачи данных, а также сигнал DAT изображения и напряжение PW питания. Напряжение PW питания подается в контроллер 11 синхронизации, схему 15 электропитания и модуль 17 определения выключения питания. В этом варианте осуществления, напряжение PW питания составляет 3,3 В.

Схема 15 электропитания формирует отпирающий потенциал VGH для переключения линии шины затвора в выбранное состояние и запирающий потенциал VGL для переключения линии шины затвора в невыбранное состояние на основе напряжения PW питания. Отпирающий потенциал VGH и запирающий потенциал VGL подаются в схему 13 сдвига уровня и схему 19 переключения опорного потенциала. Модуль 17 определения выключения питания выводит сигнал SHUT состояния источника питания, указывающий состояние источника напряжения PW питания (включенное/выключенное состояние источника питания). Сигнал SHUT состояния источника питания подается в контроллер 11 синхронизации и схему 19 переключения опорного потенциала. Схема 19 переключения опорного потенциала конфигурирована так, что избирательный переключатель, как проиллюстрировано на фиг. 4 реализуется с использованием, к примеру, транзистора. В частности, схема 19 переключения опорного потенциала выводит один из отпирающего потенциала VGH и запирающего потенциала VGL в качестве опорного потенциала H_SIG_VSS, согласно абсолютной величине напряжения сигнала SHUT состояния источника питания. Более конкретно, запирающий потенциал VGL выводится в качестве опорного потенциала H_SIG_VSS, когда сигнал SHUT состояния источника питания имеет низкий логический уровень, и отпирающий потенциал VGH выводится в качестве опорного потенциала H_SIG_VSS, если сигнал SHUT состояния источника питания имеет высокий логический уровень. Опорный потенциал H_SIG_VSS передается через линию опорного потенциала и подается в драйвер 24 затвора.

Контроллер 11 синхронизации принимает синхронизирующие сигналы, такие как сигнал HS горизонтальной синхронизации, сигнал VS вертикальной синхронизации и сигнал DE разрешения передачи данных, а также сигнал DAT изображения, напряжение PW питания и сигнал SHUT состояния источника питания, и формирует цифровой видеосигнал DV, сигнал SSP пускового импульса истока, синхросигнал SCK истока, сигнал L_GSP пускового импульса затвора, первый стробирующий синхросигнал L_CK1 и второй стробирующий синхросигнал L_CK2. Цифровой видеосигнал DV, сигнал SSP пускового импульса истока и синхросигнал SCK истока подаются в драйвер 32 истока, а сигнал L_GSP пускового импульса затвора, первый стробирующий синхросигнал L_CK1 и второй стробирующий синхросигнал L_CK2 подаются в схему 13 сдвига уровня. Здесь, касательно сигнала L_GSP пускового импульса затвора, первого стробирующего синхросигнала L_CK1 и второго стробирующего синхросигнала L_CK2, потенциал стороны высокого логического уровня является напряжением PW питания (3,3 В), а потенциал стороны низкого логического уровня является потенциалом GND земли (0 В).

Схема 13 сдвига уровня преобразует уровни потенциала сигнала L_GSP пускового импульса затвора, первого стробирующего синхросигнала L_CK1 и второго стробирующего синхросигнала L_CK2, которые выводятся из контроллера 11 синхронизации, с использованием отпирающего потенциала VGH и запирающего потенциала VGL, которые подаются из схемы 15 электропитания. Сигнал H_GSP пускового импульса затвора, первый стробирующий синхросигнал H_CK1 и второй стробирующий синхросигнал H_CK2 после преобразования уровня потенциала посредством схемы 13 сдвига уровня подаются в драйвер 24 затвора. При преобразовании уровня потенциала посредством схемы 13 сдвига уровня, потенциал первого стробирующего синхросигнала H_CK1 задается равным запирающему потенциалу VGL, когда первый стробирующий синхросигнал L_CK1 имеет низкий логический уровень, и потенциал первого стробирующего синхросигнала H_CK1 задается равным отпирающему потенциалу VGH, когда первый стробирующий синхросигнал L_CK1 имеет высокий логический уровень. Второй стробирующий синхросигнал L_CK2 и сигнал L_GSP пускового импульса затвора преобразуются таким же образом.

Драйвер 32 истока принимает цифровой видеосигнал DV, сигнал SSP пускового импульса истока и синхросигнал SCK истока, которые выводятся из контроллера 11 синхронизации, и применяет видеосигнал возбуждения к каждой из линий SL1-SLj шины истока.

Драйвер 24 затвора повторяет применение активного сигнала сканирования к каждой из линий GL1-GLi шины затвора при использовании одного периода вертикального сканирования в качестве одного цикла на основе сигнала H_GSP пускового импульса затвора, первого стробирующего синхросигнала H_CK1 и второго стробирующего синхросигнала H_CK2, которые выводятся из схемы 13 сдвига уровня, а также на основе опорного потенциала H_SIG_VSS, выводимого из схемы 19 переключения опорного потенциала. Драйвер 24 затвора подробнее описан ниже.

Посредством применения видеосигнала возбуждения к каждой из линий SL1-SLj шины истока и применения сигнала сканирования к каждой из линий GL1-GLi шины затвора вышеуказанным способом, изображение на основе сигнала DAT изображения, подаваемого внешним образом, отображается на модуле 22 отображения.

В этом варианте осуществления, модуль определения состояния источника питания реализуется посредством модуля 17 определения выключения питания, модуль формирования опорного потенциала реализуется посредством схемы 19 переключения опорного потенциала, и модуль формирования синхросигнала реализуется посредством контроллера 11 синхронизации и схемы 13 сдвига уровня.

1.2. Конфигурация и работа драйвера затвора

Далее описывается конфигурация и работа драйвера 24 затвора согласно этому варианту осуществления. Ссылаясь на фиг. 5, драйвер 24 затвора конфигурирован посредством сдвигового регистра 240, включающего в себя множество каскадов. Модуль 22 отображения содержит пиксельную матрицу из i строк * j столбцов, и каждый каскад сдвигового регистра 240 предусмотрен так, что он соответствует каждой линии пиксельной матрицы. Дополнительно, каждый каскад сдвигового регистра 240 является бистабильной схемой, которая находится в любом из двух состояний в каждый момент времени и которая выводит сигнал, указывающий это состояние (в дальнейшем называемый "сигналом состояния"). Здесь, сигнал состояния, выводимый из каждого каскада сдвигового регистра 240, подается в качестве сигнала сканирования в соответствующую линию шины затвора.

Фиг. 6 является блок-схемой, иллюстрирующей конфигурацию сдвигового регистра 240 в драйвере 24 затвора. Здесь, фиг. 6 показывает конфигурацию бистабильных схем SRn-1, SRn и SRn+1, соответственно, (n-1)-вого каскада, n-ного каскада и (n+1)-вого каскада сдвигового регистра 240. Каждая бистабильная схема содержит входные контактные выводы для приема опорного потенциала VSS, первого тактового сигнала CKa, второго тактового сигнала CKb, сигнала S задания и сигнала R сброса, соответственно, и выходной контактный вывод для вывода сигнала Q состояния. В этом варианте осуществления, опорный потенциал H_SIG_VSS, выводимый из схемы 19 переключения опорного потенциала, подается в качестве опорного потенциала VSS, один из первого стробирующего синхросигнала H_CK1 и второго стробирующего синхросигнала H_CK2, выводимых из схемы 13 сдвига уровня, подается в качестве первого тактового сигнала CKa, а другой из первого стробирующего синхросигнала H_CK1 и второго стробирующего синхросигнала H_CK2 подается в качестве второго тактового сигнала CKb. Дополнительно, сигнал Q состояния, выводимый из предыдущего каскада, подается в качестве сигнала S задания, и сигнал Q состояния, выводимый из последующей ступени, подается в качестве сигнала R сброса. В частности, фокусируясь на n-ном каскаде, сигнал OUTn-1 сканирования, подаваемый в (n-1)-вую линию шины затвора, подается в качестве сигнала S задания, и сигнал OUTn+1 сканирования, подаваемый в (n+1)-ю линию шины затвора, подается в качестве сигнала R сброса.

В вышеуказанной конфигурации, когда импульс сигнала H_GSP пускового импульса затвора в качестве сигнала S задания подается в первый каскад сдвигового регистра 240, на основе первого стробирующего синхросигнала H_CK1 и второго стробирующего синхросигнала H_CK2, имеющих рабочий цикл включения, заданный так, что он составляет 50 процентов (см. фиг. 7), импульс, включенный в сигнал H_GSP пускового импульса затвора (этот импульс включается в сигнал Q состояния, выводимый из каждого каскада), последовательно переносится из первого каскада в i-й каскад. Согласно переносу импульса, сигналы Q состояния, выводимые из соответствующих каскадов, последовательно задаются равными высокому логическому уровню. Затем, сигналы Q состояния, выводимые из каскадов, соответственно, подаются в качестве сигналов OUT1-OUTi сканирования в линии GL1-GLi шины затвора. Вследствие этого, как проиллюстрировано на фиг. 7, сигналы OUT1-OUTi сканирования, которые последовательно заданы равными высокому логическому уровню посредством заданного периода, подаются в линии GL1-GLi шины затвора в модуле 22 отображения.

1.3. Конфигурация и работа бистабильной схемы

Фиг. 8 является принципиальной схемой, иллюстрирующей конфигурацию бистабильной схемы, включенной в сдвиговый регистр 240 (конфигурацию n-ного каскада сдвигового регистра 240). Ссылаясь на фиг. 8, бистабильная схема SRn содержит семь тонкопленочных транзисторов TI, TB, TL, TN, TE, TM и TD, конденсатор CAP и логическую схему 242 "AND". На фиг. 8, входной контактный вывод для приема первого тактового сигнала CKa представляется посредством ссылки с номером 41, входной контактный вывод для приема второго тактового сигнала CKb представляется посредством ссылки с номером 42, входной контактный вывод для приема сигнала S задания представляется посредством ссылки с номером 43, входной контактный вывод для приема сигнала R сброса представляется посредством ссылки с номером 44, и выходной контактный вывод для вывода сигнала Q состояния представляется посредством ссылки с номером 45.

Контактный вывод истока тонкопленочного транзистора TB, контактный вывод стока тонкопленочного транзистора TL, контактный вывод затвора тонкопленочного транзистора TI, контактный вывод истока тонкопленочного транзистора TE и один контактный вывод конденсатора CAP соединены друг с другом. Следует отметить, что область (межсоединение), в которой эти контактные выводы соединены друг с другом, для удобства называется "netA".

Тонкопленочный транзистор TI конфигурирован так, что его контактный вывод затвора, контактный вывод стока и контактный вывод истока, соответственно, соединены с netA, входным контактным выводом 41 и выходным контактным выводом 45. Тонкопленочный транзистор TB конфигурирован так, что его контактный вывод затвора и контактный вывод стока соединены с входным контактным выводом 43 (в частности, в диодном включении), и его контактный вывод истока соединен с netA. Тонкопленочный транзистор TL конфигурирован так, что его контактный вывод затвора, контактный вывод стока и контактный вывод истока, соответственно, соединены с входным контактным выводом 44, netA и линией опорного потенциала. Тонкопленочный транзистор TN конфигурирован так, что его контактный вывод затвора, контактный вывод стока и контактный вывод истока, соответственно, соединены с входным контактным выводом 44, выходным контактным выводом 45 и линией опорного потенциала. Тонкопленочный транзистор TE конфигурирован так, что его контактный вывод затвора, контактный вывод стока и контактный вывод истока, соответственно, соединены с входным контактным выводом 41, выходным контактным выводом 45 и netA. Тонкопленочный транзистор TM конфигурирован так, что его контактный вывод затвора, контактный вывод стока и контактный вывод истока, соответственно, соединены с выходным контактным выводом логической схемы 242 "AND", выходным контактным выводом 45 и линией опорного потенциала. Тонкопленочный транзистор TD конфигурирован так, что его контактный вывод затвора, контактный вывод стока и контактный вывод истока, соответственно, соединены с входным контактным выводом 42, выходным контактным выводом 45 и линией опорного потенциала. Конденсатор CAP конфигурирован так, что его один контактный вывод соединен с netA, а другой контактный вывод соединен с выходным контактным выводом 45. Логическая схема 242 "AND" конфигурирована так, что сигнал, указывающий логическое "AND" между логическим значением сигнала логической инверсии сигнала Q состояния и логическим значением первого тактового сигнала CKa, подается на контактный вывод затвора тонкопленочного транзистора TM.

Далее описывается функция каждого компонента в бистабильной схеме. Тонкопленочный транзистор TS обеспечивает потенциал первого тактового сигнала CKA на выходной контактный вывод 45, когда потенциал netA имеет высокий логический уровень. Тонкопленочный транзистор TB задает потенциал netA равным высокому логическому уровню, когда сигнал S задания имеет высокий логический уровень. Тонкопленочный транзистор TL задает потенциал netA равным низкому логическому уровню, когда сигнал R сброса имеет высокий логический уровень. Тонкопленочный транзистор TN задает потенциал сигнала Q состояния (выходного контактного вывода 45) равным низкому логическому уровню, когда сигнал R сброса имеет высокий логический уровень. Тонкопленочный транзистор TE задает потенциал netA и потенциал сигнала Q состояния равными, когда тонкопленочный транзистор TE находится во включенном состоянии. Конденсатор CAP выступает в качестве емкости для достижения эффекта использования компенсационной обратной связи с увеличением потенциала netA по мере того, как потенциал сигнала Q состояния увеличивается.

Логическая схема 242 "AND" подает сигнал, указывающий логическое "AND" между логическим значением сигнала логической инверсии сигнала Q состояния и логическим значением первого тактового сигнала CKa, на контактный вывод затвора тонкопленочного транзистора TM. В частности, когда сигнал Q состояния имеет низкий логический уровень, первый тактовый сигнал CKa подается на контактный вывод затвора тонкопленочного транзистора TM. Тонкопленочный транзистор TM задает потенциал сигнала Q состояния равным низкому логическому уровню, когда выходной сигнал из логической схемы 242 "AND" имеет высокий логический уровень. Тонкопленочный транзистор TD задает потенциал сигнала Q состояния равным низкому логическому уровню, когда второй тактовый сигнал CKb имеет высокий логический уровень. Логическая схема 242 "AND", тонкопленочный транзистор TM и тонкопленочный транзистор TD предусмотрены, чтобы снижать уровень потенциала сигнала Q состояния до уровня опорного потенциала по мере необходимости в течение периода времени, в который линия шины затвора, соединенная с этой бистабильной схемой SRn, должна быть в невыбранном состоянии (уровень опорного потенциала находится на уровне запирающего потенциала в течение периода времени, в который напряжение PW питания подается нормально). Другими словами, логическая схема 242 "AND", тонкопленочный транзистор TM и тонкопленочный транзистор TD предусмотрен так, что потенциал сигнала Q состояния поддерживается на уровне опорного потенциала, фокусируясь на относительно более длительном периоде времени, хотя уровень потенциала сигнала Q состояния немного выше уровня опорного потенциала, если рассматривать чрезвычайно короткий период времени. Как описано выше, в этом варианте осуществления, модуль 241 поддержания уровня потенциала реализуется посредством логической схемы 242 "AND", тонкопленочного транзистора TM и тонкопленочного транзистора TD.

Далее, работа бистабильной схемы SRn, когда напряжение PW питания внешним образом подается обычным способом, описывается со ссылкой на фиг. 9. В течение периода времени, в который жидкокристаллическое устройство отображения работает, в бистабильную схему SRn подается первый тактовый сигнал CKa и второй тактовый сигнал CKb, имеющие рабочий цикл включения, заданный так, что он составляет приблизительно 50 процентов. Здесь, касательно первого тактового сигнала CKa и второго тактового сигнала CKb, потенциал стороны высокого логического уровня является отпирающим потенциалом VGH, а потенциал стороны низкого логического уровня является запирающим потенциалом VGL. Дополнительно, в последующем описании, предполагается, что опорный потенциал VSS и запирающий потенциал VGL равны. Тем не менее, опорный потенциал VSS и запирающий потенциал VGL могут отличаться (например, опорный потенциал VSS составляет -7 В, а запирающий потенциал составляет -10 В).

В момент t1 времени, когда сигнал S задания изменяется от низкого логического уровня к высокому логическому уровню, тонкопленочный транзистор TB переключается во включенное состояние в качестве диодного включения, как проиллюстрировано на фиг. 8. Вследствие этого, конденсатор CAP заряжается, и потенциал netA изменяется от низкого логического уровня к высокому логическому уровню. Это переключает тонкопленочный транзистор TI во включенное состояние. Здесь, в течение периода времени от t1 до t3, первый тактовый сигнал CKa имеет низкий логический уровень. Следовательно, в течение этого периода времени, сигнал Q состояния поддерживается на низком логическом уровне. Дополнительно, в течение этого периода времени, поскольку сигнал R сброса имеет низкий логический уровень, тонкопленочный транзистор TL поддерживается в отключенном состоянии. Следовательно, потенциал netA не снижается в течение этого периода времени.

После того, как сигнал S задания изменяется от высокого логического уровня к низкому логическому уровню в момент t2 времени, при достижении момента t3 времени первый тактовый сигнал CKa изменяется от низкого логического уровня к высокому логическому уровню. В это время, поскольку тонкопленочный транзистор TI находится во включенном состоянии, потенциал выходного контактного вывода 45 увеличивается по мере того, как потенциал входного контактного вывода 41 увеличивается. Здесь, поскольку конденсатор CAP предусмотрен между netA и выходным контактным выводом 45, как проиллюстрировано на фиг. 8, потенциал netA увеличивается по мере того, как потенциал выходного контактного вывода 45 увеличивается (netA использует компенсационную обратную связь). Идеально, потенциал netA увеличивается до потенциала, в два раза превышающего отпирающий потенциал VGH. Как результат, высокое напряжение прикладывается к контактному выводу затвора тонкопленочного транзистора TI, и потенциал выходного контактного вывода 45 увеличивается до потенциала высокого логического уровня первого тактового сигнала Cka, т.е. отпирающего потенциала VGH. Вследствие этого, линия шины затвора, соединенная с выходным контактным выводом 45 этой бистабильной схемы SRn, переключается в выбранное состояние. Здесь, в течение периода времени от t3 до t4, тонкопленочный транзистор TN поддерживается в отключенном состоянии, поскольку сигнал R сброса имеет низкий логический уровень, и тонкопленочный транзистор TD поддерживается в отключенном состоянии, поскольку второй тактовый сигнал CKb имеет низкий логический уровень. Дополнительно, в течение этого периода времени, поскольку сигнал Q состояния имеет высокий логический уровень, выходной сигнал из логической схемы 242 "AND" задается равным низкому логическому уровню, и тонкопленочный транзистор TM находится в отключенном состоянии. Соответственно, потенциал сигнала Q состояния не снижается в течение этого периода времени. Кроме того, в течение периода времени от t3 до t4, хотя первый тактовый сигнал CKa имеет высокий логический уровень, потенциал netA приблизительно в два раза превышает отпирающий потенциал VGH, и потенциал сигнала Q состояния равен отпирающему потенциалу VGH, и, следовательно, тонкопленочный транзистор TE находится в отключенном состоянии. Дополнительно, в течение этого периода времени, поскольку сигнал R сброса имеет низкий логический уровень, тонкопленочный транзистор TL поддерживается в отключенном состоянии. Соответственно, потенциал netA не снижается в течение этого периода времени.

В момент t4 времени первый тактовый сигнал CKa изменяется от высокого логического уровня к низкому логическому уровню. Вследствие этого, потенциал выходного контактного вывода 45, т.е. потенциал сигнала Q состояния снижается по мере того, как потенциал входного контактного вывода 41 снижается. Следовательно, потенциал netA также снижается через конденсатор CAP. В момент t5 времени сигнал R сброса изменяется от низкого логического уровня к высокому логическому уровню. Вследствие этого, тонкопленочный транзистор TL и тонкопленочный транзистор TN переключаются во включенное состояние. Как результат, потенциал netA и потенциал сигнала Q состояния переходят к низкому логическому уровню.

Посредством выполнения вышеуказанной операции посредством каждой бистабильной схемы сдвигового регистра 240, сигналы OUT1-OUTi сканирования, которые последовательно задаются равными высокому логическому уровню посредством заданного периода, подаются в линии GL1-GLi шины затвора модуля 22 отображения. В этом варианте осуществления, первый тактовый сигнал CKa и второй тактовый сигнал CKb попеременно задаются равными высокому логическому уровню в течение каждого второго заданного периода, как проиллюстрировано на фиг. 9. Следовательно, тонкопленочный транзистор TD и тонкопленочный транзистор TM попеременно переключаются к включенному состоянию каждый второй заданный период. Вследствие этого, каждая линия шины затвора электрически соединена с линией опорного потенциала каждый второй заданный период (исключая период времени в выбранном состоянии), и сигнал Q состояния поддерживается на низком логическом уровне в течение периода времени в невыбранном состоянии.

1.4. Работа, когда источник питания выключен

Далее, работа жидкокристаллического устройства отображения, когда внешний источник напряжения PW питания выключен, описывается со ссылкой на фиг. 1, фиг. 2 и фиг. 8. Фиг. 1 показывает формы сигналов напряжения PW питания, сигнала SHUT состояния источника питания, отпирающего потенциала VGH, запирающего потенциала VGL, первого стробирующего синхросигнала H_CK1, второго стробирующего синхросигнала H_CK2 и опорного потенциала H_SIG_VSS. Здесь, на фиг. 1, период времени, представленный посредством ссылки с номером T-on, указывает период времени, в который напряжение PW питания подается нормально, момент времени, представленный посредством ссылки с номером tz, указывает момент времени, в который источник напряжения PW питания выключен, и период времени, представленный посредством ссылки с номером T-off, указывает период времени, в который напряжение PW питания не подается.

В течение периода времени, в который напряжение PW питания подается нормально, отпирающий потенциал VGH и запирающий потенциал VGL, подаваемые из схемы 15 электропитания в схему 13 сдвига уровня и схему 19 переключения опорного потенциала, поддерживаются, например, равными 22 В и -10 В, соответственно. Дополнительно, в течение этого периода времени, модуль 17 определения выключения питания поддерживает сигнал SHUT состояния источника питания на низком логическом уровне (здесь, потенциал GND земли). На основе этого сигнала SHUT состояния источника питания, схема 19 переключения опорного потенциала поддерживает опорный потенциал H_SIG_VSS равным запирающему потенциалу VGL. Кроме того, контроллер 11 синхронизации задает первый стробирующий синхросигнал L_CK1 и второй стробирующий синхросигнал L_CK2 попеременно равными высокому логическому уровню в течение каждого второго заданного периода на основе сигнала SHUT состояния источника питания. Как описано выше, касательно первого стробирующего синхросигнала L_CK1 и второго стробирующего синхросигнала L_CK2, потенциал стороны высокого логического уровня является напряжением PW питания, а потенциал стороны низкого логического уровня является потенциалом GND земли. Первый стробирующий синхросигнал L_CK1 и второй стробирующий синхросигнал L_CK2 подвергаются преобразованию уровня потенциала посредством схемы 13 сдвига уровня, как описано выше. Таким образом, в течение периода времени, в который напряжение PW питания подается нормально, как проиллюстрировано на фиг. 1, первый стробирующий синхросигнал H_CK1 и второй стробирующий синхросигнал H_CK2 попеременно повторяют отпирающий потенциал VGH и запирающий потенциал VGL, и опорный потенциал H_SIG_VSS поддерживается равным запирающему потенциалу VGL.

Когда источник напряжения PW питания выключен в момент tz времени, как проиллюстрировано на фиг. 1, отпирающий потенциал VGH и запирающий потенциал VGL постепенно приближаются к потенциалу GND земли. Дополнительно, при определении выключения источника напряжения PW питания (отключенного состояния источника питания), модуль 17 определения выключения питания задает сигнал SHUT состояния источника питания равным высокому логическому уровню. При определении сигнала SHUT состояния источника питания равным высокому логическому уровню, контроллер 11 синхронизации задает первый стробирующий синхросигнал L_CK1 и второй стробирующий синхросигнал L_CK2 равными высокому логическому уровню. Первый стробирующий синхросигнал L_CK1 и второй стробирующий синхросигнал L_CK2 подвергаются преобразованию уровня потенциала посредством схемы 13 сдвига уровня. В это время, поскольку первый стробирующий синхросигнал L_CK1 и второй стробирующий синхросигнал L_CK2 имеют высокий логический уровень, первый стробирующий синхросигнал H_CK1 и второй стробирующий синхросигнал H_CK2 задаются равными отпирающему потенциалу VGH. Кроме того, схема 19 переключения опорного потенциала переключает опорный потенциал H_SIG_VSS от запирающего потенциала VGL к отпирающему потенциалу VGH на основе сигнала SHUT состояния источника питания. Таким образом, в момент tz времени, в который источник напряжения PW питания выключен, как проиллюстрировано на фиг. 1, опорный потенциал H_SIG_VSS, первый стробирующий синхросигнал H_CK1 и второй стробирующий синхросигнал H_CK2 задаются равными отпирающему потенциалу VGH.

Когда оба из первого стробирующего синхросигнала H_CK1 и второго стробирующего синхросигнала H_CK2 задаются равными отпирающему потенциалу VGH, первый тактовый сигнал CKa и второй тактовый сигнал CKb, подаваемые в каждую бистабильную схему (см. фиг. 8), задаются равными высокому логическому уровню. Затем, посредством переключения второго тактового сигнала CKb к высокому логическому уровню, тонкопленочный транзистор TD переключается во включенное состояние. Дополнительно, линии шины затвора переключаются в выбранное состояние только в течение короткого периода времени в одном периоде вертикального сканирования, и, следовательно, сигналы Q состояния большинства бистабильных схем имеют низкий логический уровень. Следовательно, посредством переключения первого тактового сигнала CKa к высокому логическому уровню выходной сигнал из логической схемы 242 "AND" задается равным высокому логическому уровню в большинстве бистабильных схем, и тонкопленочный транзистор TM переключается во включенное состояние. Вследствие этого, линия шины затвора, соединенная с каждой бистабильной схемой, электрически соединена с линией опорного потенциала, которая передает опорный потенциал H_SIG_VSS. Кроме того, в этом варианте осуществления, в момент tz времени, в который источник напряжения PW питания выключен, опорный потенциал H_SIG_VSS увеличивается от запирающего потенциала VGL до отпирающего потенциала VGH. Это увеличивает потенциал сигнала Q состояния, выводимого из каждой бистабильной схемы, и тонкопленочный транзистор 220 переключается во включенное состояние на каждом участке формирования пикселов в модуле 22 отображения (см. фиг. 3). Как результат, остаточные заряды на участках формирования пикселов быстро разряжаются.

1.5. Преимущества

Согласно этому варианту осуществления, бистабильная схема, которая составляет сдвиговый регистр 240 в драйвере 24 затвора, содержит модуль 241 поддержания уровня потенциала для поддержания потенциала сигнала Q состояния на низком логическом уровне (строго говоря, снижения уровня потенциала сигнала Q состояния до уровня опорного потенциала по мере необходимости) в течение периода времени, в который линия шины затвора, соединенная с этой бистабильной схемой, должна быть в невыбранном состоянии. Модуль 241 поддержания уровня потенциала конфигурирована посредством логической схемы 242 "AND" для подачи сигнала, указывающего логическое "AND" между логическим значением сигнала логической инверсии сигнала Q состояния и логическим значением первого тактового сигнала CKa, на контактный вывод затвора тонкопленочного транзистора TM, тонкопленочного транзистора TM для электрического соединения линии шины затвора и линии опорного потенциала, когда выходной сигнал из логической схемы 242 "AND" имеет высокий логический уровень, и тонкопленочного транзистора TD для электрического соединения линии шины затвора и линии опорного потенциала, когда второй тактовый сигнал CKb имеет высокий логический уровень. В этой конфигурации, когда внешний источник напряжения PW питания выключен, первый тактовый сигнал CKa и второй тактовый сигнал CKb задаются равными высокому логическому уровню. Вследствие этого, в каждой бистабильной схеме тонкопленочный транзистор TM и тонкопленочный транзистор TD задаются равными включенному состоянию, и линия шины затвора и линия опорного потенциала электрически соединены. Дополнительно, когда внешний источник напряжения PW питания выключен, уровень опорного потенциала VSS, подаваемого в каждую бистабильную схему, увеличивается от запирающего потенциала VGL до отпирающего потенциала VGH. Вследствие этого, поскольку линии шины затвора переключаются в выбранное состояние, а тонкопленочный транзистор 220 каждого участка формирования пикселов переключается во включенное состояние, остаточные заряды участков формирования пикселов быстро разряжаются. Как результат, когда источник питания жидкокристаллического устройства отображения затем включается, понижение визуального качества вследствие остаточных зарядов, накопленных на участках формирования пикселов, подавляется.

2. Второй вариант осуществления

Ниже описан второй вариант осуществления настоящего изобретения. Здесь, только отличия от первого варианта осуществления подробно описываются, а общие черты с первым вариантом осуществления описываются только вкратце.

2.1. Общая конфигурация и работа

Фиг. 10 является блок-схемой, иллюстрирующей общую конфигурацию жидкокристаллического устройства отображения с активной матрицей согласно второму варианту осуществления настоящего изобретения. Жидкокристаллическая панель 20 и TAB 30 имеют такую же конфигурацию, как в первом варианте осуществления. На PCB 50 формируются контроллер 51 синхронизации, схема 53 сдвига уровня, схема 55 электропитания и модуль 57 определения выключения питания.

Схема 55 электропитания формирует отпирающий потенциал VGH и запирающий потенциал VGL на основе напряжения PW питания. Отпирающий потенциал VGH и запирающий потенциал VGL подаются в схему 53 сдвига уровня. Модуль 57 определения выключения питания выводит сигнал SHUT состояния источника питания, указывающий состояние источника напряжения PW питания (включенное/выключенное состояние источника питания). Сигнал SHUT состояния источника питания подается в контроллер 51 синхронизации.

Контроллер 51 синхронизации принимает синхронизирующие сигналы, такие как сигнал HS горизонтальной синхронизации, сигнал VS вертикальной синхронизации и сигнал DE разрешения передачи данных, а также сигнал DAT изображения, напряжение PW питания и сигнал SHUT состояния источника питания, и формирует цифровой видеосигнал DV, сигнал SSP пускового импульса истока, синхросигнал SCK истока, сигнал L_GSP пускового импульса затвора, первый стробирующий синхросигнал L_CK1, второй стробирующий синхросигнал L_CK2 и опорный потенциал L_SIG_VSS. Цифровой видеосигнал DV, сигнал SSP пускового импульса истока и синхросигнал SCK истока подаются в драйвер 32 истока, а сигнал L_GSP пускового импульса затвора, первый стробирующий синхросигнал L_CK1, второй стробирующий синхросигнал L_CK2 и опорный потенциал L_SIG_VSS подаются в схему 53 сдвига уровня. Здесь, касательно опорного потенциала L_SIG_VSS, потенциал стороны высокого логического уровня является напряжением PW питания, а потенциал стороны низкого логического уровня является потенциалом GND земли.

Схема 53 сдвига уровня преобразует уровни потенциала сигнала L_GSP пускового импульса затвора, первого стробирующего синхросигнала L_CK1, второго стробирующего синхросигнала L_CK2 и опорного потенциала L_SIG_VSS, которые выводятся из контроллера 51 синхронизации, с использованием отпирающего потенциала VGH и запирающего потенциала VGL, которые подаются из схемы 55 электропитания. Сигнал H_GSP пускового импульса затвора, первый стробирующий синхросигнал H_CK1, второй стробирующий синхросигнал H_CK2 и опорный потенциал H_SIG_VSS после преобразования уровня потенциала посредством схемы 53 сдвига уровня подаются в драйвер 24 затвора. При преобразовании уровня потенциала посредством схемы 53 сдвига уровня, опорный потенциал H_SIG_VSS задается равным запирающему потенциалу VGL, когда опорный потенциал L_SIG_VSS имеет низкий логический уровень, и опорный потенциал H_SIG_VSS задается равным отпирающему потенциалу VGH, когда опорный потенциал L_SIG_VSS имеет высокий логический уровень.

Драйвер 32 истока и драйвер 24 затвора выполняют операции, идентичные операциям в первом варианте осуществления. Вследствие этого, видеосигнал возбуждения применяется к каждой из линий SL1-SLj шины истока, и сигнал сканирования применяется к каждой из линий GL1-GLi шины затвора, и тем самым изображение на основе сигнала DAT изображения, подаваемого внешним образом, отображается на модуле 22 отображения.

В этом варианте осуществления, модуль определения состояния источника питания реализуется посредством модуля 57 определения выключения питания, и модуль формирования опорного потенциала и модуль формирования синхросигнала реализуются посредством контроллера 51 синхронизации и схемы 53 сдвига уровня.

Сдвиговый регистр 240 и бистабильные схемы имеет такую же конфигурацию, как в первом варианте осуществления (см. фиг. 6 и фиг. 8). Соответственно, операции сдвигового регистра 240 и бистабильных схем являются идентичными операциям в первом варианте осуществления (см. фиг. 7 и фиг. 9).

2.2. Способ для изменения опорного потенциала

В первом варианте осуществления, уровень опорного потенциала H_SIG_VSS, подаваемого в линию опорного потенциала, переключается между запирающим потенциалом VGL и отпирающим потенциалом VGH с использованием схемы 19 переключения опорного потенциала, сконфигурированной посредством, к примеру, транзистора. В частности, в первом варианте осуществления, конфигурация для увеличения уровня опорного потенциала H_SIG_VSS, когда источник напряжения PW питания выключен, реализуется посредством аналогового способа. В отличие от этого, в этом варианте осуществления конфигурация для увеличения уровня опорного потенциала H_SIG_VSS реализуется посредством цифрового способа. Это описывается ниже.

В течение периода времени, в который напряжение PW питания подается нормально, сигнал SHUT состояния источника питания, выводимый из модуля 57 определения выключения питания, задается равным низкому логическому уровню. Вследствие этого, опорный потенциал L_SIG_VSS, подаваемый из контроллера 51 синхронизации в схему 53 сдвига уровня, имеет низкий логический уровень. Здесь, как описано выше, при преобразовании уровня потенциала посредством схемы 53 сдвига уровня, опорный потенциал H_SIG_VSS задается равным запирающему потенциалу VGL, когда опорный потенциал L_SIG_VSS имеет низкий логический уровень. Соответственно, в течение периода времени, в который напряжение PW питания подается нормально, опорный потенциал H_SIG_VSS, подаваемый в линию опорного потенциала, задается равным запирающему потенциалу VGL.

Когда источник напряжения PW питания выключен, сигнал SHUT состояния источника питания, выводимый из модуля 57 определения выключения питания, задается равным высокому логическому уровню. Вследствие этого, опорный потенциал L_SIG_VSS, подаваемый из контроллера 51 синхронизации в схему 53 сдвига уровня, имеет высокий логический уровень. Здесь, как описано выше, при преобразовании уровня потенциала посредством схемы 53 сдвига уровня, опорный потенциал H_SIG_VSS задается равным отпирающему потенциалу VGH, когда опорный потенциал L_SIG_VSS имеет высокий логический уровень. Соответственно, опорный потенциал H_SIG_VSS, выводимый из схемы 53 сдвига уровня, изменяется от запирающего потенциала VGL к отпирающему потенциалу VGH. Таким образом, когда источник напряжения PW питания выключен, опорный потенциал H_SIG_VSS, подаваемый в линию опорного потенциала, задается равным отпирающему потенциалу VGH.

Здесь, когда источник напряжения PW питания выключен, аналогично первому варианту осуществления, первый стробирующий синхросигнал H_CK1 и второй стробирующий синхросигнал H_CK2 задаются равными отпирающему потенциалу VGH. В частности, когда источник напряжения PW питания выключен, аналогично первому варианту осуществления, опорный потенциал H_SIG_VSS, первый стробирующий синхросигнал H_CK1 и второй стробирующий синхросигнал H_CK2 задаются равными отпирающему потенциалу VGH (см. фиг. 1).

2.3. Преимущества

Согласно этому варианту осуществления, аналогично первому варианту осуществления, когда внешний источник напряжения PW питания выключен, линии шины затвора и линия опорного потенциала электрически соединены, и уровень опорного потенциала VSS увеличивается от запирающего потенциала VGL до отпирающего потенциала VGH. Вследствие этого, линии шины затвора переключаются в выбранное состояние, и остаточные заряды участков формирования пикселов быстро разряжаются. Как результат, понижение визуального качества вследствие остаточных зарядов, накопленных на участках формирования пикселов, подавляется.

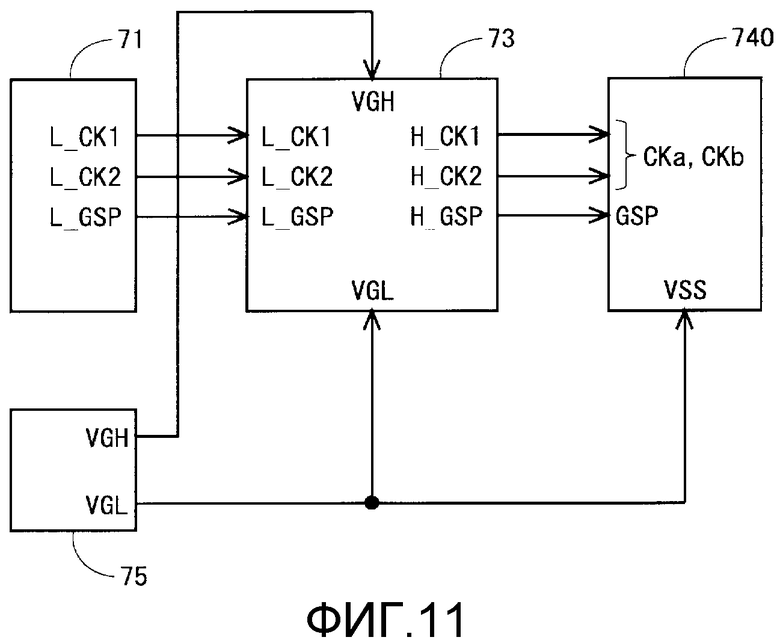

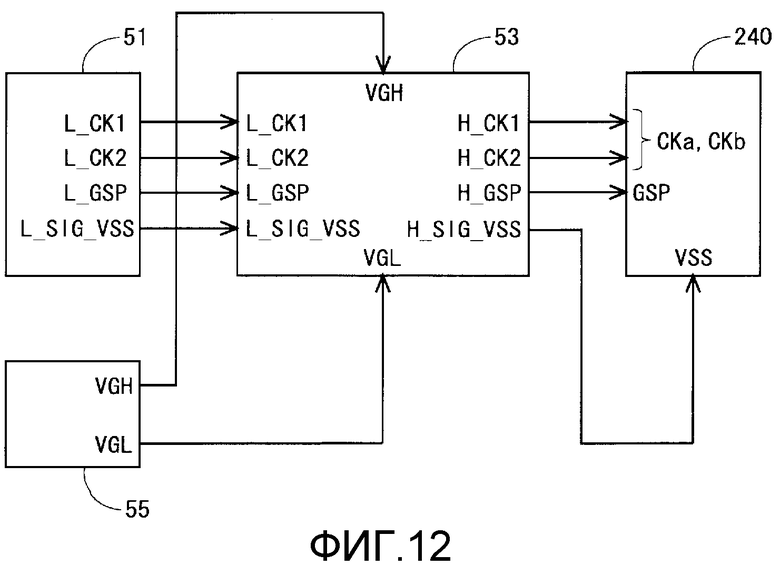

Дополнительно, согласно этому варианту осуществления, жидкокристаллическое устройство отображения, допускающее быстрое исключение остаточных зарядов на участках формирования пикселов, когда питание выключается, может быть реализовано при относительно низких затратах. Это описано ниже. Согласно обычной конфигурации, как проиллюстрировано на фиг. 11, например, запирающий потенциал VGL, выводимый из схемы 75 электропитания, подается в качестве опорного потенциала VSS в сдвиговый регистр 740. Кроме того, в монолитной панели с драйвером затвора, чтобы получать относительно высокое напряжение в панели, необходимо предусмотреть схему 73 сдвига уровня вне панели, как проиллюстрировано на фиг. 11. Согласно такой обычной конфигурации, опорный потенциал VSS, подаваемый в сдвиговый регистр 740, является фиксированным потенциалом. В этом случае, даже когда тонкопленочные транзисторы TD и TM, проиллюстрированные на фиг. 8, переключаются во включенное состояние, невозможно увеличивать потенциал сигнала Q состояния, выводимого из каждой бистабильной схемы. Таким образом, в этом варианте осуществления, как проиллюстрировано на фиг. 12, конфигурация является такой, что выходной сигнал H_SIG_VSS, выводимый из схемы 53 сдвига уровня, подается в сдвиговый регистр 240 в качестве опорного потенциала VSS. При такой конфигурации можно легко задавать уровень опорного потенциала VSS, подаваемого в сдвиговый регистр 240, переменным и увеличивать потенциал сигнала Q состояния, выводимого из каждой бистабильной схемы, когда тонкопленочные транзисторы TD и TM находятся во включенном состоянии. Здесь, как описано выше, в монолитной панели с драйвером затвора, схема сдвига уровня обычно обеспечена вне панели. Следовательно, не обязательно увеличивать число схемных компонентов и т.п., даже когда конфигурация является такой, что выходной сигнал из схемы сдвига уровня используется для опорного потенциала. Соответственно, жидкокристаллическое устройство отображения, допускающее быстрое исключение остаточных зарядов на участках формирования пикселов, может быть реализовано при небольших затратах. Дополнительно, поскольку можно выполнять цифровую обработку посредством использования схемы сдвига уровня, управление схем может быть упрощено.

2.4. Модифицированные примеры

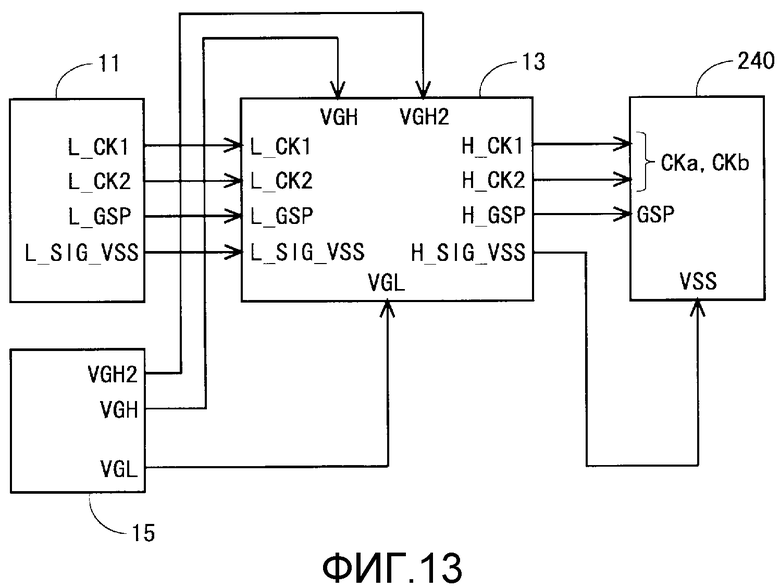

Согласно второму варианту осуществления, конфигурация является такой, что уровень опорного потенциала VSS, подаваемого в сдвиговый регистр 240, увеличивается от запирающего потенциала VGL до отпирающего потенциала VGH, когда источник напряжения PW питания выключен. Тем не менее, настоящее изобретение не ограничено этим. Например, в случае, если потенциал электрода 223 вспомогательной емкости (см. фиг. 3) задается равным относительно высокому напряжению, когда источник напряжения PW питания выключен, потенциал стока тонкопленочного транзистора 220 на участке формирования пикселов в значительной степени снижается. Следовательно, он может переключиться во включенное состояние, даже если потенциал, подаваемый в линии шины затвора, ниже отпирающего потенциала VGH. Таким образом, как проиллюстрировано на фиг. 13, можно использовать конфигурацию, в которой второй отпирающий потенциал VGH2 (например, 10 В) ниже отпирающего потенциала VGH (например, 22 В) подается из схемы 15 электропитания в схему 13 сдвига уровня, так что уровень опорного потенциала VSS, подаваемого в сдвиговый регистр 240, увеличивается от запирающего потенциала VGL до второго отпирающего потенциала VGH2, когда источник напряжения PW питания выключен.

3. Другие конфигурации

3.1. Число фаз синхросигнала

Согласно вариантам осуществления, описанным выше, сдвиговый регистр 240 работает на основе двухфазных синхросигналов. Тем не менее, число фаз синхросигнала не ограничено двумя. Далее описывается пример применения настоящего изобретения к жидкокристаллическому устройству отображения, содержащему сдвиговый регистр 640, работающий на основе четырехфазных синхросигналов. Фиг. 14 является блок-схемой, иллюстрирующей пример конфигурации сдвигового регистра 640, работающего на основе четырехфазных синхросигналов. Здесь, фиг. 14 показывает конфигурацию бистабильных схем SR1-SR4 первого-четвертого каскадов сдвигового регистра 640. Каждая бистабильная схема содержит, в дополнение к входным/выходным контактным выводам согласно первому варианту осуществления, входной контактный вывод для приема третьего тактового сигнала CKc и входной контактный вывод для приема четвертого тактового сигнала CKd. Первый-четвертый стробирующие синхросигналы H_CK1-H_CK4, передаваемые в сдвиговый регистр 640, подаются в каждую бистабильную схему, как проиллюстрировано на фиг. 14. Фиг. 15 является принципиальной схемой, иллюстрирующей конфигурацию каждой бистабильной схемы, включенной в сдвиговый регистр 640. В первом варианте осуществления, модуль 241 поддержания уровня потенциала для поддержания потенциала сигнала Q состояния на низком логическом уровне реализуется посредством логической схемы 242 "AND", тонкопленочного транзистора TM и тонкопленочного транзистора TD (см. фиг. 8). В отличие от этого, согласно конфигурации, проиллюстрированной на фиг. 15, модуль 245 поддержания уровня потенциала реализуется посредством тонкопленочного транзистора TD, сконфигурированного таким же образом, как в первом варианте осуществления, тонкопленочного транзистора TP, на контактный вывод затвора которого подается третий тактовый сигнал CKc, и тонкопленочного транзистора TQ, на контактный вывод затвора которого подается четвертый тактовый сигнал CKd.

В вышеуказанной конфигурации, первый-четвертый стробирующие синхросигналы H_CK1-H_CK4, имеющие такие формы сигналов, как проиллюстрировано на фиг. 16, подаются в сдвиговый регистр 640. Вследствие этого, каждая бистабильная схема работает так, как описано ниже (см. фиг. 17).