Предлагаемые технические решения объединены единым изобретательским замыслом и относятся к области электросвязи, а именно к технике секретной (конфиденциальной) связи, обеспечивающей шифрованную передачу избыточных сообщений, таких как преобразованные к цифровому виду речевые, звуковые, телевизионные, факсимильные и т.п. сообщения.

Предлагаемые способ и устройство шифрования/дешифрования сообщений хэширующей функцией могут быть использованы для исключения несанкционированного доступа третьих лиц к сообщениям, передаваемым отправителем получателю сообщений по дискретным каналам связи, с одновременным повышением достоверности передачи в условиях воздействия ошибок передачи. Под термином "шифрование" понимают преобразование сообщений с использованием известного отправителю и получателю сообщений секретного ключа на передаче и обратное преобразование на приеме, исключающее или существенно затрудняющее несанкционированный доступ к передаваемым сообщениям третьих лиц, которым не известен секретный ключ. Под термином "криптограмма" понимают передаваемое по каналу связи зашифрованное сообщение.

Известные способы шифрования/дешифрования сообщений описаны, например, в книге: Дж. Месси "Введение в современную криптологию". ТИИЭР, 1988, - т. 76, N 5, стр. 34. Они заключаются в формировании отправителем сообщений шифрующей последовательности из секретного ключа, поэлементном сложении очередного элемента последовательности сообщения с очередным элементом шифрующей последовательности, передаче получателю сообщений зашифрованной последовательности, формировании получателем сообщений дешифрующей последовательности из секретного ключа и дешифровании последовательности сообщения поэлементным вычитанием из очередного элемента зашифрованной последовательности соответствующего ему элемента шифрующей последовательности. Недостатком известных способов шифрования/дешифрования сообщений является низкая достоверность передачи зашифрованных сообщений по каналам с помехами, обусловленная невозможностью обнаружения ошибок передачи. По виду принятого зашифрованного сообщения невозможно определить, искажено ли оно ошибками передачи, так как в известных способах шифрования/дешифрования сообщений может быть сформировано зашифрованное сообщение произвольного вида.

Известные устройства шифрования/дешифрования сообщений описаны, например, в книге: У.Диффи, М. Хэллмен "Защищенность и имитостойкость". ТИИЭР, 1979, - т. 67, N3, стр. 55. Устройство включает передающий и приемный узлы. Передающий узел состоит из блока наложения шифрующей последовательности, блока памяти секретного ключа, блока преобразования и счетчика. Шифрующая последовательность на выходе блока преобразования формируется в зависимости от значения секретного ключа и текущего состояния счетчика. В блоке наложения шифрующей последовательности осуществляется поэлементное суммирование последовательности сообщения с шифрующей последовательностью. Зашифрованное сообщение передается по каналу-связи. В приемном узле, состоящем из блока вычитания шифрующей последовательности, блока памяти секретного ключа, блока преобразования и счетчика, синхронно формируется шифрующая последовательность, идентичная шифрующей последовательности, сформированной в передающем узле. Дешифрование сообщения выполняется в блоке вычитания шифрующей последовательности поэлементным вычитанием из принятой последовательности зашифрованного сообщения шифрующей последовательности. Недостатком известных устройств шифрования/дешифрования сообщений является низкая достоверность передачи зашифрованных сообщений по каналам с помехами, обусловленная невозможностью обнаружения ошибок передачи. По виду принятого зашифрованного сообщения невозможно определить, искажено ли оно ошибками передачи, так как в известных устройствах шифрования/дешифрования сообщений может быть сформировано зашифрованное сообщение произвольного вида.

Наиболее близким по своей технической сущности к заявленному способу шифрования/дешифрования сообщений хэширующей функцией является способ, описанный в патенте США 5483598 МПК6 H 04 L 9/20 от 9.01.96. Способ-прототип шифрования/дешифрования сообщений хэширующей функцией заключается в предварительном формировании функции хэширования, секретного ключа и стартового блока двоичных символов, передаче между отправителем и получателем сообщений секретного ключа и стартового блока двоичных символов, разбиении сообщения на информационные блоки двоичных символов, хэшировании отправителем сообщений стартового блока двоичных символов по функции хэширования и секретному ключу, шифровании первого информационного блока двоичных символов сложением его с хэшированным стартовым блоком двоичных символов, передаче получателю сообщений блока криптограммы двоичных символов, хэшировании попучателем сообщений стартового блока двоичных символов по функции хэширования и секретному ключу, дешифровании принятого блока криптограммы вычитанием из него хэшированного стартового блока двоичных символов и восстановления тем самым первого информационного блока двоичных символов. Для шифрования второго и последующих информационных блоков двоичных символов хэшируют предыдущий блок криптограммы по функции хэширования и секретному ключу, а затем шифруют очередной информационный блок двоичных символов сложением с очередным хэшированным блоком двоичных символов. Очередной блок криптограммы передают получателю сообщений, который аналогичным образом хэширует предыдущий полученный блок криптограммы по функции хэширования и секретному ключу, а затем дешифрует очередной принятый блок криптограммы вычитанием из него очередного хэшированного блока двоичных символов, причем повторное хэширование блоков криптограмм и последующие за ним действия выполняют до тех пор, пока поступают очередные информационные блоки двоичных символов.

Недостатком прототипа заявленного способа шифрования/дешифрования сообщений хэширующей функцией является низкая достоверность передачи зашифрованных сообщений по каналам с помехами, обусловленная невозможностью обнаружения ошибок передачи. По виду принятого зашифрованного сообщения невозможно определить, искажено ли оно ошибками передачи, так как в известных способах шифрования/дешифрования сообщений хэширующей функцией может быть сформировано зашифрованное сообщение произвольного вида.

Наиболее близким по своей технической сущности к заявленному устройству шифрования/дешифрования сообщений хэширующей функцией является устройство, описанное в патенте США N 548 3598 МПК5 H 04 L 9/20 от 9.01.96. Известное устройство-прототип включает передающий и приемный узлы. На передающем узле вход модуля памяти информационного блока является входом устройства. Вход секретного ключа блока хэширования подключен к выходу модуля памяти секретного ключа. Первый информационный вход блока хэширования подключен к выходу блока коммутации, первый информационный вход блока коммутации подключен к выходу модуля памяти стартового блока, второй информационный вход блока коммутации подключен к выходу модуля памяти предыдущего блока криптограммы. Выход модуля памяти информационного блока соединен с первым входом сумматора по модулю 2, выход блока хэширования соединен с вторым входом сумматора по модулю 2. Выход сумматора по модулю 2 соединен с входом модуля памяти блока криптограммы и в параллель с входом модуля памяти предыдущего блока криптограммы. Выход модуля памяти блока криптограммы соединен со входом канала связи. На приемном узле вход модуля памяти принятого блока криптограммы подключен к выходу канала связи. Вход секретного ключа блока хэширования подключен к выходу модуля памяти секретного ключа, первый информационный вход блока хэширования подключен к выходу блока коммутации, первый информационный вход блока коммутации подключен к выходу модуля памяти стартового блока, второй информационный вход блока коммутации подключен к выходу модуля памяти предыдущего принятого блока криптограммы. Выход модуля памяти принятого блока криптограммы соединен с первым входом сумматора по модулю 2 и в параллель с входом модуля памяти предыдущего принятого блока криптограммы. Выход сумматора по модулю является выходом устройства.

Недостатком прототипа заявленного устройства шифрования/дешифрования сообщений хзширующей функцией является низкая достоверность передачи зашифрованных сообщений по каналам с помехами, обусловленная невозможностью обнаружения ошибок передачи. По виду принятого зашифрованного сообщения невозможно определить, искажено ли оно ошибками передачи, так как в известных устройствах шифрования/дешифрования сообщений хэширующей функкцией может быть сформировано зашифрованное сообщение произвольного вида.

Целью изобретения заявленных технических решений является разработка способа шифрования/дешифрования сообщений хэширующей функцией и устройства, его реализующего, обеспечивающих повышение достоверности передачи зашифрованных сообщений по каналам с помехами благодаря обнаружению ошибок передачи и повторной передачи зашифрованных сообщений, принятых с ошибкой.

Поставленная цель достигается тем, что в известном способе шифрования/дешифрования сообщений хэширующей функцией, заключающемся в предварительном формировании функции хэширования, секретного ключа и стартового блока двоичных символов, передаче между отправителем и получателем сообщений секретного ключа и стартового блока двоичных символов, разбиении сообщения на информационные блоки символов, хэшировании отправителем сообщений блоков двоичных символов, передаче получателю сообщений блоков двоичных символов и хэшировании принятых блоков двоичных символов, дополнительно предварительно формируют N помехоустойчивых блоков криптограмм, где N>2. Формирование N помехоустойчивых блоков криптограмм выполняют перемножением каждого из N блоков двоичных символов на порождающую матрицу двоичного помехоустойчивого кода. Хэшируют помехоустойчивые блоки криптограмм по функции хэширования, секретному ключу и стартовому блоку двоичных символов, сравнивают каждый i-й, где i= 1, 2,...,N, хэшированный помехоустойчивый блок криптограммы с первым информационным блоком q-ичных символов, где q>2. Среди N хэшированных помехоустойчивых блоков криптограмм выбирают наиболее близкий к первому информационному блоку q-ичных символов. Для сравнения каждого i-го, где i = 1, 2, . . . ,N, хэшированного помехоустойчивого блока криптограммы с первым информационным блоком q-ичных символов из значения каждого q-ичного отсчета i-го хэшированного помехоустойчивого блока криптограммы вычитают соответствующее ему значение q-ичного отсчета первого информационного блока q-ичных символов, для каждого i-го хэшированного помехоустойчивого блока криптограммы абсолютные значения полученных разностей суммируют, а наиболее близкий хэшированный помехоустойчивый блок криптограммы к первому информационному блоку q-ичных символов выбирают соответствующий минимальный сумме полученных разностей. Помехоустойчивый блок криптограммы, соответствующий выбранному хэшированному помехоустойчивому блоку криптограммы, передают по прямому каналу связи получателю сообщений, идентифицируют принятый помехоустойчивый блок криптограммы с N помехоустойчивыми блоками криптограмм, и если он не идентифицирован, стирают принятый помехоустойчивый блок криптограммы и по обратному каналу связи передают управляющий сигнал для повторной передачи получателю сообщений помехоустойчивого блока криптограммы, соответствующего выбранному хэшированному помехоустойчивому блоку криптограммы. Принятый идентифицированный помехоустойчивый блок криптограммы хэшируют по функции хэширования, секретному ключу и стартовому блоку двоичных символов. Повторно хэшируют N помехоустойчивых блоков криптограмм по функции хэширования, секретному ключу и помехоустойчивому блоку криптограммы, соответствующему выбранному на предыдущем шаге хэшированному помехоустойчивому блоку криптограммы, сравнивают каждый i-й, где i=1,2,..,N, хэшированный помехоустойчивый блок криптограммы с очередным информационным блоком q-ичных символов, среди N хэшированных помехоустойчивых блоков криптограмм выбирают наиболее близкий к очередному информационному блоку q-ичных символов. Для сравнения каждого i-го, где i =1, 2,...,N, хэшированного помехоустойчивого блока криптограммы с очередным информационным блоком q-ичных символов из значения каждого q-ичного отсчета i-го хэшированного помехоустойчивого блока криптограммы вычитают соответствующее ему значение q-ичного отсчета очередного информационного блока q-ичных символов, для каждого i-го хэшированного помехоустойчивого блока криптограммы абсолютные значения полученных разностей суммируют, а наиболее близкий хэшированный помехоустойчивый блок криптограммы к очередному информационному блоку q-ичных символов выбирают соответствующий минимальной сумме полученных разностей. Передают по прямому каналу связи получателю сообщений помехоустойчивый блок криптограммы, соответствующий выбранному хэшированному помехоустойчивому блоку криптограммы. Идентифицируют принятый помехоустойчивый блок криптограммы с N помехоустойчивыми блоками криптограмм, и если он не идентифицирован, стирают принятый помехоустойчивый блок криптограммы и по обратному каналу связи передают управляющий сигнал для повторной передачи получателю сообщений помехоустойчивого блока криптограммы, соответствующего выбранному хэшированному помехоустойчивому блоку криптограммы. Хэшируют принятый идентифицированный помехоустойчивый блок криптограммы по функции хэширования, секретному ключу и предыдущему принятому идентифицированному помехоустойчивому блоку криптограммы. Повторное хэширование помехоустойчивых блоков криптограмм и последующие за ним действия выполняются до тех пор, пока поступают очередные информационные блоки q-ичных символов.

Указанная новая совокупность выполняемых действий за счет передачи по каналу связи заранее сформированных помехоустойчивых блоков криптограмм позволяет повысить достоверность передачи путем обнаружения ошибок передачи и повторной передачи зашифрованных сообщений, принятых с ошибкой, без внесения дополнительной избыточности в передаваемые зашифрованные сообщения.

Поставленная цель достигается тем, что в известном устройстве шифрования/дешифрования сообщений хэширующей фикцией, содержащем на передающем узле модуль памяти информационного блока, вход которого является входом устройства, блок хэширования, вход секретного ключа которого подключен к выходу модуля памяти секретного ключа. Первый вход блока хэширования подключен к выходу блока коммутации, первый информационный вход блока коммутации подключен к выходу модуля памяти стартового блока, второй информационный вход блока коммутации подключен к выходу модуля памяти предыдущего блока криптограммы, модуль памяти блока криптограммы, информационный выход которого соединен со входом прямого канала связи. На приемном узле модуль памяти принятого блока криптограммы, вход которого подключен к выходу прямого канала связи, блок хэширования, вход секретного ключа которого подключен к выходу модуля памяти секретного ключа. Первый информационный вход блока хэширования подключен к выходу блока коммутации, первый информационный вход блока коммутации подключен к выходу модуля памяти стартового блока, второй информационный вход блока коммутации подключен к выходу модуля памяти предыдущего принятого блока криптограммы. На передающем узле дополнительно введены блок выбора, первый информационный вход которого соединен с модулем памяти информационного блока, второй информационный вход блока выбора подключен к выходу блока хэширования, выход блока выбора подключен к информационному входу модуля памяти помехоустойчивых блоков криптограмм, выход которого соединен с информационным входом коммутатора, первый информационный выход коммутатора подключен ко второму информационному входу блока хэширования, второй информационный выход коммутатора подключен к информационному входу модуля памяти блока криптограммы и параллельно к входу модуля памяти предыдущего блока криптограммы. Первый управляющий вход модуля памяти блока криптограммы соединен с выходом обратного канала связи. На приемном узле дополнительно введены блок идентификации, первый информационный вход которого соединен с выходом модуля памяти принятого блока криптограммы, второй информационный вход блока идентификации соединен с выходом модуля памяти помехоустойчивых блоков криптограмм, первый управляющий выход блока идентификации соединен с управляющим входом модуля памяти помехоустойчивых блоков криптограмм, второй управляющий выход блока идентификации соединен с управляющим входом ключа, третий управляющий выход блока идентификации соединен со входом обратного канала связи и параллельно с входом стирания модуля памяти принятого блока криптограммы, информационный вход ключа соединен с выходом модуля памяти принятого блока криптограммы, информационный выход ключа соединен с вторым информационным входом блока хэширования и параллельно со входом модуля памяти предыдущего принятого блока криптограммы, выход блока хэширования является выходом устройства, причем модуль памяти информационного блока, блок выбора, блок хэширования, модуль памяти секретного ключа, блок коммутации, модуль памяти стартового блока, модуль памяти блока криптограммы, модуль памяти предыдущего блока криптограммы, модуль памяти помехоустойчивых блоков криптограмм, модуль памяти блока криптограммы, коммутатор на передающем узле, модуль памяти принятого блока криптограммы, блок идентификации, блок коммутации, модуль памяти секретного ключа, блок хэширования, блок коммутации, модуль памяти предыдущего принятого блока криптограммы, модуль памяти стартового блока на приемном узле снабжены управляющими входами, на которые поступают сигналы управления, формируемые блоком управления не входящим в состав заявленного устройства. Проведенный заявителем анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностями признаков, тождественных всем признакам заявленных способа и устройства шифрования/дешифрования сообщений хэширующей функцией, отсутствуют. Следовательно, каждое из заявленных изобретений соответствует условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипов признаками каждого заявленного изобретения, показали, что они не следуют явным образом из уровня техники. Из определенного заявителем уровня техники не выявлена известность влияния предусматриваемых существенными признаками каждого из заявленных изобретений на достижение указанного технического результата. Следовательно, каждое из заявленных изобретений соответствует условию патентоспособности "изобретательский уровень".

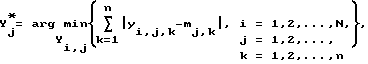

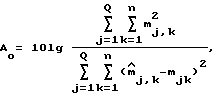

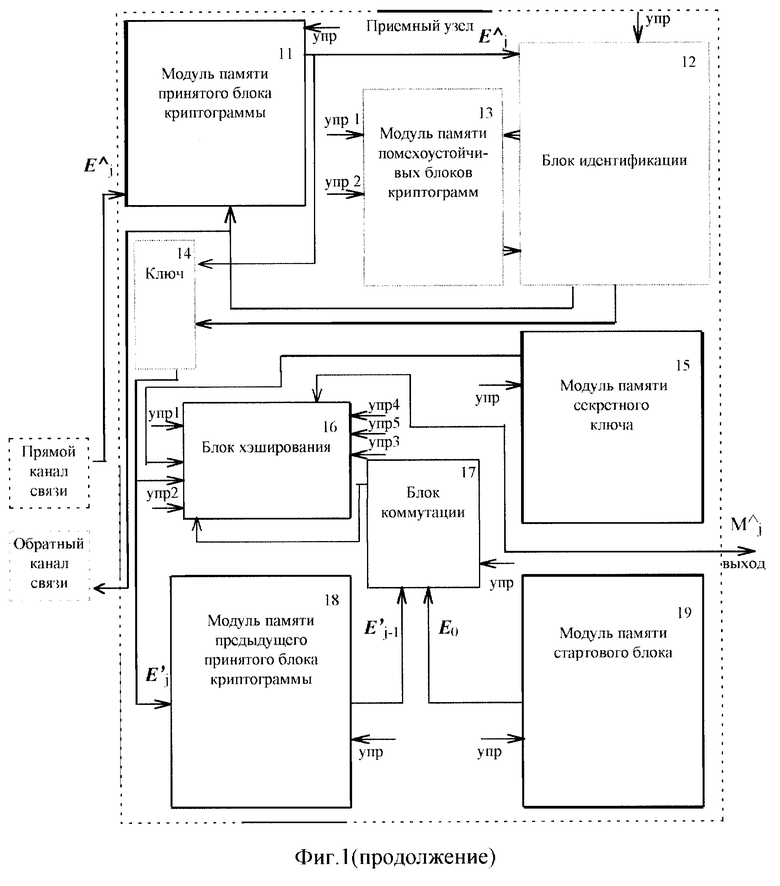

Заявленные объекты изобретения поясняются чертежами, на которых:

- на фиг. 1 - структурная схема устройства шифрования/дешифрования сообщений хэширующей функцией;

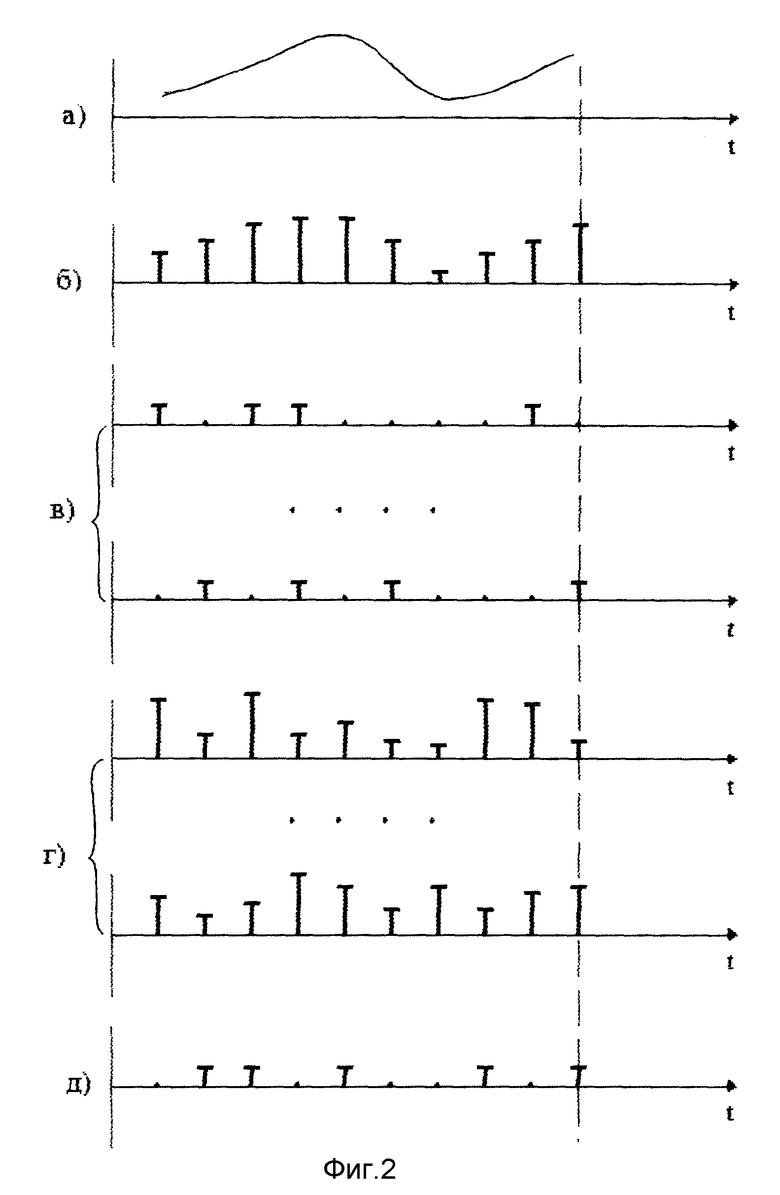

- на фиг. 2 - осциллограммы, поясняющие суть заявляемого способа шифрования/дешифрования сообщений хэширующей функцией;

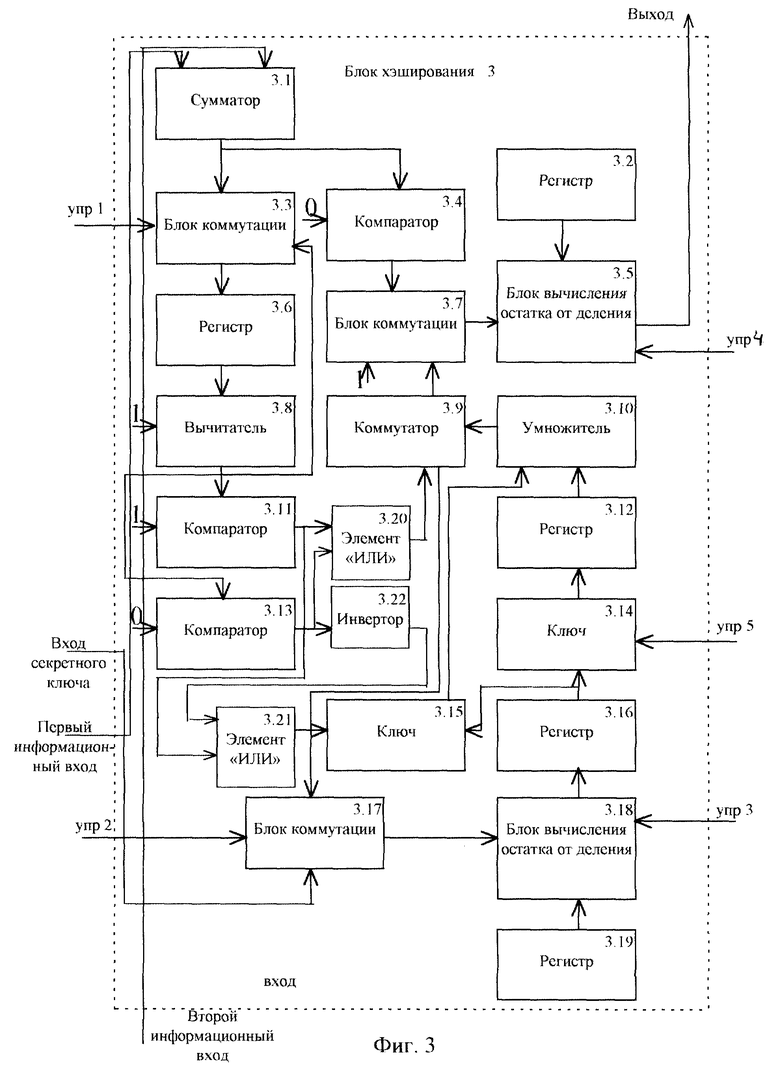

- на фиг. 3 - структурная схема блока хэширования 3;

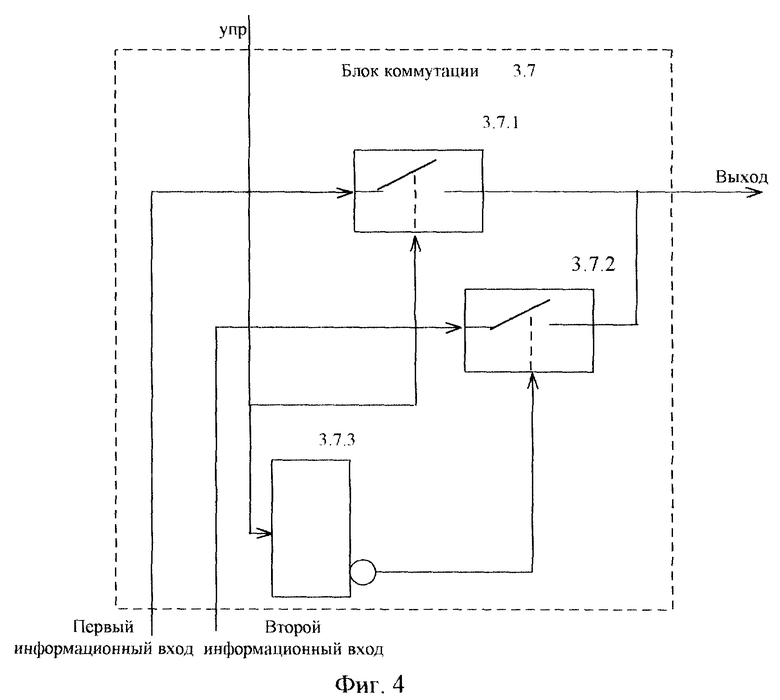

- на фиг. 4 - структурная схема блока коммутации 3.7;

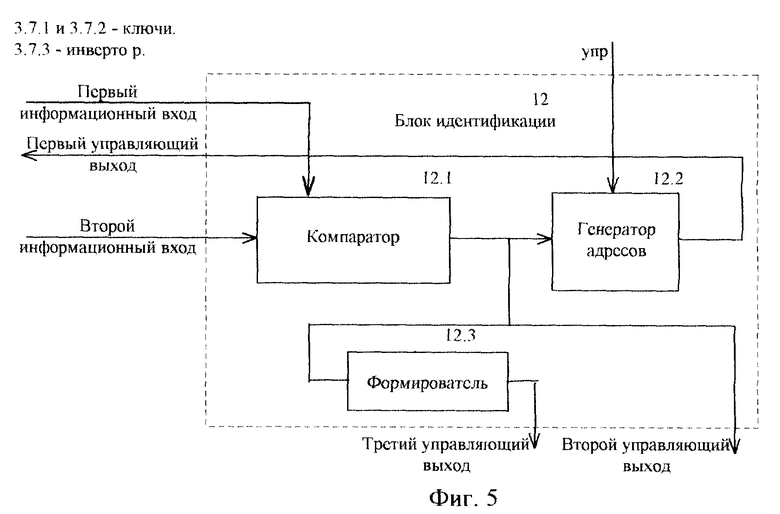

- на фиг. 5 - структурная схема блока идентификации 12;

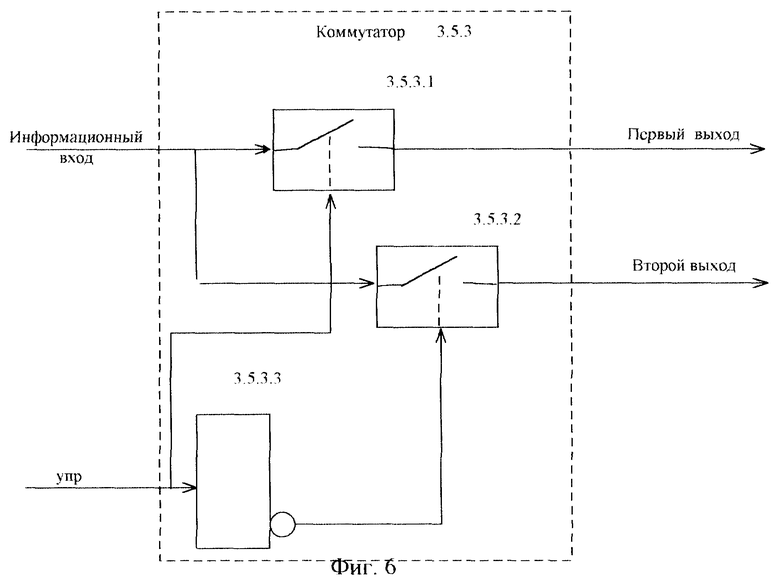

- на фиг. 6 - структурная схема коммутатора 3.5.3;

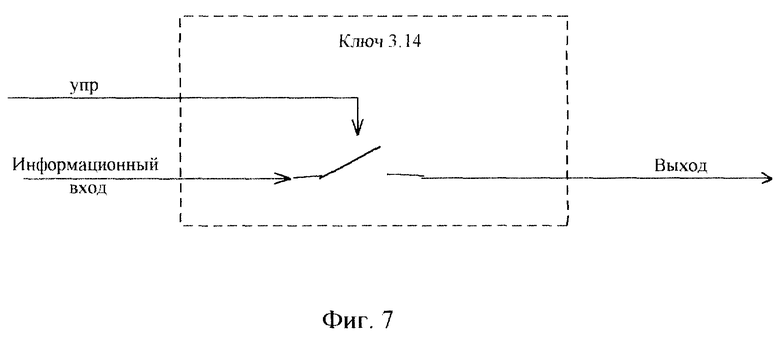

- на фиг. 7 - структурная схема ключа 3.14;

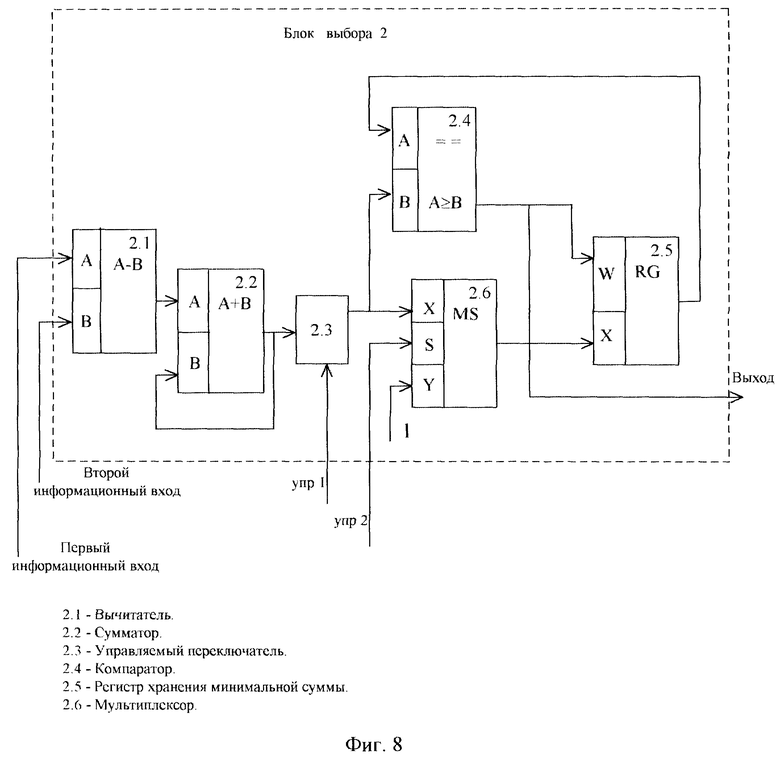

- на фиг. 8 - структурная схема блока выбора 2;

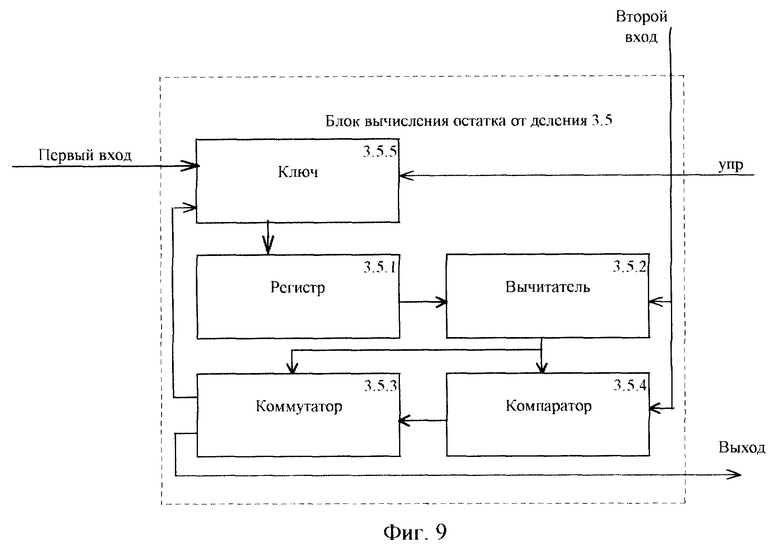

- на фиг. 9 - структурная схема блока вычисления остатка от деления 3.5;

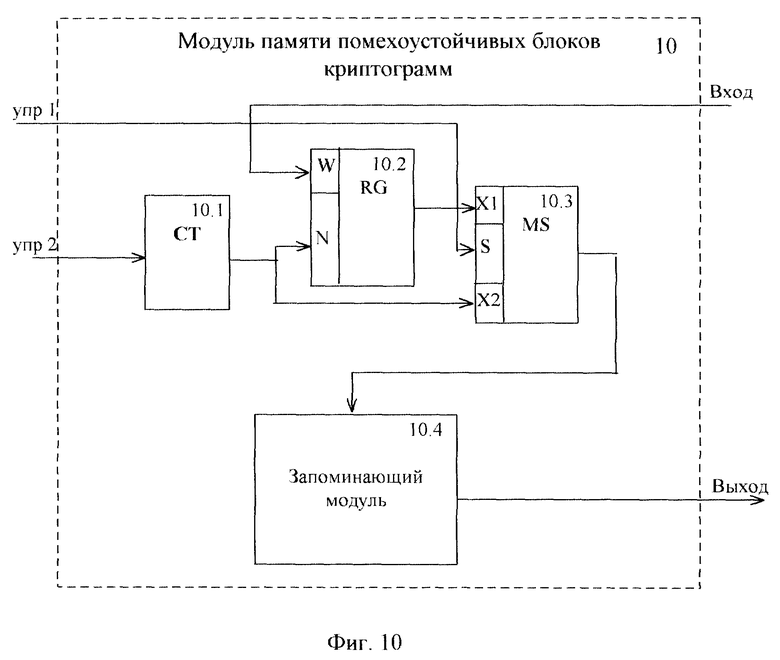

- на фиг. 10 - структурная схема модуля памяти помехоустойчивых блоков криптограмм 10;

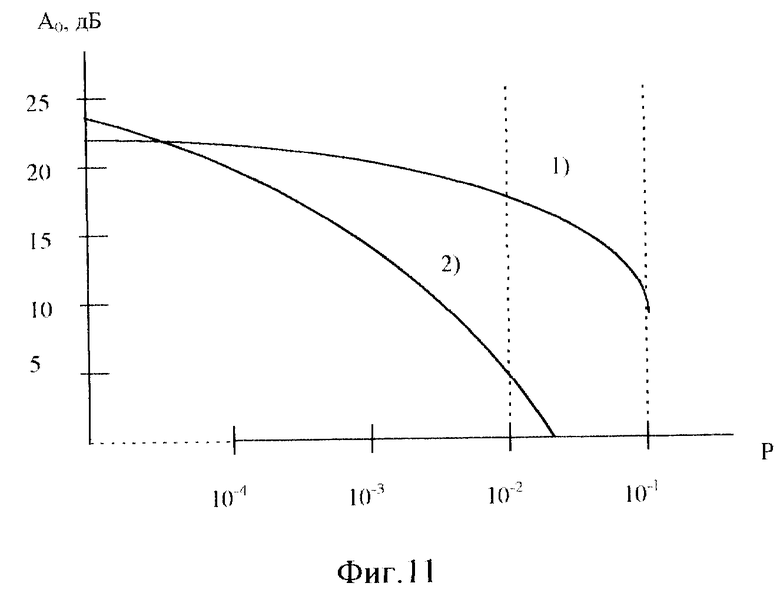

- на фиг. 11 - графики, показывающие эффект заявленного способа;

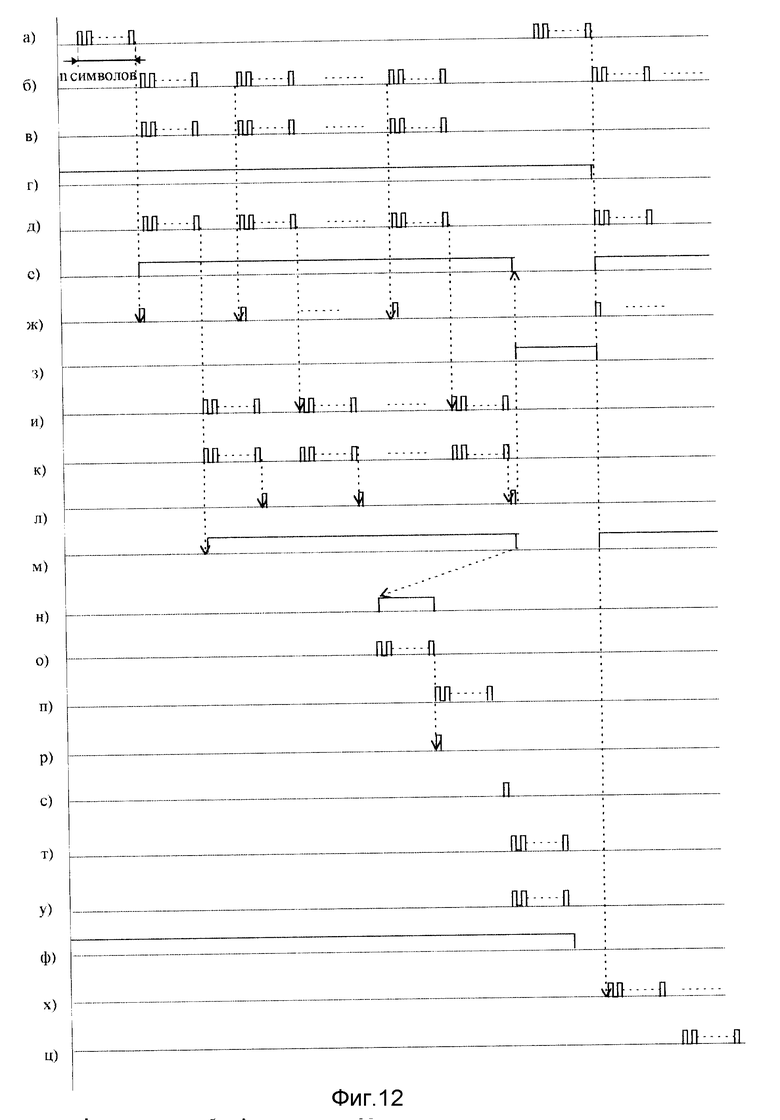

- на фиг. 12 - временные диаграммы, поясняющие суть работы предлагаемого устройства шифрования/дешифрования сообщений хэширующей функцией;

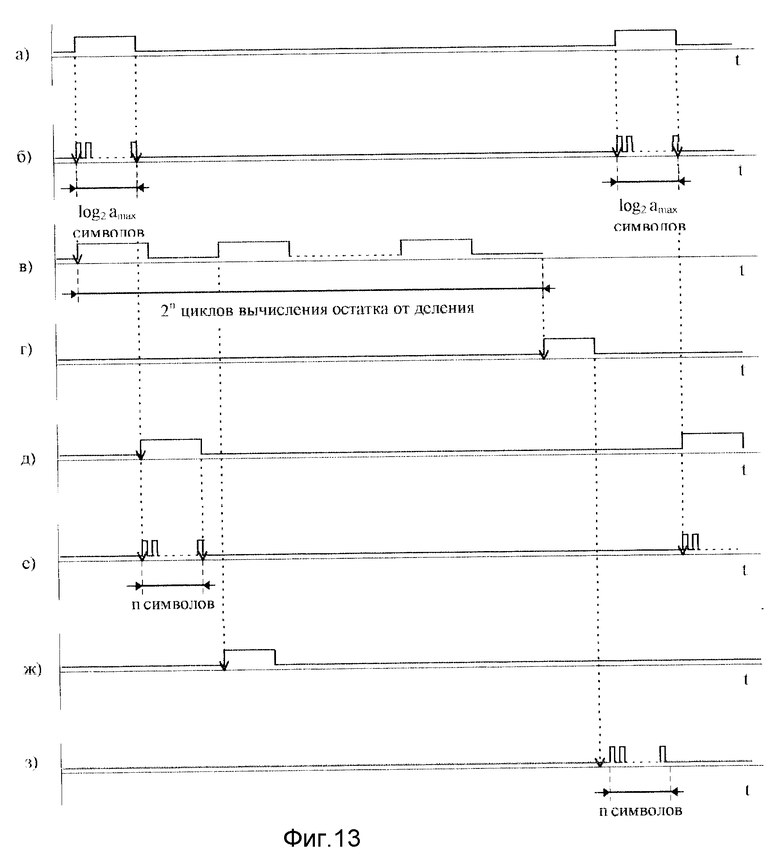

- на фиг. 13 - временные диаграммы, поясняющие суть работы блока хэширования 3 предлагаемого устройства шифрования/дешифрования сообщений хэширующей функцией.

Реализация заявленного способа заключается в следующем. Для повышения достоверности передачи зашифрованных сообщений по каналам связи с помехами используют их помехоустойчивое кодирование избыточным кодом, позволяющее обнаруживать ошибки передачи в принятых сообщениях. Однако это требует передачи по каналу дополнительной избыточной информации, сформированной из зашифрованных сообщений по правилу кодирования помехоустойчивым кодом, что требует увеличения пропускной способности канала связи. С другой стороны, зашифрованная передача по дискретным каналам избыточных сообщений, таких как речевые, звуковые, телевизионные факсимильные и т.п., вид которых показан на фиг. 2(а), требует их предварительного преобразования к цифровому виду. Известные способы аналого-цифрового преобразования не обеспечивают полного удаления избыточности перечисленных выше сигналов, поэтому цифровые речевые, звуковые, телевизионные, факсимильные и подобные им сообщения имеют существенную остаточную избыточность, что описано, например, в книге "Сжатие и поиск информации ". - М.: Радио и связь, 1988, стр.77. Вид цифровых речевых, звуковых, телевизионных, факсимильных и подобных им сообщений, дискретизированных с частотой дискретизации F = 1/Т и квантованных на q уровней (q>2) показан на фиг. 2(б).

Однако известные способы шифрования/дешифрования сообщений не учитывают наличие в сообщениях этой избыточности и в процессе шифрования формируют безизбыточные криптограммы. По виду принятой из канала связи криптограммы невозможно определить, искажена ли она ошибкой передачи. Поэтому для передачи зашифрованных избыточных сообщений по каналам связи с ошибками существенные преимущества имеет использование помехоустойчивых криптограмм, обеспечивающих без внесения дополнительной избыточности обнаружение факта их искажения при передаче.

В заявленном способе для обеспечения шифрования/дешифрования сообщений хэширующей функцией с обнаружением ошибок передачи и повторной передачи зашифрованных сообщений, принятых с ошибкой, что повысит достоверность их передачи, реализуется следующая последовательность действий.

Предварительное формирование функции хэширования, секретного ключа и стартового блока двоичных символов заключается в следующем. В качестве функции хэширования используют преобразование хэшируемого блока двоичных символов в хэшированный блок q-ичных символов, удовлетворяющее следующим требованиям.

1) Каждый q-ичный символ хэшированного блока зависит от каждого двоичного символа хэшируемого блока, каждого двоичного символа секретного ключа и каждого двоичного символа стартового вектора, то есть изменение любого двоичного символа хэшируемого блока, секретного ключа или стартового блока вызывает изменение нескольких q-ичных символов хэшированного блока.

2) Зная полное описание фикции хэширования, значение стартового блока двоичных символов и произвольно большое число значений хэшируемых блоков и соответствующих им значений хэшированных блоков, третьи лица (противник) не способны вычислить использующийся в процессе хэширования секретный ключ.

3) Зная полное описание функции хэширования а значение стартового блока двоичных символов, третьи лица не способны сформировать хэшированный блок для произвольного хэшируемого блока, не зная секретный ключ.

Известные способы предварительного формирования функции хэширования описаны, например, в книге М.Д. Смид, Д.К. Бранстел "Стандарт шифрования данных: Прошлое и будущее". ТИИЭР, 1988, - т. 76, N 5, стр. 49. Они заключаются в формирования функции хэширования по секретному ключу, используя алгоритм шифрования данных DES в режиме обратной связи по шифртексту или в режиме обратной связи по выходу. Однако данные способы предварительного формирования функции хэширования предназначены для хэширования блоков двоичных символов длиной только 64 бита, что существенно сужает область их использования. Кроме того, известные способы формирования функции хэширования порождают хэшированные блоки двоичных символов, а не q-ичных символов, что требуется в заявляемом изобретении. Поэтому для хэширования блоков двоичных символов произвольной длины с образованием хэшированных блоков q-ичных символов предлагается функция хэширования следующего вида. Случайным образом выбирают алгебраическое поле Галуа GF(p), состоящее из p элементов. В выбранном поле Галуа отыскивают один из примитивных элементов а, способный породить в произвольном порядке все значения элементов этого поля, если последовательно возводить его в целые положительные степени от 1 до р-1, вычисляя результат по модулю p;

a1 (mod р)= a, а2 (mod р), а3 (mod р), аi (mod р),.., ap-1 mod р),

где аi (mod р) принадлежит полю GF(p) для всех i = 1,...р-1.

В качестве секретного ключа предлагается использовать один из примитивных элементов поля Галуа. Предварительно сформированная функция хэширования математически описывается в виде:

ei,k + e* j-1,k

yi,j,k=(a(modp))(mod q), i= 1,2,...,N, j= 1,2.....,

где yi,j,k - k-й q-ичный символ хэшированного помехоустойчивого блока криптограммы Yi,j, полученного хэшированием i-го помехоустойчивого блока криптограммы Ei шифрования j-го информационного блока Мj q-ичных символов ( i=1,2,...,N, j= 1,2,..., k=1,2,..,n);

ei,k - k-й двоичный символ предварительно выбранного i-го помехоустойчивого блока криптограммы Ei (i= 1,2.,..,N);

e* j-1,k - k-й двоичный символ помехоустойчивого блока криптограммы, соответствующего выбранному на предыдущем шаге хэшированному помехоустойчивому блоку криптограммы:

q - простое число, q<<p, q>2.

Для шифрования/дешифрования первого информационного блока M1 q-ичных символов в качестве значения помехоустойчивого блока криптограммы, соответствующего выбранному на предыдущем шаге хэшированному помехоустойчивому блоку криптограммы, используют значение стартового блока двоичных символов E0,

E* j-1 = E0, если j = 1

Вычисление результата возведения в степень по модулю простого числа q обеспечивает одинаковую вероятность того, что вычислено значение yi,j,k примет любое значение от 0 до q-1 с одинаковой вероятностью 1/q, что доказывается в книге: Д. Кнут "Искусство программирования на ЭВМ". - М.: Мир, 1978, т.3, стр.604.

Выбор значения секретного ключа осуществляют случайным выбором одного из примитивных элементов выбранного поля Галуа GF(p). Число примитивных элементов поля оценивается значением функции Эйлера от значения функции Эйлера и при p > 1020 составляет вычислительно непереборное для третьих лиц (противника) число возможных значений секретного ключа. Способ поиска примитивных элементов поля Галуа описан, например, в книге: ИМ. Виноградов "Основы теории чисел". - М.: Наука, Главная редакция физико-математической литературы, 1981, стр.89.

Выбор значения стартового блока двоичных символов осуществляют случайным выбором блока двоичных символов, описанным, например, в книге: Д. Кнут "Искусство программирования на ЭВМ". - М.: Мир, 1977, т.2, стр.22. Вид стартового блока двоичных символов представлен на фиг. 2(д).

Передачу между отправителем и получателем сообщений секретного ключа и стартового блока двоичных символов осуществляют до начала передачи отправителем сообщений зашифрованных сообщений. При этом значение секретного ключа должно быть неизвестным для третьих лиц (противника). Для этого секретный ключ и стартовый блок двоичных символов могут быть переданы курьером с соблюдением необходимых мер предосторожности. Известные способы передачи между отправителем и получателем сообщений секретного ключа и блоков двоичных символов описаны, например, в книге: Дж. Месси "Введение в современную криптологию". ТИИЭР, 1988,-т. 76, N 5, стр. 24.

Если длина сообщения превышает длину информационного блока q-ичных символов, то сообщение разбивают на последовательно передаваемые информационные блоки q-ичных символов фиксированной длины n. Известные способы разбиения сообщения на последовательно передаваемые информационные блоки q-ичныл символов фиксированной длины описаны, например, в книге: В.И. Васильев, А.П. Буркин, В. А. Свириденко "Системы связи". - М.: Высшая школа, 1987,- стр. 208.

Предварительное формирование N помехоустойчивых блоков криптограмм заключается в следующем. Произвольный двоичный помехоустойчивый код описывается порождающей матрицей G размерностью r строк на n столбцов, где n > r. Значение n является длиной помехоустойчивых блоков кода, r - числом информационных бит в помехоустойчивых блоках кода. Формирование N помехоустойчивых блоков криптограмм Ei выполняется перемножением каждого из N блоков двоичных символов Ii длиной r бит, где i=1,2....,N. на порождающую матрицу G двоичного помехоустойчивого кода по правилу:

E = Ii G.

Известные способы формирования помехоустойчивых блоков описаны, например, в книге У. Питерсон, Э. Уэлдон " Коды, исправляющие ошибки". - М.: Мир, 1976, стр. 252. Количество N предварительно сформированных помехоустойчивых блоков криптограмм выбирают в зависимости от требуемой точности восстановления информационных блоков q-ичных символов получателем сообщений, как показано, например, в книге: Дж. Макхоул. С. Рукос, Г. Гиш "Векторное квантование при кодировании речи". ТИИЭР, 1985, - т. 73, N 11, стр. 23. Вид N предварительно сформированных помехоустойчивых блоков криптограмм представлен на фиг. 2(в).

Хэширование помехоустойчивых блоков криптограмм по функции хэширования, секретному ключу и стартовому блоку двоичных символов может быть выполнено, например, используя предложенную функцию хэширования на основе возведения в степень примитивного элемента поля Галуа по модулям простых чисел p и g:

ei,k + e0,k

yi,1,k = (а(mod р))(mod q), i= 1,2,...,N, k = 1, 2,...n, q<<p,

где yi,l,k - k-й q-ичный символ хэшированного помехоустойчивого блока криптограммы Yi,1 для шифрования первого информационного блока q-ичных символов М1 (i= 1,2...,N, k= 1,2,..,n );

ei,k - k-й двоичный символ помехоустойчивого блока криптограммы Ei (i= 1,2...,N);

e0,k - k-й двоичный символ стартового блока двоичных символов E0.

В результате хэширования N помехоустойчивых блоков криптограмм формируют N хэшированных помехоустойчивых блоков криптограмм, каждый из которых состоит из n q-ичных символов. Вид N хэшированных помехоустойчивых блоков криптограмм представлен на фиг. 2.(г).

Каждый i-й, где i=1,..,N, хэшированный помехоустойчивый блок криптограммы сравнивают с первым информационным блоком q-ичных символов. Известные способы сравнения блоков q-ичных символов описаны, например, в книге: У. Питерсон. Э. Уэлдон " Коды, исправляющие ошибки"', - М.: Мир, 1976, стр.52. Для сравнения используют метрику Ли, в соответствии с которой для сравнения каждого i-го хэшированного помехоустойчивого блока криптограммы с первым информационным блоком q-ичных символов из значения каждого q-ичного отсчета i-го хэшированного помехоустойчивого блока криптограммы вычитают соответствующее ему значение q-ичного отсчета первого информационного блока q-ичных символов и для каждого i-го хэшированного помехоустойчивого блока криптограммы абсолютные значения полученных разностей суммируют.

Среди N хэшированных помехоустойчивых блоков криптограмм выбирают наиболее близкий к первому информационному блоку q-ичных символов, соответствующий минимальной сумме подученных разностей. Известные способы выбора минимального значения среди нескольких значений описаны, например, в книге: Д. Кнут "Искусство программирования на ЭВМ". - М.: Мир, 1978, т.3, стр.219.

Передают по прямому каналу связи получателю сообщений помехоустойчивый блок криптограммы, соответствующий выбранному хэшированному помехоустойчивому блоку криптограммы. Способы двоичных блоков по каналу связи известны и описаны, например, а книге: А.Г. Зюко, Д.Д. Кловский, М.Б. Назаров. Л.М. Финк "Теория передачи сигналов". - М.: Радио и связь, 1986, стр. 11.

Принятый помехоустойчивый блок криптограммы идентифицируют с N помехоустойчивыми блоками криптограмм. Известные способы идентификации описаны, например, в книге: У. Питерсон, Э. Уэлдон "Коды, исправляющие ошибки". -М.: Мир, 1976, стр. 15. Для идентификации принятого помехоустойчивого блока криптограммы с N помехоустойчивыми блоками криптограмм его последовательно сравнивают с каждый из N помехоустойчивых блоков криптограмм. В случае, если не найдется ни одного помехоустойчивого блока криптограммы, совпадающего с принятым помехоустойчивым блоком криптограммы, то принятый помехоустойчивый блок криптограммы считают неидентифицированным.

Принятый неидентифицированный помехоустойчивый блок криптограммы стирают и по обратному каналу связи передают управляющий сигнал для повторной передачи получателю сообщений помехоустойчивого блока криптограммы, соответствующего выбранному хэшированному помехоустойчивому блоку криптограммы. Известные способы стирания принятых помехоустойчивых блоков описаны, например, в книге: У, Питерсон, Э. Уэлдон "Коды, исправляющие ошибки". -М.: Мир, 1976, стр. 17. Известные способы передачи по обратному каналу связи отправляющих сигналов для повторной передачи получателю сообщений помехоустойчивого блока описаны, например, в книге: У. Питерсон, Э. Уэддон " Коды, исправляющие ошибки", -М.: Мир, 1976, стр. 17,

Принятый идентифицированный помехоустойчивый блок хэшируют по функции хэширования, секретному ключу и стартовому блоку двоичных символов способом, идентичным хэшированию отправителем сообщений помехоустойчивых блоков криптограмм по функции хэширования, секретному ключу и стартовому блоку двоичных символов, используя предложенную функцию хэширования на основе возведения в степень примитивного элемента поля Галуа по модулям простых чисел p и g:

e'1,k + e0,k

m^1,k=(a(modp))(modq), k = 1, 2,...,n, g<<p,

где m^1,k - k-й q-ичный символ первого восстановленного информационного блока М^1 q-ичных символов;

e1,k' - k-й двоичный символ первого принятого идентифицированного помехоустойчивого блока криптограммы E1';

e0,k - k-й двоичный символ стартового блока двоичных символов E0.

В результате восстанавливают на приемной стороне аппроксимацию первого информационного блока q-ичных символов.

Для шифрования второго и последующих информационных блоков q-ичных символов повторно хэшируют N помехоустойчивых блоков криптограмм по функции хэширования, секретному ключу и помехоустойчивому блоку криптограммы, соответствующему выбранному на предыдущем шаге хэшированному помехоустойчивому блоку криптограммы, используя предложенную функцию хэширования на основе возведения в степень примитивного элемента поля Галуа по модулям простых чисел p и g:

ei,k + e* j-1,k

yi,j,k = (a(mod p))(mod q), i=1,2,...,N, j=1,2,..., k=1,2,..., n, q<<p.

где yi,j,k - k-й q-ичный символ хэшированного помехоустойчивого блока криптограммы Yi,j для шифрования j-го информационного блока q-ичных символов (i= 1,2,...,N, j= 1,2,..., k= 1,2,...,n);

ei,k - k-й двоичный символ помехоустойчивого блока криптограммы Ei (i= 1,2,...,N);

e* j-1,k - k-й двоичный символ помехоустойчивого блока криптограммы E* j-1, соответствующий выбранному на предыдущем шаге хэшированному помехоустойчивого блока криптограммы Y* j-1.

Каждый i-й, где i=1,2,...,N, хэшированный помехоустойчивый блок криптограммы сравнивают с очередным информационным блоком q-ичных символов. Известные способы сравнения блоков q-ичных символов описаны, например, в книге: У. Питерсон, Э. Уэлдон "Коды, исправляющие ошибки'". - М.: Мир, 1976, стр. 52. Для сравнения используют метрику Ли, в соответствии с которой для сравнения каждого i-го хэшированного помехоустойчивого блока криптограммы с очередным информационным блоком q-ичных символов из значения каждого q-ичного отсчета i-го хэшированного помехоустойчивого блока криптограммы вычитают соответствующее ему значение q-ичного отсчета очередного информационного блока q-ичных символов и для каждого i-го хэшированного помехоустойчивого блока криптограммы абсолютные значения порченных разностей суммируют.

Среди N хэшированных помехоустойчивых блоков криптограмм выбирают наиболее близкий к очередному информационному блоку q-ичных символов, соответствующий минимальной сумме полученных разностей. Известные способы выбора минимального значения среди нескольких значений описаны, например, в книге: Д. Кнут "Искусство программирования на ЭВМ". - М.: Мир, 1978, т.3, стр.219.

По прямому каналу связи передают получателю сообщений помехоустойчивый блок криптограммы, соответствующий выбранному хэши рованному помехоустойчивому блоку криптограммы. Способы передачи двоичного блока по каналу связи известны и описаны, например, в книге А.Г. Зюко, Д.Д. Кловский М.Б. Назаров, Л.М. Финк "Теория передачи сигналов". - М.: Радио и связь, 1986, стр. 11.

Принятый помехоустойчивый блок криптограммы идентифицируют с N помехоустойчивыми блоками криптограмм. Известные способы идентификации описаны, например, в книге: У. Питерсон, Э. Уэлдон "Коды, исправляющие ошибки". -М.: Мир, 1976, стр. 15. Для идентификации принятого помехоустойчивого блока криптограммы с N помехоустойчивыми блоками криптограмм его последовательно сравнивают с каждым из N помехоустойчивых блоков криптограмм. В случае, если не найдется ни одного помехоустойчивого блока криптограммы, совпадающего с принятым помехоустойчивым блоком криптограммы, то принятый помехоустойчивый блок криптограммы считают неидентифицированным.

Принятый неидентифицированным помехоустойчивый блок криптограммы стирают и по обратному каналу связи передают управляющий сигнал повторной передачи получателю сообщений помехоустойчивого блока криптограммы, соответствующему выбранному хэшированному помехоустойчивому блоку криптограммы. Известные способы стирания принятых помехоустойчивых блоков описаны, например, в книге: У. Питерсон. Э. Уэлдон " Коды, исправляющие ошибки". -М.: Мир, 1976, стр. 17. Известные способы передачи по обратному каналу связи управляющих сигналов для повторной передачи получателю сообщений помехоустойчивого блока описаны, например, в книге; У. Питерсон, Э. Узлдон "Коды, исправляющие ошибки". -М.: Мир. 1976, стр. 17.

Принятый идентифицированный помехоустойчивый блок криптограммы хэшируют по функции хэширования, секретному ключу и предыдущему принятому идентифицированному помехоустойчивому блоку криптограммы способом, идентичным хэшированию отправителем сообщений помехоустойчивых блоков криптограмм по функции хэширования, секретному ключу и помехоустойчивому блоку криптограммы, соответствующего выбранному на предыдущем шаге хэшированному помехоустойчивому блоку криптограммы, используя предложенную функцию хэширования на основе возведения в степень примитивного элемента поля Галуа по модулям простых чисел p и g:

e'j,k + e'j-1,k

m^j,k = (a(mod p))(mod q), k = 1,2...,n, q<<p.

где m^ j,k - k-й q-ичный символ j-ro восстановленного информационного блока М^j q-ичных символов;

e'j,k - k-й двоичный символ j-ro принятого идентифицированного помехоустойчивого блока криптограммы E'j;

e'j-1,k - k-й двоичный символ предыдущего принятого идентифицированного помехоустойчивого блока криптограммы E'j-1.

В результате этого восстанавливают на приемной стороне аппроксимацию очередного информационного блока q-ичных символов.

Действия по передаче по прямому каналу связи получателю сообщений помехоустойчивого блока криптограммы, соответствующего выбранному хэшированному помехоустойчивому блоку криптограммы, и действия по передаче по обратному каналу связи управляющего сигнала для повторной передачи получателю сообщений помехоустойчивого блока криптограммы, соответствующего выбранному хэшированному помехоустойчивому блоку криптограммы, засинхронизированы. Способы синхронизации описаны, например, в книге E. М, Мартынов "Синхронизация в системах передачи дискретных сообщений". -М.: Связь, 1972, стр. 186.

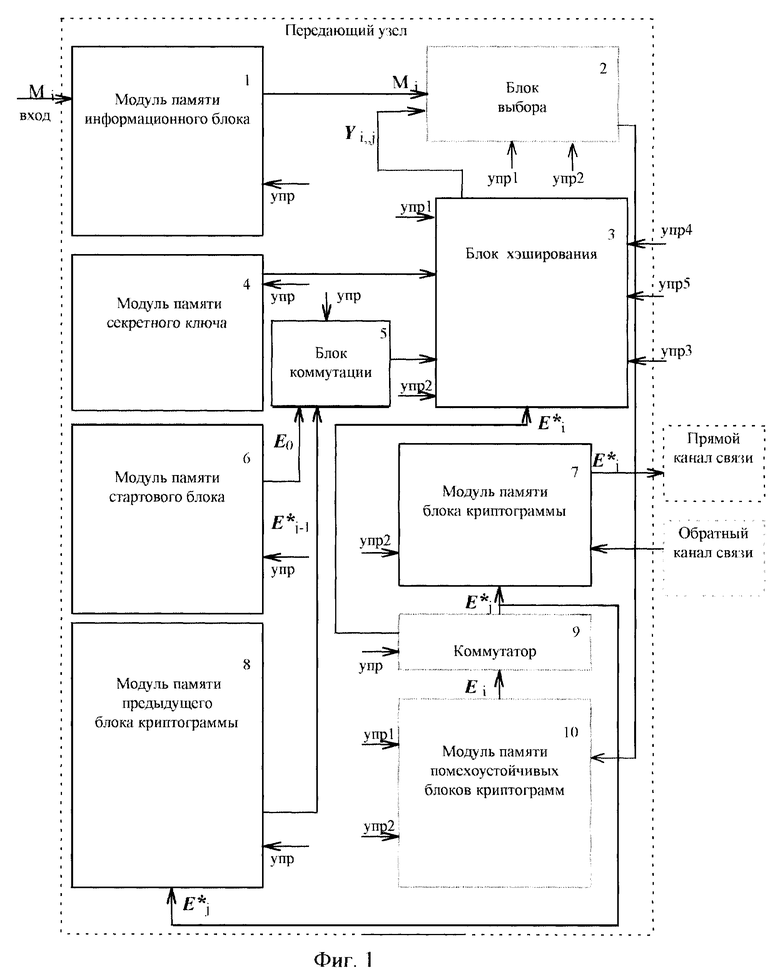

В аналитической форме данные действия можно записать следующим образом.

Mj =(mj,1, mj,2,...,mj,k,...,mj,n), k=1,2,...,n,

E0 =(e0,1, e0,2,...,e0,k,...,e0,n), k=1,2,...,n,

Ei =(ei,1, ei,2,...,ei,k,...,ei,n), k=1,2,...,n,

Yi,j=(Yi,j,1, Yi,j,2,...,Yi,j,k,...,Yi,j,n), k=1,2,...,n,

E* j = (e* j,1, e* j,2,...,e* j,k,...,e* j,n), k=1,2,...,n,

E* j-1=(e* j-1,1, e* j-1,2,...,e* j-1,k,...,e* j-1,n), k=1,2,...,n,

E^j=(e^j,1, e^j,2,...,e^j,k,...,e^j,n), k=1,2,...,n,

E'j =(e'j,1, e'j,2,...,e'j,k,...,e'j,n), k=1,2,...,n,

E'j-1 =(e'j-1,1, e'j-1,2,...,e'j-1,k,...,e'j-1,n), k=1,2,...,n,

M^j =(m^j,1, m^j,2,...,m^j,k,...,m^j,n), k=1,2,...,n,

ei,k + e* j-1,k

Yi,j,k = (a(mod p))(mod q), i=1,2,...,N, j=1,2,..., k=1,2,..n, q<<p,

e* j-1,k = e0,k, если j=1,

e'j,k + e'j-1,k

m^j,k = (a(mod p))(mod q), j=1,2,..., k=1,2,..,n, q<<p,

e'j-1,k = e0,k, если j=1,

где Yi,j - i-й хэшированный помехоустойчивый блок криптограммы для шифрования j-го информационного блока Мj q-ичных символов, состоящий из n q-ичных символов yi,j,k;;

Y* j - выбранный хэшированный помехоустойчивый блок криптограммы для шифрования j-го информационного блока Мj q- ичных символов, состоящий из n q-ичных символов y* j,k;

E0 - стартовый блок двоичных символов, состоящий из n двоичных символов e0,k;

Ei - i-й помехоустойчивый блок криптограммы, состоящий из n двоичных символов ei,k;

E* j - помехоустойчивый блок криптограммы, соответствующий выбранному хэшированному помехоустойчивому блоку криптограммы, состоящий из n двоичных символов e* j,k;

E* j-1 - помехоустойчивый блок криптограммы, соответствующий выбранному на предыдущем шаге хэшированному помехоустойчивому блоку криптограммы, состоящий из n двоичных символов e* j-1,k;

E^ j - j-й принятый помехоустойчивый блок криптограммы, состоящий из n двоичных символов e^j,k;

E'j - j-й принятый идентифицированный помехоустойчивый блок криптограммы, состоящий из n двоичных символов e'j,k;

E'j-1 - предыдущий принятый идентифицированный помехоустойчивый блок криптограммы, состоящий из n двоичных e'j-1,k;

M^j - j-й восстановленный информационный блок q-ичных символов, состоящий из n q-ичных символов m^j,k.

Проверка теоретических предпосылок заявленного способа шифрования/дешифрования сообщений хэширующей функцией проверялась путем его машинного моделирования на ПЭВМ. В результате моделирования шифрования/дешифрования избыточных сообщений, передаваемых по каналу связи с помехами, были получены результаты, представленные в виде графиков на фиг. 11. На фиг. 11 показаны зависимости отношения сигнал/шум Ao дешифрованного избыточного сигнала от вероятности ошибки p в двоичном симметричном канале без памяти. График 1) построен для случая использования заявленного способа шифрования/дешифрования сообщений хэширующей функцией, а график 2) - для случая использования способа-прототипа. Отношение сигнал/шум Ao дешифрованного избыточного сигнала определялось по формуле:

где mj,k - k-й q-ичный символ j-го информационного блока Mj q-ичных символов;

m^ j,k - k-й q-ичный символ j-го восстановленного информационного блока M^j q-ичных символов;

Q - количество шифрованных информационных блоков q-ичных сигналов.

В качестве избыточного сигнала использовался речевой сигнал, квантованный с использованием 8-разрядного кодека импульсно-кодовой модуляции и имеющий 253 различных значений амплитуды (q=253).

Проведенные экспериментальные исследования подтверждают, что использование предлагаемого способа шифрования/дешифрования сообщений хэширующей функцией обеспечивается повышение достоверности передачи зашифрованных избыточных сообщений по каналам с помехами благодаря обнаружению ошибок передачи и повторной передачи зашифрованных избыточных сообщений, принятых с ошибкой.

Устройство шифрования/дешифрования сообщений хэширующей функцией, показанное на фиг. 2, состоит из передающего и приемного узлов. Передающий узел включает модуль памяти информационного блока 1, блок выбора 2, блок хэширования 3, модуль памяти секретного ключа 4, блок коммутации 5, модуль памяти стартового блока 6, модуль памяти блока криптограммы 7, модуль памяти предыдущего блока криптограммы 8, коммутатор 9 и модуль памяти помехоустойчивых блоков криптограмм 10. Приемный узел включает модуль памяти принятого блока криптограммы 11, блок идентификации 12, модуль памяти помехоустойчивых блоков криптограмм 13, ключ 14, модуль памяти секретного ключа 15, блок хэширования 16, блок коммутации 17, модуль памяти предыдущего принятого блока криптограммы 18 и модуль памяти стартового блока 19. Вход модуля памяти информационного блока 1 является входом устройства. Выход модуля памяти информационного блока 1 соединен с первым информационным входом блока выбора 2, выход которого подключен к информационному входу модуля памяти помехоустойчивых блоков криптограмм 10. Второй информационный вход блока выбора 2 соединен с выходом блока хэширования 3. Вход секретного ключа блока хэширования 3 соединен с выходом модуля памяти секретного ключа, первый информационный вход хэширования соединен с выходом блока коммутации 5, первый информационный вход которого соединен с выходом модуля памяти стартового блока 6, второй информационный вход блока коммутации 5 соединен с выходом модуля памяти предыдущего блока криптограммы 8. Первый выход коммутатора 9 подключен к второму информационному входу блока хэширования, второй выход коммутатора соединен со входом модуля памяти выбранного блока криптограммы 7 и параллельно со входом модуля памяти предыдущего выбранного блока криптограммы 8, вход коммутатора 9 соединен с выходом модуля памяти помехоустойчивых блоков криптограмм 10. Выход модуля памяти помехоустойчивого блока криптограммы 7 соединен со входом прямого канала связи, а первый управляющий вход модуля памяти помехоустойчивого блока криптограммы 7 соединен с выходом обратного канала связи. Выход прямого канала связи соединен с входом модуля памяти принятого блока криптограммы 11, первый выход которого соединен с первым входом блока идентификации принятого блока криптограммы с помехоустойчивыми блоками криптограмм 12, выход которого подключен к информационному входу ключа 14. Второй вход блока идентификации 12 подключен к выходу модуля памяти помехоустойчивых блоков криптограмм 13. Первый управляющий выход блока идентификации 12 соединен со входом модуля памяти помехоустойчивых блоков криптограмм 13, второй управляющий выход соединен с управляющим входом ключа 14 и параллельно со входом обратного канала связи. Выход ключа 14 соединен с вторым информационным входом блока хэширования 16 и параллельно со входом блока памяти предыдущего принятого блока криптограммы 18. Вход секретного ключа блока хэширования 16 соединен с выходом модуля памяти секретного ключа 15, первый информационный вход блока хэширования 16 соединен с выходом блока коммутации 17, первый вход которого подключен к выходу модуля памяти предыдущего принятого блока криптограммы 18, а второй - к выходу модуля памяти стартового блока 19. Выход блока хэширования является выходом устройства.

Модуль памяти информационного блока 1, блок выбора 2, блок хэширования 3, модуль памяти секретного ключа 4, блок коммутации 5, модуль памяти стартового блока 6, модуль памяти выбранного блока криптограммы 7, модуль памяти предыдущего выбранного блока криптограммы 8, коммутатор 9, модуль памяти принятого блока криптограммы 11, блок идентификации 12, блок коммутации 14, модуль памяти секретного ключа 15, блок хэширования 16, блок коммутации 17, модуль памяти предыдущего принятого блока криптограммы 18, модуль памяти стартового блока 19 снабжены входами управляющих сигналов, формируемых блоком управления, не показанном на чертежах.

Модуль памяти информационного блока 1 предназначен для разбиения сообщения на информационные блоки q-ичных символов длиной n символов, записи значения первого, а затем очередного информационного блока q-ичных символов, хранения и его считывания на первый информационный вход блока выбора 2 для сравнения с значением каждого i-го, где i=1,2...,N. хэшированного помехоустойчивого криптограммы. В качестве модуля памяти информационного блока 1 может быть использовано статическое оперативное запоминающее устройство (ОЗУ), схема построения которого известна и приведена, например, в книге: В. А. Батушев, В. Н. Вениаминов и др. "Микросхемы и их применение: Справочное пособие". - М.: Радио и связь, 1983, стр. 175, рис. 5.12. Модуль памяти информационного блока 1 может быть реализован, например, на микросхеме памяти К 537РУ8 (см. В.И. Корнейчук, В.П. Тарасенко "Вычислительные устройства на микросхемах: Справочник."-К.: Техника, 1988, стр. 85-87).

Блок выбора 2, показанный на фиг. 8, предназначен для сравнения значения каждого i-го, где i=1,2,..,N, хэшированного помехоустойчивого блока криптограммы с значением первого, а затем очередного информационного блока q-ичных символов и для выбора среди N хэшированных помехоустойчивых блоков криптограммы наиболее близкого к первому, а затем очередному информационному блоку q-ичных символов. Блок выбора 2 состоит из вычитателя 2.1, сумматора 2.2, управляемого переключателя 2.3, компаратора 2.4, регистра хранения минимальной суммы 2.5) и мультиплексора 2.6.

Первый вход вычитателя 2.1 является вторым информационным входом блока выбора 2. Второй вход (вход В) вычитателя 2.1 является первым информационным входом блока выбора 2. Выход вычитателя 2.1 соединен с первым входом (входом A) сумматора 2.2. Выход сумматора 2.2 соединен в параллель с информационным входом управляемого переключателя 2.3 и своим же вторым входом (входом В). На управляющий вход управляемого переключателя 2,3 подаются сигналы управления с выхода блока управления, не показанного на чертежах. Управляющий вход управляемого переключателя 2.3 является первым управляющим входом блока выбора 2. Информационный выход управляемого переключателя 2,3 в параллель соединен со вторым входом (вход В) компаратора 2.4 и первым информационным входом (вход X) мультиплексора 2.6. На второй информационный вход (вход Y) мультиплексора 2.6 постоянно подаются информационные сигналы единичного значения "1". На управляющий вход (вход S) мультиплексора 2.6 подаются сигналы управления с выхода блока управления, не показанного на чертежах. Управляющий вход мультиплексора 2.6 является управляющим входом блока выбора 2, Выход мультиплексора 2,6 соединен с информационным входом (входом X) регистра хранения минимальной суммы 2.5. Выход регистра хранения минимальной суммы 2.5 подключен к первому входу (входу A) компаратора 2.4, выход которого соединен с управляющим входом (входом W) регистра хранения минимальной суммы 2.5, а также является выходом блока выбора 2.

Вычитатель 2.1 предназначен для определения разности значениями q-ичных символов хэшированного помехоустойчивого блока криптограммы и соответствующих им q-ичных символов информационного блока q-ичных символов. Вычитатель 2.1 представляет собой сумматор, работающий в режиме вычитания. Схема вычитателя известна, приведена, например, в книге: П. П. Мальцев и др. "Цифровые интегральные микросхемы": Справочник. -М.: Радио и связь, 1994, стр. 76, и он может быть, например, реализован на микросхеме K555ИМ7 (см. В. Л. Шило "Популярные цифровые микросхемы". - М.: Радио и связь. 1987, стр. 159-161).

Сумматор 2.2 предназначен для суммирования значений разностей между значениями q-ичных символов хэшированного помехоустойчивого блока криптограммы и информационного блока q-ичных символов. Схема сумматора известна, приведена, например, в книге: Л.А. Мальцева и др. "Основы цифровой техники". -М.: Радио и связь, 1986, стр. 53-54, рис. 51 и может быть выполнена, например, на микросхеме К155ИМ1 (см. В.Л. Шило "Популярные цифровые микросхемы". - М.: и связь, 1987, стр. 156).

Управляемый переключатель 2.3, показанный на фиг. 7, предназначен для того, чтобы обеспечить считывание значения числа с выхода сумматора 2.2 на второй вход компаратора (вход В) 2.4 и на первый информационный вход (вход X) мультиплексора 2.6 при поступлении на управляющий вход управляющего переключателя 2.3 управляющих сигналов. По физической сущности управляемый переключатель 2.3 представляет собой двухпозиционный управляемый переключатель. Схемы управляемых переключателей известны и приведены, например, в книге; В.Л. Шило "Популярные микросхемы КМОП, Справочник". -М.: Ягуар, 1993, стр. 22.

Компаратор 2.4 предназначен для сравнения значения числа, полученного с выхода сумматора 2.2 и значения числа, записанного в регистре хранения минимальной суммы 2.5. Схема компаратора известна, приведена, например, в книге: П. П. Мальцев и др. "Цифровые интегральные микросхемы: Справочник. -М.: Радио и связь, 1994, стр. 83 и может быть реализована, например, на микросхеме К555СП1 (см. В.Л. Шило "Популярные цифровые микросхемы". - М.: Радио и связь, 1987. стр. 183).

Регистр хранения минимальной суммы 2.5 предназначен для хранения минимального значения числа из полученных в сумматоре 2.2. Схема регистра хранения минимальной суммы 2.5 известна и приведена, например, в книге: В.А. Батушев, В.Н. Вениаминов и др. Микросхемы и их применение: Справочное пособие. - М. : Радио и связь, 1983, стр.134. рис, 4.34. и может быть реализована, например, на микросхеме К 531ИР19 (см. ВЛ. Шило "Популярные цифровые микросхемы". - М.: Радио и связь, 1987, стр. 120).

Мультиплексор 2.6 является двухвходовым мультиплексором, схема которого известна, приведена, например, в книге: Л.А. Мальцева и др. "Основы цифровой техники". -М.: Радио и связь, 1986, стр. 52, рис. 48, и может быть реализован, например, на микросхеме К155КП5 (см, В.Л. Шило "Популярные цифровые микросхемы". - М.: Радио и 1987, стр. 146).

Блок хэширования 3, показанный на фиг. 3, предназначен для хэширования помехоустойчивых блоков криптограмм по функции хэширования, секретному ключу и стартовому блоку двоичных символов при шифровании первого информационного блока q-ичных символов и для хэширования помехоустойчивых блоков криптограмм по функции хэширования, секретному ключу и помехоустойчивому блоку криптограммы, соответствующему выбранному на предыдущем шаге хэшированному помехоустойчивому блоку криптограммы при шифровании очередного информационного блока q-ичных символов. Блок хэширования состоит из сумматора 3.1, регистров 3.2, 3.6, 3.12, 3.16, 3.19, вычитателей 3.3 и 3.8, компараторов 3.4, 3.11, 3.13, блоков вычисления остатков от деления 3.5 и 3.18, коммутатора 3.9, блоков коммутации 3.7 и 3.17, умножителя 3.10, ключей 3.14 и 3.15, элементов ИЛИ 3.20 и 3.21 и инвертора 3.22.

Первый вход сумматора 3.1 является входом считывания стартового блока двоичных символов, считываемого из модуля памяти стартового блока при шифровании первого информационного блока q-ичных символов или входом считывания помехоустойчивого блока криптограммы, соответствующего выбранному на предыдущем шаге хэширо ванному помехоустойчивому блоку криптограммы, считываемого из модуля памяти предыдущего выбранного блока криптограмм 8 при шифровании очередного информационного блока q-ичных символов (в зависимости от значения управляющего сигнала поданного на управляющий вход блока коммутации 5). Первый вход сумматора 3.1 является первым информационным входом блока хэширования 3. Второй вход сумматора 3.1 является входом считывания помехоустойчивого блока криптограммы, считываемого из модуля памяти помехоустойчивых блоков криптограмм 10 и является вторым информационным входом блока хэширования 3. Первый информационный вход блока коммутации 3.17 является входом секретного ключа блока хэширования 3. Выход сумматора 3.1 подключен к первому информационному входу блока коммутации 3.3 и параллельно к первому входу компаратора 3.4. На второй вход компаратора 3.4 постоянно подан сигнал нулевого уровня ("0"). На управляющий вход блока коммутации 3.3, являющийся первым управляющим входом блока хэширования 3, подаются управляющие сигналы от блока управления, не показанного на чертежах. На управляющий вход блока коммутации 3.17, являющийся вторым управляющим входом блока хэширования 3, подаются управляющие сигналы от блока управления, не показанного на чертежах. На управляющие входы блоков вычисления остатка от деления 3.18 и 3.5, являющиеся соответственно третьим и четвертым управляющими входами блока хэширования 3, подаются управляющие сигналы от блока управления, не показанного на чертежах. На управляющий вход ключа 3.14, являющийся пятым управляющим входом блока хэширования 3, подаются управляющие сигналы от блока управления, не показанного на чертежах. Выход блока коммутации 3.3 соединен со входом регистра 3.6, выход которого соединен с первым входом вычитателя 3.8. На второй вход вычитателя 3.8 постоянно подан сигнал единичного уровня (1). Выход вычитателя 3.8 подключен к первому входу компаратора 3.11 и параллельно к второму информационному входу коммутации 3.3 и к первому входу компаратора 3.13. Выход компаратора 3.11 соединен с первым входом элемента ИЛИ 3,20 и параллельно с первым входом элемента ИЛИ 3.21. Выход компаратора 3.13 соединен с вторым входом элемента ИЛИ 3.20 и параллельно с входом инвертора 3.22. Выход инвертора 3.22 соединен с вторым входом элемента "ИЛИ' 3.21. Выход элемента ИЛИ 3.20 соединен с управляющим входом коммутатора 3.9. Выход элемента ИЛИ 3.21 соединен с управляющим входом ключа 3.15. Выход элемента ИЛИ 3.21 соединен с управляющим входом ключа 3.15. На второй вход компаратора 3.11 постоянно подан сигнал единичного уровня (1), а на второй вход компаратора 3.13 постоянно подан сигнал нулевого уровня (0). Второй выход коммутатора 3.9 соединен со вторым информационным входом блока коммутации 3.17, выход которого подключен к первому входу блока вычисления остатка от деления 3.18. Второй вход блока вычисления остатка от деления 3,18 соединен с выходом регистра 3.19, а выход блока вычисления остатка от деления 3.18 - со входом регистра 3.16. Выход регистра 3.16 соединен с информационным входом ключа 3.14 и параллельно с информационным входом ключа 3.15. Выход ключа 3.14 подключен ко входу регистра 3.12. Первый вход умножителя 3.10 соединен с выходом ключа 3,15, второй вход - с выходом регистра 3.12, а выход умножителя 3.10 подключен к информационному входу коммутатора 3.9. Первый выход коммутатора 3.9 соединен со вторым информационным входом блока коммутации 3.7, управляющий вход которого соединен с выходом компаратора 3.4. На первый информационный вход блока коммутации 3.7 постоянно подан сигнал единичного уровня ("1"). Первый вход блока вычисления остатка от деления 3.5 подключен к выходу блока коммутации 3.7, второй вход блока вычисления остатка от деления 3.5 подключен к выходу регистра 3.2, а выход блока вычисления остатка от деления 3.5 является выходом блока хэширования 3.

Сумматор 3.1 предназначен для суммирования значений стартового блока двоичных символов при шифровании первого информационного блока q-ичных символов либо помехоустойчивого блока криптограммы, соответствующего выбранному на предыдущем шаге хэшированному помехоустойчивому блоку криптограммы при шифровании очередного информационного блока q-ичных символов (в зависимости от значения управляющего сигнала, поданного на управляющий вход блока коммутации 5) с значением помехоустойчивого блока криптограммы, считанного из модуля памяти помехоустойчивых блоков криптограмм 10. Схема сумматора известна, приведена, например в книге: Л.А. Мальцева и др. "Основы цифровой техники". -М. : Радио и связь, 1986, стр. 53-54, рис. 51 и может быть выполнена, например, на микросхеме К155ИМ1 (см. В.Л. Шило '"Популярные цифровые микросхемы"", - М.: Радио и связь, 1987, стр. 156).

Регистр 3.2 предназначен для хранения значения простого числа q. Схема регистра 3.2 известна и приведена, например, в книге: В.А. Батушев, В.Н. Вениаминов и др. Микросхемы и их применение: Справочное пособие. - М.: Радио и связь, 1983, стр. 134, рис. 4.34, и может быть реализована, например, на микросхеме К 531ИР19 (см. В.Л. Шило "Популярные цифровые микросхемы". - М.: Радио и связь, 1987, стр. 120).

Блок коммутации 3.3 идентичен блоку коммутации 3.7, показанному на фиг. 4, и предназначен для переключения работы блока хэширования 3 из режима считывания на вход регистра 3.6 значения числа с выхода сумматора 3.1 в режим считывания на вход регистра 3.6 значения числа с выхода вычитателя 3.8.

Компаратор 3.4 предназначен для значения числа, поступившего с выхода сумматора 3.1, с нулевым значением. Схема компаратора известна, приведена, например, в книге: П. П. Мальцев и.др. "Цифровые интегральные микросхемы: Справочник. -М.: Радио и связь. 1994, стр. 83 и может быть реализована, например, на микросхеме К555СП1 (см. В.Л. Шило "Популярные цифровые микросхемы"', - М.: Радио и связь, 1987, стр. 183).

Блок вычисления остатка от деления З.5, показанный на фиг. 9, предназначен для нахождения остатка от деления значения делимого числа, считанного с выхода блока коммутации 3,7, на значение простого числа, хранящееся в регистре 3.2, Блок вычисления остатка от деления 3.5 состоит из регистра 3.5.1, вычитателя 3.5.2, коммутатора 3.5.3, компаратора 3.5.4 и ключа 3.5.5. Первый информационный вход ключа 3.5.5 является первым входом блока вычисления остатка от деления 3.5, Выход ключа 3.5.5 соединен с входом регистра 3.5.1. Управляющий вход ключа 3.5.5 является управляющим входом блока вычисления остатка от деления 3.5. Выход регистра З.5.1 соединен с первым входом вычитателя 3.5.2. Второй вход вычитателя 3.5.2 параллельно с первым входом компаратора 3.5.4 является вторым входом блока вычисления остатка от деления 3.5. Выход вычитателя 3.5.2 соединен со вторым входом компаратора 3.5.4 и параллельно с информационным входом коммутатора 3.5.3. Выход компаратора 3.5.4 соединен с управляющим входом коммутатора 3.5.3. Второй выход коммутатора 3.5.3 является выходом блока вычисления остатка от деления 3.5. Первый выход коммутатора 3.5.3 соединен с вторым информационным входом ключа 3.5.5.

Регистр 3.5.1 предназначен для хранения значения числа, считанного на вход блока вычисления остатка от деления 3.5 и хранения в дальнейшем значения промежуточных результатов вычисления от деления считанного числа на простое число q. Схема регистра 3.5.1 известна и приведена, например, в книге: В. А. Батушев, В.Н. Вениаминов и др. Микросхемы и их применение: Справочное пособие. - М.: Радио и связь. 1983, стр. 134, рис. 4.34 и может быть реализована, например, на микросхеме К 531ИР19 (см. В.Л. Шило "Популярные цифровые микросхемы". - М.: Радио и связь, 1987, стр. 120).

Вычитатель 3.5.2 предназначен для определения разности между значением делимого числа, считанного через регистр 3.5.1, и значением простого числа, считанного по второму входу блока вычисления остатка от деления 3.5. Вычитатель 3.5.2. представляет собой сумматор, работающий в режиме вычитания. Схема вычитателя известна, приведена, например, в книге; П.П. Мальцев и др. "Цифровые интегральные микросхемы; Справочник. -М.: Радио и связь, 1994, стр.76. Он может быть, реализован, например, на микросхеме К555ИМ7 (см. В.Л. Шило "Популярные цифровые микросхемы". - М. : Радио и связь. 1987, стр. 159-161).

Коммутатор 3.5.3, показанный на фиг. 6, предназначен переключения работы блока вычисления остатка от деления 3.5 из режима вычисления остатка от деления значения делимого числа на значение проcтого числа в режим считывания с выхода блока вычисления остатка от деления 3.5 значения вычисленного остатка. Коммутатор 3.5.3 содержит первый управляемый переключатель 3.5.3.1, второй управляемый переключатель 3.5.3.2 и инвертор 3.5.3.3. Информационный вход первого управляемого переключателя 3.5.3.1 и соединенный с ним в параллель информационный вход второго управляемого переключателя 3.5.3.2 является информационным входом коммутатора 3.5.3. Управляющий вход второго управляемого переключателя 3.5.3.1 соединен с выходом инвертора 3.5.3.3. Выходы первого управляемого переключателя 3.5.3.1 и второго управляемого переключателя 3.5.3.1 являются соответственно первым и вторым выходами коммутатора 3.5.3. Управляющий вход первого управляемого переключателя 3.5.3.1 и соединенный с ним в параллель вход инвертора 3.5.3.3 являются управляющими входами коммутатора 3.5.3.

Первый управляемый переключатель 3.5.3.1 предназначен для считывания значения промежуточных результатов вычисления остатка от деления числа на простое число q с выхода вычитателя 3.5.2 на второй информационный вход ключа 3.5.5. Схема первого управляемого переключателя 3.5.3.1 идентична схеме ключа 3.14, показанной на фиг. 7. Второй управляемый переключатель 3.5.3.2 предназначен для считывания с выхода блока вычисления остатка от деления 3.5 значения вычисленного остатка. Схема второго управляемого переключателя 3.5.3.2 идентична схеме ключа 3.14. показанной на фиг. 7. Инвертор 3.5.3.3 предназначен для формирования управляющего сигнала, поступающего на управляющий вход второго управляемого переключателя 3.5.3.2. Схема инвертора 3.5.3.3 известна и приведена, например, в книге: В.Л. Шило "Популярные микросхемы КМОП, справочник". -М.: Ягуар, 1993. стр. 22.

Компаратор 3.5.4 предназначен для сравнения значения числа, считанного из вычитателя 3.5.2 с значением простого числа, полученного со второго входа блока вычисления остатка от деления 3.5. Схема компаратора известна, приведена, например, в книге: П.П. Мальцев и др. "Цифровые интегральные микросхемы; Справочник. -М.: Радио и связь. 1984, стр. 83 и быть реализована, например, на микросхеме К555СП1 (см. В.Л. Шило "Популярные цифровые микросхемы". -М.: Радио и связь, 1987, стр. 183).

Ключ 3.5.5 предназначен для переключения работы блока вычисления остатка от деления 3.5 из режима считывания значения числа, считанного на вход блока вычисления остатка от деления 3.5 в режим считывания значения промежуточных результатов вычисления остатка от деления считанного числа на простое число q на вход регистра 3.5.1. Схема ключа 3.5.5 идентична схеме блока коммутации 3.7, приведенной на фиг. 4.

Регистр 3.6 предназначен для хранения значения числа, считанного с выхода блока коммутации 3.3. Схема регистра 3.6 известна и приведена, например, в книге: Б. А. Батушев. Б.Н. Вениаминов и др. Микросхемы и их применение: Справочное пособие. - М.: Радио и связь, 1983, стр. 134. рис. 4,34, и может быть реализована, например, на микросхеме К 531ИР19 (см. В.Л. Шило "Популярные цифровые микросхемы". -М.: Радио и связь, 1987, стр. 120).

Блок коммутации 3.7, показанный на фиг. 4, предназначен для переключения работы блока хэширования 3 из режима считывания промежуточного значения хэшированного помехоустойчивого блока криптограммы в режим считывания единичного значения на вход блока вычисления остатка от деления 3.5. Блок коммутации 3.7 содержит первый управляемый переключатель 3.7.1, второй управляемый переключатель 3.7.2 и инвертор 3.7.3. Информационные входы первого управляемого переключателя 3.7.1 и второго управляемого переключателя 3.7.1 являются соответственно первым и вторым информационными входами блока коммутации 3.7. Соединенные в параллель информационные выходы первого и второго управляемых переключателей 3.7.1 и 3.7.2 являются выходом блока коммутации 3.7. Вход инвертора 3.7.3 и соединенный с ним в параллель управляющий вход первого управляемого переключателя 3.7.1 являются управляющим входом блока коммутации 3.7. Выход инвертора 3.7.3 соединен с управляющим входом второго управляемого переключателя 3.7.2. Схемы управляемых переключателей и инвертора известны и приведены в книге: В.Л. Шило "Популярные микросхемы КМОП, справочник". -М.: Ягуар, 1993, стр. 22.

Вычитатель 3.8 предназначен для вычитания из значения числа, поступившего с выхода регистра 3.6, единичного значения. Вычитатель 3.8 представляет собой сумматор, работающий в режиме вычитания. Схема вычитателя известна, приведена, например, в книге: П.П. Мальцев и др. "Цифровые интегральные микросхемы: Справочник. -М.: Радио и связь, 1994, стр.76, и он может быть, например, реализован на микросхеме К555ИМ7 (см. В.Л, Шило "Популярные цифровые микросхемы". - М.: Радио и связь, 1987, стр. 159-161).

Коммутатор 3.9 идентичен коммутатору 3.5.3, показанному на фиг. 6, и предназначен для считывания значения числа с выхода умножителя 3.10 на вход блока коммутации 3.7 или на вход блока коммутации 3.17 в зависимости от значений выходных сигналов компараторов 3.11 и 3.13, поступающих на управляющий вход коммутатора 3.9.

Умножитель 3.10 предназначен для перемножения значений чисел, полученных с выходов регистра 3.12 и ключа 3.15, соответственно. Схема умножителя 3.10 известна, приведена, например, в книге: П.П. Мальцев и.др. "Цифровые интегральные микросхемы: Справочник. -М.: Радио и связь, 1994, стр. 82 и он может быть, например, реализован на микросхеме К555ИП9 (см. В.Л. Шило "Популярные цифровые микросхемы". -М.: Радио и связь, 1987, стр. 157-169).

Компаратор 3.11 предназначен для сравнения значения числа, поступившего с выхода вычитателя 3.8, с единичным значением. Схема компаратора известна, приведена, например, в книге: П.П. Мальцев и др. "Цифровые интегральные микросхемы: Справочник. -М.: Радио и связь, 1994. стр. 83 и может быть реализована, например, на микросхеме К555СП1 (см. В.Л. Шило "Популярные цифровые микросхемы". - М.: Радио и связь. 1987, стр. 183).

Регистр 3.12 предназначен для хранения значения числа, поступившего с выхода ключа 3.14. Схема регистра 3.12. известна и приведена, например, в книге: В. А. Батушев, В. Н, Вениаминов и др. Микросхемы и их применение: Справочное пособие. - М.: Радио и связь, 1983, стр. 134. рис. 4.34. и может быть реализована, например, на микросхеме К 531ИР19 (см. В.Л. Шило "Популярные цифровые микросхемы". - М.: Радио и связь, 1987, стр. 120).

Компаратор 3.13 предназначен для сравнения значения числа, поступившего с выхода вычитателя 3.8, с нулевым значением. Схема компаратора известна, приведена, например, в книге: П.П. Мальцев и др. "Цифровые интегральные микросхемы: Справочник. -М.: Радио и связь, 1994, стр. 83 и может быть реализована, например, на микросхеме К555СП1 (см. В.Л. Шило "Популярные цифровые микросхемы". - М.: Радио и связь, 1987, стр. 183).

Ключ 3.14, показанный на фиг. 7, предназначен для управления считыванием значения числа с выхода регистра 3.16 на вход регистра 3.12. По физической сущности ключ 3.14 представляет собой двухпозиционный управляемый переключатель. Схемы управляемых переключателей известны и приведены, например, в книге: В.Л. Шило "Популярные микросхемы КМОП, справочник". -М.: Ягуар, 1993, стр. 22.

Ключ 3.15 идентичен ключу 3.14, показанному на фиг. 7, и предназначен для управления считыванием значения числа с выхода регистра 3.16 на первый вход умножителя 3.10.

Регистр 3.16 предназначен для хранения значения числа, поступившего с выхода блока вычисления остатка от деления 3.18. Схема регистра 3.16 известна и приведена, например, в книге: В.А. Батушев, Б.Н. Вениаминов и др. Микросхемы и их применение: Справочное пособие. - М.: Радио и связь, 1983, стр. 134, рис. 4.34, и может быть реализована, например, на микросхеме К 531ИР19 (см. В. Л. Шило "Популярные цифровые микросхемы". - М.: Радио и связь, 1987, стр. 120).

Блок коммутации 3.17 идентичен блоку коммутации 3.7, показанному на фиг. 4, и предназначен для переключения работы хэширования 3 из режима считывания значения секретного ключа в режим считывания промежуточного значения хэшированного помехоустойчивого блока криптограммы на первый вход блока вычисления остатка от деления 3.18. Блок вычисления остатка от деления 3.18 идентичен блоку вычисления остатка от деления 3.5, показанному на фиг. 9, и предназначен для нахождения остатка от деления значения делимого числа, считанного с выхода блока коммутации 3.17 на значение простого числа p, хранящееся в регистре 3.19.

Регистр 3.19 предназначен для хранения значения простого числа p. Схема регистра 3.19 известна и приведена, например, в книге: В.А. Батушев, В.Н. Вениаминов и др. Микросхемы и их применение: Справочное пособие. -М.: Радио и связь, 1983, стр. 134, рис. 4.34, и может быть реализована, например, на микросхеме К 531ИР19 (см. В.Л. Шило "Популярные цифровые микросхемы". - М.: Радио и связь, 1987, стр. 120).

Элемент ИЛИ 3.2.0 предназначен для подачи сигнала, поступающего с выхода компаратора 3.11, или сигнала, посыпающего с выхода компаратора 3.13, на управляющий вход коммутатора 3.9. Элемент ИЛИ 3.21 предназначен для подачи сигнала, поступающего с выхода компаратора 3.11 или сигнала, поступающего с выхода инвертора 3.22, на управляющий вход ключа 3.15. Схемы элементов ИЛИ 3.20 и 3.21 идентичны, известны и приведены, например, в книге: С.А. Бирюков "Цифровые устройства на МОП-интегральных микросхемах". - М.: Радио и связь, 1990, стр.5 и могут быть реализованы, например, на микросхеме 176ЛЕ5.

Инвертор 3.22 предназначен для инвертирования двоичного сигнала, поступающего с выхода компаратора 3.13, и выдачи его на второй вход элемента ИЛИ 3.21. Схема инвертора 3.22 известна и приведена, например, в книге: С.А. Бирюков "Цифровые устройства на МОП-интегральных микросхемах". - М.: Радио и связь, 1990, стр.8 и может быть реализован, например, на микросхеме 176ЛП11.

Модуль памяти секретного ключа 4 предназначен для хранения значения секретного ключа и выдачи его на вход секретного ключа блока хэширования 3. В качестве модуля памяти секретного ключа 4 может быть использовано статическое оперативное запоминающее устройство (ОЗУ), схема построения которого известна и приведена, например, в книге: Б.А. Батушев, Б.Н. Вениаминов и др. "Микросхемы и их применение: Справочное пособие". - М.: Радио и связь, 19S3, стр. 175, рис. 5.12. Модуль памяти секретного ключа 4 может быть реализован, например, на микросхеме памяти К 537РУ8 (см. В.И. Корнейчук, В.П. Тарасенко "Вычислительные устройства на микросхемах: Справочник." -К.: Тэхника, 1988, стр. 85-87).

Блок коммутации 5 идентичен блоку коммутации 3.7, показанному на фиг. 4 и предназначен для переключения работы устройства из режима значения стартового блока двоичных символов в режим ввода значения помехоустойчивого блока криптограммы, соответствующего выбранному на предыдущем шаге хэшированному помехоустойчивому блоку криптограммы, на первый информационный вход блока хэширования 3.

Модуль памяти стартового блока 6 предназначен для хранения значения стартового блока двоичных символов и выдачи его на вход блока коммутации 5. В качестве модуля памяти стартового блока 6 может быть использовано статическое оперативное запоминающее устройство (ОЗУ), схема построения которого известна и приведена, например, в книге: В.А. Батушев, В.Н. Вениаминов и др. "Микросхемы и их применение: Справочное пособие". - М.: Радио и связь, 1983, стр. 175, рис, 5.12. Модуль памяти стартового блока б может быть реализован, например, на микросхеме памяти К537РУ8 (см. В.И. Корнейчук, В.П. Тарасенко "Вычислительные устройства на микросхемах: Справочник." -К.:Тэхника, 1988, стр. 85-87).

Модуль памяти блока криптограммы 7 предназначен для записи значения помехоустойчивого блока криптограммы, соответствующего выбранному хэшированному помехоустойчивому блоку криптограммы, хранения и выдачи его на вход прямого канала связи. В качестве модуля памяти блока криптограммы 7 может быть использовано статическое оперативное запоминающее устройство (ОЗУ), схема построения которого известна и приведена, например, в книге: В.А. Батушев, В.Н. Вениаминов и др. "Микросхемы и их применение: Справочное пособие". - М. : Радио и связь. 1983, стр. 175, рис. 5.12. Модуль памяти блока криптограммы 7 может быть реализован, например, на микросхеме памяти К537РУ8 (см. В. И. Корнейчук, В.П. Тарасенко "Вычислительные устройства на микросхемах: Справочник." -К.:Тэхника, 1988. стр. 85-87).

Модуль памяти предыдущего блока криптограммы 8 предназначен для записи значения помехоустойчивого блока криптограммы, соответствующего выбранному хэшированному блоку криптограммы, хранения и выдачи его на вход блока коммутации 5. В качестве модуля памяти предыдущего блока криптограммы 8 может быть использовано статическое оперативное запоминающее устройство (ОЗУ), схема построения которого известна и приведена, например, в книге: В.А. Батушев, В. Н. Вениаминов и др. "Микросхемы и их применение; Справочное пособие". - М.: Радио и связь, 1983, стр. 175, рис. 5.12. Модуль памяти предыдущего блока криптограммы 8 может быть реализован, например, на микросхеме памяти К 537РУ8 (см. В.И. Корнейчук, В.П. Тарасенко "Вычислительные устройства на микросхемах: Справочник." -К.: Тэхника, 1988, стр. 85-87).

Коммутатор 9 идентичен коммутатору 3.5.3, показанному на фиг. 6, и предназначен для переключения работы устройства из режима считывания значения помехоустойчивого блока криптограммы на вход блока хэширования 3 в режим считывания на вход модуля памяти выбранного блока криптограммы 7 и на вход модуля памяти предыдущего выбранного блока криптограммы 8.

Модуль памяти помехоустойчивых блоков криптограмм 10, показанный на фиг. 10, предназначен для хранения значений предварительно сформированных помехоустойчивых блоков криптограмм и считывания их на информационный вход коммутатора 9. Модуль памяти помехоустойчивых блоков криптограмм состоит из генератора адресов сигнала 10.1, регистра хранения адреса 10.2, мультиплексора, 10.3 и запоминающего модуля 10.4. Вход разрешения записи (вход W) регистра хранения адреса 10.2 является информационным входом модуля памяти помехоустойчивых блоков криптограмм 10. На вход генератора адресов сигнала 10.1 и управляющий вход (вход S) мультиплексора 10.3 подаются управляющие сигналы. Выход генератора адресов сигнала 10.1 соединен в параллель с информационным входом (вход N) регистра хранения адреса 10.2 и вторым информационным входом (вход X2) мультиплексора 10.3. Первый информационный вход (вход X1) мультиплексора 10.3 подключен к выходу регистра хранения адреса 10.2. Выход мультиплексора 10.3 соединен с входом запоминающего модуля 10.4, выход запоминающего модуля 10.4 является выходом модуля памяти помехоустойчивых блоков криптограмм 10.

Генератор адресов сигнала 10.1 предназначен для формирования адреса помехоустойчивого блока криптограммы, считываемого из запоминающего модуля 10.4 и выработки адреса соответствующего выбранному хэшированному помехоустойчивому блоку криптограммы помехоустойчивого блока криптограммы. Генератор адресов сигнала 10,1 по физической сущности представляет собой счетчик, схема которого известна, приведена, например, в книге: А.А Сикарев, О.Н. Лебедев "Микроэлектронные устройства формирования и обработки сложных сигналов", -М. : Радио и связь, 1983, стр. 128, рис, 518, и может быть реализован, например, на микросхеме К155ИЕ6 (см. В.Л. Шило "Популярные цифровые микросхемы". -М.: Радио и связь, 1987, стр. 90-93).

Регистр хранения адреса 10.2 предназначен для хранения адреса соответствующего выбранному хэшированному помехоустойчивому блоку криптограммы помехоустойчивого блока криптограммы. Схема регистра хранения адреса 10.2 известна, приведена, например, в книге В.А. Батушев, В.Н. Вениаминов и др. "Микросхемы и их применение": Справочное пособие". - М.: Радио и связь, 1983, стр. 134, рис. 4.34, и может быть реализована, например, на микросхеме К531ИР19 (см. В. Л. Шило "Популярные цифровые микросхемы". - М.: Радио и связь, 1987, стр. 120).

Мультиплексор 10.3 предназначен для переключения модуля памяти помехоустойчивых блоков криптограмм 10 из режима поочередного считывания значений N помехоустойчивых блоков криптограмм в режим считывания помехоустойчивого блока криптограммы, соответствующего выбранному хэшированному помехоустойчивому блоку криптограммы, из запоминающего модуля 10.4. Схема мультиплексора 10.3 известна, приведена в книге Л.А. Мальцева и др. "Основы цифровой техники". -М.: Радио и связь, 1986, стр. 52, рис. 48, и может быть реализована, например, на микросхеме К155КП5 (см. В.Л. Шило "Популярные цифровые микросхемы". - М.: Радио и связь, 1987, стр. 146).

Запоминающий модуль 10.4 предназначен для хранения значений N помехоустойчивых блоков криптограмм.