Изобретение относится к области передачи дискретной информации, более конкретно к устройству синхронизации приемника с передатчиком с использованием характеристик цифрового сигнала для управления фазой генератора, управляемого напряжением.

Известно, что синхронизация приемника входными данными достигается за счет использования устройства синхронизации с петлей фазовой автоподстройки частоты (ФАПЧ), содержащего генератор, управляемый напряжением. Сигнал этого генератора используется для тактирования записи входных данных в устройстве синхронизации и их сопровождения при последующей передаче принимаемых сигналов в другие устройства. Синхронизация возникает при определенных ограничениях на начальную ошибку рассогласования фазы и частоты генератора, управляемого напряжением (ГУН), относительно фазы и частоты входных данных (см. F.M.Gardner. Phaselock Technique. J.Wiley & Sons, 1979, ch. 4). Если начальные значения частоты и/или фазы превышают допустимые ограничения, то петля ФАПЧ не войдет в режим синхронизации. Для расширения области начальных значений частоты и фазы, при которых возникает синхронизация петли ФАПЧ входными данными, используется принудительное изменение частоты и/или фазы.

В приемниках систем цифровой связи фазовая синхронизация петли ФАПЧ с ГУН достигается за счет использования в контуре петли ФАПЧ фазового детектора и дополнительного устройства принудительного сканирования частоты управляемого генератора (см. F.M.Gardner. Phaselock Technique. J.Wiley & Sons, 1979, ch. 5) или фазы входного сигнала (Т.Н.Lee, J.F.Bulzacchelly.l55 Mhz Clock Recovery Delay-and-Phase-Locked Loop. IEEE Journal of Solid State Circuits, v. 27, 12, pp. 1736 - 1745). При использовании такого устройства полоса захвата петли ФАПЧ расширяется вследствие грубой подстройки частоты или фазы при сканировании.

Известно устройство синхронизации приемника цифрового сигнала, содержащее фазовый детектор и решающее устройство, на входы которых подается информационный сигнал, ГУН, формирующий тактовую частоту для фазового детектора и решающего устройства, фильтр низких частот (ФНЧ), вход которого соединен с выходом фазового детектора, аналоговый сумматор, один вход которого соединен с выходом ФНЧ, другой вход - с генератором пилообразного напряжения через управляемый коммутатор, а выход - с управляющим входом ГУН, и декодер блокового информационного сигнала, вход которого соединен с выходом решающего устройства, а выход - с управляющим входом коммутатора (см. F.M.Gardner. Phaselock Technique. J.Wiley & Sons, 1979, ch. 5). Генератор пилообразного напряжения, коммутатор и аналоговый сумматор образуют устройство сканирования частоты.

В этом устройстве на выходе решающего устройства формируется цифровой сигнал данных, а на выходе ГУН - тактовая частота, синхронизированная с цифровым сигналом. При систематическом нарушении блочной синхронизации декодер формирует сигнал включения режима сканирования, в результате чего коммутатор соединяет выход генератора пилообразного напряжения со входом сумматора. В результате на выходе сумматора формируется пилообразное напряжение, приводящее к изменению частоты генерации ГУН. Сканирование частоты генерации ГУН прекращается при формировании декодером управляющего сигнала соответствующего уровня, подаваемого на коммутатор.

Недостатком данного известного устройства синхронизации является значительное время вхождения в синхронизм. Это связано с тем, что кратковременное нарушение синхронизации петли ФАПЧ может привести к сканированию управляющего сигнала в направлении, противоположном оптимальному.

Известно устройство синхронизации, наиболее близкое к изобретению по технической сущности, содержащее цифровой фазовый детектор с элементом задержки на входе и аналоговым сумматором на выходе, ФНЧ и ГУН на основе кварцевого генератора. Сигнал входных данных поступает на первый вход элемента задержки, задержанные данные с выхода элемента задержки, в свою очередь, поступают на первые входы фазового детектора и решающего устройства. На второй управляющий вход элемента задержки поступает сигнал с выхода ФНЧ. На вторые входы фазового детектора и решающего устройства поступает сигнал с ГУН. Фазовый детектор имеет несколько выходов первого и второго типа. Усредненные взвешенные значения амплитуд импульсов, формируемых на входах первого и второго типа, служат соответственно оценкой отставания и опережения частоты ГУН относительно частоты входных данных. Для получения этих оценок в аналоговом сумматоре производится суммирование с соответствующим весом напряжений, формируемых на выходах первого типа фазового детектора, и вычитание с соответствующим весом напряжений, формируемых на выходах второго типа фазового детектора. Выходной сигнал аналогового сумматора усредняется с помощью ФНЧ, и усредненный сигнал подается на управляющие входы ГУН и элемента задержки. При синхронизации ГУН входными данными частота генератора должна быть равна частоте кодообразования. С выхода решающего устройства поступает цифровой сигнал, а с выхода ГУН - тактовая частота, синхронизированная с принимаемым цифровым сигналом (см. вышеуказанную статью Т.Н.Lee, J.F.Bulzacchelly).

Недостатком известного устройства синхронизации является узкая полоса захвата петли ФАПЧ, что приводит к необходимости использования ГУН на основе кварцевого резонатора.

Задачей изобретения является создание устройства синхронизации цифрового приемника, позволяющего устранить указанные недостатки за счет осуществления направленного сканирования частоты ГУН при потере синхронизации вплоть до возникновения режима захвата. Это позволяет уменьшить время вхождения в синхронизм и снизить требования к минимальной допустимой ошибке рассогласования по частоте и фазе.

Указанный результат достигается тем, что в одном из вариантов осуществления устройство синхронизации цифрового приемника, содержащее цифровой фазовый детектор, аналоговый сумматор, суммирующий вход которого соединен с первым выходом фазового детектора, фильтр низких частот, вход которого соединен с выходом аналогового сумматора, генератор, управляемый напряжением, вход которого соединен с выходом фильтра низких частот, а выход - с одним из входов фазового детектора, другой вход которого соединен с входом устройства синхронизации цифрового приемника, а также решающее устройство, информационный вход которого соединен с входом устройства синхронизации цифрового приемника, тактовый вход - с выходом генератора, управляемого напряжением, а выход - с выходом упомянутого устройства синхронизации, в соответствии с изобретением содержит двухвходовой мультиплексор, первый информационный вход которого соединен с вторым выходом цифрового фазового детектора, а выход - с вычитающим входом аналогового сумматора, и блок определения состояния синхронизации, первый вход которого соединен с входом устройства синхронизации цифрового приемника, второй вход блока определения состояния синхронизации соединен с выходом генератора, управляемого напряжением, первый выход блока определения состояния синхронизации соединен с управляющим входом двухвходового мультиплексора, а второй выход блока определения состояния синхронизации соединен с вторым информационным входом двухвходового мультиплексора.

Вышеуказанный технический результат достигается также тем, что во втором варианте осуществления устройство синхронизации цифрового приемника, содержащее цифровой фазовый детектор, аналоговый сумматор, суммирующий вход которого соединен с первым выходом цифрового фазового детектора, фильтр низких частот, вход которого соединен с выходом аналогового сумматора, генератор, управляемый напряжением, вход которого соединен с выходом фильтра низких частот, а выход - с одним из входов цифрового фазового детектора, другой вход которого соединен с входом устройства синхронизации цифрового приемника, и решающее устройство, информационный вход которого соединен с входом устройства синхронизации цифрового приемника, тактовый вход - с выходом генератора, управляемого напряжением, а выход - с выходом упомянутого устройства синхронизации, согласно изобретению содержит двухвходовой мультиплексор, первый информационный вход которого соединен с вторым выходом цифрового фазового детектора, а выход - с вычитающим входом аналогового сумматора, блок определения состояния синхронизации, первый вход которого соединен с входом устройства синхронизации цифрового приемника, а второй вход - с выходом генератора, управляемого напряжением, и цифровой интегратор, информационный вход которого соединен с первым выходом блока определения состояния синхронизации, тактовый вход цифрового интегратора соединен с входом устройства синхронизации цифрового приемника, а выход цифрового интегратора соединен с управляющим входом двухвходового мультиплексора, причем второй выход блока определения состояния синхронизации соединен со вторым информационным входом двухвходового мультиплексора.

При этом цифровой интегратор предпочтительно содержит регистр сдвига и логическую схему И, входы которой соединены с информационными выходами регистра сдвига, тактовый вход которого соединен с тактовым входом цифрового интегратора, информационный вход регистра сдвига соединен с информационным входом цифрового интегратора, а выход логической схемы И соединен с выходом цифрового интегратора.

Кроме того, блок определения состояния синхронизации как в первом, так и во втором варианте осуществления предпочтительно содержит первый, второй, третий и четвертый триггеры, при этом тактовые входы первого и второго триггеров соединены с вторым входом блока определения состояния синхронизации, прямой выход первого триггера соединен с информационным входом второго триггера, инверсный выход которого соединен с информационным входом первого триггера, тактовый вход третьего триггера соединен с первым входом блока определения состояния синхронизации, информационный вход третьего триггера соединен с прямым выходом второго триггера, прямой выход третьего триггера - с тактовым входом четвертого триггера, информационный вход которого соединен с прямым выходом первого триггера, причем инверсный выход третьего триггера соединен с первым выходом блока определения состояния синхронизации, а прямой выход четвертого триггера соединен с вторым выходом блока определения состояния синхронизации.

Соответствующее изобретению выполнение устройства синхронизации цифрового приемника обеспечивает непрерывное сравнение в блоке определения состояния синхронизации времени появления задних фронтов входных данных и сигнала ГУН. При потере синхронизации указанный блок формирует сигналы, индицирующие отсутствие синхронизации и опережение/отставание, путем определения соотношения частот и фаз сигнала входных данных и сигнала ГУН. Для выполнения этой функции средняя частота ГУН выбирается либо равной удвоенной частоте кодообразования для входных данных, задние фронты импульсов которых соответствуют концу или началу тактового интервала, например для сигнала формата NRZ, либо равной частоте кодообразования для входных данных, задние фронты импульсов которых соответствуют концу тактового интервала, например, для сигнала формата CMI. При формировании сигнала высокого уровня, индицирующего потерю синхронизации, один из выходов фазового детектора отключается, и на аналоговый сумматор подается сигнал постоянного уровня, индицирующий опережение или отставание синхронизации. Уровень сигнала индикации опережения/отставания устанавливается таким образом, чтобы он соответствовал уровню сигнала на выходе фазового детектора, к которому подключен мультиплексор. Например, если при опережении фазовый детектор формирует высокий средний уровень, то и уровень указанного сигнала должен быть высоким и наоборот. При наличии на выходах фазового детектора коротких импульсов и при подаче на один из входов аналогового сумматора постоянного сигнала ФНЧ интегрирует этот сигнал и формирует медленно увеличивающееся или уменьшающееся управляющее напряжение для ГУН в зависимости от того, отстает или опережает частота и фаза сигнала ГУН частоту и фазу сигнала входных данных. При этом частота ГУН изменяется в нужном направлении до тех пор, пока не возникнет режим захвата.

В случае, когда входные данные могут содержать помехи, между блоком определения состояния синхронизации и входом управления мультиплексора включается цифровой интегратор, состоящий из регистра сдвига и логической схемы. Логическая схема формирует высокий уровень, соответствующий индикации отсутствия синхронизации и приводящий к сканированию управляющего сигнала ГУН, когда в регистре сдвига содержатся только единицы, и низкий уровень - в противном случае, в результате исключается влияние помехи на устойчивую работу петли ФАПЧ, включающей в себя фазовый детектор, аналоговый сумматор, ФНЧ и ГУН.

Изобретение поясняется на примерах его осуществления, иллюстрируемых чертежами, на которых представлено следующее:

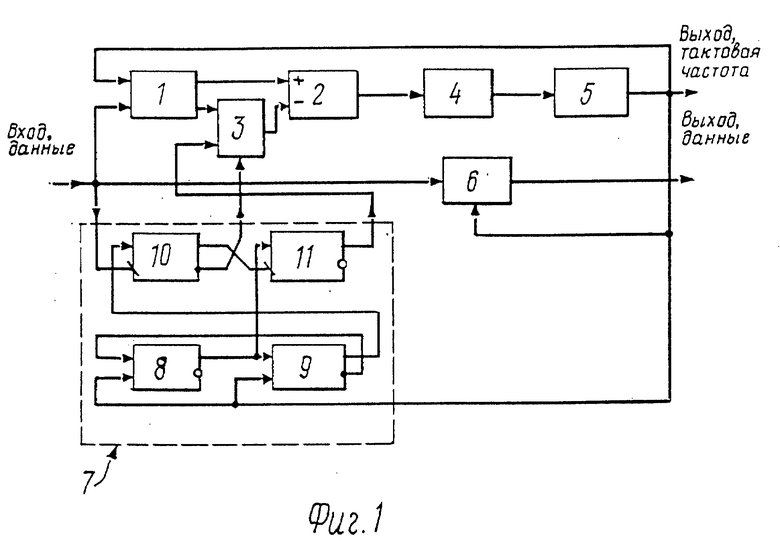

Фиг. 1 - структурная схема устройства синхронизации цифрового приемника, соответствующего первому варианту осуществления изобретения;

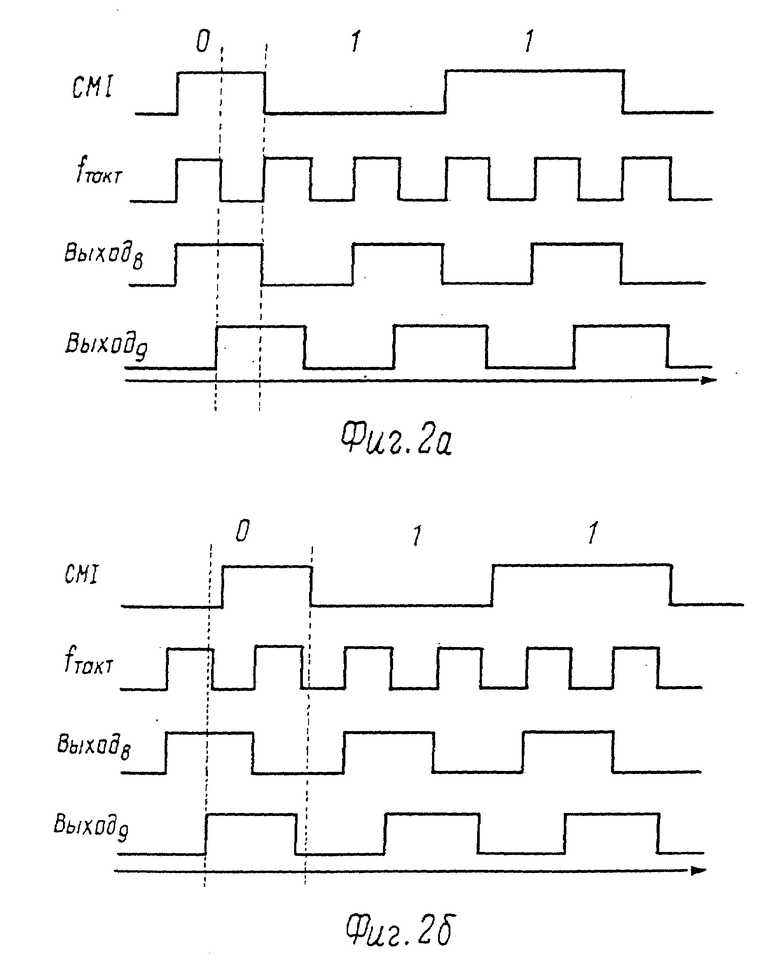

Фиг. 2 - эпюры напряжений на входах и выходах блоков устройства синхронизации для сигналов входных данных формата CMI;

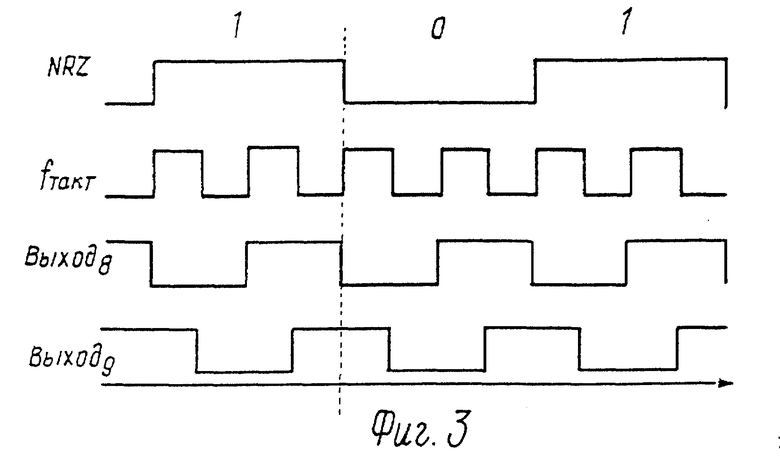

Фиг. 3 - эпюры напряжений на входах и выходах блоков устройства синхронизации для сигнала входных данных формата NRZ;

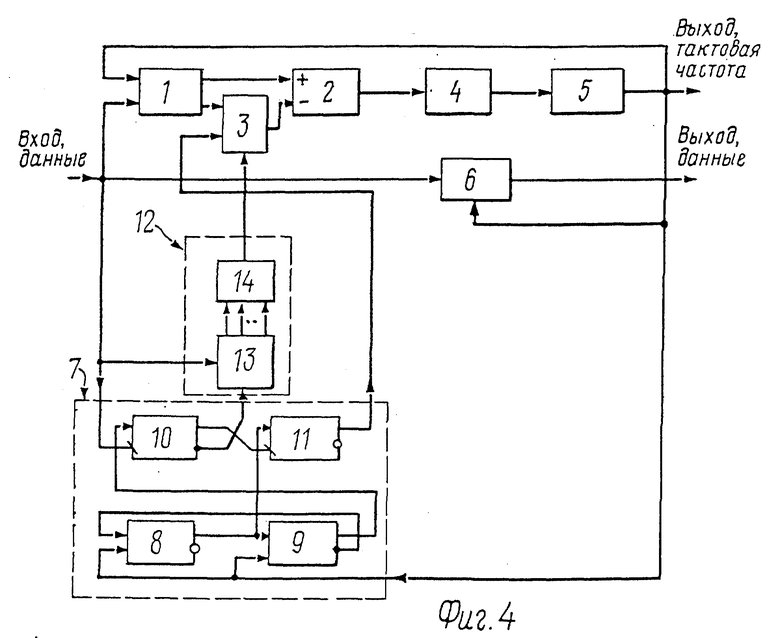

Фиг. 4 - структурная схема устройства синхронизации цифрового приемника, соответствующего второму варианту осуществления изобретения.

Устройство синхронизации цифрового приемника, представленное на фиг. 1, содержит цифровой фазовый детектор 1, выходы которого соединены соответственно с суммирующим входом аналогового сумматора 2 и с первым информационным входом двухвходового мультиплексора 3, выход которого соединен с вычитающим входом аналогового сумматора 2. Выход сумматора 2 соединен с входом ФНЧ 4, выход которого соединен с входом ГУН 5. Выход ГУН 5 соединен с тактовым входом решающего устройства 6, подключенного своим информационным входом к входу устройства синхронизации цифрового приемника, с которым соединены также первый вход фазового детектора 1 и первый вход блока определения состояния синхронизации 7. Второй вход блока 7, второй вход фазового детектора 1 и тактовый вход решающего устройства 6 соединены с выходом ГУН 5. Первый выход блока определения состояния синхронизации 7, являющийся выходом индикации отсутствия синхронизации, соединен с управляющим входом двухвходового мультиплексора 3, второй информационный вход которого соединен с вторым выходом блока 7, являющимся выходом индикации опережения/запаздывания синхронизации.

Как показано на фиг.1, блок определения состояния синхронизации 7 содержит первый триггер 8, второй триггер 9, третий триггер 10, четвертый триггер 11, причем триггеры 10, 11 тактируются задним фронтом импульсного сигнала, триггер 8 тактируется высоким уровнем, а триггер 9 - низким уровнем. Тактовые входы первого и второго триггеров 8, 9 соединены с вторым входом блока определения состояния синхронизации 7. Прямой выход первого триггера 8 соединен с информационным входом второго триггера 9, инверсный выход которого соединен с информационным входом первого триггера 8. Тактовый вход третьего триггера 10 соединен с первым входом блока определения состояния синхронизации 7. Информационный вход третьего триггера 10 соединен с прямым входом второго триггера 9, а прямой выход третьего триггера 10 - с тактовым входом четвертого триггера 11, информационный вход которого соединен с прямым выходом первого триггера 8. Инверсный выход третьего триггера 10 соединен с первым выходом блока определения состояния синхронизации 7, а прямой выход четвертого триггера 11 соединен с вторым выходом блока определения состояния синхронизации. Вариант выполнения устройства синхронизации по фиг. 4 отличается от варианта по фиг.1 дополнительно введенным цифровым интегратором 12, информационный вход которого соединен с первым выходом блока определения состояния синхронизации 7, тактовый вход цифрового интегратора 12 соединен с входом устройства синхронизации, а выход цифрового интегратора 12 соединен с управляющим входом двухвходового мультиплексора. При этом цифровой интегратор 12 содержит регистр сдвига 13 с параллельными выходами, тактируемый передним фронтом входного сигнала, и логическую схему И 14, формирующую высокий уровень на своем выходе, когда в регистре 13 содержатся только единицы. Входы схемы И 14 соединены соответственно с информационными выходами регистра сдвига 13, тактовый вход которого соединен с тактовым входом цифрового интегратора 12, информационный вход регистра сдвига 13 соединен с информационным входом цифрового интегратора 12, а выход логической схемы И 14 соединен с выходом цифрового интегратора 12.

Устройство синхронизации цифрового приемника работает следующим образом. В начальный момент, когда синхронизация отсутствует, фаза сигнала ГУН 5 "скользит" относительно фазы сигнала входных данных. В некоторый момент времени по заднему фронту импульсов входных данных в триггер 10 записывается "1", а затем "0". Это приводит к формированию правильно установленных уровней сигналов индикации синхронизации и опережения/отставания соответственно на первом и втором выходах блока 7 определения состояния синхронизации. При синхронизации ГУН 5 входными данными существует определенное соотношение между частотой и фазой входных данных и сигнала ГУН: задний фронт сигнала ГУН тактирует данные так, что задний фронт сигнала совмещен с серединой импульса данных. На фиг. 2а представлено правильное соотношение фаз указанных сигналов в случае входных данных формата CMI. Триггеры 8 и 9 включены по схеме делителя частоты. При этом выходной сигнал триггера 9 сдвинут на 90o относительно выходного сигнала триггера 8. Задние фронты сигнала формата CMI совмещены с серединой импульса выходного сигнала триггера 9. Поэтому в триггер 10 в режиме синхронизации всегда записывается "1". Если сигнал ГУН 5 по фазе опережает сигнал входных данных, то, как видно из фиг.2б, в некоторый момент времени по заднему фронту в триггер 10 записывается "0". Так как в этом случае сигнал fтакт ГУН не может тактировать данные из-за рассовмещения фронтов, то сигнал оказывается не синхронизированным с входными данными. Если входные данные опережают сигнал ГУН 5, то по заднему фронту в триггер 10 также будет записываться "0". Таким образом, уровень сигнала на выходе триггера 10 служит для контроля состояния синхронизации сигнала ГУН 5 и входных данных, при этом уровень "1" соответствует наличию синхронизации, а "0" - отсутствию синхронизации.

Если перед потерей синхронизации в триггер 10 была записана "1", то при потере синхронизации будет записан "0" и на тактовом входе триггера 11 будет сформирован импульс, по заднему фронту которого в этот триггер запишется информация с выхода триггера 8, а именно "0", если сигнал ГУН 5 опережает сигнал входных данных (фиг.2б), и "1", если сигнал ГУН 5 отстает по фазе от сигнала входных данных.

На фиг.3 представлено правильное соотношение фаз сигнала ГУН 5 и входных данных в случае сигнала формата NRZ. При этом частота генерации ГУН 5 равна удвоенной частоте кодообразования. Из сравнения фиг. 2а и 3 следует, что для данных в формате NRZ справедливы те же фазовые соотношения, что и для данных в формате CMI, т.е. сигналы индикации состояния (наличия или отсутствия) синхронизации и опережения/запаздывания формируются при тех же фазовых соотношениях.

Прямой или инверсный сигнал индикации синхронизации подается на вход мультиплексора 3. В варианте по фиг.3 сигнал с инверсного выхода триггера 10 используется как управляющий в мультиплексоре 3. В частности, если на инверсном выходе триггера 10 формируется низкий уровень, т.е. устройство в режиме синхронизации, то фазовый детектор 1 подключается к аналоговому сумматору 2. Если же на инверсном выходе триггера 10 сформирован высокий уровень, то на соответствующий вход аналогового сумматора 2 подается постоянный уровень с триггера 11. Как показано на фиг.1, выход мультиплексора 3 соединен с вычитающим входом аналогового сумматора 2. Из фиг.2б следует, что при опережении входных данных сигналом ГУН 5 на выходе триггера 11 формируется низкий уровень. ФНЧ 4 преобразует постоянный низкий уровень на вычитающем входе аналогового сумматора 2 в нарастающее во времени напряжение, подаваемое в качестве управляющего сигнала на ГУН 5, в результате чего будет обеспечено уменьшение частоты ГУН 5. Если частота ГУН 5 должна увеличиваться при увеличении напряжения, то необходимо использовать инверсный выход триггера 11. Следовательно, при нарушении синхронизации обеспечивается сканирование частоты ГУН 5 таким образом, чтобы устранить рассогласование по частоте и фазе между сигналом ГУН 5 и входными данными. При наличии синхронизации (фиг. 2а и фиг. 3) сигнал индикации инвертируется, и второй выход фазового детектора 1 подключается к вычитающему входу аналогового сумматора 2. Если ошибка рассогласования невелика, то устройство поддерживает синхронизацию только за счет петли ФАПЧ с фазовым детектором. Если ошибка велика, то режим синхронизации достигается за несколько итераций. При синхронизации входные данные записываются в решающее устройство 6, причем в качестве синхроимпульсов используется сигнал ГУН 5. На выходе решающего устройства 6 данные появляются синхронно с импульсами сигнала ГУН 5.

При наличии помехи в линии в описанном выше устройстве синхронизации возможно ложное срабатывание, приводящее к нежелательному сканированию частоты ГУН 5. Для устранения этого в устройство синхронизации может быть введен цифровой интегратор 12 (фиг. 4) на основе регистра сдвига 13 с параллельными выходами, который тактируется передним фронтом входного сигнала, и логической схемы И 14, формирующей высокий уровень, когда в регистре сдвига 13 содержатся только единицы. В данном варианте выполнения требуемый для начала сканирования частоты ГУН 5 уровень сигнала, индицирующего отсутствие синхронизации, формируется при многократно регистрируемом на инверсном выходе триггера 10 состоянии отсутствия синхронизации. Длина регистра сдвига 13 выбирается с учетом вероятного значения максимальной длительности помехи для обеспечения ослабления помехи.

Устройство синхронизации цифрового приемника, выполненное в соответствии с изобретением, может быть использовано в синхронных цифровых системах связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА СПУТНИКОВОЙ СВЯЗИ | 1994 |

|

RU2117392C1 |

| СПОСОБ И УСТРОЙСТВО ПЕРЕДАЧИ СООБЩЕНИЙ ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 1995 |

|

RU2127486C1 |

| СИСТЕМА СПУТНИКОВОЙ СВЯЗИ | 1994 |

|

RU2116699C1 |

| СЛЕДЯЩИЙ ПРИЕМНИК ШИРОКОПОЛОСНОГО СИГНАЛА | 1994 |

|

RU2113763C1 |

| СИСТЕМА СВЯЗИ С ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 1995 |

|

RU2115236C1 |

| УСТРОЙСТВО ЗАПИСИ ЦИФРОВОГО СИГНАЛА | 1995 |

|

RU2155388C2 |

| СИСТЕМА СВЯЗИ С ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 1993 |

|

RU2113762C1 |

| АСИНХРОННАЯ СИСТЕМА СВЯЗИ С ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 1995 |

|

RU2127022C1 |

| УСТРОЙСТВО МАГНИТНОЙ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОГО СИГНАЛА (ВАРИАНТЫ) | 1994 |

|

RU2127913C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА РАДИОСВЯЗИ С ПОВТОРНЫМ ИСПОЛЬЗОВАНИЕМ ЧАСТОТЫ | 1996 |

|

RU2114510C1 |

Изобретение относится к области передачи дискретной информации, а именно к устройству синхронизации приемника с передатчиком с использованием характеристик цифрового сигнала для управления фазой генератора, управляемого напряжением. Технический результат - сокращение времени вхождения в синхронизм и допустимой ошибки рассогласования по частоте и фазе. Сущность изобретения: в устройстве обеспечивается непрерывное сравнение в блоке определения состояния синхронизации времени появления задних фронтов входных данных и сигнала генератора, управляемого напряжением. При потере синхронизации указанный блок формирует сигналы, индицирующие отсутствие синхронизации и опережение/отставание путем определения соотношения частот и фаз сигнала выходных данных и сигнала генератора, управляемого напряжением. Уровень сигнала индикации опережения/отставания устанавливается таким, чтобы он соответствовал уровню сигнала на выходе фазового детектора. 2 с. и 2 з.п. ф-лы, 4 ил.

| US 4115745 A, 19.09.78 | |||

| US 4135165 A, 16.01.79 | |||

| US 5148123 A, 15.09.92 | |||

| US 3535651 A, 20.10.70 | |||

| US 4464771 A, 07.08.81 | |||

| US 4388598 A, 14.06.83 | |||

| US 4757279 A, 12.07.88 | |||

| US 5367545 A, 22.11.94 | |||

| НАГОЛОВНИК ДЛЯ ЗАКРЕПЛЕНИЯ ВИБРОПОГРУЖАТЕЛЯ НА ТРУБЕ С ФЛАНЦЕМ | 0 |

|

SU360442A1 |

| Устройство для управления работой полиграфической ниткошвейной машины | 1951 |

|

SU98705A1 |

| Устройство фазовой автоподстройки частоты | 1987 |

|

SU1450109A1 |

| Поисковая система фазовой автоподстройки частоты | 1982 |

|

SU1256200A1 |

Авторы

Даты

1999-09-27—Публикация

1996-12-24—Подача