Изобретение относится к устройству для записи цифрового сигнала, записывающему раздельную без возвращения к нулю с обращением на ЕДИНИЦАХ (I-NRZI) модуляцию, которая содержит управляющие сигналы, применяемые для трекинга головки во время воспроизведения.

Уровень техники

В устройстве записи/воспроизведения таком, как видеомагнитофон, по мере отклонения головки от дорожки среды магнитной записи во время воспроизведения ухудшается сигнал, поступающий от головки, и возрастают ошибки. Это препятствует нормальному воспроизведению изображения, так что необходимо, чтобы головка точно следовала нужной дорожке. Другими словами, необходимо осуществлять трекинг головки. Для того, чтобы увеличить время записи в видеомагнитофонах с цифровой записью, предназначенных для домашнего пользования, дорожки делаются особенно узкими, что увеличивает необходимую для удовлетворительного воспроизведения изображения точность трекинга головки. Среди способов для определения ошибки трекинга головки или отклонения от идеального трекинга имеются способы, использующие различные ответные управляющие сигналы для последующих дорожек для облегчения сравнения перекрестных помех управляющих сигналов от предшествующих дорожек и последующей дорожки, которой наиболее точно следует головка, чтобы определить, в какую сторону отклоняется трекинг головки, в сторону предшествующей дорожки или в сторону последующей дорожки. Управляющие сигналы принимают форму пиков и провалов в частном спектре цифровых сигналов, записываемых на дорожки путем выборочной записи одной из двух типов раздельной без возврата к нулю с обращением на ЕДИНИЦАХ (I-NRZI) модуляции. Эта же информация предварительно кодируется в два параллельных во времени множества последовательно передаваемых слов канала, и слова канала, которые выбираются из одного или другого множества для управления I-NRZI модуляцией в течение записи, выбираются так, чтобы I-NRZI модуляция имела наименьшее отклонение от критерия управляющего сигнала для каждой записывающей дорожки. После окончания выбора слова канала активизируется информация предварительного кодирования, загруженная в предварительный кодер, который не генерировал выбранное слово канала для подтверждения заранее закодированной информации, загруженной в предварительный кодер, который генерировал выбранное слово канала. Это делается для обеспечения непрерывности процедур предварительного кодирования и процедур декодирования, следующих за I-NRZI модуляцией, восстановленной из среды записи в течение воспроизведения и демодуляции. После завершения выбора слова канала интеграторы в схеме для определения, какое слово канала должно быть выбрано, должны обновлять свое содержимое, чтобы отразить, какое слово канала было выбрано фактически для записи. Такие методы описаны в патенте США N 5142421, опубликованном 24 августа 1992 года на имя Kahlman (Кальман) и др., озаглавленном "УСТРОЙСТВО ДЛЯ ЗАПИСИ ЦИФРОВОГО ИНФОРМАЦИОННОГО СИГНАЛА НА НОСИТЕЛЬ ЗАПИСИ" и приведенном здесь в качестве ссылки.

В этом патенте США N 5142421 осуществление I-NRZI модуляции осуществляется на основе последовательных битов. Это не пригодно для работы в магистральной линии связи, где слова канала, выбранные из предварительных кодеров последовательных битов, записываются в среду магнитной записи после некоторого фиксированного запаздывания для приспособления цепи выбора. После генерации соответствующей пары слов канала требуется некоторое время для выполнения процедуры принятия решения, которая определяет, которое из них будет записано. После процедуры принятия решения необходимо еще некоторое время для обновления загруженной в предварительные кодеры информации. Эти процедуры решения и обновления должны быть завершены до того, как будет возможна дальнейшая запись, так что запаздывания, вызванные этими процедурами решения и обновления, создают некоторые разрывы в непрерывном потоке битов по мере непрерывного тактирования способами синхронного тактирования. Соответственно, должна быть выделена память буфера первым пришел/первым ушел, которая может быть периодически считана до предварительных кодеров последовательных битов, и память буфера первым пришел/первым ушел, в которую можно осуществлять периодическую запись посредством выбранных слов канала и затем непрерывно считывать, должна быть предоставлена для слов канала, сгенерированных предварительными кодерами последовательных битов. Генерация сигналов тактирования для памяти буфера является в некоторой степени сложной, поэтому желательно избегать использования памяти буфера периодической записи и считывания.

Заявка, озаглавленная "УСТРОЙСТВО ДЛЯ ЗАПИСИ ЦИФРОВОГО СИГНАЛА", поданная 7 июня 1995 года изобретателем по настоящей заявке, приведена здесь в качестве ссылки как не имеющей существенного отношения к делу. В этой заявке автор настоящего изобретения г-н Soon-Tae Kim описывает использование предварительных кодеров параллельных битов совместно с преобразователями параллельных битов в последовательные биты (P/S), для использования обработки в магистральной линии осуществленной I-NRZI модуляции и чтобы избавиться от необходимости в памяти буфера периодической записи или периодического чтения. Процедуры предварительного кодирования на начальных шагах осуществления I-NRZI модуляции в общем случае осуществляются путем применения первого и второго предварительных кодеров типа 2T для параллельной генерации пары множеств слов канала, из которых выбираются слова канала для записи. Как указали Kahlman и др., когда префиксы единичных битов присоединяются к информационным словам, предварительно закодированным вторым и первым предварительными кодерами 2T типа, то соответствующие места нечетных битов в соответствующих словах канала, которые они сгенерировали, одновременно являются битовыми дополнениями друг друга, а соответствующие места четных битов в этих словах канала остаются без изменения. Это свойство используется для уменьшения количества преобразований параллельных битов в последовательные, необходимых после первого и второго предварительных кодеров параллельных битов 2T типа, в определенном устройстве записи цифрового сигнала, описанном в одновременно изданной заявке изобретателя, указанной выше.

В исполнениях изобретения, описанных здесь, это свойство используется для осуществления I-NRZI модуляции, используя одиночный предварительный кодер типа 2T для генерации первого из пары совместных слов канала и получения второго слова канала этой пары из первого путем битового дополнения его мест нечетных битов и сохраняя неизменными свои места четных битов. В частности, заманчиво использовать одиночный предварительный кодер 2T типа, когда предварительное кодирование выполняется на основе параллельных битов, в то время как имеется значительное количество вентилей исключающих ИЛИ и значительное количество битовых защелок в предварительном кодере параллельных битов 2T типа, как это описано в приведенной выше одновременно изданной заявке изобретателя.

Сущность изобретения

Настоящее изобретение осуществлено в устройстве записи цифрового сигнала, которое осуществляет раздельно без возврата к нулю с обращением на ЕДИНИЦАХ (I-NRZI) модуляцию, используя одиночный предварительный кодер 2T типа. В предпочтительных исполнениях настоящего изобретения одиночным предварительным кодером 2T типа является тот, который осуществляет собственно кодирование каждого информационного слова на основе параллельных битов, для использования обработки в магистральной линии осуществляемой I-NRZI модуляции и для предотвращения необходимости использования памяти буфера для периодической записи или периодического считывания.

В конкретных исполнениях настоящего изобретения, используемых для записи телевизионных сигналов, создаются условия для осуществления I-NRZI модулями, используя тот же самый предварительный кодер 2T типа для информации синхронизации и обработки, а также для видео- и аудиоинформации. Пилот-сигналы, вводимые в процессе записи видео- и аудиоинформации, продолжают свое воздействие посредством записи информации синхронизации и обработки.

Устройство для записи цифрового сигнала, использующее для записи перемещающуюся без возврата к нулю с инверсией на ЕДИНИЦАХ (I-NRZI) модуляцию, содержит порт ввода для приема информационных слов с n-параллельными битами, n является четным положительным числом; предварительный кодер для кодирования информационных слов с (n+1)-параллельными битами, которые формируются путем ввода бита управления с заранее определенной величиной в каждое информационное слово с n-параллельными битами, предварительный кодер предназначен для создания первого из двух типов (n+1)-битовых слов канала раньше второго из двух типов (n+1)-битовых слов канала, которое вырабатывается, когда бит управления имеет противоположную битовую величину, сопряженную с величиной заранее определенного бита, предварительный кодер инициализируется в соответствии с первым сигналом управления; мультиплексор с временным разделением для выделения каждого слова канала (n+1)-параллельными битами, передаваемого от предварительного кодера в первую группу битов, биты которой должны быть преобразованы в дополнительные там, где заранее определенная битовая величина бита управления будет сопряженной по отношению к заранее определенной битовой величине, и во вторую битовую группу, биты которой должны оставаться неизменными, когда заранее определенная битовая величина бита управления будет сопряженной по отношению к заранее определенной битовой величине, для передачи первой и второй группы битов совместно; первый преобразователь параллельного в последовательное для генерации первого сигнала последовательных битов путем преобразования каждого слова канала с (n+1)-параллельными битами первого типа, передаваемого от предварительного кодера в слово канала с (n+1)-последовательными битами первого типа; второй преобразователь параллельного в последовательное для генерации второго сигнала с последовательными битами путем преобразования в дополнительные только битов из первой группы битов в слове канала с (n+1)-параллельными битами, передаваемого от предварительного кодера и затем преобразовав результирующее слово канала с (n+1)-параллельными битами второго типа в слово канала с (n+1)-последовательными битами второго типа; устройство записи на параллельных дорожках среды для записи (I-NRZI) модуляции в соответствии с I-NRZI кодом, который генерируется путем выбора выходного сигнала одного из преобразователей параллельного в последовательный и выходного сигнала второго преобразователя параллельно в последовательный, выбор должен осуществляться в ответ на второй сигнал управления; генератор сигнала управления, чувствительный к первым и вторым группам битов совместно передаваемых мультиплексором с временным разделением, для генерирования первых и вторых сигналов управления, первые и вторые сигналы управления генерируются так, чтобы указывать какие из первых и вторых сигналов последовательных битов должны быть выбраны для включения в код для того, чтобы минимизировать отклонение I-NRZI модуляции от спектральной характеристики, предписанной одной из дорожек, на которых ведется запись в текущий момент.

Предварительный кодер является 2T предварительным кодером для I-NRZI кодирования (n+1)-битовых информационных слов, формируемых путем присоединения бита управления с заранее определенной битовой величиной к каждому информационному слову с параллельными битами в качестве соответствующего префиксного бита, (n+1)-битовые информационные слова формируются путем присоединения соответствующего НУЛЕВОГО префиксного бита к каждому информационному слову с n-параллельными битами.

Кроме того, мультиплексор с временным разделением содержит третий преобразователь параллельного в последовательное для преобразования первой группы битов после выбора слова канала с (n+1)-параллельными битами упомянутого первого типа, передаваемого от предварительного кодера, в нечетные слова канала с последовательными битами и четвертый преобразователь параллельного в последовательное для преобразования второй группы битов, выбранных в качестве слова канала с (n+1)-параллельными битами первого типа, передаваемого от предварительного кодера в нечетные слова канала с последовательными битами.

Генератор сигнала управления содержит цепь для генерации первого и второго сигнала управления, которая действует в зависимости от того, превысил ли второй сигнал ошибки сигнал первой ошибки по амплитуде или нет; первую цепь для аддитивного объединения единичных параметров, полярности которых определяются битами каждого нечетного слова канала с последовательными битами, передаваемого от мультиплексора с временным разделением, с другими одиночными параметрами, полярности которых определяются битами каждого четного слова канала с последовательными битами совместно передаваемого от мультиплексора с временным разделением, для генерации первых результатов объединения; первый интегратор для интегрирования первых результатов объединения совместно с исходной величиной интегрирования интегратора, для генерирования первого выходного сигнала интегратора, который равен величине первой цифровой сумме обработки, которая должна быть получена, если слово канала первого типа было выбрано следующим для записи; вторую цепь для дифференцированного объединения единичных параметров, полярности которых определяются битами, каждого нечетного слова канала, передаваемого от мультиплексора с временным разделением, с другими единичными параметрами, полярности которых определяются битами каждого четного слова канала с последовательными битами совместно передаваемого от мультиплексора с временным разделением, для генерации вторых результатов объединения; второй интегратор для интегрирования вторых результатов объединения совместно с исходной величиной интегрирования второго интегратора, чтобы таким образом генерировать выходной сигнал второго генератора, равный величине второй цифровой суммы обработки, которая будет получена, если слово канала второго типа будет выбрано следующим для записи, исходные величины первого и второго интеграторов остаются теми же и равны одному из выходных сигналов первого и второго интеграторов для слова канала, ранее выбранного для записи; цепь для вычисления энергии любого отклонения первой цифровой суммы обработки от предписанной величины цифровой суммы обработки для одной из дорожек, которые записываются в текущий момент, результат вычисления энергии любого отклонения первой цифровой суммы обработки включается в первый сигнал ошибки; и цепь для вычисления энергии любого отклонения второй цифровой суммы от предписанной величины цифровой суммы обработки для одной из дорожек, которые записываются в текущий момент, результат вычисления энергии любого отклонения второй цифровой суммы включается во второй сигнал ошибки.

Генератор сигнала управления дополнительно содержит цепь для генерации треугольной волны предписанной первой частоты в качестве величины цифровой суммы обработки, когда каждая из первого набора дорожек записывается; цепь для генерации встречающихся нечетным образом последующих образцов дискретизированных данных системой функции синусоидальной волны второй частоты и умножающую их на соответствующие единичные параметры, полярности которых определяются битами каждого четного слова канала с последовательными битами, передаваемого от мультиплексора с временным разделением для генерации первого потока произведений; цепь для генерации встречающихся нечетным образом последующих образцов дискретизированных данных системой функции синусоидальной волны второй частоты и перемножающую их на соответствующие единичные параметры, полярности которых определяются битами каждого нечетного слова канала с последовательными битами, передаваемого от мультиплексора с временным разделением для генерации второго потока произведений; третью цепь аддитивного объединения первого и второго потоков произведений для генерации третьих результатов объединения; третий интегратор для интегрирования третьих результатов объединения совместно с исходной величиной интегрирования третьего интегратора, так чтобы сгенерировать выходной сигнал третьего интегратора; цепь для вычисления энергии выходного сигнала третьего интегратора, результат вычисления энергии выходного сигнала третьего интегратора включается в первый сигнал ошибки; четвертую цепь объединения для дифференциального объединения первого и второго потоков произведений для генерации четвертых результатов объединения; четвертый интегратор для интегрирования четвертых результатов объединения совместно с исходной величиной интегрирования четвертого интегратора, так чтобы сгенерировать выходной сигнал четвертого интегратора, третья и четвертая исходные величины интегрирования остаются теми же и равными одному из выходных сигналов упомянутого третьего и четвертого интеграторов для слова канала, ранее выбранного для записи; цепь для вычисления энергии выходного сигнала четвертого интегратора, результат вычисления энергии выходного сигнала четвертого интегратора включается во второй сигнал ошибки; цепь для генерации встречающихся четным образом последующих образцов дискретизированных данных системной функции косинусоидальной волны второй частоты и умножающую их на соответствующие единичные параметры, полярности которых определяются битами каждого четного слова канала с последовательными битами, передаваемого от мультиплексора с временным разделением, для генерации третьего потока произведений; цепь для генерации встречающихся нечетным образом последующих образцов дискретизированных данных системной функции косинусоидальной волны второй частоты и умножающую их на соответствующие единичные параметры, полярности которых определяются битами каждого нечетного слова канала с последовательными битами, передаваемого от мультиплексора с временным разделением, для генерации четвертого потока произведений; пятую цепь аддитивного объединения третьего и четвертого потоков произведений для генерации пятых результатов объединения; пятый интегратор для интегрирования пятых результатов объединения совместно с исходной величиной интегрирования пятого интегратора, так чтобы сгенерировать выходной сигнал пятого интегратора; цепь для вычисления энергии выходного сигнала пятого интегратора, результат вычисления энергии выходного сигнала пятого интегратора включается в первый сигнал ошибки; шестую цепь объединения для дифференцированного объединения третьего и второго потоков произведений для генерации шестых результатов объединения; шестой интегратор для интегрирования шестых результатов объединения совместно с исходной величиной шестого интегратора, так чтобы сгенерировать выходной сигнал шестого интегратора, исходные величины интегрирования пятого и шестого интеграторов остаются теми же и равными одному из выходных сигналов пятого и шестого интеграторов для слова канала, ранее выбранного для записи, и цепь для вычисления энергии выходного сигнала шестого интегратора, результат вычисления энергии выходного сигнала шестого интегратора включается во второй сигнал ошибки.

Генератор сигнала управления дополнительно содержит цепь для генерации встречающихся четным образом последующих образцов системной функции прямоугольной волны первой частоты и объединяющую их с соответствующими единичными параметрами, полярности которых определяются битами каждого четного слова канала с последовательными битами, передаваемого от мультиплексора с временным разделением, для генерации первого потока сомножителей; цепь для генерации встречающихся нечетным образом последующих образцов системной функции прямоугольной волны первой частоты и объединяющую их с соответствующими единичными параметрами, полярности которых определяются битами, каждого нечетного слова канала с последовательными битами, передаваемого от мультиплексора с временным разделением, для генерации второго потока сомножителей; цепь для генерации встречающихся четным образом последующих образцов дискретизированных данных системной функции синусоидальной волны первой частоты и умножающую их на соответствующие образцы первого потока сомножителей, для генерации пятого потока произведений; цепь для генерации встречающихся нечетным образом последующих образцов дискретизированных данных системной функции синусоидальной волны первой частоты и умножающую их на соответствующие образцы первого потока сомножителей, для генерации шестого потока произведений; седьмую цепь аддитивного объединения пятого и шестого потоков произведений для генерации седьмых результатов объединения; седьмой интегратор для интегрирования седьмых результатов объединения совместно с исходной величиной интегрирования седьмого интегратора, так чтобы сгенерировать выходной сигнал седьмого интегратора; цепь для вычисления энергии выходного сигнала седьмого интегратора, результат вычисления энергии выходного сигнала седьмого интегратора включается в упомянутый первый сигнал ошибки; восьмую цепь для дифференциального объединения пятых и шестых потоков произведений для генерации восьмых результатов объединения; восьмой интегратор для интегрирования восьмых результатов объединения совместно с исходной величиной интегрирования восьмого интегратора, так чтобы сгенерировать выходной сигнал восьмого интегратора, исходные величины седьмого и восьмого интеграторов остаются теми же и равными одному из выходных сигналов седьмого и восьмого интеграторов для слова канала, ранее выбранного для записи; цепь для вычисления энергии выходного сигнала восьмого интегратора, результат вычисления энергии выходного сигнала восьмого интегратора включается во второй сигнал ошибки; цепь для генерации встречающихся четным образом последующих образцов дискретизированных данных системной функции косинусоидальной волны первой частоты и умножающую их на соответствующие образцы второго потока сомножителей, для генерации седьмого потока произведений; цепь для генерации встречающихся нечетным образом последующих образцов дискретизированных данных системной функции косинусоидальной волны первой частоты и умножающую их на соответствующие образцы второго потока сомножителей для генерации восьмого потока произведений; девятую цепь для аддитивного объединения седьмого и восьмого потоков произведений для генерации девятых результатов объединения; девятый интегратор для интегрирования девятых результатов объединения совместно с исходной величиной интегрирования девятого интегратора, так чтобы генерировать выходной сигнал девятого интегратора; цепь для вычисления энергии выходного сигнала девятого интегратора, результат вычисления энергии выходного сигнала девятого интегратора включается в первый сигнал ошибки; десятую цепь для дифференцированного объединения седьмого и восьмого потоков произведений для генерации десятых результатов объединения; десятый интегратор для интегрирования десятых результатов объединения совместно с исходной величиной интегрирования десятого интегратора, так чтобы сгенерировать выходной сигнал десятого интегратора, девятые и десятые исходные величины интегрирования остаются теми же и равными одному из выходных сигналов девятого и десятого интегратора для слова канала, ранее выбранного для записи; и цепь для вычисления энергии выходного сигнала десятого интегратора, результат вычисления энергии выходного сигнала десятого интегратора включается во второй сигнал ошибки.

Генератор сигнала управления дополнительно содержит цепь для генерации встречающихся четным образом последующих образцов системной функции прямоугольной волны первой частоты и объединяющую их с соответствующими единичными параметрами, полярности которых определяются битами каждого четного слова канала с последовательными битами, передаваемого от мультиплексора с временным разделением для генерации первого потока сомножителей; цепь для генерации встречающихся нечетным образом последующих образцов системной функции прямоугольной волны первой частоты и объединяющую их с соответствующими единичными параметрами, полярности которых определяются битами каждого нечетного слова канала с последовательными битами, передаваемого от мультиплексора с временным разделением, для генерации второго потока сомножителей; цепь для генерации встречающихся четным образом последующих образцов дискретизированных данных системной функции синусоидальной волны первой частоты и умножающую их на соответствующие образцы первого потока сомножителей для генерации первого потока произведений; цепь для генерации встречающихся нечетным образом последующих образцов дискретизированных данных системной функции синусоидальной волны первой частоты и умножающую их на соответствующие образцы первого потока сомножителей для генерации второго потока произведений; третью цепь для аддитивного объединения первого и второго потоков произведений для генерации третьих результатов объединения; третий интегратор для интегрирования третьих результатов объединения совместно с исходной величиной интегрирования третьего интегратора, так чтобы сгенерировать выходной сигнал третьего интегратора; цепь для вычисления энергии выходного сигнала третьего интегратора, результат вычисления энергии выходного сигнала третьего интегратора включается в первый сигнал ошибки; четвертую цепь для дифференцированного объединения первых и вторых потоков произведений для генерации четвертых результатов объединения; четвертый интегратор для интегрирования четвертых результатов объединения совместно с исходной величиной интегрирования четвертого интегратора, чтобы сгенерировать выходной сигнал четвертого интегратора, третья и четвертая исходные величины интегрирования остаются теми же и равными одному из выходных сигналов третьего и четвертого интеграторов для слова канала, ранее выбранного для записи; цепь для вычисления энергии выходного сигнала четвертого интегратора, результат вычисления энергии выходного сигнала четвертого интегратора включается во второй сигнал ошибки; цепь для генерации встречающихся четным образом последующих образцов дискретизированных данных системной функции косинусоидальной волны первой частоты и умножающую их на соответствующие образцы второго потока сомножителей для генерации третьего потока произведений; цепь для генерации встречающихся нечетным образом последующих образцов дискретизированных данных системной функции косинусоидальной волны первой частоты и умножающую их на соответствующие образцы второго потока сомножителей для генерации четвертого потока произведений, пятую цепь для аддитивного объединения третьего и четвертого потоков произведений для генерации пятых результатов объединения; пятый интегратор для интегрирования пятых результатов объединения совместно с исходной величиной интегрирования пятого интегратора, так чтобы сгенерировать выходной сигнал пятого интегратора; цепь для вычисления энергии выходного сигнала пятого интегратора, результат вычисления энергии выходного сигнала пятого интегратора включается в первый сигнал ошибки; шестую цепь для дифференцированного объединения третьего и четвертого потоков произведений для генерации шестых результатов объединения; шестой интегратор для интегрирования шестых результатов объединения совместно с исходной величиной интегрирования шестого интегратора, чтобы сгенерировать выходной сигнал шестого интегратора, пятые и шестые исходные величины интегрирования остаются теми же и равными одному из выходных сигналов пятого и шестого интеграторов для слова канала, ранее выбранного для записи; и цепь для вычисления энергии выходного сигнала шестого интегратора, результат вычисления энергии выходного сигнала шестого интегратора включается во второй сигнал ошибки.

Кроме того, генератор сигнала управления содержит цепь для генерации первого и второго сигналов управления, которые генерируются в зависимости от того, был ли первый сигнал ошибки превышен по амплитуде вторым сигналом ошибки или нет; цепь для генерации встречающихся четным образом последующих образцов дискретизированных данных системной функции синусоидальной волны с частотой, имеющей минимальное значение, и умножающую их на соответствующие единичные параметры, полярности которых определяются битами каждого четного слова канала с последовательными битами, передаваемого от мультиплексора с временным разделением, для генерации первого потока произведений; цепь для генерации встречающихся нечетным образом последующих образцов даскретизированных данных системной функции синусоидальной волны частоты с минимальным значением и умножающую их на соответствующие единичные параметры, полярности которых определяются битами каждого четного слова канала с последовательными битами, передаваемого от мультиплексора с временным разделением, для генерации первого потока произведений; цепь для генерации встречающихся нечетным образом последующих образцов дискретизированных данных системной функции синусоидальной волны частоты с минимальным значением и умножающую их на соответствующие единичные параметры, полярности которых определяются битами каждого нечетного слова канала с последовательными битами, передаваемого от мультиплексора, с совместным временем, для генерации второго потока произведений; третью цепь для аддитивного объединения первого и второго потоков произведений для генерации третьих результатов объединения; третий интегратор для интегрирования третьих результатов объединения совместно с исходной величиной интегрирования третьего интегратора, чтобы сгенерировать выходной сигнал третьего интегратора; цепь для вычисления энергии выходного сигнала третьего интегратора, результат вычисления энергии выходного сигнала третьего интегратора включается в первый сигнал ошибки; четвертую цепь для дифференцированного объединения первого и второго потоков произведений для генерации четвертых результатов объединения; четвертый интегратор для интегрирования четвертых результатов объединения совместно с исходной величиной интегрирования четвертого интегратора, чтобы сгенерировать выходной сигнал четвертого интегратора, третьи и четвертые исходные величины интегрирования остаются теми же и равными одному из выходных сигналов третьего и четвертого интеграторов для слова канала, ранее выбранного для записи; цепь для вычисления энергии выходного сигнала четвертого интегратора, результат вычисления энергии выходного сигнала четвертого интегратора включается во второй сигнал ошибки; цепь для генерации встречающихся четным образом последующих образцов дискретизированных данных системной функции косинусоидальной волны частоты с минимальным значением и умножающую их на соответствующие единичные параметры, полярности которых определяются битами каждого четного слова канала с последовательными битами, передаваемого от мультиплексора с совместным временем, для генерации третьего потока произведений; цепь для генерации встречающихся нечетным образом последующих образцов дискретизированных данных системной функции косинусоидальной волны частоты с минимальным значением и умножающую их на соответствующие единичные параметры, полярности которых определяются битами каждого нечетного слова канала с последовательными битами, передаваемого от мультиплексора с временным разделением, для генерации четвертого потока произведений; пятую цепь объединения аддитивного объединения третьего и четвертого потоков произведений для генерации пятых результатов объединения; пятый интегратор для интегрирования пятых результатов объединения совместно с исходной величиной интегрирования пятого интегратора, чтобы сгенерировать выходной сигнал пятого интегратора; цепь для вычисления энергии выходного сигнала пятого интегратора, результат вычисления энергии выходного сигнала пятого интегратора включается в первый сигнал ошибки; шестую цепь для дифференцированного объединения третьего и четвертого потоков произведений для генерации шестых результатов объединения; шестой интегратор для интегрирования шестых результатов объединения совместно с исходной величиной интегрирования шестого интегратора, чтобы сгенерировать в выходной сигнал шестого интегратора, пятые и шестые исходные величины интегрирования остаются теми же и равными выходному сигналу одного из пятого и шестого интегратора для слова канала, ранее выбранного для записи; и цепь для вычисления энергии выходного сигнала шестого интегратора, результат вычисления энергии выходного сигнала шестого интегратора включается во второй сигнал ошибки.

В устройстве каждая из параллельных дорожек среды для записи имеет исходную вторую часть дорожки, куда записывается предварительная информация, имеет последующую первую часть дорожки, где записывается видеоинформация, имеет последующую четвертую часть дорожки, где записывается информация обработки, имеет конечную пятую часть дорожки, где записывается заключительная информация; данные синхронизации записываются в начало соответствующих строк первой и третьей частей дорожек, куда записывается видео- и аудиоинформация; информационное слово данных обработки, записываемое в четвертую часть дорожки для управления схемой фазовой автоподстройки, используемой для определения бита в течение воспроизведения из среды записи, станут более очевидны после детального описания его предпочтительного исполнения со ссылкой на приложенные чертежи, на которых:

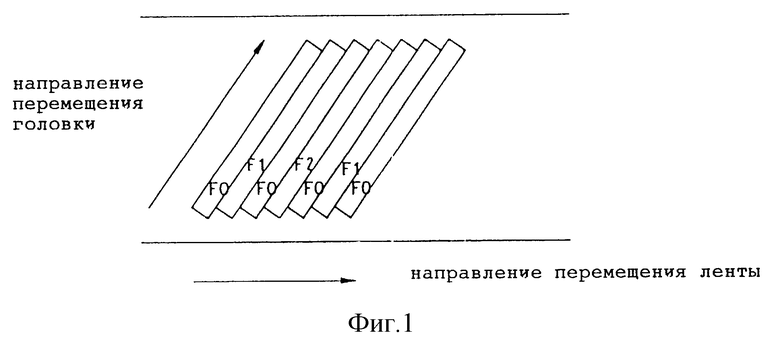

фиг. 1 изображает иллюстративный образец записи потока последовательных данных слов канала в смежные параллельные дорожки на поверхности среды магнитной записи;

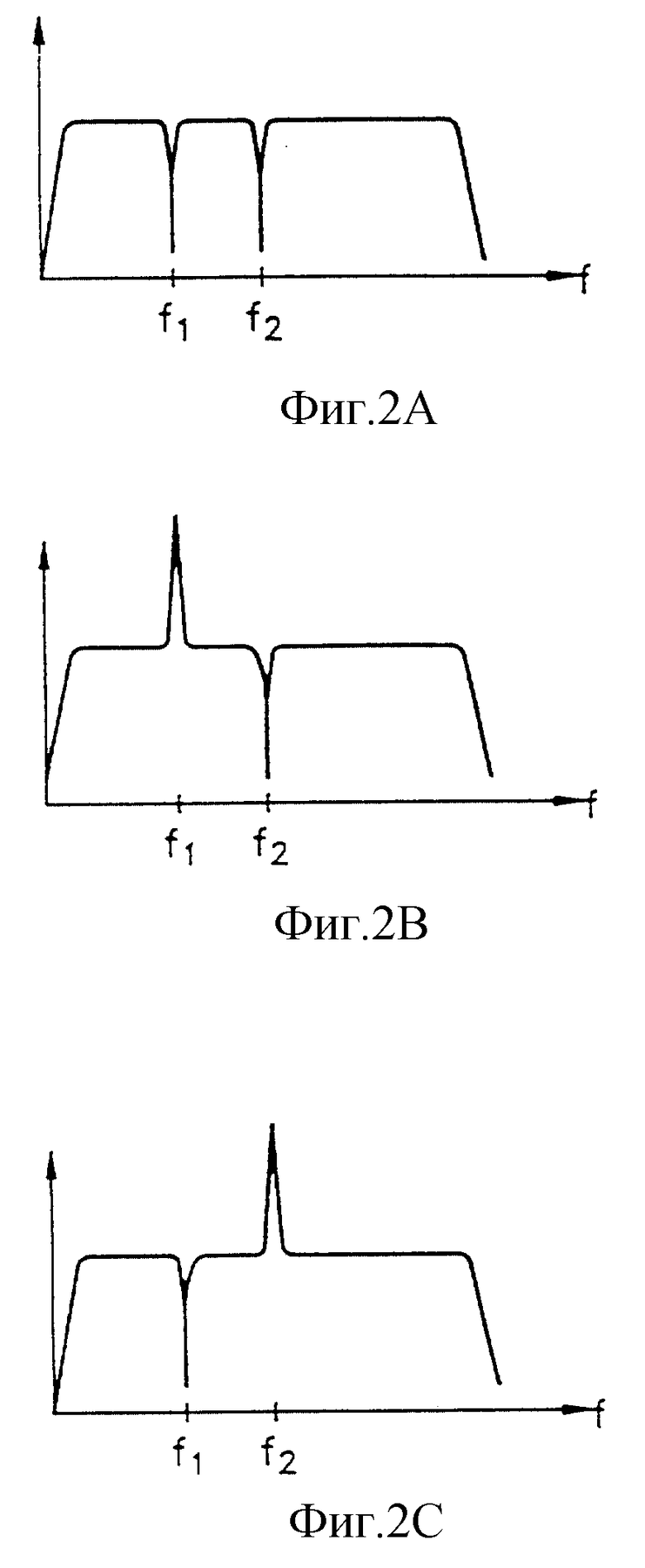

фиг. 2A, 2B и 2C иллюстрируют спектр частот, связанный с образцом, показанным на фиг. 1;

фиг. 3 является блок-схемой известного устройства записи цифрового сигнала, описанной в патенте США N 5142421;

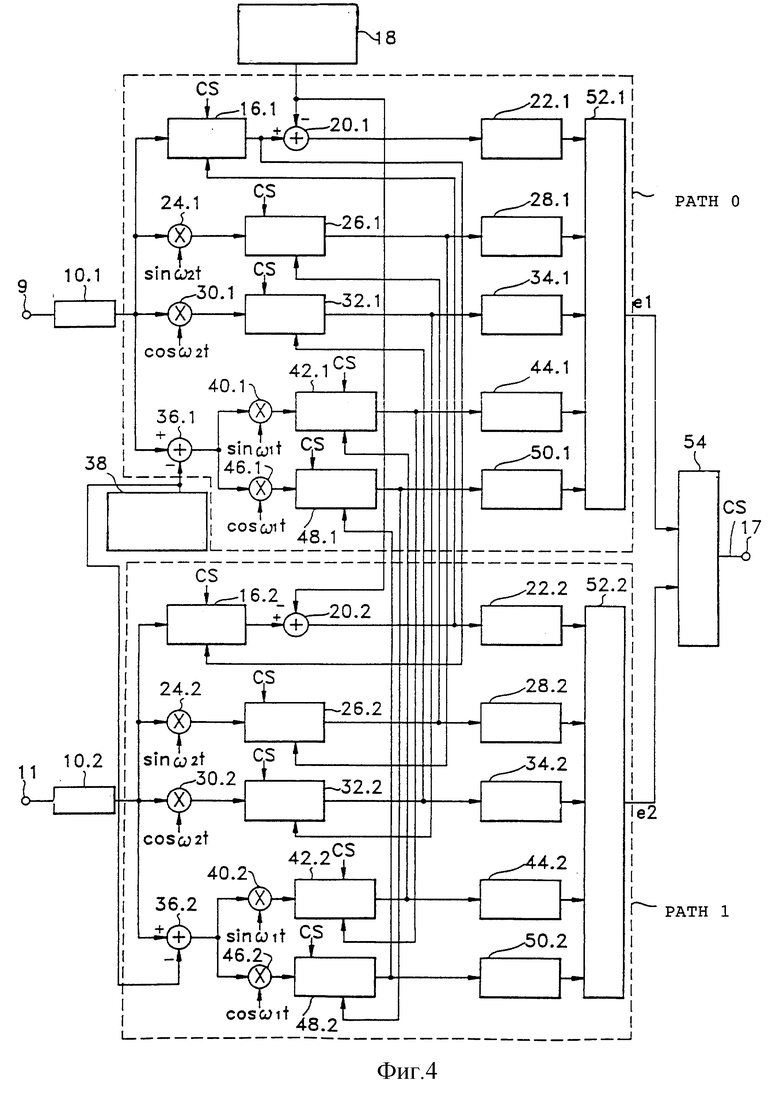

фиг. 4 является детальной диаграммой схемы части усовершенствованного генератора сигнала управления для устройства записи цифрового сигнала, показанного на фиг. 3;

фиг. 5 иллюстрирует один из частотных спектров образца потока последовательных данных слов канала, выбранных сигналом управления, сгенерированным генератором сигнала управления, показанным на фиг. 4;

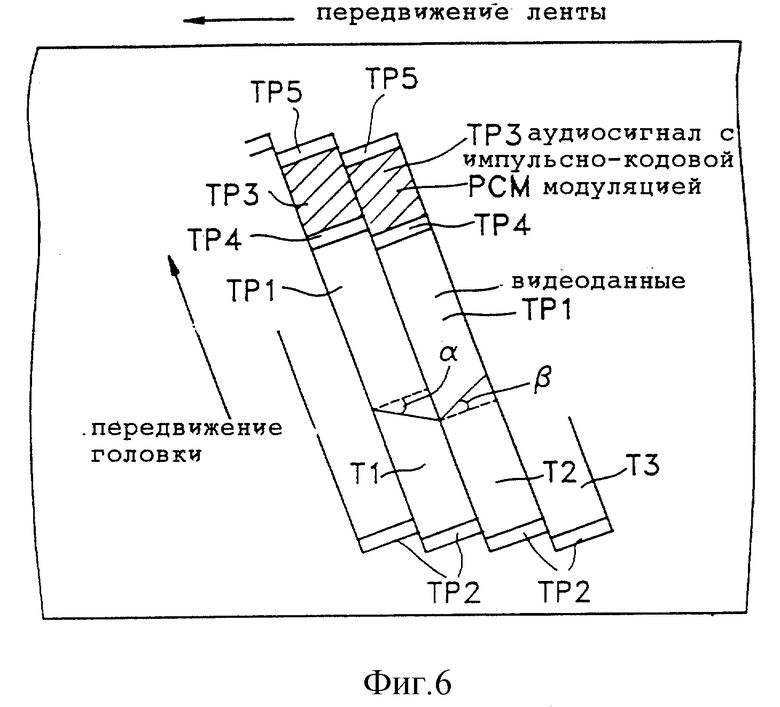

фиг. 6 является диаграммой ранее известного образца дорожки используемого в настоящем изобретении;

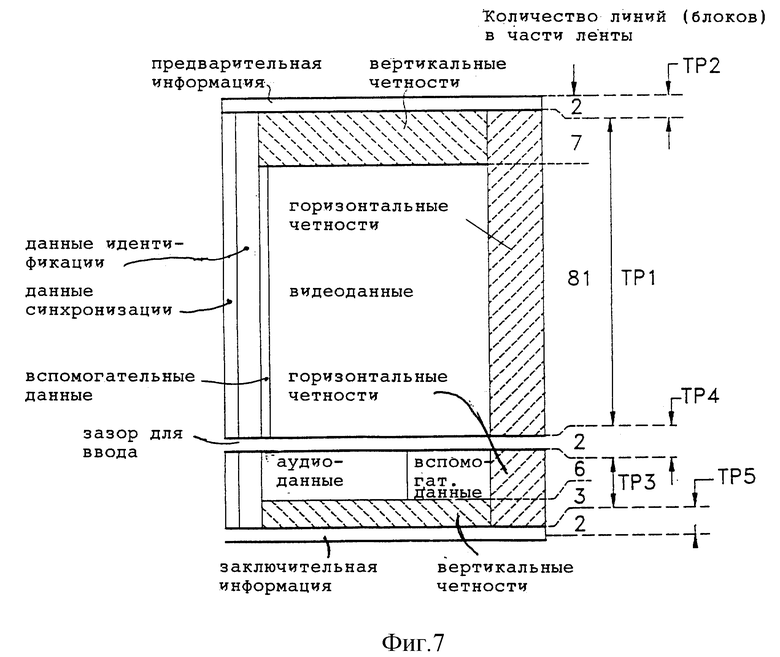

фиг. 7 иллюстрирует содержимое информации, записываемой на единичную дорожку, показанную на фиг. 6;

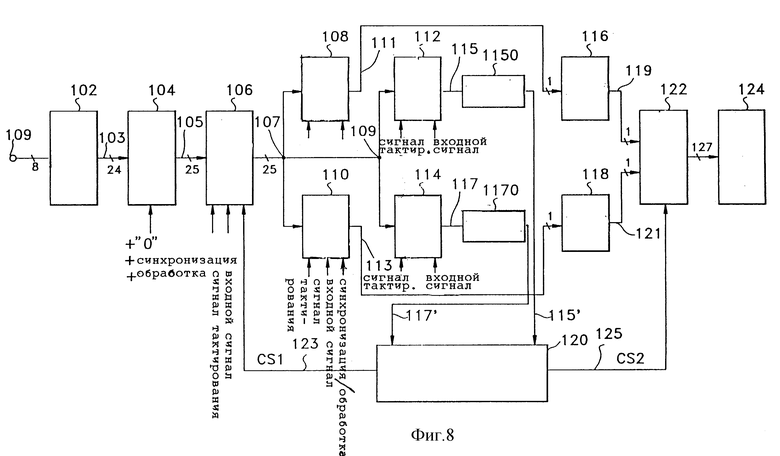

фиг. 8 является блок-схемой устройства записи цифрового сигнала, использующего настоящее изобретение;

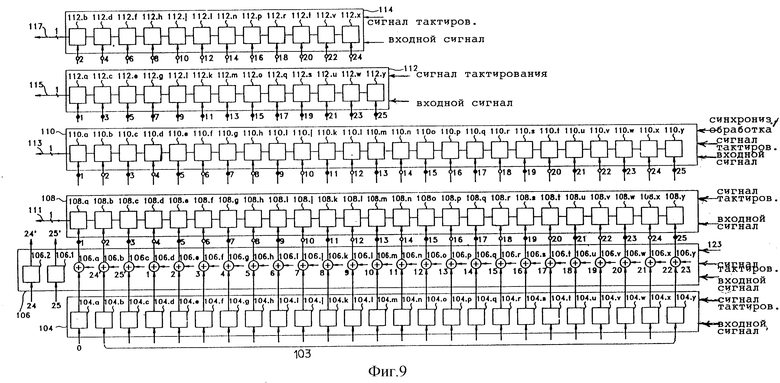

фиг. 9 является детальной блок-схемой цепи предварительного кодера, содержащегося в устройстве записи цифрового сигнала фиг. 8;

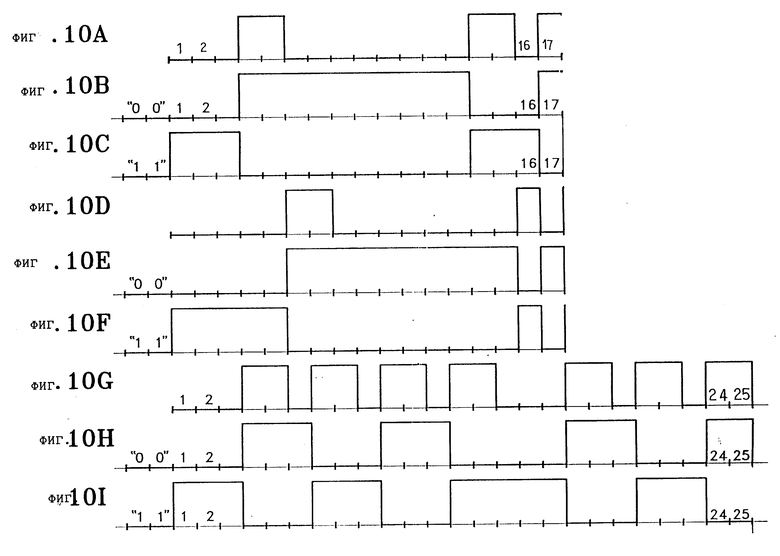

фиг. 10A-10I иллюстрируют образцы данных синхронизации и данных обработки;

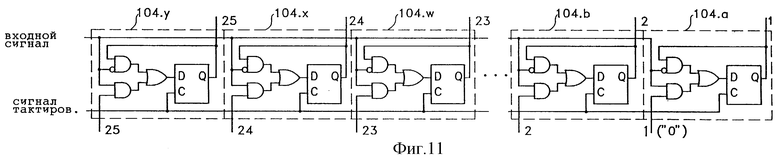

фиг. 11 является детальной диаграммой цепи устройства ввода сигналов, показанного на фиг. 9:

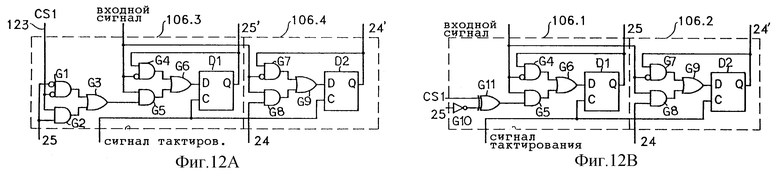

фиг. 12A и 12B являются детальными диаграммами схем части предварительного кодера, показанного на фиг. 9;

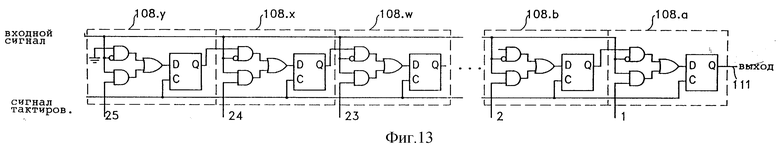

фиг. 13 является детальной диаграммой схемы первого преобразователя параллельных в последовательные, показанного на фиг. 9;

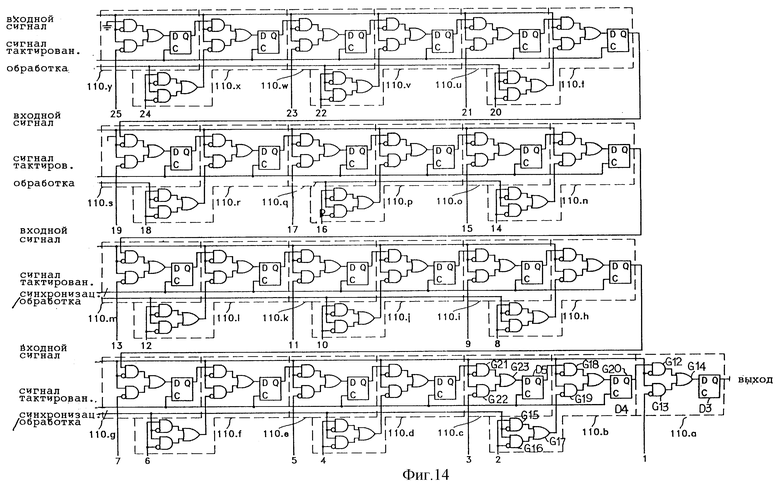

фиг. 14 является детальной диаграммой схемы второго преобразователя параллельного в последовательное, показанного на фиг. 9;

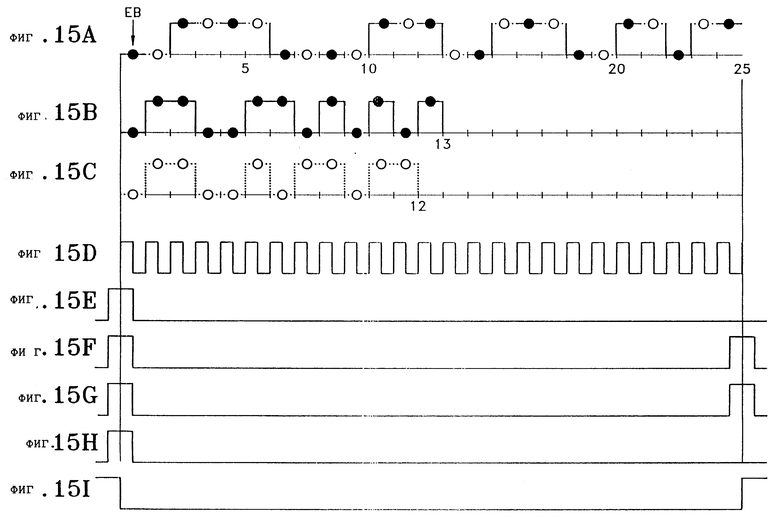

фиг. 15A-15I иллюстрируют рабочие формы волн рабочего состояния для различных блоков, показанных на фиг. 8 и 9;

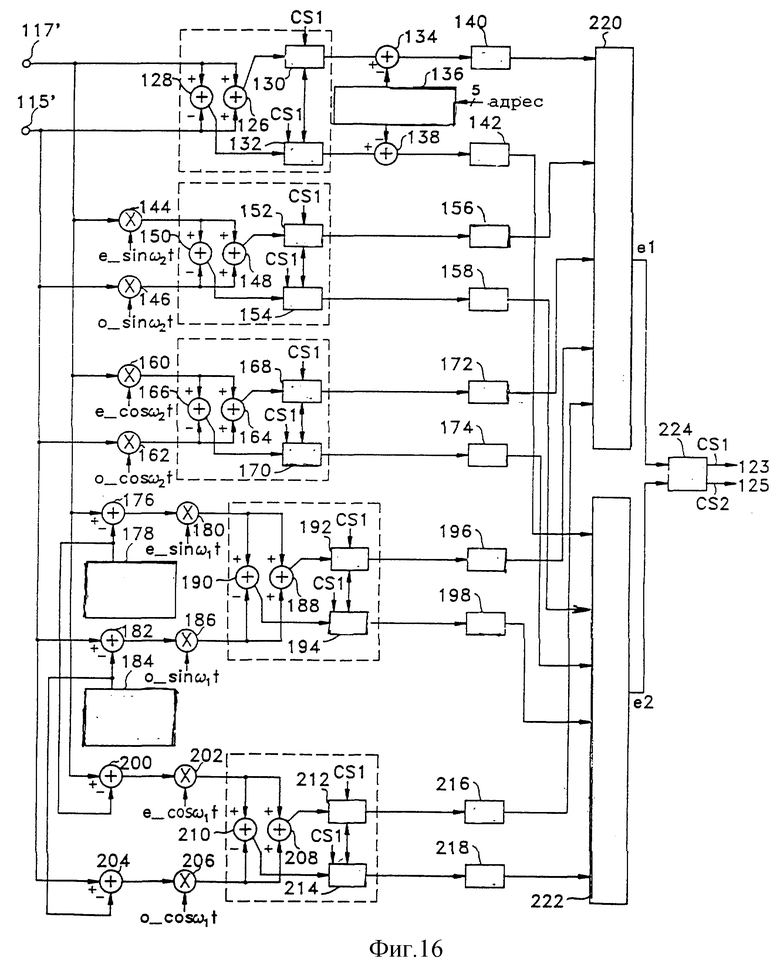

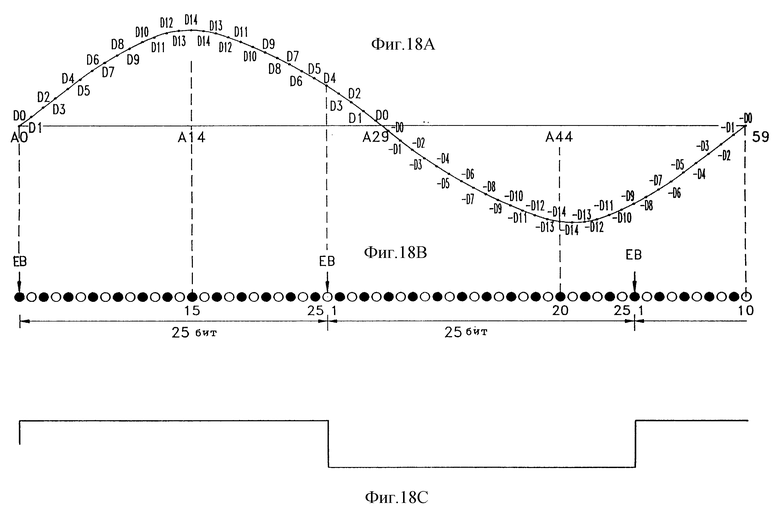

фиг. 16 является детальной диаграммой схемы генератора сигнала управления, показанного на фиг. 8;

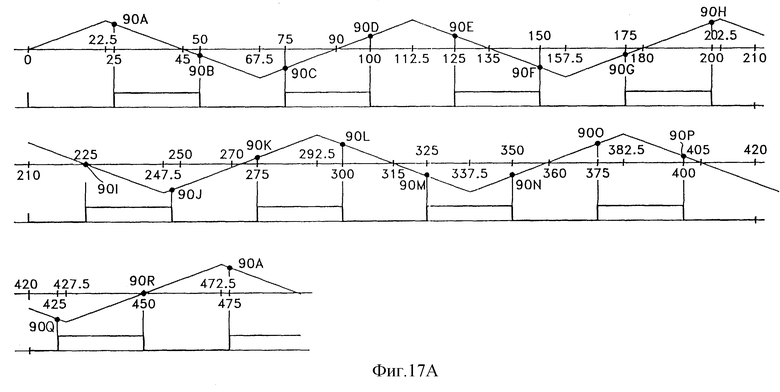

фиг. 17A и фиг. 17B иллюстрируют сигнал треугольной волны, генерируемый генератором треугольной волны, который показан на фиг. 16;

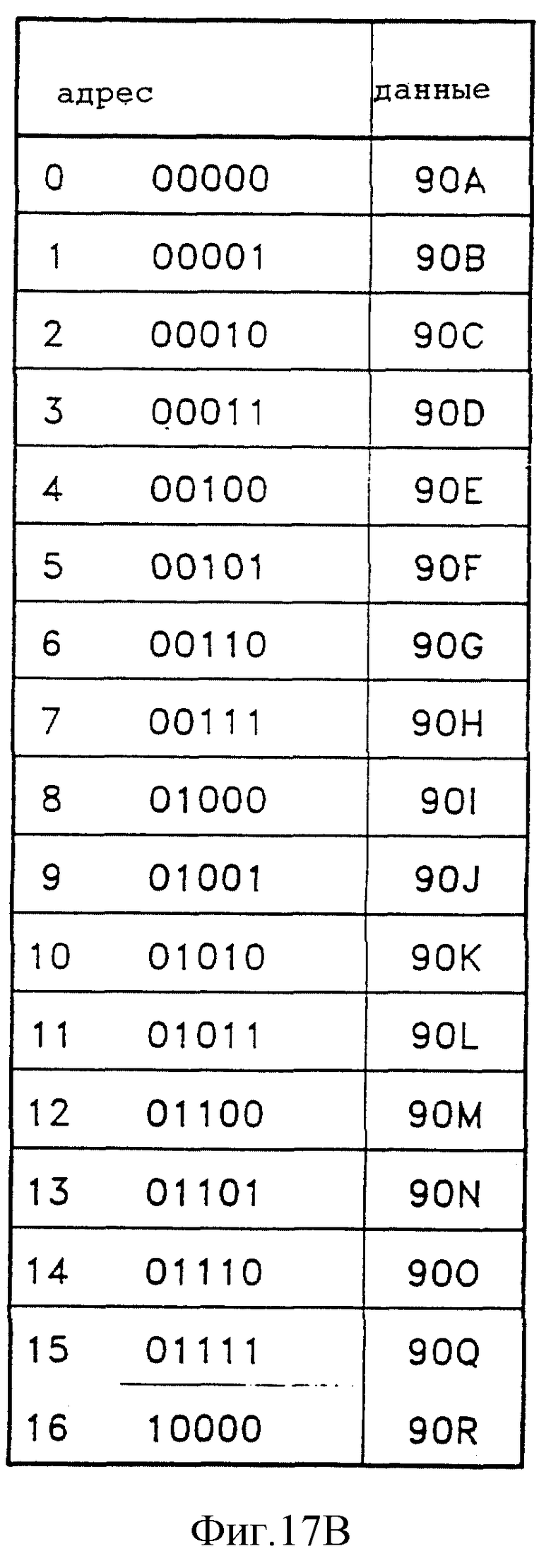

фиг. 18A, 18B и 18C иллюстрируют сигнал синусоидальной волны и сигнал прямоугольной волны, используемые в генераторе сигнала управления фиг. 16;

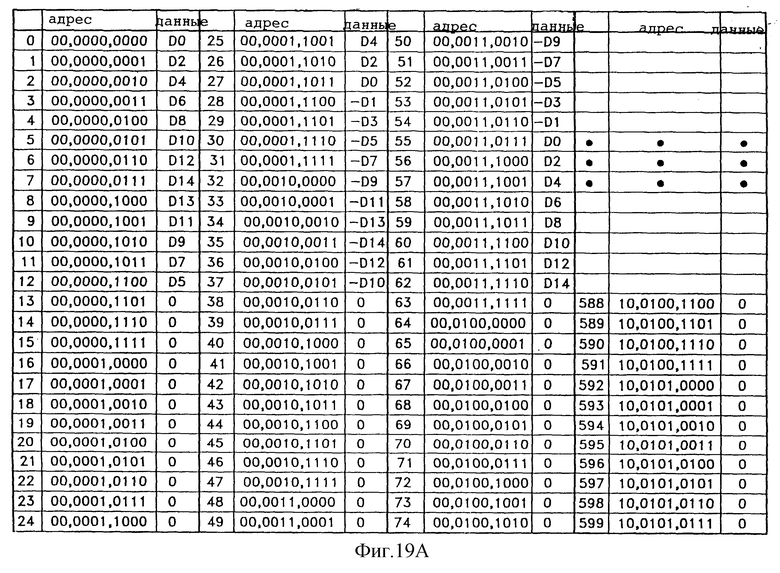

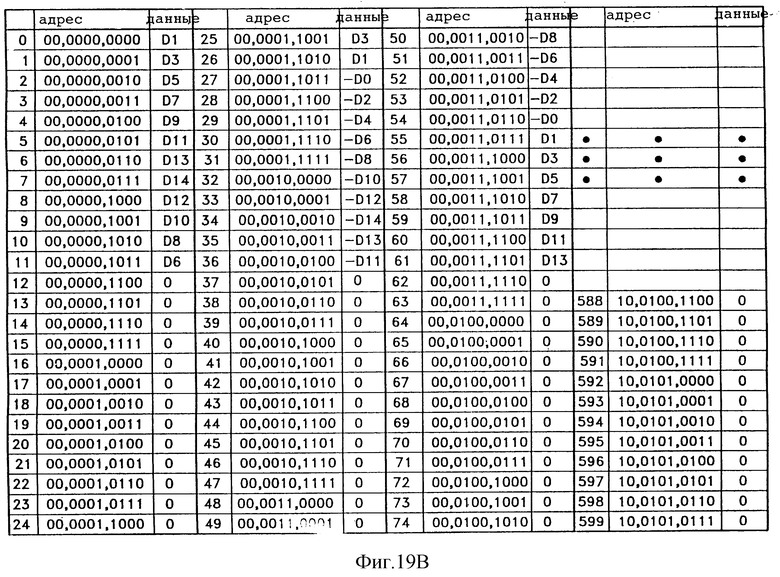

фиг. 19A и 19B являются примерами таблицы синусов нечетных образцов и таблицы косинусов четных образцов для загрузки сигнала синусоидальной волны, показанной на фиг. 18A; и

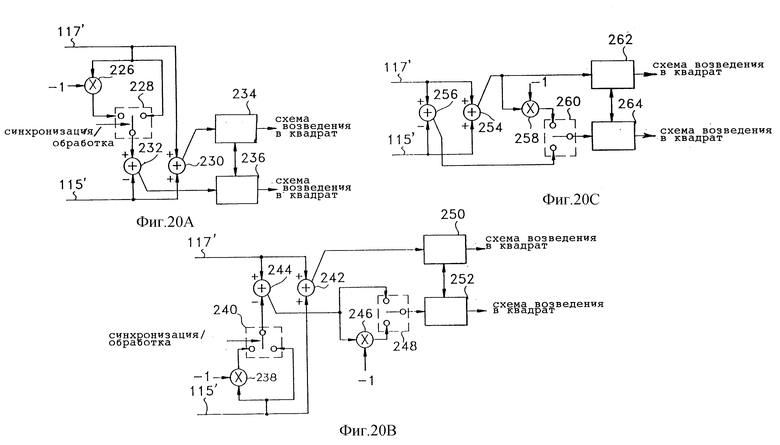

фиг. 20A, 20B и 20C являются примерами альтернативного исполнения цепей, ограниченных четырехугольниками, обозначенными пунктирными линиями фиг. 16.

Подробное описание изобретения

Фиг. 1 иллюстрирует как, для упрощения трекинга головки, устройство записи цифровой информации со спиральной разверткой записывает поток последовательных данных слов канала в три соответствующих спектральных образца F0, F1 и F2 на последовательных параллельных дорожках среды магнитной записи. По соглашению, дорожки показаны в укороченном виде и имеют большее отклонение от направления движения ленты, чем на самом деле. Пилот-сигналы появляются в спектре цифровых сигналов, записываемых в соответствии с последовательностью F0, F1, F0, F2, ... на соответствующих дорожках среды магнитной записи. Пилот-сигналы принимают форму провалов или пиков на заранее предписанных частотах, которые вводятся в частотную область спектральной энергии ответной реакции (преобразование Фурье) сигналов, записываемых на дорожки. Во время воспроизведения одной из таких дорожек конкретного образца устанавливается определенное отклонение области спектральной энергии ответной реакции для ожидаемых величин. Такие отклонения приписываются для извлечения цифровых сигналов из предыдущих и последующих дорожек, для того чтобы оценить относительную близость головки к предыдущей дорожке и к последующей дорожке, на основании чего может быть определена ошибка трекинга. Показанная последовательность образцов F0, F1, F2 является всего лишь примером, в то время как на практике количество образцов и последовательности для записи может отличаться от этой иллюстрации. Заявка США на изобретение N 5142421 описывает конкретный из этих вариантов.

Фиг. 2A, 2B и 2C иллюстрируют спектр частот потоков данных последовательных битов слов канала, несущих образцы F0, F1 и F2, показанные на фиг. 1, соответствующим образом. В частотном спектре образца F0 имеются минимумы на частотах f1 и f2, где спектральная энергия относительно мала. В частотном спектре образца F1 имеется пилот-сигнал (пик) на частоте f1 = 1/2π, где спектральная энергия относительно велика, и имеются минимальные значения на частоте f2 = ω2/2π, где спектральная энергия относительно мала. В частотном спектре образца F2 имеется минимум на частоте f1, где спектральная энергия относительно мала, и пилот-сигнал (пик) на частоте f2, где спектральная энергия относительно велика.

В течение воспроизведения образца F0 используется эффект переходного взаимодействия между управляющими сигналами (пиками f1 и f2) образцов F1 и F2 смежных дорожек для определения ошибки трекинга. С одной стороны, если головка отклонилась от центра образца F0 в сторону образца F1, то переходное влияние пилот-сигнала от образца F1 становится больше, чем влияние пилот-сигнала от образца F2. В результате, частотная компонента f1 сигнала воспроизведения увеличивается, а частотная компонента f2 уменьшается. С другой стороны, если головка отклонится от центра образца F0 в сторону образца F2, то переходное влияние пилот-сигнала от образца F2 станет больше, чем пилот-сигнала образца F1. В результате, в среднем, частотная компонента f2 сигнала воспроизведения увеличится, а частотная компонента f1 уменьшится. Во время воспроизведения образца F0, после этого, сравнение среднего значения спектральной энергии сигнала воспроизведения на частотах f1 и f2 позволяет определить отклонение трекинга дорожки. Используя этот результат, становится возможным точный трекинг путем управления высотой элемента головки посредством напряжения, приложенного к пьезоэлектронному элементу, на котором установлена головка, или путем управления скоростью перемещения среды магнитной записи (ленты).

Фиг. 3 является блок-схемой устройства записи цифрового сигнала, описанного в заявке США на изобретение N 5142421, изданной 25 августа 1992 года Kahlman et alii, озаглавленной "СРЕДСТВО ДЛЯ ЗАПИСИ СИГНАЛА ЦИФРОВОЙ ИНФОРМАЦИИ НА НОСИТЕЛЬ ЗАПИСЕЙ" и приведенной здесь в качестве ссылке. Схематичная конфигурация и работа его будут обсуждены в сравнении с обычным способом записи образцов F0, F1 и F2.

На фиг. 3 цифровые слова с 8-параллельными битами принимаются посредством порта ввода 1 в преобразователь 2 параллельного в последовательный (P/S). P/S преобразователь 2 преобразует, например, каждую последующую группу из трех цифровых слов с 8-параллельными битами в одно цифровое информационное слово с 24-последовательными битами, передаваемое посредством порта вывода 3 преобразователя. Устройство ввода сигнала 4 содержит устройство ввода бита "0" 4.1 и устройство ввода бита "1" 4.2, каждое из которых принимает в качестве соответствующего входного сигнала поток цифровых информационных слов с 24- последовательными битами, которые появляются в порте вывода 3 P/S преобразователя 2. Устройство ввода бита "0" 4.1 вводит цифровой префикс одиночного бита, состоящий из "0" перед самым старшим разрядом (MSB) каждого информационного слова с 24- последовательными битами для генерации соответствующего "положительного" информационного слова с 25-последовательными битами, передаваемого с выхода порта вывода 5 устройства ввода "0" бита 4.1. Устройство ввода бита "1" 4.2 вводит цифровой префикс одиночного бита, содержащий "1" перед самым старшим разрядом (MSB) каждого информационного слова с 24-последовательными битами для генерации соответствующего "отрицательного" информационного слова с 25-последовательными битами, передаваемого от порта вывода 7 устройства ввода бита "1" 4.2.

Кодер 6 содержит предварительный кодер 6.1, преобразующий "положительные" информационные слова в соответствующие слова канала с 25-последовательными битами, которые передаются посредством соединения 9. Кодер 6, кроме этого, содержит предварительный кодер 6.2, преобразующий "отрицательные" информационные слова в соответствующие слова канала с 25-последовательными битами, которые передаются посредством соединения 11. В конце этого описания и в формулах изобретения, приложенных к этому описанию, для того, чтобы различать слова канала, передаваемые от предварительного кодера 6.1, и слова канала, передаваемые предварительным кодером 6.2, слова канала, получаемые от предварительного кодера 6.1, упоминаются как "положительные" информационные слова канала, а слова канала, передаваемые от предварительного кодера 6.2, упоминаются как "отрицательные" информационные слова канала. Если предварительные кодеры 6.1 и 6.2 являются 2T предварительными кодерами, то префиксный код одиночного бита заставляет их генерировать слова канала с 25-последовательными битами, в которых соответствующие четные биты те же, а соответствующие нечетные биты являются битовыми дополнениями. 2T предварительный кодер содержит два входных вентиля исключающего ИЛИ и регистр двухступенчатого сдвига, который позволяет осуществить интегрирующую обратную связь выходного соединения вентиля исключающего ИЛИ с первым из его входных соединений. Вентиль исключающего ИЛИ принимает входной сигнал предварительного кодера на свое второе входное соединение, передает выходной сигнал предварительному кодеру со своего выходного соединения и обычным образом принимает на свое первое входное соединение выходной сигнал предварительного кодера с задержкой 2T из-за прохождения через регистр двухступенчатого сдвига. Интервал Т является интервалом квантования входного сигнала предварительного кодера и интервалом между тактируемыми сдвигами битов регистра двухступенчатого сдвига. Обратная связь вентиля исключающего ИЛИ, осуществляемого регистром двухступенчатого сдвига, упоминается как "интегрирующая обратная связь" или просто "интегрирующее соединение".

Предварительный кодер 6.1 передает "положительные" информационные слова канала с 25-последовательными битами посредством соединения 9 в качестве своего выходного сигнала; а предварительный кодер 6.2 передает "отрицательные" информационные слова канала с 25-последовательными битами посредством соединения 11 в качестве своего выходного сигнала. На основании этих слов канала с 25-последовательными битами, которые передаются параллельно от предварительных кодеров 6.1 и 6.2, генератор сигнала управления 10 сравнивает соответствующие характеристики спектральной энергии частотной области каждого слова с предписанными характеристиками спектральной энергии для дорожки, которая должна быть записана цифровым записывающим устройством 14 для определения, какое из слов канала отклонилось меньше от предписанного спектрального ответного сигнала. Генератор сигнала управления 10 генерирует сигнал управления CS, указывая, какое из слов канала, полученное от предварительных кодеров 6.1 и 6.2, отклонилось наименьшим образом от предписанного спектрального ответного сигнала и которое должно быть выбрано для записи. Сигнал управления CS передается посредством соединения 17 на порт управления выбором селектора 12, который выбирает выходной сигнал от одного из предварительных кодеров 6.1 и 6.2 (после задержки, полученной от устройства компенсации по времени 8), который имеет наименьшее отклонение от предписанного ответного спектрального сигнала, для использования в цифровом записывающем устройстве 14. Запаздывания 8.1 и 8.2 устройства компенсации по времени 8 необходимы для компенсации по времени, необходимого для генератора сигнала управления 10 для генерации сигнала управления CS для использования в селекторе 12. Сигнал управления CS тоже передается посредством соединения 17 на соответствующие порты управления предварительных кодеров 6.1 и 6.2 для управления передачей содержимого регистра сдвига в одном из предварительных кодеров 6.1 и 6.2, выходной сигнал которого выбирается для записи в регистр сдвига другого из предварительных кодеров 6.1 и 6.2, чтобы обеспечить непрерывность кодирования.

Селектор 12 принимает посредством соединения 13 "положительный" информационный выходной сигнал предварительного кодера 6.1 с запаздыванием 8.1 и принимает посредством соединения 15 "отрицательный" информационный выходной сигнал предварительного кодера 6.2 с запаздыванием 8.2. В ответ на сигнал управления CS селектор 12 передает один из выбранных выходных сигналов с запаздыванием от предварительных кодеров 6.1 и 6.2 посредством соединения 19 на цифровое записывающее устройство 14 в качестве выходного сигнала для записи. Необходим некоторый запас скорости для того, чтобы битовая модуляция могла быть записана при постоянной битовой скорости

цифровым записывающим устройством 14. Запаздывания 8.1 и 8.2 могут быть фиксированными запаздываниями с запасом скорости, обеспечиваемым после селектора 12; или в качестве альтернативы запаздывания 8.1 и 8.2 могут быть буферной памятью скорости типа первым пришел/первым обслужен (FIFO), что обеспечит необходимый запас скорости.

Фиг. 4 является детальной диаграммой схемы усовершенствованного генератора сигнала управления для устройства записи цифрового сигнала фиг. 3, который работает для генерации последовательного потока данных слов канала с ответным частотным спектром, показанным на фиг. 5. Сравнивая со спектром образца F1, показанного на фиг. 2В, увидим, что в спектре, показанном на фиг. 5, имеются провалы с каждой стороны f1. Эти провалы указывают, что мощность шума спектра уменьшается вслед за частотой пилот-сигнала f1, что приводит к повышению отношения сигнал/шум для определения пилот-сигнала на частоте f1.

Усовершенствованный генератор сигнала управления фиг. 4 отличается от того, который описан Kahiman и др., тем, что он содержит устройства отображения кода в арифметику 10.1 и 10.2. Устройство отображения кода в арифметику 10.1 преобразует ЕДИНИЦЫ и НУЛИ "положительного" информационного выходного сигнала предварительного кодера 6.1 в арифметические описания I-NRZI модуляции, которая осуществляет коммутацию отрицательных и положительных арифметических величин с одинаковыми амплитудами и не порождает постоянной составляющей. Устройство отображения кода в арифметику 10.2 по своей конструкции аналогично устройству отображения кода в арифметику 10.1. Преобразователь кода в арифметику 10.2 преобразует ЕДИНИЦЫ и НУЛИ "отрицательного" информационного выходного сигнала предварительного кодера 6.2 в арифметические описания I-NRZI модуляции, которая осуществляет коммутацию отрицательных и положительных арифметических величин одинаковой амплитуды и не порождает постоянную составляющую. В качестве примера, каждое из устройств отображения 10.1 и 10.2 может использовать ЕДИНИЦЫ и НУЛИ, передаваемые туда как изменяющийся битовый знак перед неизменной ЕДИНИЦЕЙ, так что модуляция описывается в терминах двоичной арифметики дополнений.

Таблица для просмотра синусов/косинусов, загруженная в постоянное запоминающее устройство (ПЗУ), которое не показано, генерирует комплексный носитель частоты f1, имеющей угловую частоту ω1, и состоит из компонентов sinω1t и cosω1t. Другая таблица для просмотра синусов/косинусов, загруженная в ПЗУ (ROM), которая не показана, генерирует комплексный носитель частоты f2, который имеет угловую частоту ω2 и состоит из компонентов sinω2t и cosω2t. Генератор треугольной волны 18 генерирует треугольный сигнал, соответствующий величине цифровой суммы необходимой частоты (f1) потока последовательных данных слов канала, а генератор прямоугольной волны 38 генерирует прямоугольную волну с частотой ω1. Генератор треугольной волны 18 и генератор прямоугольной волны 38 могут тоже обеспечиваться таблицами для просмотра, загруженными в ROM. Генерирование всех системных функций в ROM упрощает обработку слов канала в последовательности, отличной от нормальной последовательности битов.

Цепь фильтра PATH0 определяет, как распределение спектральной энергии I-NRZI модуляции во время продолжения генерации на основе "положительного" информационного слова канала от предварительного кодера 6.1 отклоняется от необходимого распределения спектральной энергии для записи дорожки по образцу F1, имеющему пик на частоте f1, провал с одной из сторон от f1 и с минимальным значением на частоте f2. Схема взвешенного суммирования 52.1 объединяет с соответствующим весом вычисленное отклонение от необходимого минимального значения на нулевой частоте и от необходимого пикового значения на частоте f1 после получения от схемы возведения в квадрат 22.1 с вычисленными отклонениями от других желаемых величин. Вычисленные отклонения от минимального значения на частоте f2 после передачи для ортогональных фаз частот f2 схемами возведения в квадрат 28.1 и 34.1 взвешиваются аналогичным образом по отношению друг к другу в схеме взвешенного суммирования 52.1. Вычисленные отклонения от провалов с одной из сторон частоты f1 после передачи для ортогональных фаз частоты f1 схемами возведения в квадрат 44.1 и 50.1 взвешиваются аналогичным образом по отношению друг к другу в схеме взвешенного суммирования 52.1. Осуществить эффективное взвешивание входных сигналов схемы взвешенного суммирования 52.1, полученных от схем возведения в квадрат 28.1 и 34.1, относительно сложно по сравнению с взвешиванием входного сигнала схемы взвешенного суммирования 52.1 от схемы возведения в квадрат 22.1, так как отсутствие правильной пилот-частоты f1 лучше переносится, чем присутствие неправильной пилот-частоты f2, цепью коррекции трекинга, используемой в течение воспроизведения. Осуществить эффективное взвешивание входных сигналов схемы взвешенного суммирования 52.1, полученных от схем возведения в квадрат 44.1 и 50.1, относительно просто по сравнению с взвешиванием входного сигнала схемы взвешенного суммирования 52.1, полученного от схемы возведения в квадрат 22.1. Схема фильтра PATH0 передает в качестве выходного сигнала суммирования схемы взвешенного суммирования 52.1 сигнал первой ошибки e1.

Вычисление в системе PATH0 величины, на которую распределение спектральной энергии I-NRZI модуляции, когда генерация в ней продолжается на основании "положительного" информационного слова канала от предварительного кодера 6.1, отклоняется от необходимого минимального значения на нулевой частоте и необходимого пикового значения на частоте f1, осуществляется следующим образом. Схема интегрирования 16.1 принимает текущее "положительное" информационное слово канала от предварительного кодера 6.1 после преобразования в арифметическую форму устройством отображения кода в арифметику 10.1 и интегрирует его с заранее загруженной величиной. Устройство вычитания 20.1 вычитает выходной сигнал генератора треугольной волны 18 из выходного сигнала схемы интегрирования 16.1; а схема возведения в квадрат 22.1 помножает само на себя результирующее различие, а результирующий квадрат передается в сеть взвешенного суммирования 52.1 для получения компонент и первого сигнала ошибки e1. Генератор треугольной волны 18 и устройство вычитания 20.1 составляют схему детектирования для определения любого отклонения от предписанной цифровой суммы, необходимой для поддержания нужного пилот-сигнала, соответствующего величине цифровой суммы, которую передает схема интегрирования 16.1. Схема возведения в квадрат 22.1 вычисляет энергию этого отклонения.

Вычисления в системе PATH0 величины, на которую распределение спектральной энергии I-NRZI модуляции, когда генерация в ней продолжается на основании "положительного" информационного слова канала от предварительного кодера 6.1, отклоняется от необходимого минимального значения на нулевой частоте и необходимого пикового значения на частоте f2, осуществляется следующим образом. Устройство помножения 24.1 умножает выходной сигнал предварительного кодера 6.1, после преобразования в арифметику устройством отображения кода в арифметику 10.1, системную функцию синусоидальней волны sinω2t частоты f2; схема интегрирования 26.1 интегрирует произведение, полученное от устройства умножения 24.1; а схема возведения в квадрат 28.1 возводит в квадрат результат интегрирования, полученный от схемы интегрирования 26.1, для использования в сети взвешенного суммирования 52.1. Устройство умножения 30.1 умножает выходной сигнал предварительного кодера 6.1, после преобразования в арифметическую форму устройством отображения кода в арифметику 10.1, на системную функцию косинусоидальной волны cosω2t частоты f2; схема интегрирования 32.1 интегрирует это произведение, полученное от устройства умножения 30.1, а схема возведения в квадрат 34.1 возводит в квадрат результаты интегрирования, полученные от схемы интегрирования 32.1, для использования в сети взвешенного суммирования 52.1. (Фраза "системная функция" используется в цифровой электронике для обращения к функции в аналоговом режиме, что описывается на основании дискретизированных данных, цифровыми выборками).

Вычисления в системе PATH0 величины, на которую распределение спектральной энергии I-NRZI модуляции, когда генерация в ней продолжается на основании "положительного" информационного слова канала от предварительного кодера 6.1, отклоняется от необходимого минимума на нулевой частоте и необходимого пикового значения на частоте f1, осуществляется следующим образом. Устройство вычитания 36.1 вычитает прямоугольную волну частоты f1, переданную генератором прямоугольной волны 38, из выходного сигнала предварительного кодера 6.1, после преобразования в арифметическую форму устройством отображения кода в арифметику 10.1. Генератор прямоугольной волны 38 и устройство вычитания 36.1 составляют схему детектирования для определения любого отклонения от необходимой прямоугольной волны "положительного" информационного слова канала с последовательными битами, полученного от предварительного кодера 6.1, после преобразования к арифметической форме устройством отображения кода в арифметику 10.1. Устройство помножения 40.1 перемножает выходной сигнал различия от устройства вычитания 36.1 на системную функцию синусоидальной волны sinω1t частоты f1; схема интегрирования 42.1 интегрирует произведение, полученное от устройства умножения 40.1; а схема возведения в квадрат 44.1 возводит в квадрат результаты интегрирования, полученные от схемы интегрирования 42.1, для использования в сети взвешенного суммирования 52.1. Устройство умножения 46.1 умножает выходной разностный сигнал от устройства вычитания 36.1 на системную функцию косинусоидальной волны cosω1t частоты f1, схема интегрирования 48.1 интегрирует произведение, полученное от устройства умножения 46.1; а схема возведения в квадрат 50.1 возводит в квадрат результаты интегрирования, полученные от схемы интегрирования 48.1, для использования в сети взвешенного суммирования 52.1.

Цепь фильтра PATH1 определяет величину, на которую распределение спектральной энергии в I-NRZI модуляции, когда генерация в ней продолжается на основе "отрицательного инф. слова канала, полученного от предварительного кодера 6.2, отклоняется от необходимого распределения спектральной энергии для дорожки, записываемой при помощи образца F1, имеющего пиковое значение на частоте f1, провалы по обе стороны частоты f1 и минимальное значение на частоте f2. Схема взвешенного суммирования 52.2 в схеме фильтра PATH1 объединяет с соответствующим весом вычисленное отклонение от необходимого минимального значения на нулевой частоте и от необходимого пикового значения на частоте f1, после приема от схемы возведения в квадрат 22.2, после вычисления отклонения от других необходимых качеств переданных от схем возведения в квадрат 28.2, 34.2, 44.2 и 50.2. Сеть взвешенного суммирования 52.2 передает, в качестве суммарного выходного сигнала, сигнал второй ошибки e2. Компаратор 54 сравнивает сигналы ошибок e1 и e2 для генерации сигнала управления CS, которые передаются на порт управления выбором селектора 12, который выбирает слово канала, имеющее сигнал ошибки наименьшей величины.

Вычисления в системе PATH1 величины, на которую распределение спектральной энергии I-NRZI модуляции, когда генерация в ней продолжается на основании "отрицательного" информационного слова канала, полученного от предварительного кодера 6.2, отклоняется от необходимого минимального значения на нулевой частоте и от необходимого пикового значения на частоте f2, осуществляется следующим образом. Схема интегрирования 16.2 принимает текущее "отрицательное" информационное слово канала от предварительного кодера 6.2 после преобразования в арифметическую форму устройством отображения кода в арифметику 10.2 и интегрирует его с заранее загруженным значением. Устройство вычитания 20.2 вычитает выходной сигнал генератора треугольной волны 18 из выходного сигнала схемы интегрирования 16.2, схема возведения в квадрат 22.2 умножает результирующее различие само на себя, а результирующий квадрат передается на сеть взвешенного суммирования 52.2 для получения компоненты сигнала первой ошибки e2. Генератор треугольной волны 18 и устройство вычитания 20.2 составляют схему детектирования для определения любого отклонения от предписанной цифровой суммы, необходимой для поддержания нужного пилот-сигнала, величины цифровой суммы, которую передает схема интегрирования 16.2. Схема возведения в квадрат 22.2 вычисляет энергию этого отклонения.

Вычисление в системе PATH1 величины, на которую распределение спектральной энергии I-NRZI модуляции после продолжения в ней генерации на основании "отрицательного" информационного слова канала, полученного от предварительного кодера 6.2, отклоняется от необходимого минимального значения на нулевой частоте и от необходимого пикового значения на частоте f2, выполняется следующим образом. Устройство умножения 24.2 перемножает выходной сигнал предварительного кодера 6.2, после преобразования в арифметическую форму устройством отображения кода в арифметику 10.2, на системную функцию синусоидальной волны sinω2t частоты f2; схема интегрирования 26.2 интегрирует произведение, полученное от схемы умножения 24.1; а схема возведения в квадрат 28.2 возводит в квадрат результаты интегрирования, полученные от схемы интегрирования 26.2, для использования в сети взвешенного суммирования 52.2. Устройство умножения 30.2 перемножает выходной сигнал, полученный от предварительного кодера 6.2, после преобразования в арифметическую форму устройством отображения кода в арифметику 10.2, на системную функцию косинусоидальной волны cosω2t частоты f2; схема интегрирования 32.2 интегрирует произведение, полученное от устройства умножения 30.2; а схема возведения в квадрат 34.2 возводит в квадрат результаты интегрирования, полученные от схемы интегрирования 32.2, для использования в сети взвешенного суммирования 52.1.

Вычисления в системе PATH1 величины, на которую распределение спектральной энергии I-NRZI модуляции, когда генерация в ней продолжается на основании "отрицательного" информационного слова канала, полученного от предварительного кодера 6.2, отличается от необходимого минимального значения по любую сторону пика на частоте f1, осуществляется следующим образом. Устройство вычитания 36.2 вычитает прямоугольную волну частоты f1, переданную генератором прямоугольной волны 38, из выходного сигнала предварительного кодера 6.2 после преобразования в арифметическую форму устройством отображения кода в арифметику 10.2. Генератор прямоугольной волны 38 и устройство вычитания 36.2 образуют цепь детектирования для определения любого отклонения от предписанной прямоугольной волны "отрицательного" информационного слова канала с последовательными битами, которое передает предварительный кодер 6.2 посредством соединения 11. Устройство помножения 40.2 перемножает входной сигнал различия устройства вычитания 36.2 на системную функцию синусоидальной волны sinω1t; частоты f1; а схема интегрирования 42.2 интегрирует произведение, полученное от устройства умножения 40.2; схема возведения в квадрат 44.2 возводит в квадрат результаты интегрирования, полученные от схемы интегрирования 42.2, для использования в сети взвешенного суммирования 52.2. Устройство умножения 46.2 умножает выходной сигнал различия от устройства вычитания 36.2 на системную функцию косинусоидальной волны cosω1t частоты f1, схема интегрирования 48.2 интегрирует произведение, полученное от устройства умножения 46.2; а схема возведения в квадрат 50.2 возводит в квадрат результаты интегрирования, полученные от схемы интегрирования 48.2, для использования в сети взвешенного суммирования 52.2.

Работа генератора сигнала управления 10 в процессе генерации образца F1 была описана выше. В процессе генерации образца F2 работа генератора сигнала управления 10 улучшается путем транспозиции f1 и f2, и тем самым осуществляется транспозиция ω1 и ω2. В процессе генерации образца F0 работа генератора сигнала управления 10 совершенствуется путем отключения генератора треугольной волны 18 и генератора прямоугольной волны 38. Независимо от того, какой из образцов F0, F1 или F2 был сгенерирован, должны последовать определенные процедуры повторной инициализации после того, как будет принято решение выбрать "положительное" информационное слово канала, переданное предварительным кодером 6.1, или выбрать "отрицательное" информационное слово канала, переданное предварительным кодером 6.2, для определения I-NRZI модуляции, которая должна быть записана. Эти процедуры повторной инициализации выполняются для непрерывности кодирования и для того, чтобы позволить генератору сигнала управления получить основу для принятия решения относительно того, какая из следующих пар должна быть выбрана для записи.

Позже, когда слово канала, которое должно быть записано следующим, определено, содержание схем интегрирования 16.1, 26.1, 32.1, 42.1 и 48.1 или содержание схем интегрирования 16.2, 26.2, 32.2, 42.2 и 48.2 должно быть изменено. Если новое выбранное слово канала является "отрицательного" информационного типа, то содержание схем интегрирования 16.1, 26.1, 32.1, 42.1 и 48.1 должно быть изменено в соответствии с содержанием схем интегрирования 16.2, 26.2, 32.2, 42.2 и 48.2 соответственно.

Как было отмечено ранее, когда слово канала, которое должно быть записано следующим, было определено, информация для предварительного кодирования от "интегрирующей обратной связи" одного из предварительных кодеров 6.1 и 6.2, которые передают слово канала, которое выбирается для записи, должна передаваться на "интегрирующую обратную связь" одного из предварительных кодеров 6.1 и 6.2. Если слово канала, выбранное для последующей записи, было передано от предварительного кодера 6.1, то содержимое регистра сдвига в интегрирующей обратной связи в его вентиле исключающего ИЛИ передается на соответствующие позиции в регистре сдвига в интегрирующем соединении обратной связи вентиля исключительного или в предварительном кодере 6.2. С другой стороны, если слово канала, выбранное для последующей записи, было передано от предварительного кодера 6.2, то содержимое регистра сдвига в интегрирующей обратной связи его вентиля исключающего ИЛИ передается на соответствующие позиции регистра сдвига в интегрирующей обратной связи вентиля исключающего ИЛИ в предварительном кодере 6.1.

На практике, однако, имеется существенная задержка по времени до завершения этой передачи в ранее известном устройстве записи цифрового сигнала, описанном в заявке США на изобретение N 5142421, такое запаздывание возникает в устройствах цифрового умножения, схемах интегрирования и схемах возведения в квадрат в генераторе сигнала управления 10. Это запаздывание делает необходимым использование памяти буфера совместного чтения после кодера 6, что может быть обеспечено компенсатором времени 8 и делает необходимым использование памяти буфера совместного чтения перед кодером 6, что может осуществляться преобразователем параллельного в последовательное 2. Приготовления для такого совместного чтения и записи в память буфера на практике трудно синхронизируются. Как указывалось изобретателем Soon-Tae Kim в его заявке на изобретение из конкурирующей области, озаглавленное УСТРОЙСТВО ЗАПИСИ ЦИФРОВОГО СИГНАЛА, можно избежать необходимости в совместном чтении и записи в память буфера путем осуществления предварительного кодирования на основании слова с параллельными битами. Однако 2T предварительный кодер для слов с параллельными битами значительно более сложен по своей структуре, чем предварительный кодер 2T для слов с последовательными битами.

Фиг. 6 изображает среду для магнитной записи, на которой записываются цифровые видеосигналы и цифровые аудиосигналы на дорожки T1, T2, ..., расположенные под заранее определенным углом к продольной оси на среде для магнитной записи. Цифровая видеоинформация запоминается в соответствующей первой части TP1 дорожки каждой дорожки. Каждая дорожка начинается с соответствующей второй части TP2 дорожки, которая содержит предварительную информацию. Цифровая аудиоинформация, например аудиосигнал с импульсно-кодовой модуляцией, загружается в соответствующую третью часть дорожки TP3 каждой дорожки. Первая и третья части дорожки TP1 и TP3 каждой дорожки разделяются соответствующей четвертой частью дорожки TP4. Каждая дорожка заканчивается соответствующей пятой частью дорожки TP5, которая содержит заключительную информацию.

Фиг. 7 схематично показывает информацию потока последовательных данных слов канала, записанных на единичной дорожке. На фиг. 7, например, две строки 25-битовых слов канала записаны на каждой второй части дорожки TP2. Каждая из соответствующих строк имеет сорок семь 25-битовых слов канала. Вся информация, записанная в каждую вторую часть дорожки TP2, состоит из девяносто четырех 25-битовых слов канала.

После второй части дорожки TP2 записанная в первую часть дорожки TP1 информация состоит из 88 строк. Каждая из соответствующих строк содержит сорок семь 25-битовых слов канала. Часть TP1 дорожки содержит данные синхронизации, данные идентификации (ID), вспомогательные данные, видеоданные, данные горизонтальной четности и данные вертикальной четности.

Четвертая часть TP4 дорожки следует за первой частью TP1 дорожки. Как в случае второй части TP2 дорожки, сорок семь 25-битовых слов канала записываются в каждую из двух строк четвертой части TP4 дорожки.

За четвертой частью TP4 дорожки следует девять строк с информацией на третьей части TP3 дорожки. Каждая из соответствующих строк содержит сорок семь 25-битовых слов канала. Третья часть TP3 канала содержит данные синхронизации, данные ID, вспомогательные данные, аудиоданные, данные горизонтальной четности и данные вертикальной четности.

В пятой части TP5 дорожки 1325 битов (пятьдесят три 25-битовых слов канала) записываются в случае системы из 625 строк и 1445 битов записывается в случае 525-строковой системы.

Детальное описание структуры и информации сигнала, записанного в среду магнитной записи, показанное на фиг. 6 и 7, описано в европейской заявке на изобретение N 0492704 A1, изданной 1 июля 1992 г., озаглавленной "Приспособление для записи кодовых слов, используемых в тактовых сигналах, в начало дорожки на носителе магнитных записей" и приведенной здесь путем ссылки. В этой ссылке пилот-сигнал загружается во вторую часть TP2 дорожки при помощи заранее определенного количества слов канала. Четвертая часть TP4 четвертой дорожки в качестве входного интервала содержит те же слова канала, что и вторая часть TP2 дорожки, то же самое справедливо и в отношении пятой части TP5 дорожки.

В настоящем изобретении, однако, поток последовательных данных таков, что он содержит пилот-сигнал с частотой f1, который продолжается в частях дорожки TP2, TP1, TP4, TP3 и TP5 каждой дорожки в первом наборе дорожек, и пилот-сигнал частотой f2, который продолжается в частях дорожки TP2, TP1, TP4, TP3 и TP5 каждой дорожки во втором наборе дорожек. Данные обработки загружаются в четвертую часть TP4 дорожки каждой дорожки вместо того, чтобы повторять слова канала первой части TP1 дорожки. Загруженные данные обработки предназначены для предотвращения неправильной работы схемы фазовой автоподстройки, работающей на частоте битового тактового сигнала, и необходимы для выделения битов воспроизведенного сигнала в течение воспроизведения. Предпочтительное исполнение настоящего изобретения будет описано ниже.

Обратимся к фиг. 8, порт ввода 101 для приема последовательно передаваемых слов с 8-параллельными битами связывается с портом для ввода преобразователя параллельного в параллельное (P/P) 102. Преобразователь P/P 102 преобразует каждую последующую группу трех последовательных слов с 8-параллельными битами, переданными на его порт ввода, в три цифровых слова с 8-параллельными битами, т.е. в 24-битовое информационное слово, и передает преобразованное слово в форме параллельных битов с его порта вывода 103. Устройство ввода сигнала 104 присоединяет префикс цифрового слова с единичным битом "0" бит к каждому 24-битовому информационному слову, переданному в форме параллельных битов от порта вывода 103 P/P преобразователя 102.

Фиг. 7 показывает, как данные синхронизации записываются в заранее определенном формате и загружаются в начало соответствующих строк первой и третьей частей TP1 и TP3 дорожек. Семнадцать битов данных синхронизации 25-битового информационного слова совместно с исходным 8-битовым информационным словом передается параллельно от P/P преобразователя 102. Исходное 8-битовое информационное слово соответствует данным ID и описывается детально в европейской заявке на изобретение N 0492704 A1.

После записи сигнала в четвертую часть TP4 четвертой дорожки устройство ввода сигнала 104 принимает внешние данные обработки, в которых 25-битовые информационные слова имеют заранее определенный формат. Генератор (не показан) предназначен для генерации данных синхронизации и данных обработки, а также для генерации "0" бита для устройства ввода сигнала 104, если бит вводится последовательно в 24-битовую информацию, вместо того, чтобы вводиться как связанный НОЛЬ в информацию с 24-параллельными битами.

Полученное путем таких процедур 25-битовое информационное слово передается посредством порта вывода 105 для использования в качестве входного сигнала предварительного кодера 106. Предварительный кодер 106 преобразует информационное слово с 25-параллельными битами в слово канала с 25-параллельными битами. Желательно, чтобы устройство ввода сигнала 104 присоединяло только префикс единичного бита к каждому информационному слову и чтобы 2T предварительный кодер 2T использовался для предварительного кодирования 106.

Если устройство ввода сигнала 104 присоединяет префикс бита "0" к каждому информационному слову, то предварительный кодер 106 генерирует "положительное" информационное слово канала, которое обычно генерируется другим предварительным кодером, обрабатывающим информационные слова, к которым был присоединен префикс бита "1", но в которых добавленные и встречающиеся нечетным образом биты те же, что и соответствующие биты в "отрицательном" информационном слове канала. Соответственно, когда в соответствии с настоящим изобретением используется только один предварительный кодер 2T для генерации I-NRZI модуляции, то в исполнениях, где этот предварительный кодер 2T генерирует "положительное" информационное слово канала, "отрицательное" информационное слово канала может быть получено из "положительного" информационного слова канала путем битового дополнения его нечетных битовых мест и сохраняя его четные битовые места без изменения. В альтернативных выполнениях настоящего изобретения, в которых одиночный предварительный кодер 2T генерирует "отрицательное" информационное слово канала, "положительное" информационное слово канала может быть получено из "отрицательного" информационного слова канала путем битового дополнения его нечетных битовых мест и сохранив его четные битовые места без изменения.

Первые и вторые P/S преобразователи 108 и 110 имеют соответствующие порты ввода, к каждому из которых подсоединяется порт вывода 107 предварительного кодера 106, и имеют соответствующие порты вывода, связанные с портами ввода селектора 122 посредством задержек 116 и 118 соответственно. Задержки 116 и 118 обеспечивают компенсацию на время, необходимое для передачи сигнала управления от генератора сигнала управления 120 на селектор 122, в ответ на выходной сигнал предварительного кодера 106 после преобразования в формат последовательных битов. Более конкретно, первый P/S преобразователь 108 преобразует в форму последовательных битов "положительное" информационное слово канала с 25-параллельными битами, переданное от предварительного кодера 106. Второй P/S преобразователь выборочно инвертирует только места нечетных битов "положительного" информационного слова канала с 25-параллельными битами (далее упоминаемое как слово "нечетного канала") и преобразует в формат последовательных битов результирующее "отрицательное" информационное слово канала.

Третий P/S преобразователь 112 выбирает ответное нечетное слово канала из каждого слова канала с 25-параллельными битами, переданное предварительным кодером 106, и преобразует выбранное нечетное слово канала в нечетное слово канала с 13-последовательными битами, переданное от его порта вывода 115 на устройство отображения кода в арифметику 1150. Устройство отображения кода в арифметику 1150 преобразует ЕДИНИЦЫ и НУЛИ слова нечетного канала в арифметические описания NRZI модуляции, которая осуществляет коммутацию отрицательных и положительных арифметических величин с аналогичными амплитудами и не порождает постоянную составляющую. Устройство отображения кода в арифметику 1150 передает эти описания от своего порта вывода 115 на генератор сигнала управления 120. Четвертый P/S преобразователь 114 выбирает места четных битов каждого слова канала с 25-параллельными битами, переданного предварительным кодером 106 (далее упомянутого как слово "четного канала"), и преобразует выбранное четное слово канала в четное слово канала с 12-последовательными битами, передаваемое от его порта вывода 117 на устройство отображения кода в арифметику 1170. Устройство отображения кода в арифметику 1170 преобразует ЕДИНИЦЫ и НУЛИ слова четного канала в арифметические описания I-NRZI модуляции, которая коммутирует отрицательные и положительные арифметические величины аналогичной амплитуды и не порождает постоянной составляющей. Устройство отображения кода в арифметику 1170 передает эти описания от своего порта вывода 117 на генератор сигнала управления 120. Третий и четвертый P/S преобразователи 112 и 114 совместно могут быть спроектированы как мультиплексор с временным разделением.

Генератор сигнала управления 120 генерирует первый и второй сигналы управления на основании сигналов нечетных и четных слов канала, принятых от третьего P/S преобразователя 112 и от четвертого P/S преобразователя 114. Первый сигнал управления CS1 передается с выхода 123 генератора сигнала управления 120 на порт управления предварительного кодера 106 для управления его повторной инициализацией в конце каждого интервала слова канала. Второй сигнал управления CS2 поддерживает одно из двух величин в интервале слова канала и передается от порта вывода 125 генератора сигнала управления 120 на выход порта управления селектором 122.

Селектор 122 принимает очередное "положительное" информационное слово канала с 25-последовательными битами, переданное от первого P/S преобразователя 108, и "отрицательное" информационное слово канала с 25-последовательными битами, переданное от второго P/S преобразователя 110. Затем селектор 122 выбирает в качестве записываемой порции 124 одно из этих слов канала, которое согласно второму сигналу управления CS2 вызовет наименьшее отклонение от спектральной характеристики, необходимой для записывающей дорожки.

Фиг. 9 является детальной блок-схемой устройства ввода сигнала 104, предварительного кодера 106, а также P/S преобразователей 108, 110, 112 и 114, которые показаны на фиг. 8. Работа этих схем, показанных на фиг. 9, будет объяснена со ссылкой на фиг. 10A-10I, 11, 12A, 12B, 13, 14, а также на 15A-15I.

Обратимся к фиг. 9, устройство ввода сигнала 104 состоит из двадцати пяти защелок 104. a-104.y. В ответ на одновременное появление сигнала системного задающего генератора и сигнала загрузки бит "0" вводится в защелку 104. a, используемую для хранения самого старшего разряда, а другие двадцать четыре защелки 104.b-104.y принимают информационное слово с 24-параллельными битами, переданное от порта вывода 103 P/P преобразователя 102. Когда вводятся данные синхронизации, как показано на фиг. 10A-10D, то семнадцать битов данных синхронизации, имеющих заранее определенный формат, вводятся в защелки 104.a- 104.q. Восемь битов данных ID, выводимые из порта вывода 103 P/P преобразователя 102, вводятся в остальные восемь защелок 104.r- 104.y. В случае, когда вводятся данные обработки, как показано на фиг. 10G, двадцать пять битов данных обработки, имеющих заранее определенный формат, вводятся в защелки 104.a-104.y.

Как показано на детальной блок-схеме устройства ввода сигналов 104 на фиг. 11, каждый из двадцати пяти защелок 104.a-104.y состоит соответственно из одного D-триггера, двух вентилей И и одного вентиля ИЛИ. Во время работы соответствующих защелок, когда сигнал ЗАГРУЗКИ имеет высокий логический уровень, бит "0", переданный в порт данных защелки 104.a, и 24-битовое информационное слово, переданное из P/P преобразователя 102, защелкиваются и защелкнутые выходные сигналы передаются посредством Q порта соответствующих D-триггеров. Когда сигнал ЗАГРУЗКИ имеет низкий логический уровень, то защелки, поддерживающие выход Q соответствующих D-триггеров, остаются неизменными.

Первые выходы XOR вентилей 106. a-106.y предварительного кодера 106, показанного на фиг. 9, связываются с выходами соответствующих защелок 104. a-104.y устройства ввода сигнала 104. Вторые входы вентилей исключающего ИЛИ (XOR) 106.a и 106.b соединяется с соответствующими выходами защелок 106.2 и 106.1. Вторые входы вентилей XOR 106.c-106.y соединяются с соответствующими выходами вентилей XOR 106.a-106.w. Выходы вентилей XOR 106.x и 106.y связываются с входами защелок 106.2 и 106.1.

Работа предварительного кодера 106 будет описана ниже. Второй самый младший разряд (LSB) от предыдущего слова канала и самый старший разряд (MSB) (здесь, введенный "0" бит) настоящего 25-битового слова канала вводятся в вентиль XOR 106. a. LSB от предыдущего слова канала и второй самый старший разряд (здесь, первый бит выходных данных) настоящего 25-битового слова канала вводятся в вентиль XOR 106.b. Выход вентиля XOR 106.a и второй бит входных данных вводятся в вентиль XOR 106.c. Выход вентиля XOR 106.b и третий бит входных данных вводятся в вентиль XOR 106.d.