Изобретение относится к области измерительной техники, в частности, к преобразованию временных интервалов и может быть использовано в автоматике, медтехнике, вычислительной технике и телеметрических системах.

Известен способ измерения временных интервалов по а. с. СССР N 1196802, кл. G 04 F 10/04, 1985, предусматривающий совокупность операций: формируют эталонную последовательность, заполняют импульсами этой последовательности измеряемый временной интервал, подсчитывают эти импульсы, уложившиеся на измеряемом интервале, и анализируют состояния этой последовательности в моменты начала и окончания временного интервала, выделяют при анализе событие, заключающееся в том, что состояние импульсной последовательности соответствует логической единице, вычитают из результата подсчета импульсов эталонной последовательности величины, равной половине количества выделенных событий.

Данный способ имеет ограниченную область применения, т.к. для преобразования нескольких временных интервалов он должен быть применен соответствующее количество раз для каждого временного интервала.

Наиболее близким по технической сущности является способ измерения интервалов времени по а. с. СССР N 1661717, кл. G 04 F 10/04, 1991, предусматривающий совокупность операций: формируют N эталонных последовательностей импульсов с заданным периодом следования, подсчитывают количество импульсов от первого входного сигнала до последующего, изменяют независимо и по случайному закону фазовые соотношения импульсов в эталонных последовательностях, суммируют количество подсчитанных импульсов, делят на N и определяют временной интервал.

Наличие операций подсчета импульсов в каждой из сформированных последовательностей, суммирования и деления усложняет алгоритм способа и ограничивает область его применения.

Техническим результатом предлагаемого изобретения является расширение области применения за счет возможности преобразования временных интервалов относительно предыдущего.

Технический результат достигается тем, что в известном способе преобразования интервалов времени, заключающемся в совокупности и последовательности операций: формируют эталонные импульсные последовательности с заданным периодом следования импульсов, подсчитывают число импульсов эталонных последовательностей до последующего входного сигнала, дополнительно определяют критерий окончания подсчета, блокируют подсчет импульсов эталонной последовательности, задают режим преобразования, первым входным сигналом разрешают подсчет импульсов эталонной последовательности, анализируют фазы эталонных последовательностей, передают по результатам анализа для подсчета эталонную последовательность, фаза которой совпала с началом преобразования, стробируют модуляцию фазы относительно момента фазы π при совпадении входного сигнала с фазой (π,2π) эталонной последовательности, формируют сигнал считывания по факту завершения подсчета каждого импульса эталонной последовательности, но исключают формирование сигнала считывания при совпадении входного сигнала с фазой (π,2π) эталонной последовательности, восстанавливают блокирование подсчета импульсов эталонной последовательности при выполнении критерия окончания подсчета, анализируют фазы эталонной последовательности в моменты подачи последующих сигналов, по результатам анализа синхронизируют фазу последующего импульса эталонной последовательности с началом последующего входного сигнала, прерывают по фазе π эталонной последовательности формирование сигнала считывания при поступлении входного сигнала на время, достаточное для выполнения последующих операций, синхронно с прерыванием в момент первой фазы π эталонной последовательности устанавливают исходное состояние, формируют сигнал синхронизации последующей обработки цифрового кода в момент первой фазы π эталонной последовательности при поступлении входного сигнала.

Операция определяют критерий окончания подсчета необходима для определения факта прекращения поступления входной последовательности сигналов, например, по превышению величины временного интервала и достаточна для блокирования подсчета импульсов эталонной последовательности.

Операция блокируют подсчет импульсов эталонной последовательности необходима и достаточна для поддержания исходного состояния ПВЦ до поступления сигналов входной последовательности без формирования сигнала начальной установки после включения питания, что упрощает последующие операции при обеспечении точностных характеристик прототипа.

Операция задают режим преобразования необходима для организации алгоритмов преобразования:

относительно первого входного сигнала или

относительно предыдущего сигнала.

Последнее обеспечивает сокращение объема выходных данных в результате операции подсчитывают. Данная операция достаточна для построения управляемого преобразования единым ПВЦ, т.е. в процессе следования одной последовательности может быть изменен информационный сигнал, получаемый операцией считывают.

Операция разрешают подсчет импульсов эталонной последовательности первым входным сигналом необходима для начала работы по факту поступления входной последовательности сигналов и достаточна для сокращения количества операций начала работы.

Операция стробируют синхронизацию фазы относительно момента фазы π при совпадении входного сигнала с фазой (π,2π) необходима для создания минимально допустимого смещения рабочего фронта относительно фазы π в случае совпадения или минимального смещения момента поступления входного сигнала относительно фазы π и достаточна для обеспечения достоверных результатов преобразования за счет исключения искажений в операции подсчитывают.

Операция формируют сигнал считывания по факту завершения подсчета каждого импульса эталонной последовательности необходима для преобразования случайной последовательности контролируемых сигналов на основе единой операции подсчитывают, выполняемой в момент фазы 0. Операция формируют выполняется с частотой следования эталонной последовательности импульсов, что упрощает алгоритм преобразования и техническую реализацию при высокой достоверности данных ПВЦ.

Операция исключают формирование сигнала считывания при совпадении входного сигнала с фазой (π,2π) эталонной последовательности необходима и достаточна для обеспечения единой погрешности +0.5t с учетом вносимой коррекции в результат преобразования величиной +0.5t. Текущий результат преобразования был считан сформированным предыдущим импульсом эталонной последовательности.

Операция прерывают по фазе π формирование сигнала считывания при поступлении входного сигнала на время, достаточное для выполнения последующих операций, необходима для достоверной обработки полученного цифрового кода последующими операциями и достаточна для сохранения точностных характеристик прототипа.

Операция устанавливают исходное состояние синхронно с прерыванием по факту первой фазы после поступления входного сигнала необходима для построения алгоритма преобразования от предыдущего сигнала до последующего и достаточна для сохранения точностных характеристик прототипа, т.к. исключаются потери в операции подсчитывают.

Операция формируют сигнал подготовки последующей обработки цифрового кода в момент первой фазы эталонной последовательности импульсов при поступлении входного сигнала необходима и достаточна для синхронизации последующих операций с результатами преобразования случайных последовательностей сигналов.

Операция восстанавливают блокирование подсчета импульсов эталонной последовательности импульсов при выполнении критерия окончания подсчета необходима для исключения несанкционированных результатов от функционирующих операций подсчитывают и считывают для последующей обработки при упрощении совокупности операций в нем.

Таким образом, совокупность и последовательность выполнения введенных операций необходимы и достаточны для достижения технического результата:

преобразование последовательности временных интервалов по задаваемому критерию: от первого входного в последовательности ИЛИ от предыдущего до последующего.

Прототипом устройства для реализации данного способа является многоканальное устройство для преобразования временных интервалов по а.с. N1471314 G 04 F 10/04, 1989, в составе совокупности элементов и связей, в том числе генератора эталонной импульсной последовательности, двух триггеров, счетчика, элементов И, элементом ИЛИ, формирователя импульсов.

Недостаток данного устройства заключается в возможности преобразования временных интервалов только относительно первого входного сигнала, что ограничивает область применения.

Техническим результатом предлагаемого изобретения является расширение области применения за счет возможности преобразования временных интервалов относительно предыдущего.

Технический результат достигается тем, что в известный преобразователь временных интервалов в составе первого и второго триггеров, элемента ИЛИ, счетчика, выход которого является шиной данных, входа эталонной импульсной последовательности, отличающийся тем, что вход эталонной импульсной последовательности через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к первым входам элемента ИЛИ и третьего триггера, второй вход которого подключен к входу сигналов и через последовательное соединение четвертого и пятого триггеров, второго формирователя импульсов по следу, второй элемент ИЛИ, счетчик, формирователя по фронту и спаду, элемента И подключен к выходу "Считывание", при этом выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен со вторым входом пятого триггера, а через последовательное соединение первого формирователя импульсов по спаду, элемента ИЛИ-НЕ, первого элемента ИЛИ связан со счетчиком и шестым триггером, выход третьего триггера через второй вход элемента ИЛИ-НЕ связан с элементом И, выход счетчика через второй триггер соединен с другим входом второго элемента ИЛИ, вход преобразователя подключен к второму триггеру, кроме того, второй выход третьего триггера связан с шиной данных, а через последовательное соединение шестого триггера, первого триггера подключен к другому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго формирователя импульсов по спаду соединен с третьим, четвертым триггером и является выходом синхронизации устройства, причем, третий вход четвертого триггера является входом устройства.

Введение шестого триггера с совокупностью связей необходимо и достаточно для модуляции фазы импульсов эталонной последовательности на 180o при совпадении входного сигнала с фазой (π,2π) после подсчета первого импульса этой последовательности.

Введение пятого триггера с совокупностью связей необходимо и достаточно для идентификации факта начала преобразования и окончания без дополнительных внешних сигналов. Факт окончания входной последовательности определяется фактом переполнения счетчика.

Введение третьего триггера необходимо и достаточно для фиксации факта поступления каждого входного сигнала независимо от его длительности на время, достаточное для модуляции фазы, сохранение результатов преобразования, установки исходного состояния.

Введение четвертого триггера с совокупностью связей необходимо и достаточно для выбора фазы π, определяющей начало формирования импульса обнуления блоком.

Введение второго формирователя импульсов по спаду с совокупностью связей необходимо и достаточно для формирования импульса определенной длительности, достаточной для переключения третьего триггера и счетчика через второй элемент ИЛИ.

Введение второго элемента ИЛИ с совокупностью связей необходимо для передачи нескольких сигналов на установочный вход счетчика.

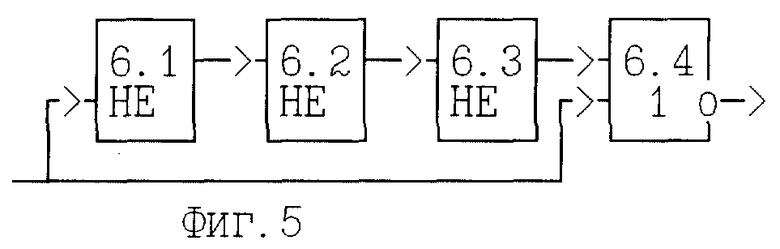

Введение первого формирователя импульсов по спаду с совокупностью связей необходимо для формирования сигнала, длительность которого создавала бы минимально допустимый интервал (фиг. 2/5)между фазой и рабочим фронтом, задаваемым асинхронностью входного сигнала по отношению к эталонной последовательности импульсов.

Введение элемента ИЛИ-НЕ с совокупностью связей необходимо и достаточно для передачи факта модуляции фазы со второго триггера через время, определяемое первым формирователем импульсов по спаду (фиг. 2/6.)

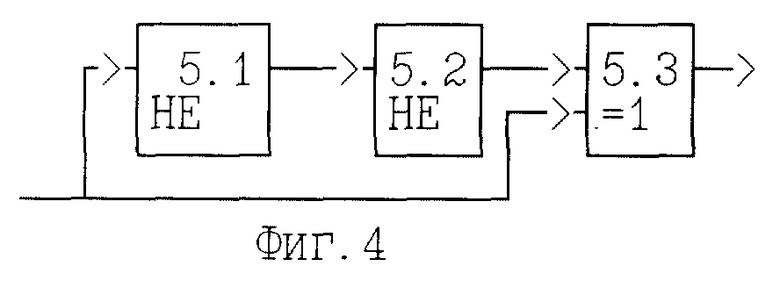

Формирователь импульсов по спаду и фронту сигнала 5 необходим для организации импульса считывания по факту завершения подсчета очередного импульса эталонной последовательности (фиг. 2/6), что упрощает сохранение данных при поступлении входного сигнала.

Введение второго выхода со счетчика необходимо для выдачи информации о факте превышения заданной емкости для идентификации окончания входной последовательности.

Введение третьего выхода со счетчика необходимо и достаточно для идентификации факта окончания переходных процессов при подсчете каждого рабочего фронта, что достаточно для последующего формирования импульсов считывания.

Введение связи выхода третьего триггера с выходом устройства необходимо для дополнения выходных данных информацией о факте модуляции, т.е. фазе эталонной импульсной последовательности, при которой поступил входной сигнал. Этого достаточно для санкционированной коррекции результата преобразования при поступлении двух соседних сигналов в фазу (0,π) и (π,2π), т.к. в этом случае погрешность в пределах (0...t). Вычитание из результата 0,5t позволяет сохранить единую погрешность преобразования ±0,5t.

Введение выхода синхронизации со второго формирователя импульсов по спаду необходимо и достаточно для построения организованной обработки результатов преобразования каждого временного интервала.

Введение элемента И 15 и связи его с выходом триггера 9 необходимо и достаточно для исключения передачи импульса считывания при совпадении переднего фронта входного сигнала с фазой (π,2π) импульса эталонной последовательности.

Введение третьего входа во второй триггер необходимо и достаточно для его установки в исходное состояние после формирования импульса считывания, что исключает формирование его на выходе устройства.

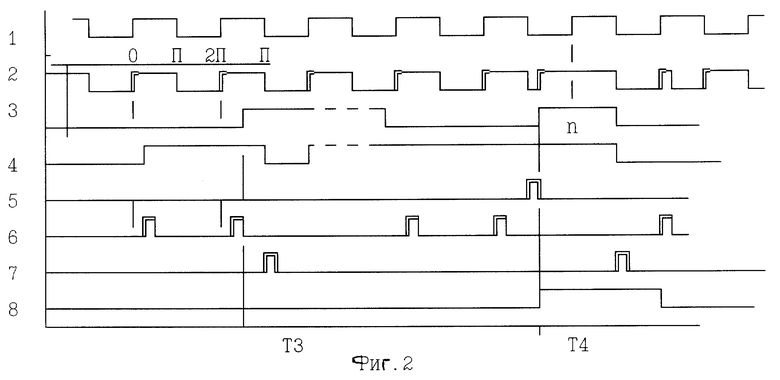

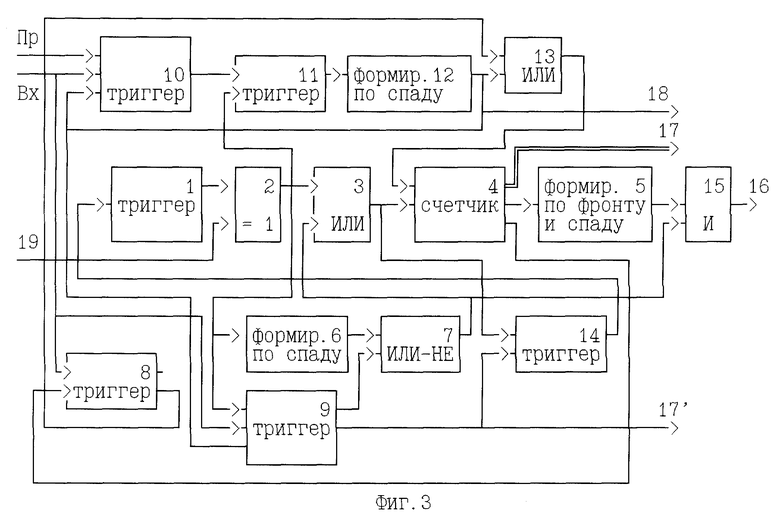

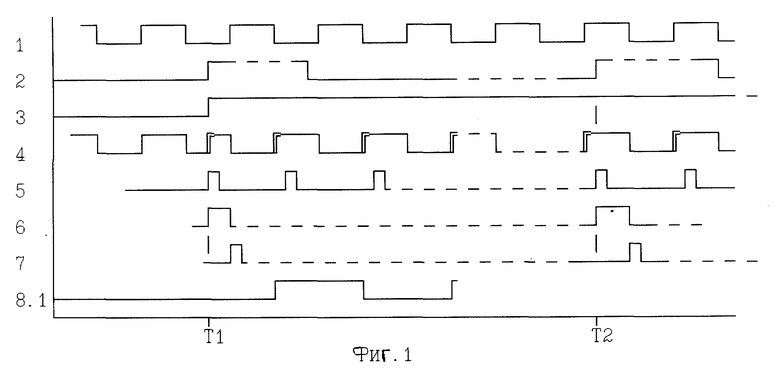

На фиг. 1, 2 представлены временные диаграммы, поясняющие работу способа, на фиг. 3 - вариант устройства для реализации способа, на фиг. 4,5 - варианты формирователей импульсов.

Рассмотрим взаимосвязь и последовательность выполнения операций способа.

Исходное состояние совокупности операций определяется фактом отсутствия входных сигналов и операций задают режим преобразования: от первого входного сигнала или от каждого предыдущего до последующего. Определяют критерий окончания подсчета превышения результатом операции подсчитывают предельной величины и блокируют подсчет эталонных последовательностей импульсов.

Первым сигналом (фиг. 1/2)входной последовательности:

Разрешают подсчет импульсов эталонной последовательности путем снятия блокирования за счет операции регистрируют факт (фиг. 1/3) его поступления, по факту поступления сигнала анализируют фазы эталонных последовательностей импульсов. По результатам анализа синхронизируют ее путем инвертирования (фиг. 1/4/Т1) при совпадении входного сигнала с фазой (π,2π) и сохраняют (фиг. 1/4/Т2) при совпадении с фазой (0,π) В момент фазы π (фиг. 1/7):

исключают результат подсчета (фиг. 1/6), если он произойдет, т.к. устанавливают исходное состояние и подсчитывают (фиг. 1/8.1) (младший разряд) импульсы эталонной последовательности в последующую фазу 0. Формируют сигнал считывания (фиг. 1/5, фиг. 2/6) по факту завершения подсчета каждого импульса эталонной последовательности.

При поступлении последующих сигналов, совпадающих с фазой (0,π) (фиг. 2/3/Т3), анализируют фазы эталонной последовательности, а по результатам анализа сохраняют фазу (фиг. 2/2) последующего входного импульса эталонной последовательности.

При поступлении последующих сигналов, совпадающих с фазой (π,2π) (фиг. 2/3/Т4), анализируют фазы эталонной последовательности, а по результатам анализа синхронизируют фазу последующего входного импульса эталонной последовательности с началом последующего входного сигнала и стробируют (фиг. 2/5) ее для подсчета, затем исключают регистрацию (фиг. 2/2) импульса эталонной последовательности и формирование импульса считывания (фиг. 2/6/Т4).

Каждым поступающим сигналом устанавливают исходное состояние в момент первой фазы π эталонной последовательности импульсов (фиг. 2/Т3, фиг. 2/Т4) и формируют сигнал синхронизации для последующей обработки результатов преобразования.

При отсутствии сигналов входной последовательности по заданному критерию, например превышение величины временного интервала, восстанавливают блокирование подсчета как идентификатор окончания работы.

Устройство для реализации данного способа фиг. 3 содержит первый триггер 1, элемент исключающее ИЛИ 2, первый элемент ИЛИ 3, счетчик 4, формирователь 5 по фронту и спаду, формирователь импульсов по спаду 6, первый элемент ИЛИ/НЕ 7, второй, третий, четвертый, пятый триггеры 8, 9, 10, 11, второй формирователь по спаду 12, второй элемент ИЛИ 13, входную шину вх, программирующий вход Пр, шестой триггер 14, элемент И 15, выход считывания 16, шину данных 17, 17', выход синхронизации 18, вход импульсов эталонной последовательности 19.

Формирователи импульсов могут быть реализованы по схемам, вариант которых дан на фиг. 4,5.

Входная шина ВХ через последовательное соединение триггеров 10, 11, формирователь импульсов по спаду 12, элемент ИЛИ 13, первый вход счетчика 4 подключена с первого выхода к формирователю 5 импульсов по фронту и спаду, а через триггер 8 связана с другим входом элемента ИЛИ 13, выход триггера 14 через последовательное соединение триггера 1, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элемента ИЛИ 3, другой вход счетчика 4 и второй его выход подключена к другому входу триггера 8. Третий выход счетчика 4 является шиной данных 17, а выход формирователя 5 импульсов по фронту и спаду через элемент И 15 является выходом 16 импульсов считывания. Вход 19 импульсов эталонной последовательности связан с другим входом ИСКЛЮЧАЮЩЕЕ ИЛИ 2. Причем вход ВХ через последовательное соединение триггера 9 и элемента ИЛИ-НЕ 7 связан со вторыми входами элемента ИЛИ 3 и элемента И 15. Кроме того, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен ко входам формирователя по спаду 6 триггеров 9, 11, а выход второго формирователя импульсов по спаду 12 соединен с третьим входом второго триггера 9 и является выходом синхронизации 18 устройства, программирующий вход Пр - с шестым триггером 14.

В исходном состоянии триггер 8 выключен сигналом переполнения счетчика 4, что блокирует через элемент ИЛИ 13 работу счетчика 4. Триггер 9 установлен в исходное состояние, исключающем срабатывание триггера 14, блокирование импульсов с выхода элемента 2 и разрешающем передачу импульсов через элемент И 15. Потенциал с триггера 9 через элемент ИЛИ-НЕ 7 обеспечивает передачу импульсов с выхода элемента 2 на вход счетчика 4 с выхода элемента 3. Состояние триггера 1 - произвольное. Потенциал со входа Пр определяет режим работы: уровень "1" - преобразование относительно первого сигнала, "0" - относительно предыдущего.

При поступлении сигналов входной последовательности (фиг. 1/2 срабатывают: триггер 8, снимающий блокировку счетчика 4,(фиг. 1/3),

триггер 10, если преобразование должно быть от предыдущего, триггер 9, если входной сигнал совпал с фазой (π,2π) (фиг. 1/6/Т1).

Рассмотрим работу в случае совпадения входного сигнала с фазой (0,π) (фиг. 1/Т2, фиг. 2/Т3). В этом случае счетчик сработает через время (0,5t, t),

т. е. с погрешностью О. .. 0,5 t. Фактом срабатывания первого разряда (фиг. 1/8.1) счетчика 4 в момент фазы 0 санкционируется срабатывание формирователя 5 импульсов для организации считывания содержимого счетчика 4. Подобный алгоритм упрощает построение считывания и снижает вероятность искажений при различных сочетаниях момента поступления входного сигнала и импульсов эталонной последовательности. Режим работ аналогичен для последующих входных сигналов при совпадении с фазой (0,π).

Центрированная погрешность в этом случае, т. е. при сочетаниях фаз (0,π), (π,2π) - ±0,5t, где t - период следования импульсов эталонной последовательности.

При поступлении последующих импульсов, совпадающих с фазой (π,2π) (фиг. 2/3/Т4), анализируют на триггере 9 фазы эталонной последовательности, а по результатам анализа синхронизируют при помощи формирователя 6 импульса и элемента ИЛИ-НЕ 7 фазу последующего входного импульса эталонной последовательности с началом последующего входного сигнала и стробируют при помощи формирователя 6 импульсов (фиг. 2/5) ее для подсчета, затем исключают при помощи элемента 7 ИЛИ-НЕ регистрацию (фиг. 2/2/n) импульса эталонной последовательности, а при помощи элемента 15 И формирование импульса на выходе 16. Далее цикл повторяется аналогично с фазой (0,2π), т.е. формируется импульс считывания (фиг. 2/6/T4). Импульс установки (фиг. 2/7) обеспечивает кроме установки в исходное состояние (в соответствии с выбранной программой по входу Вх) и постоянство начальной погрешности +0.5t.

Погрешность результата преобразования в данном случае считывания находится в пределах ±0.5t, что обеспечивает суммарную погрешность t. Индикатор фазы с триггера 9 используется для коррекции результата на -0.5t, что обеспечивает погрешность результата в пределах ±0.5t.

При отсутствии (превышении) входных сигналов счетчик сигналом переполнения со старшего разряда инициирует выключение триггера 8, что блокирует работу преобразователя до поступления следующего сигнала по входу Вх.

Таким образом, положительный эффект от предлагаемого изобретения определяется:

- преобразованием последовательности временных интервалов с программируемым законом: от первого входного или от каждого предыдущего до последующего,

- для начала и окончания преобразования не требуется отдельного сигнала.

Способ преобразования и вариант его технической реализации был апробирован в макете аппаратуры на ИС серии 564 при преобразовании входных сигналов с дискретностью между ними более 5 мкс и на ИС серии 1533 при частоте импульсов эталонной последовательности 10 МГц, где была подтверждена погрешность преобразования в пределах ±50 нс. Работоспособность и эффективность способа и его технической реализации была подтверждена при обработке электрокардиосигнала в качестве оценки промышленной применимости. В составе кардиомонитора была подтверждена возможность построения подобной аппаратуры без средств вычислительной техники для индивидуального пользователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПРЕОБРАЗОВАНИЯ ИНТЕРВАЛОВ ВРЕМЕНИ | 1991 |

|

RU2069888C1 |

| СПОСОБ И УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1994 |

|

RU2098862C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ СИГНАЛА СЛУЧАЙНОГО ПРОЦЕССА | 1993 |

|

RU2072563C1 |

| СИСТЕМА ДИАГНОСТИКИ ПО СТАТИЧЕСКОМУ НИЗКОЧАСТОТНОМУ СИГНАЛУ | 1997 |

|

RU2128843C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1990 |

|

RU2024194C1 |

| СПОСОБ ИДЕНТИФИКАЦИИ СИГНАЛА СЛУЧАЙНОГО ПРОЦЕССА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2097917C1 |

| КОМПЛЕКС МНОГОКАНАЛЬНОЙ ЭКСПРЕСС ДИАГНОСТИКИ | 1997 |

|

RU2152073C1 |

| СПОСОБ И УСТРОЙСТВО ЦИФРОВОЙ ДЕМОДУЛЯЦИИ ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1996 |

|

RU2130695C1 |

| УСТРОЙСТВО ВЫДЕЛЕНИЯ ОГИБАЮЩЕЙ СИГНАЛА СЛУЧАЙНОГО ПРОЦЕССА | 1996 |

|

RU2119189C1 |

| УСТРОЙСТВО ИДЕНТИФИКАЦИИ СХОДА С РЕЛЬСОВ ВАГОНА ПОДВИЖНОГО СОСТАВА | 2000 |

|

RU2199456C2 |

Изобретение может быть использовано для измерения временных интервалов в автоматике, медтехнике, вычислительной технике и телеметрических системах. Способ основан на подсчете импульсов эталонной последовательности, уложившихся на исследуемом интервале, и коррекции данных подсчета по результатам анализа, фаз эталонной последовательности в начале и конце измеряемого интервала. Новым является то, что перед началом преобразования определяют критерий окончания подсчета и задают режим преобразования. Для подсчета передают последовательность, фаза которой совпала с началом преобразования. При поступлении входного сигнала, совпадающего с фазой (π,2π) эталонной последовательности, стробируют модуляцию фазы эталонной последовательности относительно момента фазы π и исключают формирование сигнала считывания. Фазу последующего импульса эталонной последовательности синхронизируют с началом последующего входного сигнала. Корректируют результат подсчета при совпадении входного сигнала с фазой (π,2π) эталонной последовательности. При выполнении критерия окончания подсчета подсчет импульсов блокируют. Формируют сигнал синхронизации последующей обработки цифрового кода в момент первой фазы π эталонной последовательности при поступлении входного сигнала. Способ позволяет выполнять преобразование с программируемым законом: от первого входного сигнала или от каждого предыдущего до последующего. 2 с.п. ф-лы, 5 ил.

| SU 1196802 A, 07.12.85 | |||

| Устройство для измерения временного интервала | 1990 |

|

SU1793426A1 |

| Способ измерения временных интервалов и устройство для его осуществления | 1989 |

|

SU1661717A1 |

| Устройство для измерения временного интервала | 1990 |

|

SU1817056A1 |

Авторы

Даты

1999-10-10—Публикация

1995-10-17—Подача