Изобретение относится к системе цифровой передачи, имеющей передатчик и приемник, имеющие соответственно кодер и декодер для поддиапазонного кодирования цифрового сигнала, в частности, звукового, имеющего заданную частоту выборки Fs. Кодер принимает цифровой сигнал для генерации М сигналов поддиапазона с уменьшением частоты дискретизации, причем кодер делит диапазон цифрового сигнала на последовательные поддиапазоны номеров m (1 ≤ m ≤ M), увеличивающихся с частотой, а декодер получает М сигналов поддиапазонов для формирования копии цифрового сигнала, причем декодер преобразует поддиапазон в диапазон цифрового сигнала с возрастанием частоты дискретизации.

Изобретение также относится к передатчику и приемнику, предназначенным для использования в системе цифровой передачи.

Известна система поддиапазонного кодирования, в которой используется деление диапазонов речевого сигнала на некоторое число поддиапазонов, ширина которых приблизительно соответствует ширине диапазона критических диапазонов органов слуха человека в соответствующих диапазонах частот; причем указанное деление основано на психоакустических экспериментах, результаты которых показывают, что в таком поддиапазоне шумы квантования будут оптимально подавлены сигналами в пределах этого поддиапазона, когда квантование учитывает характеристику подавления органов слуха (см. M.E.Krasner "The critical Band Coder-Diqital eucoding of speech signals based on the perceptual Requirements of the auditory system". Proc. IEEE ICASS p. 80, Vol. 1, pp. 327-311, April 9-11, 1980).

Задачей изобретения является создание системы, обеспечивающей уменьшение искажений из-за наложения спектров в восстановленном сигнале на стороне приемника, а также создание передатчика и приемника, обеспечивающих повышение эффективности обработки передаваемого и принимаемого сигналов в отношении времени, затрачиваемого на обработку, и уменьшение сложности схем, реализующих указанную обработку.

Указанный результат достигается тем, что в системе цифровой передачи, содержащей передатчик и приемник, причем передатчик содержит поддиапазонный кодер, а приемник содержит поддиапазонный декодер, при этом поддиапазонный кодер имеет вход для приема цифрового сигнала, такого как цифровой аудиосигнал, с заданной частотой дискретизации Fs, и М выходов для выдачи М сигналов поддиапазонов с уменьшением частоты дискретизации, а поддиапазонный декодер имеет М входов для приема М сигналов поддиапазонов и выход для выдачи копии цифрового сигнала, в соответствии с изобретением поддиапазонный кодер содержит блок анализирующих фильтров и первый блок обработки сигналов, блок анализирующих фильтров содержит М анализирующих фильтров, каждый из которых имеет один вход и два выхода, 2M выходов анализирующих фильтров соединены с 2M выходами блока анализирующих фильтров, каждый из 2M выходов анализирующих фильтров соединен с соответствующим одним из 2M входов первого блока обработки сигналов, первый блок обработки сигналов имеет М выходов, соединенных с М выходами поддиапазонного кодера, а поддиапазонный декодер содержит второй блок обработки сигналов и блок синтезирующих фильтров, второй блок обработки сигналов имеет М входов для приема М сигналов поддиапазонов и 2M выходов, блок синтезирующих фильтров содержит М синтезирующих фильтров, каждый из которых имеет два входа и один выход, каждая пара выходов второго блока обработки сигналов соединена с парой входов соответствующего одного из М синтезирующих фильтров, причем каждый выход синтезирующего фильтра имеет возможность соединения с выходом блока синтезирующих фильтров, где М - четное число, при этом поддиапазонный кодер выполнен в виде кодера поддиапазонов с равной шириной полос, анализирующие фильтры и синтезирующие фильтры имеют умножители с коэффициентами умножения, значения которых получены из значений нечетного числа коэффициентов стандартного фильтра (H(f)), при этом стандартный фильтр имеет характеристику фильтра нижних частот с шириной полосы, примерно равной половине ширины полосы поддиапазонов (B1, B2...), а для обеспечения равенства числа коэффициентов числу коэффициентов умножения для анализирующих фильтров и синтезирующих фильтров к матрице коэффициентов стандартного фильтра добавлены нули.

При этом блок анализирующих фильтров предпочтительно содержит первый блок, имеющий вход, являющийся входом кодера для приема выборок цифрового сигнала, и М выходов для выдачи М выходных сигналов с частотой дискретизации Fs/M, причем упомянутый первый блок предназначен для выдачи на М выходов каждый раз М выборок в виде последовательных блоков из М выборок цифрового входного сигнала, так что m-ая выборка каждого блока подается на m-ый выход, каждый из М выходов связан со входом соответствующего одного из М анализирующих фильтров, а блок синтезирующих фильтров содержит второй блок, имеющий М входов, соединенных с М выходами синтезирующих фильтров, и выход, связанный с выходом блока синтезирующих фильтров, причем упомянутый второй блок предназначен для упорядочивания М выборок, каждый раз, когда они подаются на М входов, в блок из числа последовательных блоков, состоящих из М выборок, так чтобы выборки, принимаемые на m-ом входе, располагались в m-ой позиции в последовательных блоках, выдаваемых на выход.

Кроме того, каждый анализирующий фильтр может содержать последовательный ряд элементов задержки, имеющих одинаковую задержку T, вход анализирующего фильтра соединен с входом первого элемента задержки, выходы по меньшей мере нескольких элементов задержки с нечетными номерами в указанном последовательном ряду соединены с соответствующими входами первого блока объединения сигналов, а выходы по меньшей мере нескольких элементов задержки с четными номерами в указанном последовательном ряду соединены с соответствующими входами второго блока объединения сигналов, причем выходы первого и второго блоков объединения сигналов связаны соответственно с первым и вторым выходами анализирующего фильтра.

При этом каждый анализирующий фильтр предпочтительно содержит два последовательных ряда элементов задержки, имеющих одинаковую задержку 2 T, вход анализирующего фильтра связан с входами первого и по меньшей мере нескольких других элементов задержки в каждом из последовательных рядов, выходы двух последовательных рядов элементов задержки связаны соответственно с первым и вторым выходом анализирующего фильтра, причем дополнительный элемент задержки, имеющий задержку, равную половине задержки элементов задержки в упомянутых последовательных рядах, подсоединен в тракт сигнала от входа к второму выходу анализирующего фильтра.

Кроме того, каждый синтезирующий фильтр предпочтительно содержит два последовательных ряда элементов задержки, имеющих одинаковую задержку, первый и второй входы синтезирующего фильтра связаны с входом первого элемента задержки первого и второго последовательных рядов соответственно, выходы по меньшей мере нескольких элементов задержки в первом последовательном ряду соединены с соответствующими входами блока объединения сигналов, выходы по меньшей мере нескольких элементов задержки во втором последовательном ряду также соединены с соответствующими входами блока объединения сигналов, а выход блока объединения сигналов соединен с выходом синтезирующего фильтра, и дополнительный элемент задержки, имеющий задержку, равную половине задержки элементов задержки в последовательных рядах, подсоединен в тракт сигнала от второго входа к выходу синтезирующего фильтра.

А также каждый синтезирующий фильтр может содержать последовательный ряд элементов задержки, имеющих одинаковую задержку T, первый вход синтезирующего фильтра связан с входами по меньшей мере нескольких элементов задержки с нечетными номерами в упомянутом последовательном ряду, второй вход синтезирующего фильтра связан с входами по меньшей мере нескольких элементов задержки с четными номерами в последовательном ряду, а выход последнего элемента задержки связан с выходом синтезирующего фильтра.

При этом блок обработки сигнала может содержать М блоков объединения сигналов, каждый из которых имеет выход, связанный с одним из М выходов блока обработки сигналов, причем для каждого блока объединения сигналов по меньшей мере несколько входов из 2M входов блока обработки сигналов связаны с соответствующими входами указанного блока объединения сигналов через соответствующие умножители.

Кроме того, второй блок обработки сигналов может содержать 2M блоков объединения сигналов, каждый из которых имеет выход, связанный с соответствующим одним из 2M выходов блока обработки сигналов, причем для каждого блока объединения сигналов по меньшей мере несколько входов из М входов блока обработки сигналов соединены с соответствующими входами указанного блока объединения сигналов через соответствующие умножители.

При этом два выхода каждого анализирующего фильтра предпочтительно соединены с соответствующими входами блока обработки сигналов через соответствующий блок усиления сигналов, оба блока усиления сигналов предназначены для усиления сигналов, подаваемых на их входы, на одинаковую комплексную величину, два выхода каждой пары выходов второго блока обработки сигналов соединены с соответствующим входом синтезирующего фильтра через соответствующий блок усиления сигналов, оба блока усиления сигналов предназначены для усиления сигналов, подаваемых на их входы, на одинаковую комплексную величину, а каждый из М входов декодера соединен с соответствующим одним из М входов второго блока обработки сигналов через блок усиления сигналов, предназначенный для усиления сигнала, подаваемого на его вход, на вторую комплексную величину.

При этом блок обработки сигналов предпочтительно содержит средство переключения и М блоков объединения сигналов, каждый из 2M входов блока обработки сигналов соединен с соответствующим одним из 2M входов средства переключения, имеющего один выход, соединенный с входом каждого из М блоков объединения сигналов, каждый из которых содержит умножитель, блок памяти, имеющий 2M ячеек памяти, сумматор и накапливающий регистр, вход блока объединения сигналов и выход блока памяти соединены соответственно с первым и вторым входами умножителя, выход умножителя и выход накапливающего регистра соединены соответственно с первым и вторым входами сумматора, выход сумматора соединен со входом накапливающего регистра, выход накапливающего регистра m-го блока объединения сигналов соединен с m-ым выходом блока обработки сигналов, средство переключения предназначено для циклического соединения каждого из 2M его входов с его выходом так, чтобы выдавать выборки, в блоках по М выборок, поступающие на 2M его входов, по одной выборке на каждом входе, последовательно на его выход, при этом блок памяти, содержащий 2M коэффициентов умножения, предназначен для циклической подачи 2M коэффициентов умножения на его выход таким образом, чтобы i-ый коэффициент умножения подавался на выход блока памяти, когда средство переключения подает i-ую выборку в блоке из 2M выборок на свой выход, где i изменяется от 1 до 2M, сумматор и накапливающий регистр предназначены для суммирования результата i-го умножения с содержимым накапливающего регистра, накапливающий регистр, кроме того, предназначен для подачи его содержимого, полученного после 2 M-го шага умножения, на выход (10.m) блока объединения сигналов и для установки после этого в нуль содержимого регистра.

Кроме того, второй блок обработки сигналов предпочтительно содержит средство переключения и 2M блоков объединения сигналов, каждый из М входов этого второго блока обработки сигналов соединен с соответствующим одним из М входов средства переключения, средство переключения имеет один выход, соединенный со входом каждого из 2M блоков объединения сигналов, каждый блок объединения сигналов содержит умножитель, блок памяти, имеющий М ячеек памяти, сумматор и накапливающий регистр, вход указанного блока объединения сигналов и выход блока памяти соединены соответственно с первым и вторым входами умножителя, выход умножителя и выход накапливающего регистра соединены соответственно с первым и вторым входами сумматора, выход сумматора соединен со входом накапливающего регистра, выход накапливающего регистра i-го блока объединения сигналов соединен с i-ым выходом второго блока обработки сигналов, где i изменяется от 1 до 2M, указанное средство переключения предназначено для циклического соединения каждого из его входов с его выходом так, чтобы выдавать каждый раз выборки, в блоки по М выборок, которые появляются на его М входах, по одной выборке на каждом входе, последовательно к его выходу, причем блок памяти содержит М коэффициентов умножения и предназначен для циклической выдачи М коэффициентов умножения на его выход так, чтобы m-ый коэффициент умножения подавался на его выход, когда средство переключения выдает m-ую выборку из М выборок в блоке на свой выход, сумматор и накапливающий регистр предназначены для суммирования результата m-го умножения с содержимым этого накапливающего регистра, накапливающий регистр, кроме того, предназначен для подачи его содержимого, полученного после M-го шага умножения, на выход блока объединения сигналов и для установки после этого в нуль содержимого регистра.

Указанный технический результат достигается также тем, что в передатчике для передачи цифрового сигнала, включающем кодер для поддиапазонного кодирования цифрового сигнала, такого как цифровой аудиосигнал, с заданной частотой дискретизации Fs, причем кодер реагирует на цифровой сигнал для генерации ряда сигналов М поддиапазонов с уменьшением частоты дискретизации, и кодер делит полосу цифрового сигнала на последовательные поддиапазоны с номерами полос m (1<m<M), увеличивающимися с возрастанием частоты, в соответствии с изобретением, кодер содержит блок анализирующих фильтров и блок обработки сигналов, при этом блок анализирующих фильтров содержит М анализирующих фильтров, каждый из которых имеет один вход и два выхода, 2M выходов анализирующих фильтров соединены соответственно с 2M выходами блока анализирующих фильтров для выдачи 2M выходных сигналов с частотой дискретизации Fs/M, каждый анализирующий фильтр предназначен для осуществления двух различных процедур фильтрации для сигнала, поданного на его вход, и для выдачи двух отфильтрованных вариантов входного сигнала на соответствующий один из двух выходов, каждый из 2M выходов фильтров соединен с соответствующим одним из 2 М входов блока обработки сигналов, блок обработки имеет М выходов, связанных с М выходами кодера, для выдачи сигналов М поддиапазонов, при этом блок обработки сигналов предназначен для подачи выходных сигналов на каждый из М выходов, причем выходной сигнал является комбинацией по меньшей мере ряда входных сигналов, поданных на 2 М входа, а кодер предназначен для деления полосы цифровых сигналов на последовательные поддиапазоны примерно равной ширины полосы, при этом коэффициенты каждого из анализирующих фильтров получены из коэффициентов стандартного фильтра, имеющего характеристику фильтра нижних частот с шириной полосы, примерно равной половине ширины полосы поддиапазонов, причем коэффициенты анализирующих фильтров получены из стандартного фильтра, имеющего нечетное число коэффициентов, М является четным числом, а для обеспечения равенства числа коэффициентов стандартного фильтра числу коэффициентов умножения каждого из анализирующих и синтезирующих фильтров к матрице коэффициентов стандартного фильтра добавлены нули.

Передатчик в одном из вариантов осуществления выполнен в виде устройства записи цифрового аудиосигнала на носитель записи и дополнительно содержит средство записи, имеющее М входов, каждый из которых соединен с соответствующим одним из М выходов блока обработки, причем средство записи предназначено для записи сигналов М поддиапазонов, подаваемых на его М входов, на дорожку носителя записи.

Кроме того, указанный технический результат достигается тем, что в приемнике для приема цифрового сигнала, который закодирован при передаче в виде ряда сигналов М поддиапазонов, путем деления полосы цифрового сигнала на поддиапазоны с примерно равной шириной полосы с уменьшением частоты дискретизации, причем декодер реагирует на сигналы М поддиапазонов для формирования копии цифрового сигнала и обеспечивает объединение поддиапазонов в полосу цифрового сигнала с увеличением частоты дискретизации, в соответствии с изобретением декодер содержит блок обработки сигнала и блок синтезирующих фильтров, при этом блок обработки сигнала имеет М входов для приема сигналов М поддиапазонов и 2 М выходов, блок синтезирующих фильтров содержит М синтезирующих фильтров, каждый из которых имеет два входа и один выход, соединенный с выходом декодера, блок обработки сигналов предназначен для генерации выходного сигнала на каждом из его 2 М выходов, причем выходной сигнал представляет собой комбинацию по меньшей мере нескольких входных сигналов, поступающих на его М входов, каждая пара выходов блока обработки сигналов соединена с парой входов соответствующего из М синтезирующих фильтров, каждый синтезирующий фильтр имеет один выход и предназначен для осуществления различной процедуры фильтрации для двух сигналов, подаваемых на два входа, и для выдачи комбинации двух отфильтрованных сигналов на его выход, каждый выход предназначен для соединения с выходом блока синтезирующих фильтров для выдачи копии цифрового сигнала с частотой дискретизации Fs, при этом коэффициенты каждого из синтезирующих фильтров получены из коэффициентов стандартного фильтра, имеющего характеристику фильтра нижних частот с шириной полосы, примерно равной половине ширины полосы поддиапазонов, причем коэффициенты синтезирующих фильтров получены из стандартного фильтра, имеющего нечетное число коэффициентов, М является четным числом, а для обеспечения равенства числа коэффициентов стандартного фильтра числу коэффициентов умножения каждого из анализирующих и синтезирующих фильтров к матрице коэффициентов стандартного фильтра добавлены нули.

При этом в одном из вариантов осуществления приемник выполнен в виде устройства воспроизведения цифрового аудиосигнала, предназначенного для воспроизведения цифрового аудиосигнала с носителя записи, и дополнительно содержит средство воспроизведения, имеющее М выходов, каждый из которых соединен с соответствующим одним из М входов блока обработки, причем средство воспроизведения предназначено для считывания сигналов М поддиапазонов с дорожки носителя записи.

Изобретение поясняется на примерах осуществления, иллюстрируемых чертежами, на которых показано следующее:

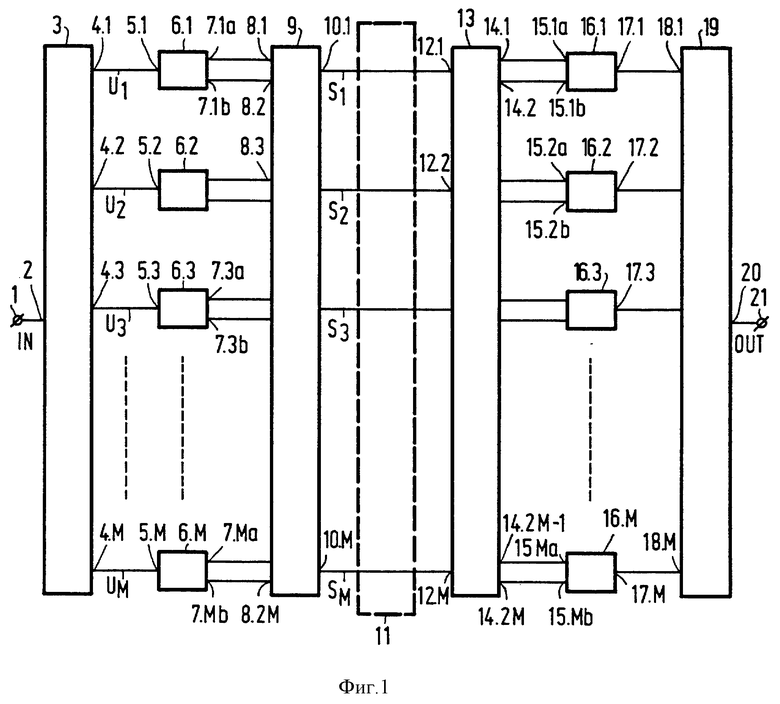

фиг. 1 - блок-схема системы цифровой передачи в соответствии с изобретением,

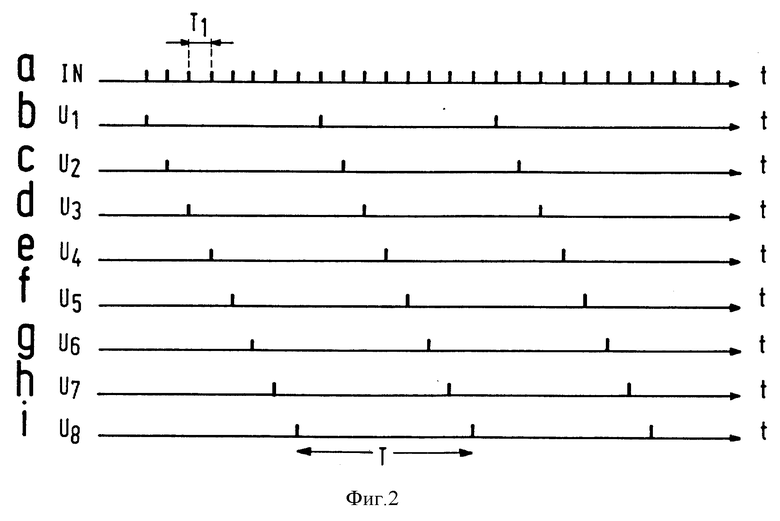

фиг. 2 - реализация принципа повышения частоты дискретизации с помощью первого блока,

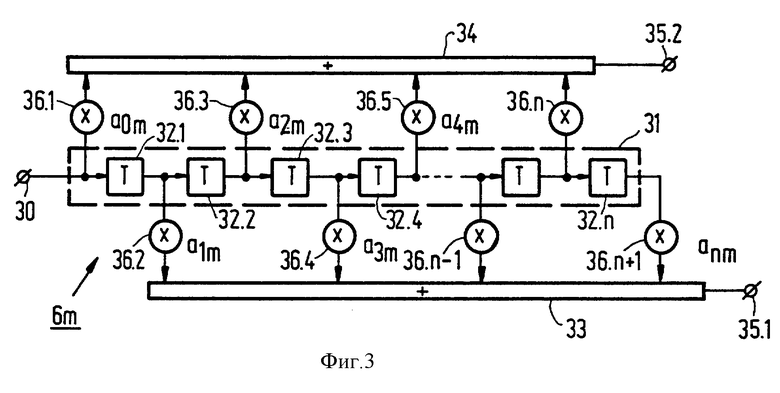

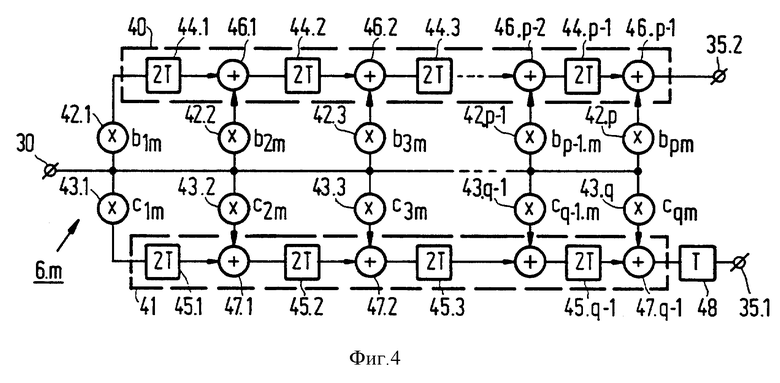

фиг. 3 и 4 - два варианта анализирующего фильтра в системе цифровой передачи,

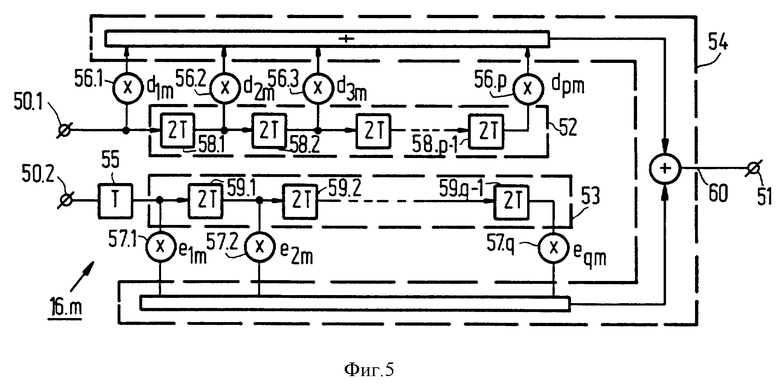

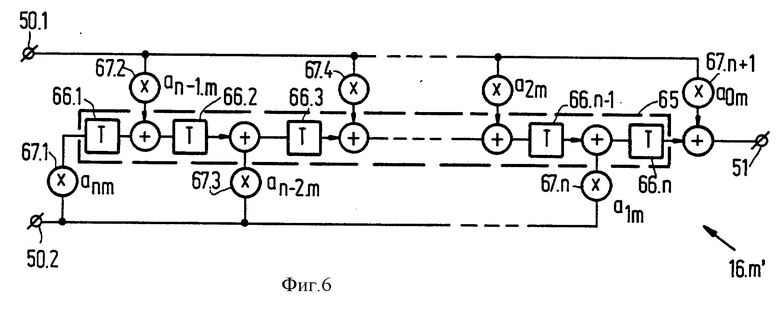

фиг. 5 и 6 - два варианта синтезирующего фильтра в системе цифровой передачи,

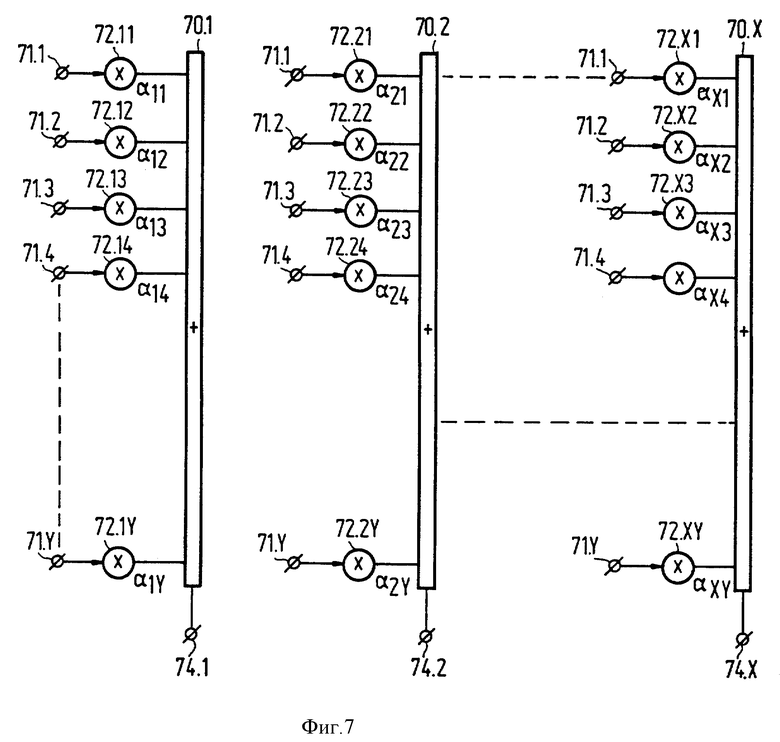

фиг. 7 - возможный вариант осуществления блока обработки сигналов в передатчике или второго блока обработки сигналов в приемнике,

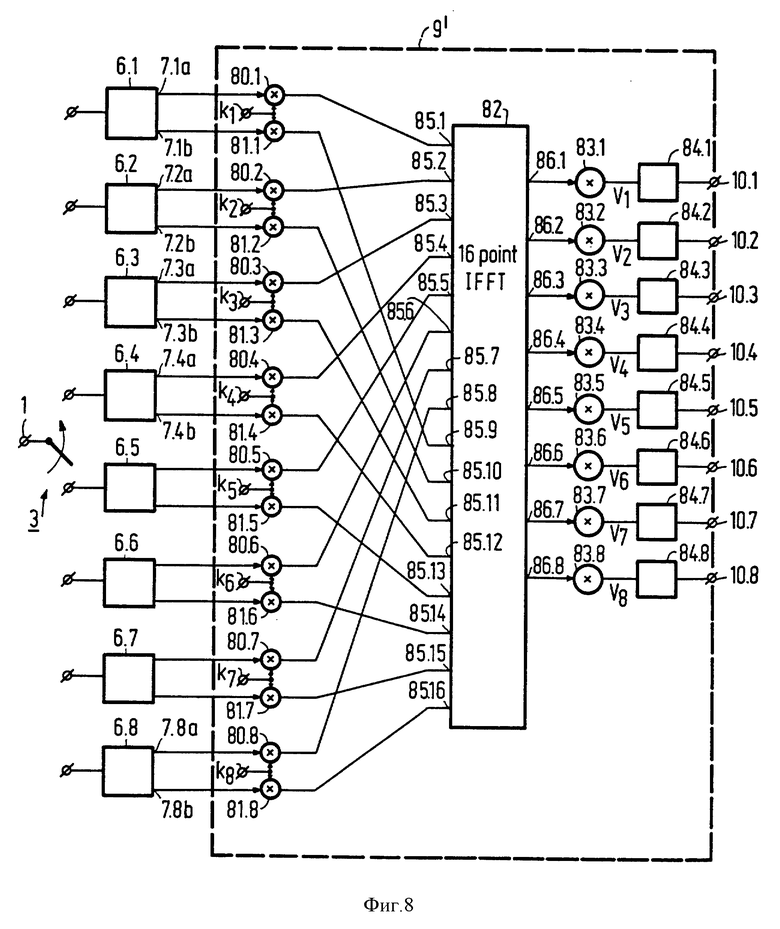

фиг. 8 - второй вариант осуществления передатчика в системе цифровой передачи,

фиг. 9 - второй вариант осуществления приемника в системе цифровой передачи,

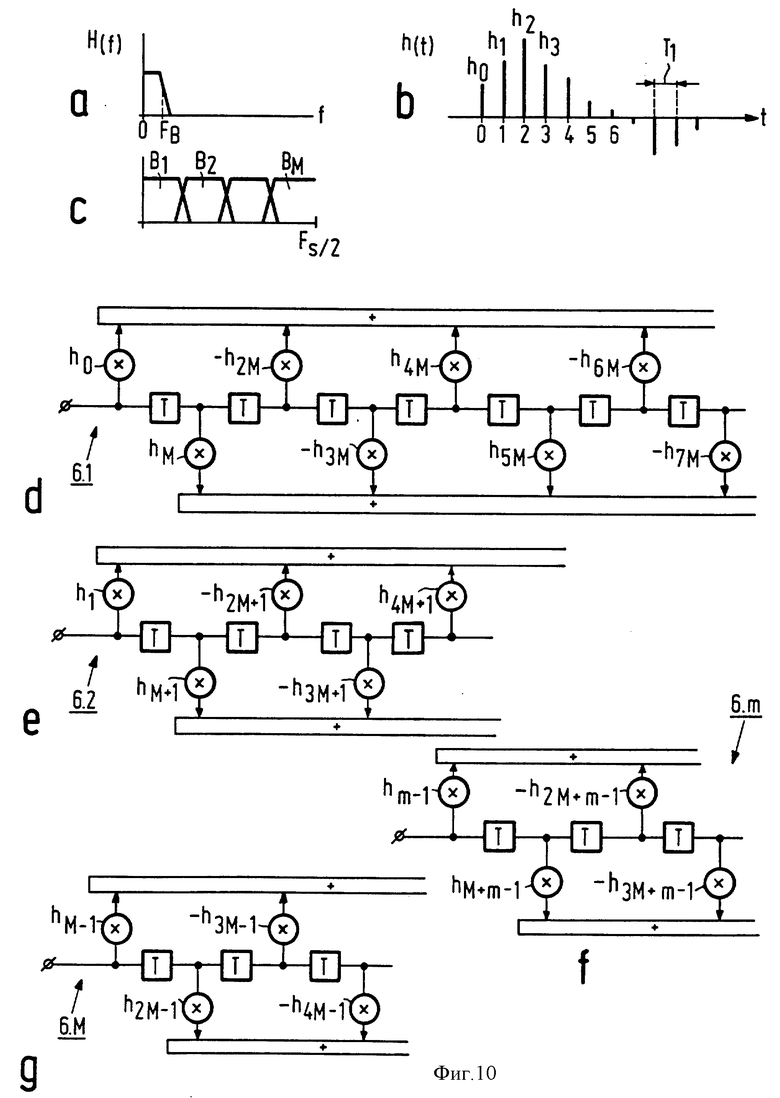

фиг. 10 - иллюстрация получения коэффициентов анализирующих фильтров в приемнике,

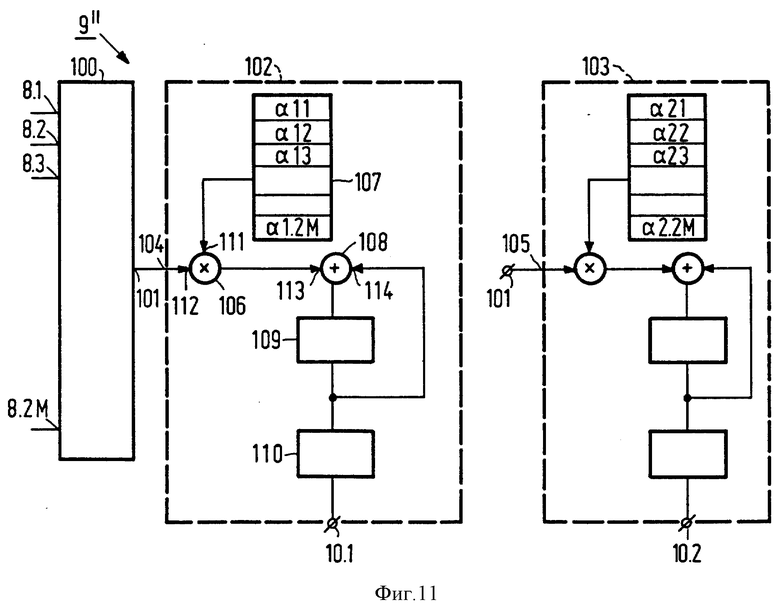

фиг. 11 - другой вариант осуществления блока обработки сигналов в передатчике, или второго блока обработки сигналов в приемнике,

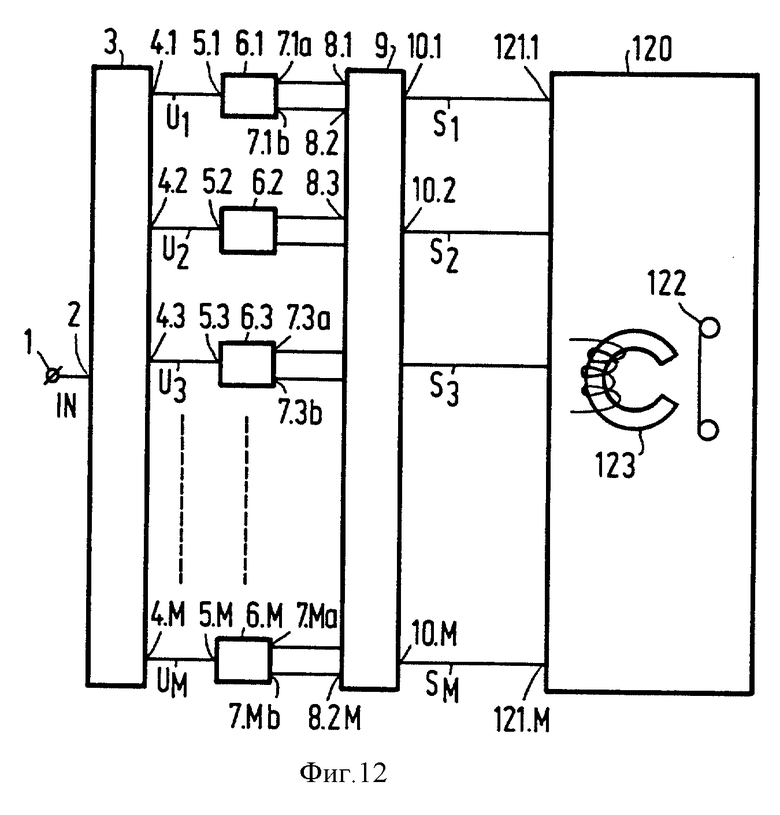

фиг. 12 - устройство записи цифровых сигналов и

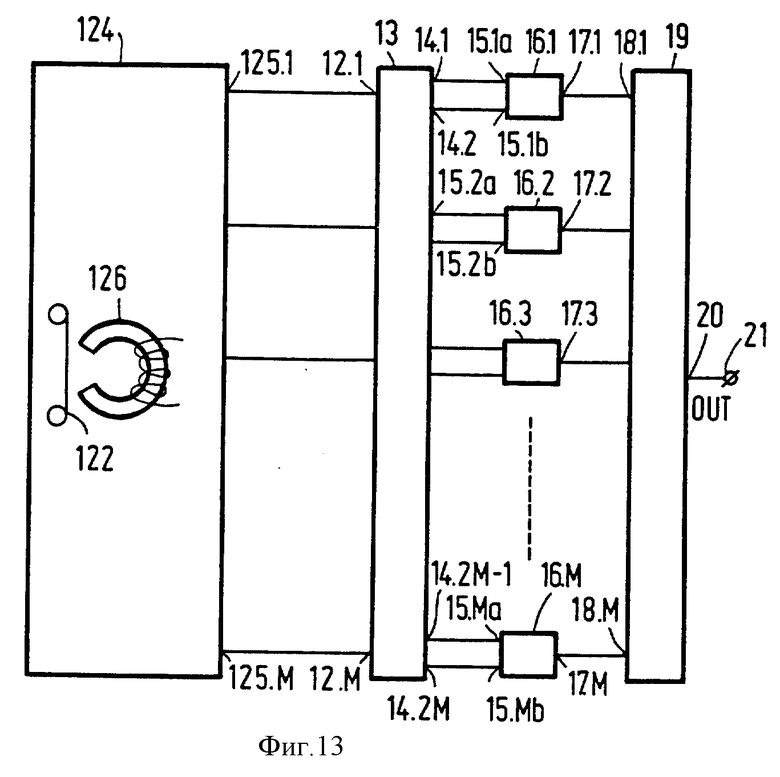

фиг. 13 - устройство воспроизведения цифровых сигналов.

На фиг. 1 представлена блок-схема системы цифровой передачи. Система цифровой передачи имеет вход 1, подсоединенный ко входу 2 первого блока 3 для приема цифрового сигнала IN, имеющего заданную частоту дискретизации Fs. Первый блок 3 имеет М выходов 4.1 по 4.M, на которых присутствуют выходные сигналы U1-Um. Первый блок 3 предназначен для обеспечения понижения частоты дискретизации в М раз во входном сигнале IN, поданном на его вход 2. Функционирование первого блока пояснено ниже со ссылками на фиг. 2. Представлены M анализирующих фильтров 6.1-6. М, причем каждый анализирующий фильтр m, имеющий вход 5.m, соединен с соответствующим одним (4.m) из M выходов первого блока 3, причем m принимает значение от 1 до M. Каждый анализирующий фильтр 6. m имеет два выхода 7.ma и 7.mb. Каждый анализирующий фильтр (6.m) предназначен для выполнения двух различных фильтраций сигнала Um, поступающего на его вход (5.m), и для подачи каждого из двух различных отфильтрованных вариантов этого сигнала на соответствующий один из двух выходов (7.ma и 7.mb).

Выполнение и функционирование анализирующих фильтров пояснены позже со ссылками на фиг. 3, 4 и 10. Каждый один из 2M выходов фильтров 7.1a, 7.1b, 7.2a, 7.2b,..., 7.ma, 7.mb... 7Ma, 7Mb подсоединяется к соответствующему одному из 2M входов 8.1, 8.2,..., 8M, 8M+1, ... 8.2M блока обработки сигналов 9.

Блок обработки 9 имеет М выходов 10.1-10.М.

Блок обработки 9 предназначен для подачи различных выходных сигналов на каждый из его М выходов, выходной сигнал является комбинацией некоторого числа входных сигналов, поступающих на его 2M входов.

Конструкция и функционирование блока обработки сигналов 9 пояснены ниже со ссылками на фиг. 7 и 8. Если выходы 10.1- 10.М идентичны М выходам блока фильтров, то это значит, что блок обработки сигналов 9 выдает М сигналов поддиапазонов S1-Sm, каждый сигнал поддиапазона Sm присутствует на соответствующем одном (10 m) из М выходов блока обработки 9.

Входной сигнал IN, подаваемый на вход 1 и имеющий частоту дискретизации Fs, занимает ширину диапазона, равную Fs/2. Деление диапазона сигнала на М означает, что ширина поддиапазонов от B1 до Вm равна Fs/2 M (см.фиг.10c).

Сигналы М поддиапазонов при необходимости могут быть обработаны в дополнительном квантователе (не показан), в котором может применяться (адаптивное) квантование сигналов, для уменьшения скорости передачи битов.

Описанная выше обработка сигнала выполняется на стороне передатчика системы цифровой передачи.

Сигналы, сформированные в передатчике, подаются через передающую среду 11 в приемник. Это может потребовать последующего канального кодирования сигнала, чтобы обеспечить возможность корректировки ошибок на стороне приемника. Передача через передающую среду 11 может осуществляться в форме беспроводной передачи, по каналу радиосвязи. Однако использование другой среды также возможно, например оптической передачи через оптико-волоконные каналы связи или оптические диски, или передачи через носители магнитной записи.

Информация, присутствующая в М поддиапазонах, может быть передана параллельно через передающую среду, как это рассмотрено на фиг. 1, либо может быть передана последовательно. В этом случае необходимы средства временного сжатия на стороне передатчика для преобразования потока параллельных данных в поток последовательных данных, а также соответствующие средства временного расширения на стороне приемника для повторного преобразования потока данных в поток параллельных данных, так что сигналы М поддиапазонов S1-Sm могут подаваться на соответствующие из М входов 12.1-12.М второго блока обработки 13, который имеет 2M выходов 14.1-14.2M. Второй блок обработки 13 предназначен для генерации выходного сигнала на каждом из его 2M выходов, выходной сигнал является комбинацией определенного числа входных сигналов, подаваемых на его М входы.

Выполнение и функционирование второго блока обработки 13 сигналов поясняются ниже со ссылками на фиг. 7 и 9. Пары выходов, например 14.1 и 14.2, второго блока обработки подсоединяются к парам входов, например 15.1a и 15.1b, соответствующего из М синтезирующих фильтров 16.1-16.М. Каждый синтезирующий фильтр 16.m имеет один выход 17m. Синтезирующие фильтры используются для обеспечения разной фильтрации двух сигналов, поступающих: на их два входа и для подачи комбинации двух отфильтрованных сигналов на их выход.

Выполнение и функционирование синтезирующего фильтра рассмотрены ниже со ссылками на фиг. 5, 6 и 10. Выход 17.m каждого синтезирующего фильтра 16.m подсоединяется к соответствующему одному (18.m) из М входов 18.1-18.M второго блока 19. Выход 20 второго блока подсоединяется к выходу 21 системы цифровой передачи. Функционирование второго блока 19 поясняется ниже со ссылками на фиг. 2.

Приемник в системе цифровой передачи включает в себя по меньшей мере элементы 13, 16.1-16.М и 19.

Если сигналы поддиапазонов квантованы на стороне передатчика, то необходим соответствующий деквантователь в приемнике. Такой деквантователь должен быть включен перед вторым блоком обработки 13 сигналов. Обработка сигналов на стороне приемника должна быть такой, чтобы сигналы U1-Um присутствовали на выходах синтезирующих фильтров 16.1-16.М и чтобы восстановленный сигнал OUT присутствовал на выходе 21 в том виде, который в идеальном случае соответствует входному сигналу IN, подаваемому на вход 1.

Фиг. 2 поясняет функционирование первого и второго блоков 3 и 19 соответственно. Сигнал IN, поступающий на вход 1, изображен схематически на фиг. 2 (а) как функция времени.

На фиг. 2a изображены выборки, из которых строится входной сигнал IN, причем показаны только местоположения выборок во времени, но не амплитуда выборок. Выборки расположены с временным интервалом T1, который равен 1/Fs. Таким образом, частота выборок входного сигнала равна Fs. В примере на фиг. 2 предполагается, что М равно 8. Сигналы, приведенные на фиг. 2b-2i представляют сигналы U8-U1, присутствующие на выходах 4.1-4.8 соответственно блока 3. Блок 3 в действительности работает как коммутатор, распределяя восемь выборок, заключенных в виртуально последовательных блоках, циклически между восемью выходами (см. также коммутатор 3 на фиг. 8).

Из фиг. 2 ясно, что выходные сигналы, имеющиеся на М выходах блока 3, имеют частоту дискретизации Fs/M. Выборки выходных сигналов при этом имеют интервал Т, который равен M.T1.

Восстановление выходного сигнала OUT во втором блоке 19 будет объяснено ниже. Блок 19 также может рассматриваться как коммутатор, циклически связывающий каждый из М входов 18.1-18.8 с выходом 20. В этом случае выборки появляются друг за другом на входах 18.1-18.М по очереди и подаются коммутатором 19 на выход 20. Более ясно это показано на фиг. 9.

Первый блок может выполняться различным образом, а именно, с использованием линии задержки, имеющей ответвление в необходимых местах вдоль указанной линии задержки. Затем эти ответвления подсоединяются ко входам прореживателей, в результате чего частота дискретизации снижается до необходимой величины.

Можно также объединить первый блок 3 с анализирующими фильтрами, особенно при использовании линий задержки в первом блоке 3, в качестве части линий задержки в анализирующих фильтрах, что хорошо известно.

Рассмотренное выше действительно для второго блока 19. В этом случае необходимы интерполяторы, чтобы обеспечить повышение частоты дискретизации.

На фиг. 3 приведен первый вариант анализирующего фильтра 6.m. Вход 30 анализирующего фильтра, который соответствует входу 5.m на фиг. 1, подсоединяется к последовательному ряду 31 элементов задержки, имеющих одинаковые задержки T. Выходы нечетных элементов задержки 32.1, 32.3. 32.n подсоединены ко входам первого блока суммирования сигналов 33. Выходы четных секций задержки 32.2, 32.4... подсоединяются ко входам второго блока объединения сигналов 34. Выходы первого и второго блоков объединения сигналов 33 и 34 образуют первый и второй выходы 35.1 и 35.2 соответственно анализирующего фильтра 6.m. Они соответствуют выходам 7.mb и 7.ma на фиг. 1. Вход 30 фильтра 6. m подсоединяется ко входу второго блока объединения сигналов 34 через умножитель 36.1, который умножает сигналы (выборки), поступающие на его вход, на коэффициент a0m.

Выходы нечетных элементов задержки подсоединяются ко входам блока объединения сигналов 33 через умножители 36.2, 36.4., 36.n-1 и 36.n+1. Они умножают сигналы (выборки), поступающие на их соответствующие входы на соответствующие коэффициенты a1m, a3m, anm. Выходы четных элементов задержки подсоединяются по входам блока объединения сигналов 34 через умножители 36.3, 36.5, . .. 36.n. Они умножают сигналы (выборки), поступающие на их входы, на соответствующие коэффициенты a2m, a4m ... . В более общем определении блоков объединения сигналов эти умножители могут рассматриваться как включенные в блоки объединения сигналов. В этом случае блоки объединения сигналов не только выполняют суммирование сигналов, поступающих на их входы, но и обеспечивают весовые комбинации (суммирование) этих сигналов. Очевидно, что в случае, если умножитель имеет коэффициент a1m, который равен нулю, то исключается связь от элемента задержки до блока объединения сигналов, включающая указанный умножитель. Также очевидно, что в случае, когда указанный умножитель имеет коэффициент a1m, равный единице, то исключается умножитель, так что связь осуществляется напрямую.

На фиг. 4 показан другой вариант анализирующего фильтра 6.m. Несмотря на то, что выполнение фильтра по фиг. 4 отличается от выполнения фильтра по фиг. 3, он может выполнять одинаковые функции и осуществлять одинаковую фильтрацию при удовлетворении некоторых условий. Фильтр по фиг. 4 содержит два последовательных ряда 40 и 41 элементов задержки, имеющих одинаковую величину задержки 2T. Вход 30 фильтра соединен с входами элементов задержки в последовательном ряду 40 через умножители 42.1-42.p-1 соответственно и с выходом 35.2 фильтра через умножитель 42.p. Это значит, что последовательный ряд 40 включает в себя P-1 элементов задержки 44.1-44.p-1. Вход 30 фильтра, кроме того, подсоединен с входами элементов задержки в последовательном ряду 41 через умножитель 43.1-43.q-1 и с выходом 35.1 фильтра через умножитель 43q. Это значит, что последовательный ряд 41 включает q-1 элементов задержки 45.1-45q-1. Умножители 42.1-42. p умножают полученные входные сигналы на коэффициенты b1m, b2m,..., bpm соответственно. Умножители 43.1-43q умножают свои входные сигналы на коэффициенты C1m,..., Cqm, соответственно. Блоки объединения сигналов 46.1-46. р-1 соединены с выходами элементов задержки 44.1-44. p-1 последовательного ряда 40. Блоки объединения сигналов 47.1-47. q-1 соединены с выходами элементов задержки 45.1-45q-1 последовательного ряда 41. Выход блока объединения сигналов 47.q-1 соединен с выходом фильтра 35.1 через дополнительный элемент задержки 48, имеющий величину задержки T, которая равна половине величины задержки элементов в последовательных рядах. Элемент задержки 48 может быть предусмотрен в любом месте в тракте сигнала от входа 30 к выходу 35.1, при условии, что он не включен в тракт сигнала от входа 30 к выходу 35.2.

То, что было отмечено для фиг. 3, в случаях, когда умножитель имеет коэффициент единицу или ноль, сохраняет силу и в данном случае. Если b2m равен нулю, то это также означает исключение соответствующего блока объединения сигналов 46.1, который в противном случае соединяется с выходом соответствующего умножителя 42.2. Это значит, что элемент задержки 44.1 непосредственно соединен с элементом задержки 44.2, или они могут быть преобразованы в элемент задержки, имеющий задержку 4T.

При определенных условиях фильтр по фиг. 4 работает аналогичным образом и обеспечивает аналогичную фильтрацию входного сигнала, как и фильтр по фиг. 3.

Соответствующие условия имеют вид

p=q=(n+1)/2, bpm=a0m, cqm=a1m, bp-1.m=a2m,

Cq-1.m=a3m,..., b1m=an-1.m, и c1m=anm.

В этом случае предполагается, что n - нечетное число. Однако, если n - четное число, то число связей с блоком объединения 34 сигналов по фиг.3 на единицу больше, чем число соединений с блоком объединения 33 сигналов. В этом случае условия следующие:

q=p-1-n/2, bpm=a0m, cqm=a1m, bq-1.m=a2m

cq-1.m=a3m,..., b1m=anm и c1m=an-1.m

Соединение, включающее умножитель 36.n+1 в фильтре на фиг. 3, где n является четным числом, является соединением от выхода последовательного ряда 31 к блоку объединения 34.

На фиг. 5 изображен синтезирующий фильтр 16.m, имеющий два входа 50.1 и 50.2 и один выход 51. Входы соответствуют входам 15.ma и 15.mb, а выход соответствует выходу 17.m на фиг. 1.

Синтезирующий фильтр содержит два последовательных ряда 52 и 53 элементов задержки, имеющих величину задержки, равную 2T. Фильтр 16.m включает также блок объединения 54 сигналов и дополнительный элемент задержки 55, имеющий величину T задержки, равную половине задержки элементов задержки в последовательных рядах. Входы 50.1 и 50.2 подсоединены ко входам блока объединения 54 сигналов через умножители 56.1 и 57.1 соответственно. Последовательный ряд 52 включает p-1 элементов задержки 58.1-58.p-1. Выходы секций задержки соединены с соответствующими входами блока объединения 54 через соответствующие умножители 56.2-56. p. Умножители 56.1-56.p умножают свои входные сигналы на коэффициенты d1m-dpm соответственно.

Последовательный ряд 53 включает в себя q-1 элементов задержки, 59.1-59. q-1. Выходы этих элементов задержки соединены с соответствующими входами блока объединения 54 через соответствующие умножители 57.2-57.q. Умножители 57.1-57. q умножают свои входные сигналы на коэффициент l1m-lqm соответственно. Выход 60 блока объединения 54 соединен с выходом фильтра 51. Элемент задержки 55 включен между входом 50.2 и входом последовательного ряда 53. В более общем случае элемент задержки 55 может быть включен в любом месте в тракте сигнала от входа 50.2 к выходу 51, при условии, что он не включен в тракт сигнала от входа 50.1 к выходу 51.

Для фильтра 16. m, чтобы обеспечить правильную фильтрацию на стороне приемника двух сигналов, поступающих на входы 50.1 и 50.2, если m-ый фильтр на стороне передатчика является фильтром 6.m по фиг. 3, должны удовлетворяться следующие условия:

p=q=(n+1)/2, d1m=a0m; l1m=a1m, d2m=a2m

l2m=a3m,..., dpm=an-1.m и lqm=anm

Вновь предполагается, что n - нечетное число. Аналогично приведенному выше можно определить, что для n, являющегося четным числом, должны выполняться следующие условия:

q=p-1=n/2, d1m=a0m; l1m=a1m, d2m=a2m

l2m=a3m,..., lqm=an-1.m и dpm=an.m.

На фиг. 6 изображен другой вариант синтезирующего фильтра 16.m, обозначенного 16.m'. Фильтр содержит последовательный ряд 65 элементов задержки 66.1-66. n, имеющих одинаковую величину задержки T. Вход 50.1 соединяется со входами четных элементов задержки через умножители 67.2, 67.4,., 67.n+1. В данном случае n считается нечетным числом. Вход 50.2 соединен с входами нечетных элементов задержки через умножители 67.1, 67.3,., 67.n. Чтобы фильтр 16.m' выполнял правильную фильтрацию на стороне приемника сигналов, поступающих на входы 50.1-50.2, если m-ый фильтр на стороне передатчика является фильтром 6. m по фиг. 3, коэффициенты, на которые умножители 67.1-67.n+1 производят умножение входных сигналов, должны соответствовать фиг. 6. Эти коэффициенты, таким образом, равны anm, an-1.m,..., a2m, a1m, anm соответственно.

Выбор коэффициента a0m-anm для фильтра 6.m на фиг. 3 будет объяснен со ссылками на фиг. 10.

На фиг. 10(c) изображена полоса пропускания фильтра цифрового сигнала, ширина которой составляет Fs/2 Гц. Суммарная полоса пропускания фильтра разделена на М поддиапазонов B1-ВM одинаковой ширины Fs/2M. На фиг. 10(a) изображен идеальный или стандартный низкочастотный фильтр, имеющий характеристику H(f) и ширину полосы пропускания FB, равную половине ширины поддиапазона. На фиг. 10(b) изображена импульсная характеристика низкочастотного фильтра H(f) как функция времени. Эта импульсная характеристика имеет вид последовательности импульсов с одинаковыми интервалами между ними, равными T1=1/Fs. Импульсная характеристика определяется рядом значений h0, h1, h2,.. ., включающих амплитуду импульсов на временных интервалах t=0, TI, 2TI.

На фиг. 10(d)-(q) показано, как коэффициенты умножения умножителей в фильтрах 6.1-6. M могут быть получены с использованием импульсной характеристики стандартного низкочастотного фильтра H(f). Можно видеть, что коэффициенты a01-a0m, являющиеся коэффициентами умножения умножителей 36.1 в фильтрах 6.I-6M (фиг. 3), равны h0-hm-1 соответственно. Коэффициенты a11-a1m, являющиеся коэффициентами умножения для умножителей 36.2 в фильтрах 6.I-6.М (фиг. 3), равны hm-h2m-1 соответственно, коэффициенты a21-a2m равны от - h2m до - h3m-1 соответственно, коэффициенты a31-a3m равны от - h3m до - h4m-1 соответственно и так далее (фиг. 10d).

Предпочтительно, чтобы стандартный фильтр H(q) имел нечетное число импульсов. Это значит, что фильтр имеет нечетное число коэффициентов h0, h1, h2, что будет пояснено ниже.

На фиг. 7 изображен вариант осуществления блока обработки 9. Блок обработки 9 включает в себя X блоков объединения сигналов 70.I-70.X. Y входов 71.I-71.Y блока сигналов 9 соединены через соответствующие умножители 72.II-72.1Y с соответствующими входами блока объединения 70.I. Y входов блока обработки также соединены с входами блока объединения сигналов 70.2 через соответствующие умножители 72.21-72.2Y. Это справедливо для всех других блоков объединения сигналов 70.x, где x принимает значение от 1 до X включительно. Это означает, что y-тый вход 71.y соединен с соответствующим входом x-го блока объединения сигналов 70.x через соответствующий умножитель 72. xy, где y принимает значение 1 до Y. Ясно, что Y=2M, a X=М. Входы 71.1-71.2M соответствуют в этом порядке входам 8.1-8.2M на фиг. 1. Выходы 74.1-74.М в этом порядке соответствуют выходам 10.1-10.М на фиг.1. Умножители 71.II-72. IY. 72.2I-72.2Y, 72.3I-72.3Y,., 72.XI-72.XY производят умножение их входных сигналов на коэффициенты а11-a1y, a21-a2y, a31-a3y.., ax1-axy соответственно. Коэффициенты axy могут быть вычислены, с использованием следующей формулы:

при ϕ = (-I)x-1π(X-1/2) {1/2-(y-1)/DIV 2/М}

Выше предполагалось, что импульсная характеристика H(f) стандартного фильтра на фиг. 10b имеет нечетное число импульсов и, таким образом, нечетное число коэффициентов.

Фиг. 7 также будет использоваться для объяснения выполнения и функционирования второго блока обработки 13 на стороне приемника.

В этом случае Y=M, а X=2M. Входы 71.1-71.М в этом порядке соответствуют входам 12.1-12. М на фиг. 1, а выходы 74.1-74.2M соответствуют выходам 14.1-14.2M на фиг. 1. Коэффициенты axy для блока обработки 13 могут быть вычислены с использованием следующей формулы:

при ψ = (-1)y-1π(y-1/2) {1/2-(X-1)DIV 2/M}

для нечетного числа коэффициентов в импульсной характеристике (Н f) на фиг. 10b.

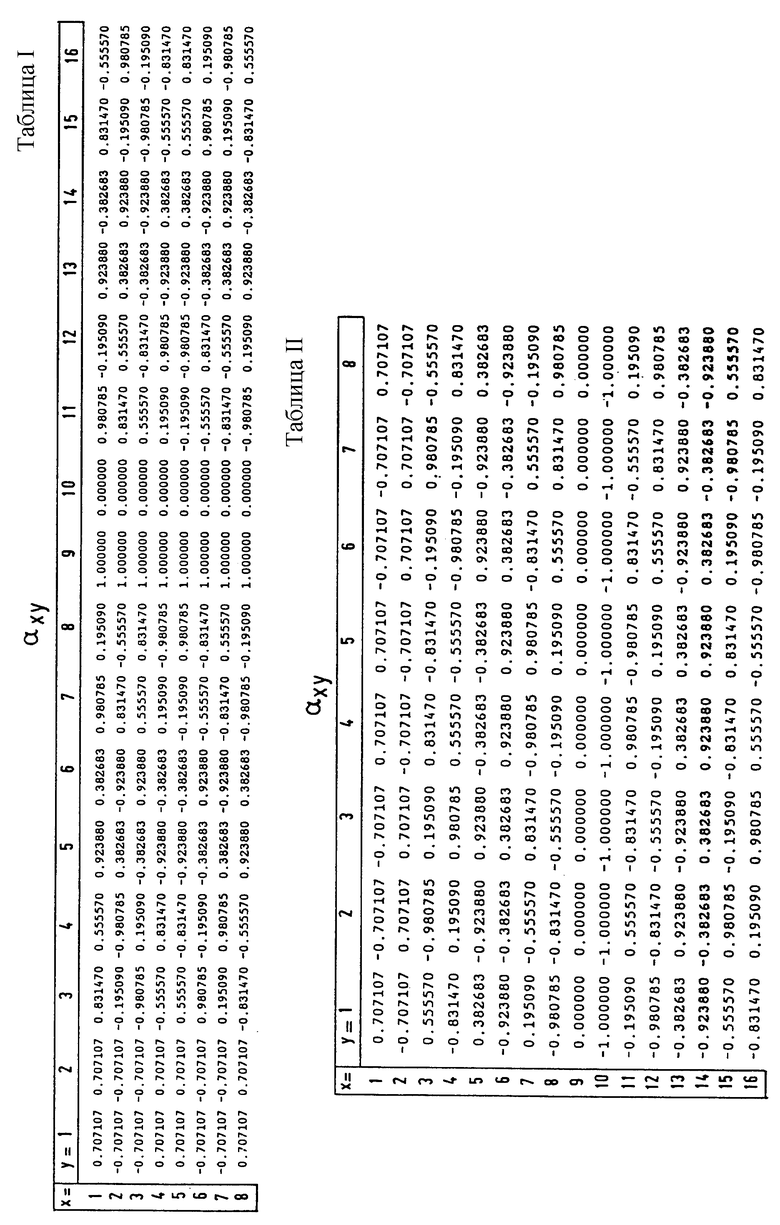

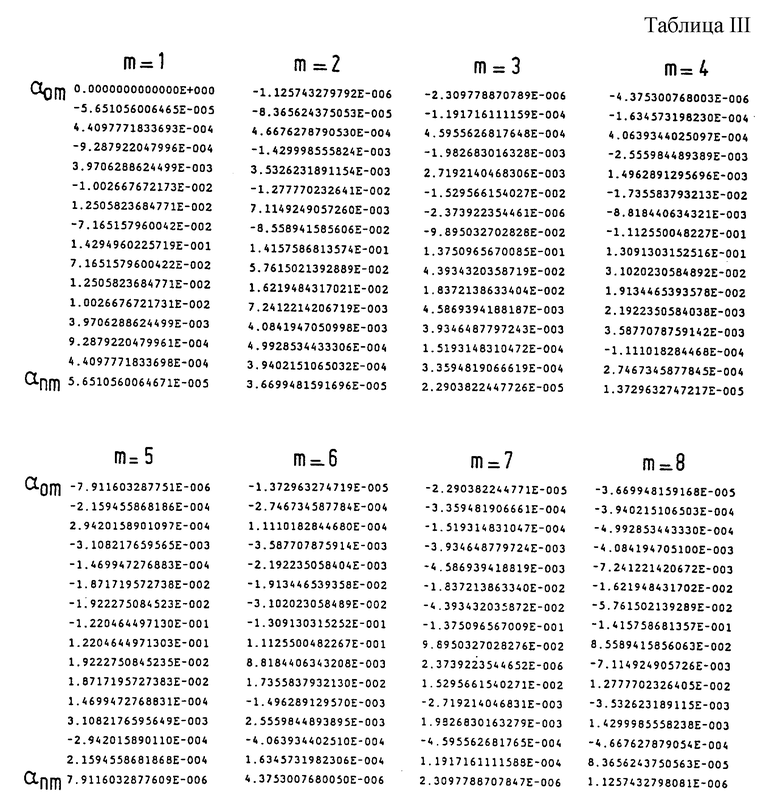

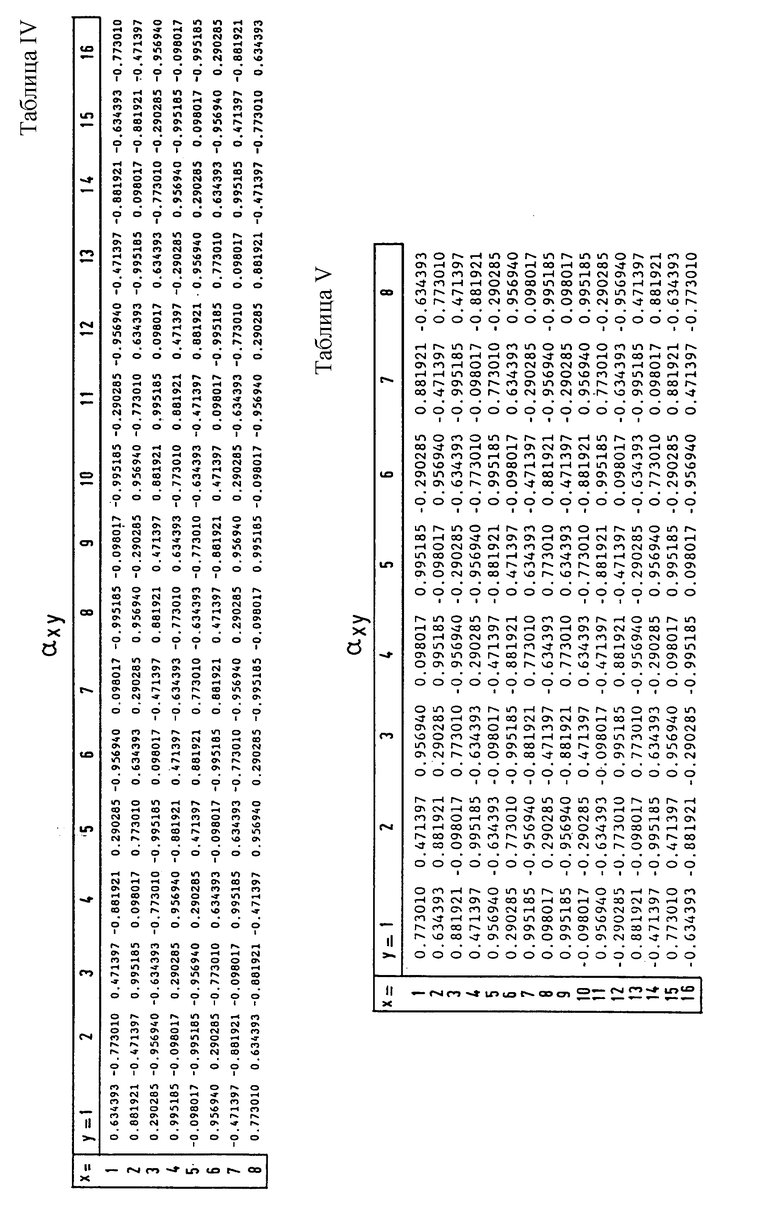

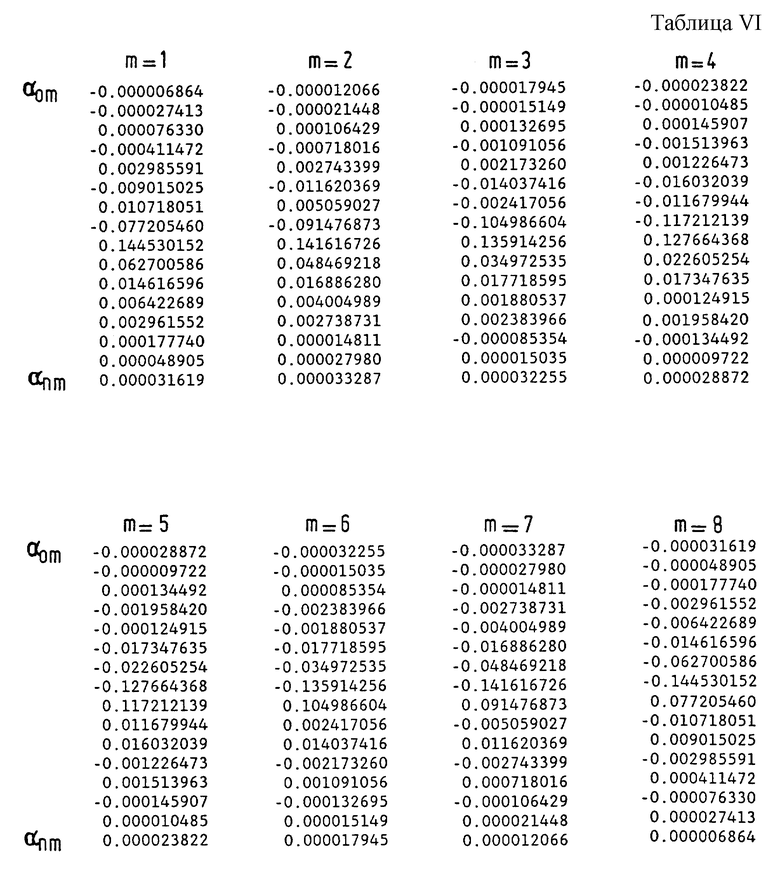

Используя эти коэффициенты axy в блоках обработки сигналов на стороне передатчика и приемника, можно реализовать систему цифровой передачи, которая практически полностью исключает какие-либо искажения. Это фактически также требует выполнения определенных условий, налагаемых на частотную передаточную функцию стандартного фильтра. Предпочтительно, чтобы полоса пропускания указанного фильтра не превышала Fs/4M. Числовой пример приведен в таблице I для коэффициентов для блока обработки 9, а в таблице II - для коэффициентов для второго блока обработки 13, где М принимается равным 8, в предположении, что импульсная характеристика H(f) на фиг. 10b имеет нечетное число коэффициентов. Таблица III содержит соответствующие коэффициенты фильтра для восьми анализирующих фильтров 6.m. Коэффициенты для соответствующих синтезирующих фильтров 16.m могут быть получены из коэффициентов в таблице III, как пояснено со ссылками на фиг. 5 и 6. В следующих таблицах IV и V приведены коэффициенты axy для блока обработки 9 и второго блока обработки 13, а в таблице VI приведены коэффициенты для восьми анализирующих фильтров 6.m в том случае, когда импульсная характеристика стандартного фильтра H(f) включает в себя четное число коэффициентов. Из таблиц I и II, для случая, когда стандартный фильтр имеет нечетное число коэффициентов, ясно, что для блоков обработки имеет место значительная симметрия в коэффициентах. Большое число коэффициентов в одной таблице равны друг другу, либо отличаются только своим знаком. Это обстоятельство позволяет значительно уменьшить количество операций умножения. Противоположный случай наблюдается в таблицах IV и V, для случая, когда стандартный фильтр имеет четное число коэффициентов. Здесь коэффициенты значительно отличаются друг от друга.

Как уже объяснено, таблица III включает в себя коэффициенты фильтра, полученные из стандартного фильтра, имеющего нечетное число импульсов в импульсной характеристике. Это фильтр, который генерирует 127 импульсов на один входной импульс, и включает 127 коэффициентов фильтра. Однако таблица содержит 128 коэффициентов. Это получено путем добавления одного нуля в качестве первого коэффициента h0 (значение для a01 в таблице III).

Таблица VI получена из стандартного фильтра, имеющего четное число (128) коэффициентов. В обоих случаях импульсная характеристика стандартного фильтра является симметричной. Это значит, что два коэффициента, расположенных симметрично относительно середины, равны, за исключением их знаков. Эта середина для случая нечетного числа коэффициентов, соответствует по времени местоположению импульса h64. Это значит, что h1(=a0.2) равен h127(=a16.8), h2(= а0.3) равен h126(=a16.7), h3(=а0.4) равен h125(=a16.6), h4(=a0.5) равен h124(= a16.5), h5(= a0.6) равен h123(=a16.4), h6(=a0.7) равен h122(=a16.3), h7(= a0.8) равен h121(=a16.2), h8(=a1.1) равен h120(=a16.1), h9(=a1.2) равен h119(=a15.8) и так далее.

Все коэффициенты равны за исключением их знаков. Коэффициент h64, соответствующий a8.1, имеет отдельное значение (см. таблицу III). Середина для случая четного числа коэффициентов находится точно между коэффициентами h63 и h64.

Это значит, что h0(= a0.1) равен h127(=a16.8), h1(=a0.2) равен h126(= a16.7), h2(= a0.3) равен h125(=a16.6), h3(=а0.4) равен h124(=a16.5), h4(= a0.5) равен h123(= a16.4), h5(=a0.6) равен h122(=a16.3), h6(=а0.7) равен h121(= a16.2), h7(=a0.8) равен h120(=a16.1), h8(=a1.1) равен h119(=a15.8), и так далее до h63(=а7.8), равного h64(=a8.1)

Все равны за исключением их знаков.

Если имеет место различие больше, чем на единицу, как объяснено выше для стандартного фильтра с нечетным числом коэффициентов, между числом коэффициентов в стандартном фильтре и числом коэффициентов а, необходимых для анализирующих (синтезирующих) фильтров, то должны быть добавлены нули симметрично, начиная с внешней стороны и сходящиеся внутрь. Так предположим, что стандартный фильтр имеет 126 коэффициентов, то a0.1, а также a16.8 равны нулю.

На фиг. 8 изображен вариант передатчика, который делит входной сигнал на восемь сигналов поддиапазонов. Выходы 7.1a и 7.1б анализирующего фильтра 6.1 подсоединяются по входам соответствующих усилителей 80.1 и 81.1 соответственно. Усилители 80.1 и 81.1 усиливают свои входные сигналы на комплексный коэффициент KI, который является одинаковым для обоих усилителей 80.1 81.1, выходы которых подсоединяются ко входам 85.1 и 85.9 соответственно блока обработки 82. Выходы 72a и 72b фильтра 6.2 подсоединяются по входам соответствующих усилителей 80.2 и 81.2 соответственно. Оба усилителя усиливают их входные сигналы на комплексный коэффициент K2. Выходы этих усилителей подсоединяются ко входам 85.2 и 85.10 блока обработки 82. Таким образом все другие выходы фильтров подсоединяются через соответствующие усилители 80.3, 81.3, 80.8, 81.8 по входам 85.3, 85.11, 85.4, 85.12,..., 85,8, 85,16 блока обработки 82. Усилители, подсоединенные к выходам того же фильтра 6.m, умножают свои входные сигналы на комплексную величину Km. Комплексные величины Km определяются следующей формулой:

Km= exp[j(m-1)π/2M]

Блок обработки 82 выполняет 2M(=16) точечное обратное быстрое преобразование Фурье (БПФ) для шестнадцати входных сигналов, поступающих на входы 85.1-85.16. Блок 16-точечного обратного БПФ имеет шестнадцать выходов. Использоваться будут только первые М(=8) выходов. Эти выходы в основном связаны с низкочастотными выходами блока 82. Каждый из этих выходов 86.1-86.8 подсоединяется через соответствующий усилитель 83.1-83.3 соответственно и блок определения действительной величины 84.1-84.8 соответственно к выводам 10.1-10.8 соответственно, которые связаны с передающей средой II. Усилители 83.1-83.8 усиливают их входные сигналы на комплексную величину V1-V8 соответственно. Комплексные величины определяются следующей формулой:

Vm= expjβm

где βm должно быть выбрано правильно и так, чтобы режим работы схемы внутри блока, обозначенного 9', был эквивалентен режиму работы схемы, описанной со ссылками на фиг. 8 и таблицу I или таблицу IV. Преимуществом блока обработки, изображенного на фиг. 8, является то, что он может обеспечить работу, как это объяснено со ссылками на фиг. 7 для четных и нечетных коэффициентов H(f). В этом случае необходимо только иначе выбрать величины βm. В общем, комплексные величины отличаются друг от друга для различных величин m.

На фиг. 9 показан вариант приемника, который может взаимодействовать с передатчиком, изображенным на фиг. 8. Вводы 12.1-12.8 подсоединяются к первым М(=8) входам 92.1-92.8 соответственно блока обработки 91 через соответствующие усилители 90.1-90.8 соответственно. Эти усилители производят усиление своих входных сигналов с коэффициентом V'1-V'8 соответственно. Блок обработки 91 выполняет 2M(=16)-точечное БПФ. Такие блоки имеют 16 входов. Это значит, что на вторые М(=9) входов 92.9-92.16 блока обработки 91 будут подаваться величины, равные нулю. Пары выходов 93.1 и 93.9, 93.2 и 93.10,... 93.8 и 93.16 подсоединяются к двум входам соответствующих фильтров 16.1, 16.2, ..., 16.8 через соответствующие усилители 94.1 и 95.1 соответственно, 94.2 и 95.2 соответственно,..., 94.8 и 95.8 соответственно. Усилители 94.m и 95.m производят усиление своих входных сигналов на комплексные величины K'm.

Комплексные величины K'm определяются следующей формулой:

Km'=exp[-j(m-1)/2M]

Комплексные величины Vm' определяются следующей формулой:

где  должно быть выбрано правильно и так, чтобы режим работы схемы внутри блока 18', показанного пунктиром, был эквивалентен режиму работу схемы, описанной со ссылками на фиг. 7 и таблицу II или V, преимуществом другого блока обработки, изображенного на фиг. 9, является то, что он может обеспечивать функционирование, описанное со ссылками на фиг. 7, для четного и нечетного числа коэффициентов для H(f). В этом случае необходимо только иначе выбрать значение

должно быть выбрано правильно и так, чтобы режим работы схемы внутри блока 18', показанного пунктиром, был эквивалентен режиму работу схемы, описанной со ссылками на фиг. 7 и таблицу II или V, преимуществом другого блока обработки, изображенного на фиг. 9, является то, что он может обеспечивать функционирование, описанное со ссылками на фиг. 7, для четного и нечетного числа коэффициентов для H(f). В этом случае необходимо только иначе выбрать значение

На фиг. 11 показан другой вариант блока обработки сигналов 9, изображенного на фиг. 1, имеющего обозначение 9''. Блок обработки 9'' имеет средство переключения 100 и М блоков объединения сигналов, из которых показаны только первые два 102 и 103 соответственно. Входы 8.1-8.2M блока обработки 9'' подсоединены к 2M входам средства переключения 100. Это средство 100 имеет один выход 101, который связан со входами всех блоков объединения сигналов. На чертеже показаны соединения только с входами 104 и 105 блоков объединения 102 и 103. Выходы М блоков обработки являются выходами 10.1-10.М блока обработки 9''. Каждый блок объединения имеет умножитель 106, запоминающее устройство 107, имеющее 2M ячеек памяти, сумматор 108 и накопительный генератор 109.

Средство переключения 100 предназначено для подготовки каждый раз блоков из 2M выборок, которые более или менее одновременно присутствуют на 2M входах от 8.1 до 8.2M, каждая выборка на одном входе, в последовательном виде поступающих на выход 101. Содержимое запоминающего устройства 107 в блоке объединения 102 и 103 приведена на фиг. 11. Коэффициенты умножения a1.2-a1.2M и a2.1-a2.2M, имеющего место в указанных запоминающих устройствах, равны соответствующим коэффициентам в блоке обработки 9 на фиг. 7. Блоки обработки 9 и 9'' должны естественно выполнять одинаковую обработку сигналов, поступающих на их входы. Запоминающее устройство 107 управляется таким образом, чтобы оно выдавало коэффициент α1,1 на вход 111 умножителя 106, когда средство переключения 100 подключает на вход 112 устройства 106 выборку, присутствующую на входе 8.1. В этот момент содержание регистра 109 равно нулю, так что после умножения результат запоминается в регистре 109. На вход 112 подается выборка, присутствующая на входе 82, а на вход 111 поступает от запоминающего устройства 107 коэффициент a1.2 и они перемножаются друг с другом.

С помощью сумматора 108 результат умножения, поступающий на вход 113 сумматора 108, прибавляется к содержанию регистра 109, которое подается на вход 114 сумматора 108 и запоминается в регистре 109.

Такая обработка продолжается в течение периода умножения на все 2M коэффициентов, находящихся в запоминающем устройстве 107. Более того, эта обработка выполняется параллельно в других блоках комбинации, таких как 103.

После 2M-ного умножения результат прибавляется к содержанию регистра. Затем это содержание подается на выход 10.1 посредством запоминания его в дополнительном буферном запоминающем устройстве 110. Затем содержание регистра 109 обнуляется и может начинаться следующий цикл 2M-ного умножения. Очевидно, что другой блок обработки 12 может быть выполнен так же. Такой блок обработки содержит 2M блоков объединения сигналов, аналогично блоку 102 по фиг. 11, с той лишь разницей, что запоминающее устройство 107 теперь содержит М коэффициентов a1.1-a1.M, или a2.1-a2M для запоминающего устройства 107 в блоке 103.

Средство переключения 100 имеет М входов 12.1- 12.М и формирует каждый раз выборки в последовательные блоки из М выборок, имеющихся более или менее в одинаковый момент на М входах 12.1-12.М, по одной выборке на каждом входе, последовательно поступающие на выход 101. После M-ного умножения регистр обнуляется.

На фиг. 12 и 13 изображена передача посредством носителей магнитной записи. На фиг. 12 изображено устройство записи цифрового сигнала, которое включает в себя передатчик, изображенный на фиг. 1. Это устройство включает блок записи 120, имеющий М входов от 121.1 до 121.М., каждый из которых соединен с соответствующим одним из М выходов блока обработки сигналов 9. Устройство предназначено для записи цифрового звукового сигнала, поступающего на вход 1, на носителе 122 магнитной записи с помощью одной магнитной записывающей головки 123.

Блок записи 120 может быть типа RDAT, который использует для записи сигналов S1-Sm спиральный принцип записи на дорожках, лежащих друг за другом на носителе в форме магнитной ленты. В этом случае для блока записи 120 необходимо разработать средства для реализации параллельно-последовательного преобразования сигнала, подаваемого на входы 121.1-121.М.

Блок записи 120 одинаково хорошо может быть типа SDAT, в котором сигналы S1-Sm, подлежащие записи, делятся на определенное число дорожек, не обязательно равное М, лежащих параллельно по длине носителя записи. Также и в этом случае может быть необходимо обеспечивать параллельно-последовательное преобразование сигналов, если число дорожек меньше М.

На фиг. 13 изображено цифровое устройство воспроизведения, которое содержит приемник, показанный на фиг. 1. Устройство включает в себя блок воспроизведения 124, имеющий М выходов 125.1-125. М, каждый из которых подсоединяется к одному из входов 12.1-12.М другого блока обработки сигналов 13.

Устройство предназначено для воспроизведения цифрового сигнала, поскольку он записан на записывающем носителе 122 с помощью устройства на фиг. 12. Поэтому блок воспроизведения 124 содержит по меньшей мере одну считывающую головку 126, и может быть, например, типа RDAT или типа SDAT.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПЕРЕДАЮЩАЯ СИСТЕМА НА ПРИНЦИПАХ РАЗЛИЧНОГО КОДИРОВАНИЯ | 1994 |

|

RU2144261C1 |

| УЛУЧШЕННОЕ РАСШИРЕНИЕ ДИАПАЗОНА ЧАСТОТ В ДЕКОДЕРЕ ЗВУКОВОГО СИГНАЛА | 2015 |

|

RU2682923C2 |

| ОПТИМИЗИРОВАННЫЙ МАСШТАБНЫЙ КОЭФФИЦИЕНТ ДЛЯ РАСШИРЕНИЯ ДИАПАЗОНА ЧАСТОТ В ДЕКОДЕРЕ СИГНАЛОВ ЗВУКОВОЙ ЧАСТОТЫ | 2014 |

|

RU2668058C2 |

| СПОСОБ ОБНОВЛЕНИЯ КОДЕРА ПОСРЕДСТВОМ ИНТЕРПОЛЯЦИИ ФИЛЬТРА | 2009 |

|

RU2530327C2 |

| КОДИРОВАНИЕ ИЛИ ДЕКОДИРОВАНИЕ АУДИОСИГНАЛА | 2004 |

|

RU2374703C2 |

| Томографическое вычислительное устройство | 1980 |

|

SU950204A3 |

| Устройство для оценки контура изображения | 1981 |

|

SU1076002A3 |

| УЛУЧШЕННОЕ РАСШИРЕНИЕ ДИАПАЗОНА ЧАСТОТ В ДЕКОДЕРЕ ЗВУКОВОГО СИГНАЛА | 2015 |

|

RU2763848C2 |

| УЛУЧШЕННОЕ РАСШИРЕНИЕ ДИАПАЗОНА ЧАСТОТ В ДЕКОДЕРЕ ЗВУКОВОГО СИГНАЛА | 2015 |

|

RU2763547C2 |

| УЛУЧШЕННОЕ РАСШИРЕНИЕ ДИАПАЗОНА ЧАСТОТ В ДЕКОДЕРЕ ЗВУКОВОГО СИГНАЛА | 2015 |

|

RU2763481C2 |

Устройство относится к системе цифровой передачи, использующей поддиапазонное кодирование цифрового сигнала. Технический результат - обеспечение уменьшения искажений из-за наложения спектров в восстановленном сигнале, обеспечение эффективности обработки передаваемого и принимаемого сигналов в отношении времени, затрачиваемого на обработку сигнала. Устройство цифровой передачи содержит передатчик и приемник для передачи цифрового сигнала, в частности, звукового, имеющего заданную частоту выборки Fs. Цифровой сигнал кодируется по М поддиапазонам с уменьшением частоты выборки. Для этой цели передатчик содержит первый блок для приема цифрового сигнала, разделенного на М сигналов, имеющих частоту выборки Fs/M. Эти сигналы присутствуют на входах первого блока обработки и подаются на М анализирующих фильтров, каждый фильтр имеет один вход и два выхода. 2М выходов фильтров подсоединены к 2М входам первого блока обработки сигналов, который имеет М выходов для выдачи М сигналов поддипазонов (S1 - SM). Каждый фильтр предназначен для выполнения двух различных фильтраций сигнала, поступающего на его вход, и для выдачи двух различных отфильтрованных вариантов входного сигнала на свои два выхода. Блок обработки сигналов предназначен для выдачи выходных сигналов на каждый из М выходов, выходной сигнал, являющийся комбинацией определенного числа входных сигналов, подается на его 2М входа. На приемной стороне обработка сигналов осуществляется, в основном в обратном порядке по отношению к обработке сигналов на передающей стороне, для получения сигнала на выходе, который является почти точной копией входного сигнала. 3 с. и 14 з.п. ф-лы, 13 ил., 6 табл.

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ПЕРЕХОДА С ПОСТА НА ПОСТ ПРИ ДЕМОНСТРАЦИИ КИНОФИЛЬМОВ | 0 |

|

SU285495A1 |

| US 4569075 A, 04.02.86 | |||

| US 3781793 A, 25.12.73 | |||

| US 4811398 A, 04.03.89 | |||

| DE 3106855 A1, 10.12.81 | |||

| DE 3118950 A1, 08.04.82 | |||

| СПОСОБ И УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ИЗМЕНЕНИЯ ОБСЛУЖИВАЮЩЕЙ СОТЫ ВЫСОКОСКОРОСТНОГО СОВМЕСТНО ИСПОЛЬЗУЕМОГО КАНАЛА НИСХОДЯЩЕЙ ЛИНИИ СВЯЗИ | 2009 |

|

RU2467510C1 |

| СПОСОБ ПОЛУЧЕНИЯ КОНСЕРВОВ "КОТЛЕТЫ ДОМАШНИЕ С СОУСОМ СМЕТАННЫМ С ТОМАТОМ" | 2012 |

|

RU2481027C1 |

Авторы

Даты

2000-02-10—Публикация

1990-05-30—Подача