Предлагаемое устройство относится к области радиотехники и может найти применение в адаптивных системах радиосвязи.

Известен "Анализатор временных искажений" двоичных сигналов, описанный в книге Бухвинера B. E. "Оценка качества радиосвязи". М., Связь, 1974 г. на стр. 57, рис.2.18, в котором формируются зоны анализа на предлагаемой длине элемента симметрично его середине, а принятие решения о переданном символе производится путем проверки совпадения положения фронтов, попадающих в каждую зону анализа.

Однако данное устройство обладает узким диапазоном измерения.

Известна также "Система контроля качества сигнала" по заявке Японии N 60-5098 от 08.02.85 г., бюлл. N 7-128, в которой передаваемый сигнал кодируется псевдослучайным кодом, а на приемной стороне декодируется, при этом с помощью счетчика подсчитывается число состояний блока декодирования, отличных от фиксированного в приемном устройстве. На основании значения, подсчитанного в счетчике, оценивается качество принимаемого сигнала.

Однако данное устройство обладает низкой точностью оценки качества принимаемого сигнала.

Наиболее близким по технической сути к предлагаемому устройству является устройство по патенту РФ N 2001529 "Способ оценки качества приема двоичных сигналов и устройство для его осуществления" от 15.10.93 г., бюлл. N 37-38, принятое за прототип.

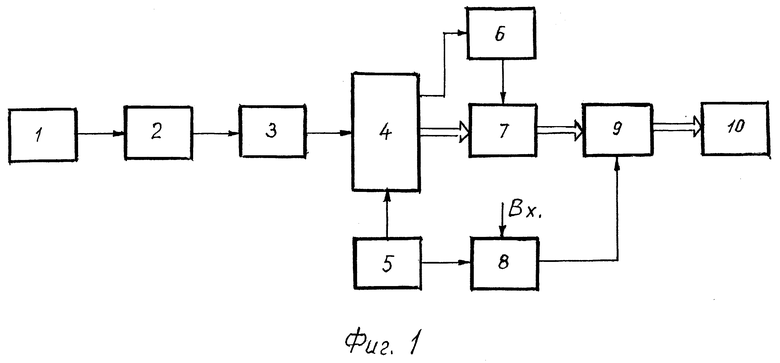

Функциональная схема прототипа представлена на фиг.1, где приняты следующие обозначения:

1 - частотный детектор (ЧД);

2 - фильтр нижних частот (ФНЧ);

3 - пороговый блок;

4 - регистр;

5 - синхронизатор;

6 - инвертор;

7 - блок сумматоров по модулю два (СМД);

8 - блок формирования импульсов разрешения считывания (ФИРС);

9 - блок элементов ИЛИ-НЕ;

10 - блок счетчиков.

Устройство-прототип содержит последовательно соединенные ЧД1, ФНЧ2, пороговый блок 3, регистр 4, блок СМД7, блок элементов ИЛИ-НЕ 9 и блок счетчиков 10, последовательно соединенные синхронизатор 5 и блок ФИРС8, выход которого подключен ко второму входу блока элементов ИЛИ-НЕ 9, и инвертор 6, при этом второй выход синхронизатора 5 соединен со вторым входом регистра 4, второй выход которого подключен ко входу инвертора 6, выход инвертора 6 соединен со вторым входом блока СМД7, а второй вход блока ФИРС8 является входом устройства.

Устройство-прототип работает следующим образом. Частотно-модулированный сигнал поступает на вход ЧД1, где преобразуется в двухполярные импульсы, которые поступают затем на вход ФНЧ2, выполняющего функцию интегратора, накапливаются в нем и поступают на вход порогового блока 3. Здесь производится сравнение с порогом и принимается решение о принятом символе. Сигнал с порогового блока 3 записывается с помощью тактовых импульсов, поступающих с синхронизатора 5, в регистр 4, при этом частота тактовых импульсов записи берется в несколько раз выше тактовой частоты принимаемой информации. С выходов регистра 4 значения отсчетов сигнала (выборок) поступают на первые входы блока СМД7, а на вторые входы блока СМД7 поступает отсчет с первого выхода регистра 4, проинвертированный инвертором 6. Таким образом в блоке СМД7 производится сравнение значений отсчетов сигнала с наилучшим. В случае несовпадения (поскольку наилучший отсчет проинвертирован) на выходе блока СМД7 появляется "1". Значения результатов с выходов блока СМД7 поступают на первые входы блока элементов ИЛИ-НЕ 9, а на вторые входы этого блока поступает сигнал разрешения считывания с блока ФИРС8, формируемый на основе импульсов с выхода синхронизатора 5 и опорной частоты, подающейся на второй вход блока ФИРС8. Сигнал разрешения считывания по временному положению находится в конце двоичного элемента и представляет собой короткий импульс, который разрешает прохождение результатов сравнения с блока СМД7 на вход блока счетчиков 10, где фиксируется. При этом блок счетчиков 10 подсчитывает побитно результаты сравнения на отрезке информационной последовательности, длительность которой определяется периодом его счета. Таким образом, результат оценки качества приема отрезка информации формируется к концу работы блока счетчиков 10. Затем блок счетчиков 10 сбрасывается в начальное состояние и цикл работы устройства-прототипа повторяется заново.

Однако устройство-прототип обладает низкой надежностью получения результатов оценки качества приема двоичных сигналов и узкими функциональными возможностями.

С целью повышения надежности получения результатов оценки качества приема двоичных сигналов и расширения функциональных возможностей в устройство, содержащее последовательно соединенные частотный детектор, интегратор, пороговый блок и первый регистр, блок сумматоров по модулю два и синхронизатор, первый выход которого соединен со входом синхронизации первого регистра, при этой вход частотного детектора является входом устройства, дополнительно введены (2..n) регистров, (1...n) блоков ключей, блок хранения эталонного сигнала и сумматор, при этом выход порогового блока подключен к информационным входам (2....n) регистров, (1....N) выходов каждого из (1...n) регистров соединены соответственно с (1..N) информационными входами соответствующих (1...n) блоков ключей, соответствующие (1...N) выходы которых объединены и подключены к соответствующим (1...N) первым входам блока сумматоров по модулю два, выход частотного детектора соединен со входом синхронизатора, первый выход которого подключен к управляющему входу первого блока ключей, (2. ..n) выходов синхронизатора соединены со входами синхронизации соответствующих (2. . .n) регистров и со входами управления соответствующих (2...n) блоков ключей, n-й выход синхронизатора соединен со вторым входом интегратора, (1...N) выходов блока хранения эталонного сигнала подключены к соответствующим (1...N) вторым входам блока сумматоров до модулю два, выходы которого соединены со входами сумматора, выходы сумматора являются выходами устройства.

Функциональная схема предлагаемого устройства представлена на фиг.2, где приняты следующие обозначения:

1 - частотный детектор (ЧД);

2 - интегратор;

3 - пороговый блок;

4 - синхронизатор;

51...n - регистры;

61...n - блоки ключей;

7 - блок сумматоров по модулю два (СМД);

8 - блок хранения эталонного сигнала (ХЭС);

9 - сумматор.

Предлагаемое устройство содержит последовательно соединенные ЧД1, интегратор 2 и пороговый блок 3, последовательно соединенные блок ХЭС8, блок СМД7 и сумматор 9, выходы которого являются выходами устройства, синхронизатор 4, регистры 51...n и блоки ключей 61...n, при этом выход порогового блока 3 подключен к информационным входам регистров 51...n, (1....N) выходов каждого из которых соединены соответственно с (1...N) информационными входами соответствующих блоков ключей 61...n, соответствующие выходы (1...N) блоков ключей 61...n объединены и подключены к соответствующим (1...N) вторым входам блока СМД7, выход ЧД1 соединен со входом синхрониpатора 4, (1...n) выходов которого подключены ко входам синхронизации соответствующих регистров 51...n и входам управления соответствующих блоков ключей 61...n, n-й выход синхронизатора 4 соединен со вторым входом интегратора 2, вход ЧД1 является входом устройства.

Предлагаемое устройство работает следующим образом. Частотно-модулированный сигнал поступает на вход ЧД1, где преобразуется в двухполярные импульсы, которые поступают затем на вход интегратора 2 (ФНЧ), накапливаются в нем на интервале одного бита информации и подаются на вход порогового блока 3. Затем значение накопленного на интеграторе 2 сигнала сбрасывается в конце каждого бита информации с помощью синхроимпульсов, поступающих от синхронизатора 4. В пороговом блоке 3 производится сравнение с порогом и принимается решение о принятом символе "0" или "1". Сигнал с ЧД1, кроме того, поступает еще на синхронизатор 4, где вырабатывается набор тактовых импульсов, следующих с частотой информации, но сдвинутых относительно друг друга на время ti = T/n, где T - длительность бита информации, а n - целое число. Информационная последовательность с блока 3 поступает затем на входы регистров 51...n, где записывается с помощью соответствующих тактовых импульсов с синхронизатора 4. Этим самым осуществляется дискретизация по времени каждого бита принимаемой информации и в регистры 51...n записываются отсчеты (выборки) отрезка информации. При этом число выборок, которое берется на одном бите информациия, равно n, а длительность отрезка информации определяется длиной (разрядностью N) отдельного регистра блока 5. Записанные в регистрах 51...n выборки сигнала поступают затем через соответствующие блоки ключей 61...n, открывающиеся под действием того же набора сдвинутых по времени тактовых импульсов с синхронизатора 4, на блок СМД7, где сравниваются с эталонным сигналом длиной N бит, хранящимся в блоке ХЭС8. Результаты сравнения подаются на сумматор 9, где осуществляется подсчет количества несовпадений по однотипным выборкам с эталонным сигналом на всем отрезке информации в N бит. Таким образом, на выходе сумматора 9 постоянно (с периодом ti) формируется результат сравнения N однотипных отсчетов с эталонным сигналом, причем наиболее достоверный результат сравнения априорно определяется в конце элемента двоичного сигнала, где значение сигнала при накоплении на интеграторе 2 достигает своей максимальной величины. Очевидно, что значения результатов сравнения, соответствующие интервалу элемента двоичного сигнала, имеют неодинаковую вероятность совпадения с наиболее достоверным результатом сравнения, что позволяет учитывать при анализе совокупность искажений сигнала (как краевых искажений, так и дроблений). Результаты сравнения группами по n значений, соответствующих отрезку обрабатываемой информации длиной в N бит, непрерывно (с периодом Т) поступают на выход устройства к потребителю.

Такой алгоритм получения оценки качества сигнала эквивалентен алгоритму получения оценки качества путем сравнения отсчетов, взятых на одном бите информации, с наилучшим (последним), соответствующим концу интегрирования, реализованным в прототипе.

Предлагаемое устройство реализуется физически на базе элементов и блоков, широко известных из технической литературы.

Техническая эффективность предлагаемого устройства в сравнении с прототипом заключается в более высокой надежности получения результатов оценки качества приема сигналов и более широких функциональных возможностях.

Первое обеспечивается тем, что в предлагаемом устройстве реализован принцип непрерывного формирования оценки качества на "скользящем" отрезке информации в отличие от прототипа, где формирование оценки качества осуществляется с периодом, определяемым цикличностью работы счетчика 10, после сброса которого накопленный результат оценки качества теряется и получается затем только к концу следующего периода его счета по другому отрезку информации.

Второе подучается за счет того, что если в предлагаемом устройстве записать в блок хранения эталонного сигнала 8 известный сигнал, то оно может работать еще как устройство поиска сигнала, т.е. реализуется принцип вычисления корреляционной функции принимаемого сигнала с заданным эталонным сигналом, что невозможно в прототипе.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛИЗАТОР СПЕКТРА | 1989 |

|

RU2007692C1 |

| ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ С ПОВЫШЕННОЙ ИНФОРМАЦИОННОЙ СКРЫТНОСТЬЮ | 1992 |

|

RU2033692C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2000 |

|

RU2168867C1 |

| ПРИЕМНОЕ УСТРОЙСТВО С ДВУХЭТАПНЫМ ПОИСКОМ ШУМОПОДОБНОГО СИГНАЛА | 2001 |

|

RU2190299C1 |

| СИСТЕМА РАДИОСВЯЗИ | 1998 |

|

RU2150175C1 |

| ЛИНИЯ РАДИОСВЯЗИ С ПОВТОРНЫМ ИСПОЛЬЗОВАНИЕМ ЧАСТОТЫ | 1999 |

|

RU2160506C2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ШИРОКОПОЛОСНЫХ СИГНАЛОВ ПРИ РАЗНЕСЕННОМ ПРИЕМЕ | 1992 |

|

RU2031544C1 |

| ЛИНИЯ РАДИОСВЯЗИ | 1999 |

|

RU2163053C2 |

| ЛИНИЯ РАДИОСВЯЗИ | 1999 |

|

RU2161865C2 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ ДЛЯ АДАПТИВНЫХ АДРЕСНЫХ СИСТЕМ | 1978 |

|

SU1840438A1 |

Предлагаемое устройство относится к области радиотехники и может быть использовано в адаптивных системах радиосвязи. Известное устройство оценки качества приема двоичных сигналов, содержащее последовательно соединенные частотный детектор, интегратор, пороговый блок и первый регистр, синхронизатор, первый выход которого подключен ко входу синхронизации первого регистра, и блок сумматоров по модулю два, обладает низкой надежностью получения результатов оценки качества приема двоичных сигналов и узкими функциональными возможностями. Введение в известное устройство дополнительно n-1 регистров, блоков ключей, блока хранения эталонного сигнала и сумматора позволяет повысить надежность получения результатов оценки качества приема двоичных сигналов и расширить функциональные возможности устройства. 2 ил.

Устройство оценки качества приема двоичных сигналов, содержащее последовательно соединенные частотный детектор, интегратор, пороговый блок и первый регистр, синхронизатор, первый выход которого подключен ко входу синхронизации первого регистра, и блок сумматоров по модулю два, при этом вход частотного детектора является входом устройства, отличающееся тем, что в устройство дополнительно введены п-1 регистров, п блоков ключей, блок хранения эталонного сигнала и сумматор, при этом выход порогового блока подключен к информационным входам (п-1) регистров, N выходов каждого из п регистров соединены соответственно с N информационными входами соответствующих п блоков ключей, соответствующие N выходы которых объединены и подключены к соответствующим N первым входам блока сумматоров по модулю два, выход частотного детектора соединен со входом синхронизатора, первый выход которого подключен к управляющему входу первого блока ключей, (п-1) выходов синхронизатора соединены со входами синхронизации соответствующих (п-1) регистров и с управляющими входами соответствующих (п-1) блоков ключей, п-й выход синхронизатора соединен со вторым входом интегратора, N выходов блока хранения эталонного сигнала подключены к соответствующим N вторым входам блока сумматоров по модулю два, выходы которого соединены со входами сумматора, выходы сумматора являются выходами устройства.

| RU 2001529 С1, 15.10.1993 | |||

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА ДИСКРЕТНЫХ КАНАЛОВ СВЯЗИ | 1992 |

|

RU2017333C1 |

| US 3976835 А, 24.08.1976 | |||

| US 3986168 А, 12.10.1976 | |||

| US 3731011 А, 01.05.1973 | |||

| US 3864528 А, 04.02.1975 | |||

| US 4633411 А, 30.12.1986 | |||

| US 4455644 А, 19.06.1984. | |||

Авторы

Даты

2000-09-20—Публикация

1998-12-16—Подача