Изобретение относится к области техники радиосвязи и может быть применимо для приема информации по каналам связи с использованием шумоподобных сигналов - ШПС.

Известны приемные устройства шумоподобных сигналов, построенные на базе согласованных фильтров. Время поиска сигнала в таких устройствах соизмеримо с периодом используемой двоичной последовательности. Однако реализовать на практике такие приемные устройства при больших базах сигнала - задача весьма проблематичная (см. Алексеев А.И., Шереметьев А.Г., Тузов Г.И. и Глазов Б.И. "Теория и применение псевдослучайных сигналов", М., 1965 г.).

Известно также приемное устройство широкополосных сигналов по а.с. 119915, содержащее линейный тракт, квадратурный перемножитель, интегратор, блок выбора и запоминания на такт, фильтр нижних частот - ФНЧ, управляемый фазовращатель, детектор огибающей, весовой сумматор и решающий блок. Недостатком этого устройства является то, что при наличии на его входе структурной помехи резко падает помехоустойчивость по отношению к другим видам помех, а при достаточно большом уровне этой помехи наступает срыв связи.

Наиболее близким по технической сущности к заявляемому объекту является приемное устройство шумоподобных сигналов, приведенное в книге "Шумоподобные сигналы в системах передачи информации" под ред. Пестрякова В.Б., М., "Сов. радио", 1973 г., стр.171, рис.55, принятое за прототип.

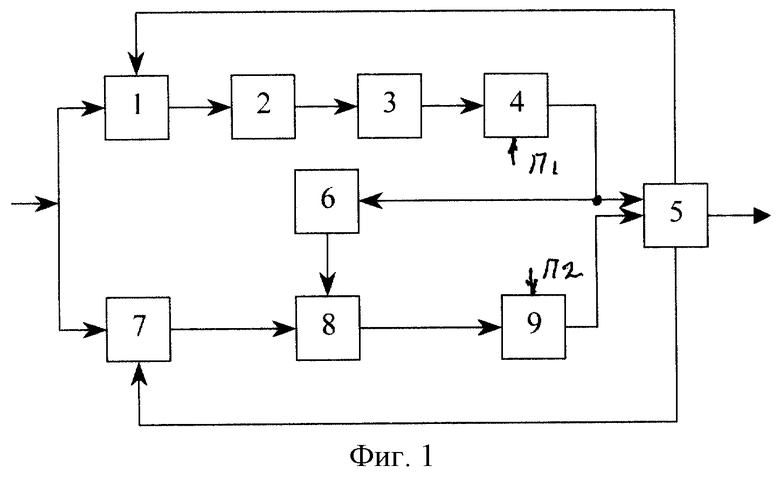

На фиг. 1 приведена функциональная схема устройства-прототипа, где введены следующие обозначения:

1 - первый ключ;

2 - согласованный с сегментом сигнала фильтр;

3 - детектор огибающей;

4 - первый пороговый блок;

5 - логический блок;

6 - генератор копий сигнала псевдослучайной последовательности (ГПСП);

7 - второй ключ;

8 - корреляционный блок (коррелятор);

9 - второй пороговый блок.

Устройство-прототип имеет следующие функциональные связи: последовательно соединенные первый ключ 1, согласованный с сегментом сигнала фильтр 2, детектор огибающей 3 и первый пороговый блок 4, выход которого соединен с первым входом логического блока 5 и входом генератора копий сигнала псевдослучайной последовательности 6, выход которого соединен со вторым входом корреляционного блока 8, а второй вход логического блока 5 через последовательно соединенные второй пороговый блок 9 и корреляционный блок 8 присоединен к выходу второго ключа 7; сигнальные входы первого 1 и второго 7 ключей соединены между собой и являются входом устройства, а управляющие входы этих ключей присоединены к первому и третьему выходам логического блока 5 соответственно, второй выход которого является выходом устройства; кроме того, вторые входы первого 4 и второго 9 пороговых блоков являются входами для напряжения порога.

Работает устройство-прототип следующим образом.

Сигнал с линейного тракта приемника поступает на вход устройства (сигнальные входы первого 1 и второго 7 ключей). В начале поиска первый ключ 1 открыт, а второй ключ 7 закрыт. Сигнал и помеха поступают на фильтр 2, согласованный с сегментом сигнала, и детектор огибающей 3. При превышении сигналом уровня порога первого порогового блока 4 включаются цепи проверки (второй этап), для чего включается генератор копий сигналов (ГПСП) 6, открывается логический блок 5 и второй ключ 7, а первый ключ 1 при этом закрывается. Сигнал и помеха поступают на корреляционный блок 8, на второй вход которого поступают копии сигнала с генератора 6 с задержкой, заданной согласованным фильтром 2. После накопления сигнала результат во втором пороговом блоке 9 сравнивается с пороговым напряжением, подаваемым на его второй вход, и выносится решение либо о возобновлении режима поиска (для чего логический блок 5 возвращает систему в исходное состояние), либо об окончании поиска. Это решение в виде нормированного вторичного сигнала запускает генератор копий сигнала 6 системы слежения за задержкой, которая устраняет оставшуюся ошибку задержки копии сигнала. После этого копия сигнала, синхронная с приходящим сигналом, подается в систему приема информации.

Однако данное устройство-прототип имеет довольно большое время поиска сигнала.

Для устранения указанного недостатка в устройство, содержащее первый и второй ключи, сигнальные входы которых соединены между собой и являются также входом устройства, при этом управляющие входы ключей соединены соответственно с первым и третьим выходами логического блока, второй выход которого является выходом устройства; первый и второй пороговые блоки, на вторые входы которых подается пороговое напряжение, а их выходы соединены с первым и вторым входами логического блока соответственно, и генератор копий сигналов, выход которого соединен со вторым входом первого коррелятора, введены второй коррелятор, состоящий из последовательно соединенных второго перемножителя и второго интегратора, причем выход первого ключа соединен с первым входом второго перемножителя, второй вход которого присоединен к выходу генератора копий сигнала. Второй вход второго интегратора соединен со вторым входом синхронизатора и четвертым входом логического блока, а выход второго интегратора соединен с первым входом первого порогового блока, выход которого присоединен к входу первого счетчика. Выход второго ключа соединен с первым входом первого коррелятора, состоящего из последовательно соединенных первого перемножителя и первого интегратора, второй вход которого соединен с третьим выходом синхронизатора и третьим входом логического блока, а выход первого интегратора соединен с первым входом второго порогового блока, выход которого присоединен к входу второго счетчика, n выходов которого соединены с первой группой n входов формирователя адреса, вторая группа n входов которого соединена с n выходами первого счетчика. Кроме того, четвертый выход логического блока соединен с первым входом формирователя адреса, n выходов которого присоединены к n входам постоянно-запоминающего устройства, n выходов которого соединены с n входами синхронизатора, первый выход которого соединен с входом генератора копий сигнала.

На фиг. 2 приведена функциональная схема предлагаемого устройства, где обозначено:

1 - первый ключ;

2 - второй коррелятор, состоящий из второго перемножителя 14 и второго интегратора 15;

3 - первый счетчик;

4 - первый пороговый блок;

5 - логический блок;

6 - генератор копий сигнала псевдослучайной последовательности (ГПСП);

7 - второй ключ;

8 - первый коррелятор, состоящий из первого перемножителя 16 и первого интегратора 17;

9 - второй пороговый блок;

10 - синхронизатор;

11 - второй счетчик;

12 - формирователь адреса;

13 - постоянно-запоминающее устройство (ПЗУ).

Предлагаемое устройство имеет следующие функциональные связи. Cигнальные входы первого 1 и второго 7 ключей соединены между собой и являются входом устройства. Выход второго коррелятора 2, состоящего из последовательно соединенных второго перемножителя 14 и второго интегратора 15, выход которого (является также и выходом второго коррелятора 2) через первый пороговый блок 4 соединен со входом первого счетчика 3 и первым входом логического блока 5, первый выход которого соединен с управляющим входом первого ключа 1, второй выход логического блока 5 является выходом устройства; третий выход логического блока 5 соединен с управляющим входом второго ключа 7, выход которого соединен с первым входом первого коррелятора 8, состоящего из последовательно соединенных первого перемножителя 16 и первого интегратора 17, выход которого соединен с первым входом второго порогового блока 9; при этом вторые входы первого 16 и второго 14 перемножителей соединены между собой и с выходом генератора копий сигнала ПСП 6, вход которого соединен с первым выходом синхронизатора 10, второй выход которого соединен со вторым входом второго интегратора 15 и с четвертым входом логического блока 5, третий выход синхронизатора 10 соединен со вторым входом первого интегратора 17 и третьим входом логического блока 5, второй вход которого соединен с выходом второго порогового блока 9 и входом второго счетчика 11, n выходов которого соединены с первой группой n входов формирователя адреса 12, вторая группа n входов которого соединена с n выходами первого счетчика 3; четвертый выход логического блока 5 соединен с первым входом формирователя адреса 12, n выходов которого через постоянно-запоминающее устройство (ПЗУ) 13 соединены с n входами синхронизатора 10; кроме того, на вторые входы первого 4 и второго 9 пороговых блоков поступают сигналы порогового напряжения.

Предлагаемое устройство работает следующим образом.

Принятый широкополосный сигнал преобразуется в промежуточную частоту и усиливается до необходимой величины в линейном тракте приемника и затем поступает на вход устройства - сигнальные входы первого 1 и второго 7 ключей.

В начале поиска сигнала первый ключ 1 открыт, а второй ключ 7 закрыт. Сигнал и шум поступают на первый вход коррелятора 2, состоящего из последовательно соединенных второго перемножителя 14 и второго интегратора 15. На второй вход второго перемножителя 14 поступает сигнал с генератора копий сигнала ПСП 6. С интегратора 15, работой которого управляет синхронизатор 10, сигнал поступает на первый счетчик 3. Если измеренное время задержки не совпадает с истинным (напряжение на выходе интегратора не превышает порога порогового блока 4), то значение первого счетчика 3 увеличивается на единицу и поступает на n входы формирователя адреса 12, который последовательно формирует адрес первого столбца матрицы (см. таблицу), значение элементов которой записаны в ПЗУ для заданной базы фазоманипулированного (ФМ) сигнала.

В таблице приведено разложение на смежные классы для элементов ПСП с базой В = 63. В первом столбце таблицы приведены наименьшие элементы смежных классов (лидеры смежных классов).

Синхронизатор 10 имеет время задержки шумоподобного сигнала в генераторе копий сигнала ПСП 6 на количество тактов К, считанное ПЗУ 13. Кроме этого, синхронизатор 10 обеспечивает включение и выключение второго интегратора 15 и подачу отсчетных импульсов на логический блок 5. При превышении сигналов с выхода второго интегратора 15 порога первого порогового блока 4 включаются цепи проверки (второй этап), для чего логический блок 5 открывает второй ключ и закрывает первый ключ 1, подает сигнал на формирователь адреса 12, который начинает формировать адреса строки матрицы (таблица), для которой произошло превышение порога в первом пороговом блоке 4.

Сигнал с шумом поступает на первый вход первого коррелятора 8, а на его второй вход поступает копия сигнала с генератора ПСП 6 с задержкой, сформированной синхронизатором 10. С первого коррелятора 8 сигнал поступает на второй пороговый блок 9 (его порог отличается от порога первого порогового блока 4), с выхода которого сигнал поступает на второй счетчик 11 и логический блок 5.

После каждого непревышения порога во втором пороговом блоке 9 значение второго счетчика 11 увеличивается на единицу и сигнал поступает в формирователь адреса 12, который формирует адрес строки матрицы (таблица) с номером, при котором превышен порого на первом этапе поиска.

Далее, как и на первом этапе, выбирается значение из ПЗУ 13, по которому синхронизатор 10 управляет работой генератора копий сигнала ПСП 6.

На этом синхронизация заканчивается и информационный сигнал подается на выход устройства для потребителя.

Изобретение относится к области техники радиосвязи и может быть использовано для приема информации по каналам связи с использованием шумоподобных сигналов. Достигаемый технический результат - сокращение времени поиска сигнала. Устройство содержит два ключа, два пороговых устройства, детектор огибающей, логическое устройство, генератор копии сигнала ПСП, два коррелятора, синхронизатор, два счетчика, формирователь адреса, ПЗУ. 2 ил., 1 табл.

Приемное устройство с двухэтапным поиском шумоподобного сигнала, содержащее первый и второй ключи, сигнальные входы которых соединены между собой и являются также входом устройства, при этом управляющие входы ключей соединены соответственно с первым и третьим выходами логического блока, второй выход которого является выходом устройства; первый и второй пороговые блоки, на вторые входы которых подается пороговое напряжение, а их выходы соединены с первым и вторым входами логического блока соответственно, и генератор копии сигналов псевдослучайной последовательности (ПСП), выход которого соединен с вторым входом первого перемножителя первого коррелятора, отличающееся тем, что введены второй коррелятор, состоящий из последовательно соединенных второго перемножителя и второго интегратора, причем выход первого ключа соединен с первым входом второго перемножителя; второй вход второго интегратора соединен со вторым выходом синхронизатора и четвертым входом логического блока, а выход второго интегратора соединен с первым входом первого порогового блока, выход которого присоединен к входу первого счетчика; выход второго ключа соединен с первым входом первого коррелятора, состоящего из последовательно соединенных первого перемножителя и первого интегратора, второй вход которого соединен с третьим выходом синхронизатора и третьим входом логического блока, а выход первого интегратора соединен с первым входом второго порогового блока, выход которого присоединен к входу второго счетчика, n выходов которого соединены с первой группой n входом формирователя адреса, вторая группа n входов которого соединена с n выходов первого счетчика; кроме того, четвертый выход логического блока соединен с первым входом формирователя адреса, n выходов которого присоединены к n входам постоянно запоминающего устройства, n выходов которого соединены с n входами синхронизатора, первый выход которого соединен с входом генератора копий сигнала ПСП, при этом вторые входы первого и второго перемножителей соединены между собой и с выходом генератора копий сигнала ПСП.

| Шумоподобные сигналы в системах передачи информации./Под | |||

| ред | |||

| В.Б | |||

| ПЕСТРЯКОВА, -М.: Советское радио, 1973, с | |||

| Аппарат для передачи изображений на расстояние | 1920 |

|

SU171A1 |

| Приемное устройство широкополосного сигнала | 1982 |

|

SU1109915A1 |

| АДАПТИВНОЕ ПРИЕМНОЕ УСТРОЙСТВО ШУМОПОДОБНЫХ СИГНАЛОВ | 1997 |

|

RU2128881C1 |

| US 5218620 А, 08.06.1993 | |||

| Способ получения 5-хлорпентадиена1,3 | 1973 |

|

SU472926A1 |

Авторы

Даты

2002-09-27—Публикация

2001-01-30—Подача