Изобретение относится к импульсной технике и может быть использовано в устройствах обработки импульсных сигналов.

Известен формирователь импульсов, который содержит первый и второй элементы И-НЕ, асинхронный триггер, элемент задержки, входную и выходную шины [1].

Недостатком данного аналога является то, что он обеспечивает защиту от помех только в течение малого промежутка времени после появления входного сигнала, и, следовательно, непригоден в случае, если входной сигнал низкочастотный.

Известен формирователь импульсов, который содержит входную шину, D-триггер, инверсный выход которого соединен с D-входом, и элемент задержки, состоящий из четного числа инверторов [2].

Недостатком данного прототипа является отсутствие защиты от помех во входном сигнале.

Технический результат изобретения заключается в защите устройства от помех во входном сигнале.

Сущность изобретения заключается в том, что в устройство, содержащее входную шину, D-триггер, инверсный выход которого соединен с D-входом, и элемент задержки, состоящий из четного числа инверторов, введены шина тактовых импульсов, счетчик, C-вход которого соединен с шиной тактовых импульсов, элемент И, первый вход которого соединен одновременно с D-входом и с инверсным выходом D-триггера, а второй вход соединен с выходом Qn счетчика, а выход соединен с C-входом D-триггера; элемент И-НЕ, первый вход которого соединен одновременно с входной шиной и с R- входом счетчика, а второй вход соединен с выходом элемента задержки, а выход соединен одновременно с инверсным R-входом D- триггера и выходной шиной, а вход элемента задержки соединен с прямым выходом D-григгера.

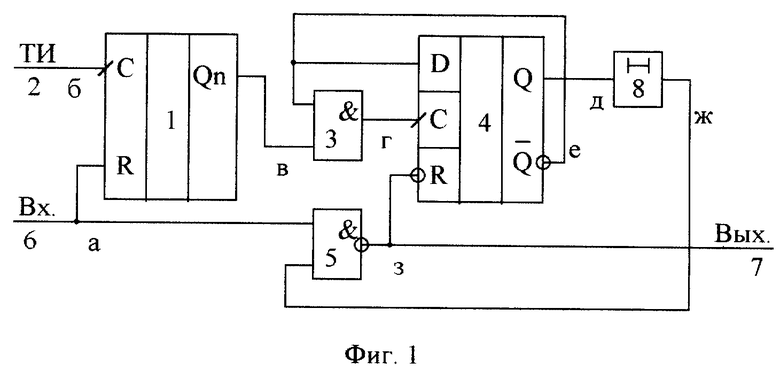

На фиг. 1 приведена электрическая функциональная схема устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Формирователь импульсов содержит счетчик 1, C-вход которого соединен с шиной тактовых импульсов 2, элемент И 3, первый вход которого соединен одновременно с D-входом и с инверсным выходом D-триггера 4, а второй вход соединен с выходом Qn счетчика 1, а выход соединен с C-входом D-триггера 4, элемент И-НЕ 5, первый вход которого соединен одновременно с входной шиной 6 и с R-входом счетчика 1, а выход соединен одновременно с инверсным R-входом D-триггера 4 и выходной шиной 7, элемент задержки 8, состоящий из четного числа инверторов, вход которого соединен с прямым выходом D-триггера 4, а выход соединен с вторым входом элемента И-НЕ 5.

Счетчик представляет собой либо суммирующий двоичный счетчик, либо суммирующий счетчик с произвольным коэффициентом счета.

Формирователь импульсов работает следующим образом.

В исходном состоянии на шине 6 - потенциал "0" (фиг. 2, а), на прямом выходе D-триггера 4 - потенциал "1" (фиг. 2, д). Сигнал с прямого выхода D-триггера 4 поступает через элемент задержки на второй вход элемента И-НЕ 5 и открывает его для прохождения входного сигнала по шине 6. При приходе входного импульса на шину 6 (фиг. 2, а) на выходе Qn счетчика 1 устанавливается потенциал "0" (фиг. 2, в) и счетчик начинает отсчет тактовых импульсов, поступающих на C-вход счетчика 1 по шине тактовых импульсов 2 (фиг. 2, б). Этим же входным импульсом на выходе элемента И-НЕ 5 устанавливается потенциал "0" (фиг. 2, з), который устанавливает на прямом выходе триггера 4 потенциал "0" (фиг. 2, д). Пройдя через элемент задержки (фиг. 2, ж), этот потенциал поступает на второй вход элемента И-НЕ 5 и на выходе этого элемента устанавливается потенциал "1" (фиг. 2, з). Таким образом, длительность импульса на выходной шине 7 формирователя импульсов t3, (фиг. 2, з) определяется числом инверторов в элементе задержки 8. Благодаря наличию потенциала "0" на втором входе элемента И-НЕ 5 случайные помехи во входном сигнале (фиг. 2, а) не оказывают влияния на работу схемы. Единственным требованием является то, что входной импульс должен закончиться раньше, чем появится потенциал "1" на выходе Qn счетчика 1. Таким образом, этим требованием определяется разрядность счетчика 1. Отсчитав заданное число тактовых импульсов (в данном случае 8), на выходе Qn устанавливается потенциал "1" (фиг. 2, в), и на выходе элемента И 3 устанавливается потенциал "1" (фиг. 2, г), что приводит к переключению D-триггера 4 и на прямом выходе триггера устанавливается потенциал "1" (фиг. 2, д), а на инверсном выходе - потенциал "0" (фиг. 2, е), который снова устанавливает на выходе элемента И 3 потенциал "0" (фиг. 2, г). Потенциал "1", установленный на прямом выходе триггера 4, пройдя через элемент задержки 8 (фиг. 2, ж), поступает на второй вход элемента И-НЕ 5 и схема снова готова к приему входного импульса.

Такое выполнение формирователя импульсов позволяет защищать его от помех во входном сигнале.

Литература

1. Авторское свидетельство СССР N 815880, кл. H 03 К 5/01. Заявлено 19.02.79. Опубликовано 23.03.81. Бюллетень N 11.

2. Применение интегральных микросхем в электронной вычислительной технике. Под. Ред. Б.Н.Файзулаева, Б.В.Тарабрина.- М.: Радио и связь, 1986.-383 с. (с. 106, рис. 5.35, б.)с

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНЫЙ КОМПАРАТОР | 1999 |

|

RU2161368C1 |

| Устройство для подавления дребезга контактов @ выключателей | 1988 |

|

SU1621155A1 |

| Устройство для выделения первого и последнего импульсов в серии | 1990 |

|

SU1739492A1 |

| ЭЛЕКТРОННАЯ СХЕМА ДЛЯ БЛОКА УПРАВЛЕНИЯ ЭКОНОМАЙЗЕРОМ ПРИНУДИТЕЛЬНОГО ХОЛОСТОГО ХОДА АВТОМОБИЛЯ | 2000 |

|

RU2172858C1 |

| Формирователь импульсов | 1989 |

|

SU1718368A1 |

| Формирователь импульсов по фронту и спаду | 1981 |

|

SU1132352A1 |

| Управляемый делитель частоты | 1985 |

|

SU1277389A1 |

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| Селектор импульсов по длительности | 1979 |

|

SU805485A1 |

| Селектор серий импульсов | 1988 |

|

SU1615875A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах обработки импульсных сигналов. Предложено устройство, содержащее входную шину (6), D-триггер (4), инверсный вход которого соединен с D-входом, и элемент задержки (8), состоящий из четного числа инверторов. Введены шина тактовых импульсов (2), счетчик (1), С-вход которого соединен с шиной тактовых импульсов (2), элемент И (3), первый вход которого соединен одновременно с D-входом и с инверсным выходом D-триггера (4), второй вход - выходом Qn счетчика (1), выход - с С-входом D-триггера (4), элемент И-НЕ (5), первый вход которого соединен одновременно с входной шиной (6) и с R-входом счетчика (1), второй вход - с выходом элемента задержки (8), а выход -одновременно с инверсным R-входом D-триггера (4) и выходной шиной (7). Вход элемента задержки (8) соединен с прямым выходом D-триггера (4). Технический результат - защита устройства от помех во входном сигнале. 2 ил.

Формирователь импульсов с защитой от помех, содержащий входную шину, D-триггер, инверсный вход которого соединен с D-входом, и элемент задержки, состоящий из четного числа инверторов, отличающийся тем, что в него введены шина тактовых импульсов, счетчик, С-вход которого соединен с шиной тактовых импульсов, элемент И, первый вход которого соединен одновременно с D-входом и с инверсным входом D-триггера, второй вход - с выходом Qn счетчика, а выход - с С-входом D-триггера, элемент И-НЕ, первый вход которого соединен одновременно с входной шиной и с R-входом счетчика, второй вход - с выходом элемента задержки, а выход - одновременно с инверсным R-входом D-триггера и выходной шиной, а вход элемента задержки соединен с прямым выходом D-триггера.

| Формирователь импульсов | 1979 |

|

SU815880A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1990 |

|

RU2074511C1 |

| Формирователь импульсов | 1978 |

|

SU720709A1 |

| Устройство для формирования импульсов | 1987 |

|

SU1422376A1 |

| Формирователь импульсов | 1977 |

|

SU661746A1 |

| Формирователь импульсов | 1990 |

|

SU1735997A2 |

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| СПОСОБ ПОЛУЧЕНИЯ МЕТИЛЕНДИАЦЕТАТА | 1993 |

|

RU2039732C1 |

| Применение интегральных микросхем в электронной вычислительной технике./Под ред | |||

| ФАЙЗУЛАЕВА Б.Н., ТАРАБРИНА Б.В | |||

| - М.: Радио и связь, 1986, с.106, рис.5.35.б. | |||

Авторы

Даты

2000-10-10—Публикация

1999-10-19—Подача