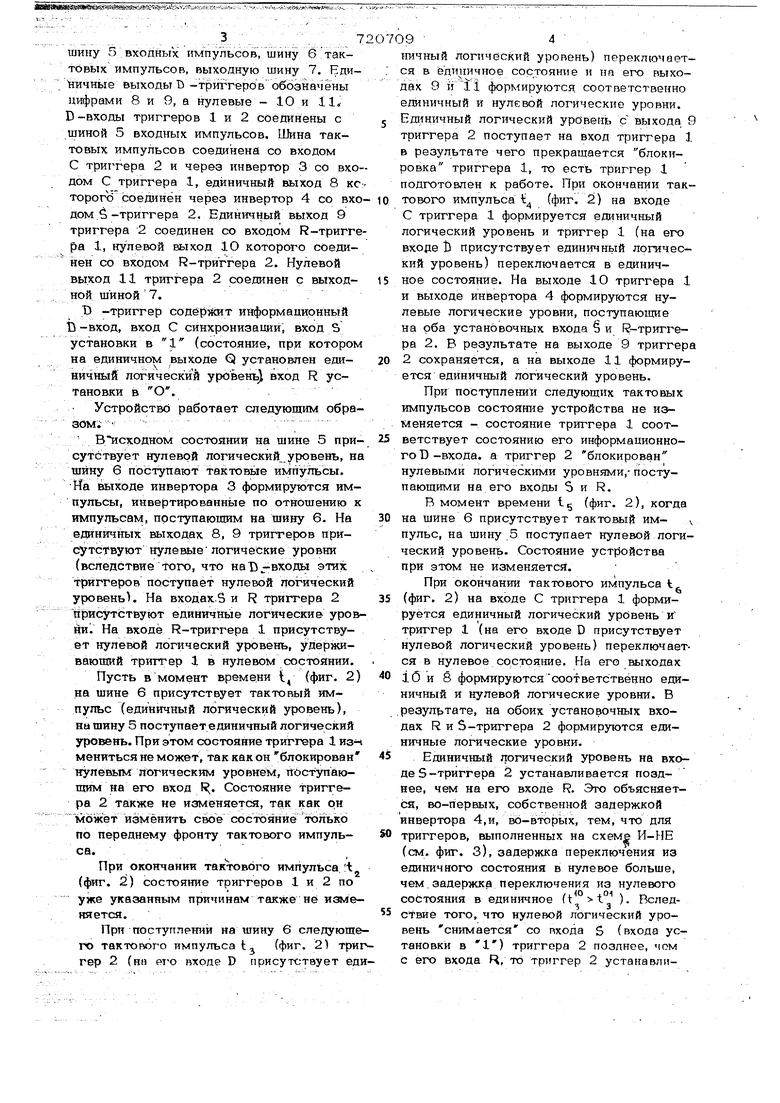

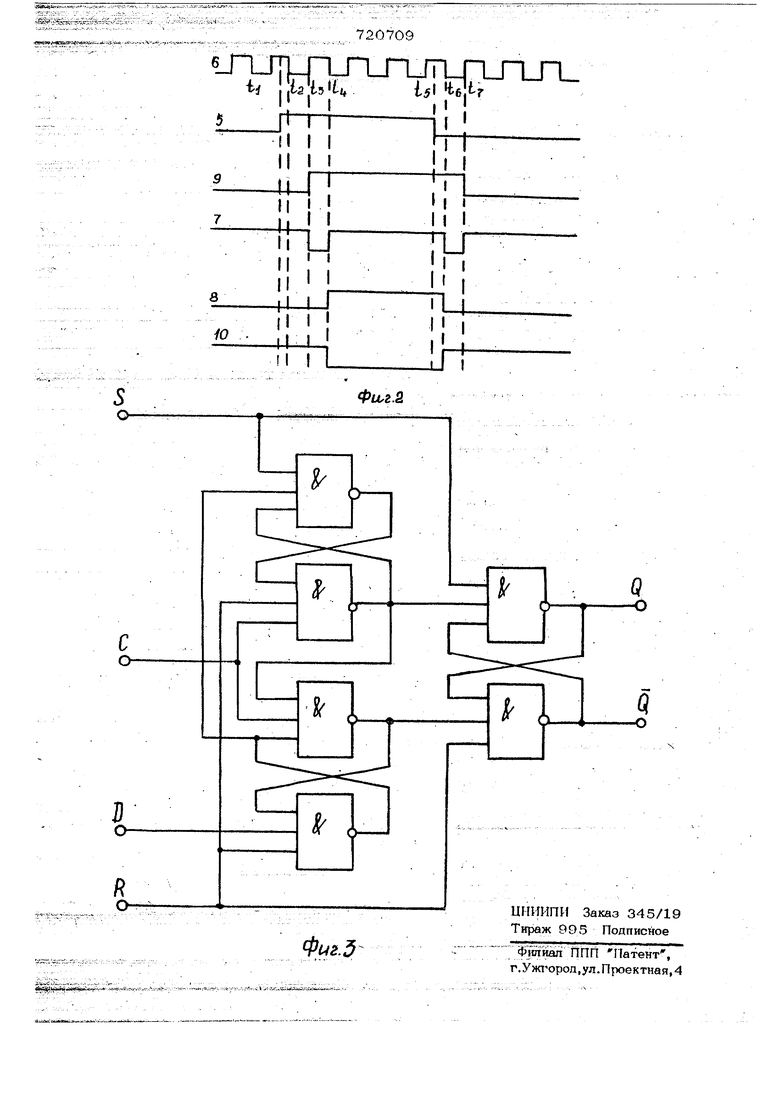

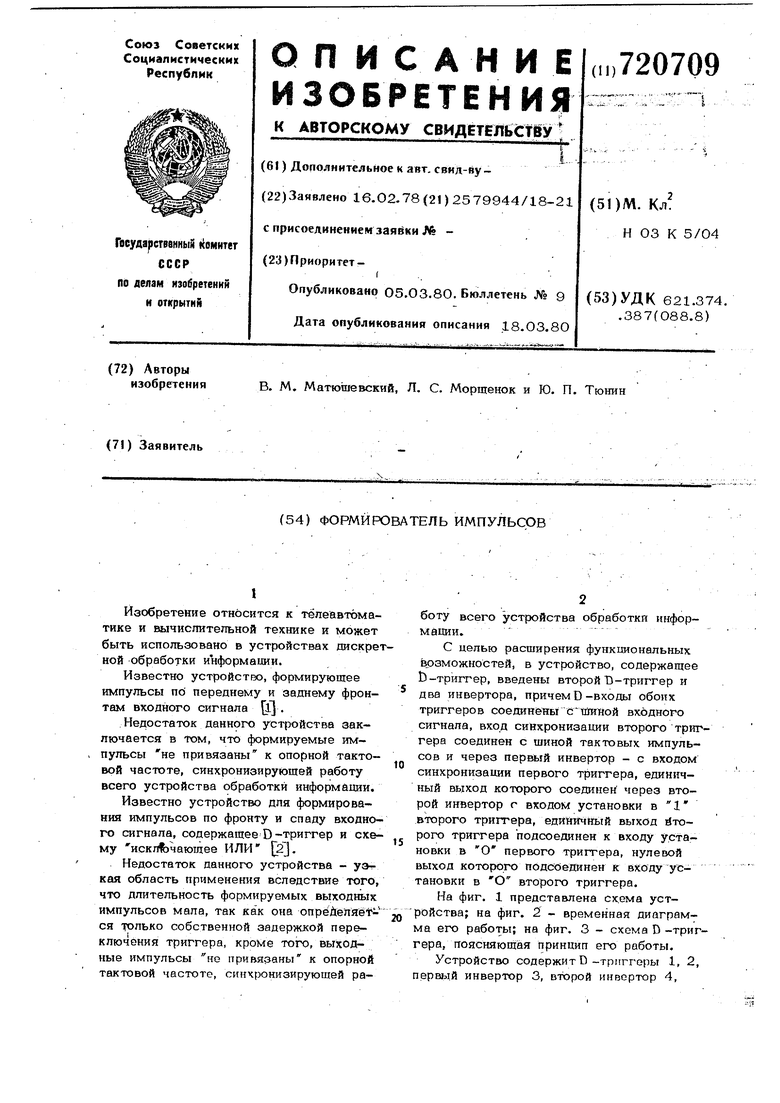

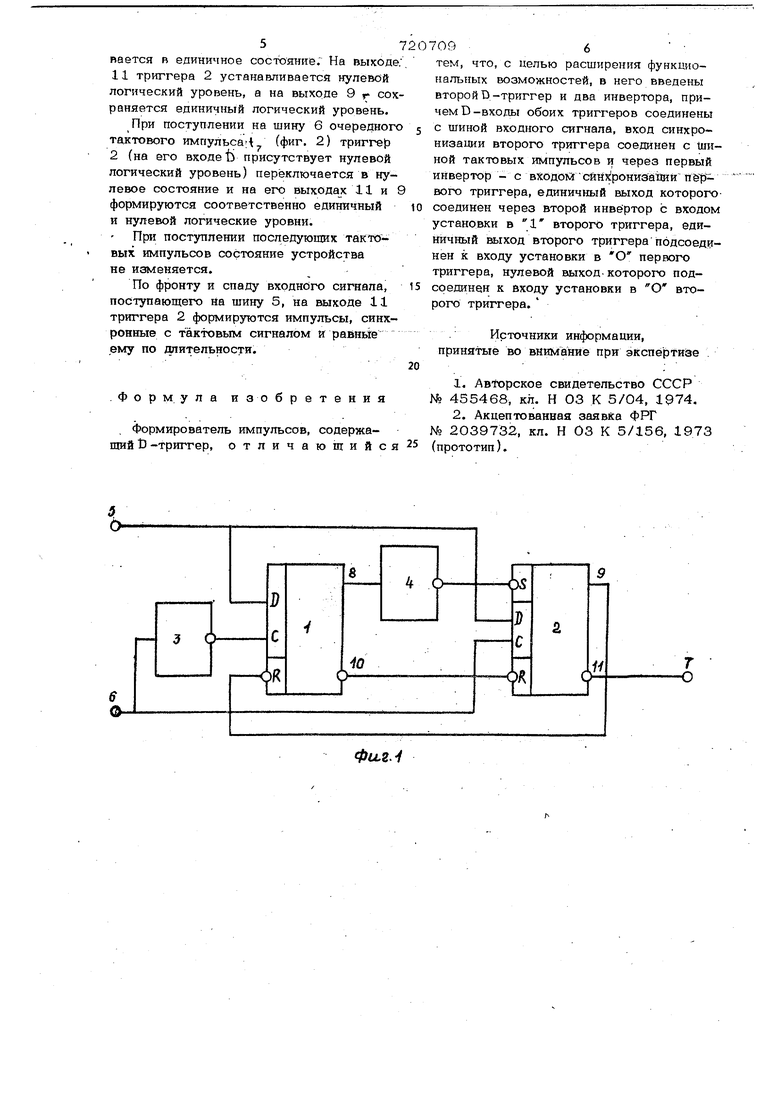

Изобретение относится к телеавтоматике и ш 1числительной текнике и может быть использовано в устройствах дискрет ной обработки информации. Известно устройство, формирующее импульсы по переднему и заднему фронтам входного сигнала jl . Недостаток данного устройства заключается в том, что формируемые импульсы не привязаны к опорной тактовой частоте, синхронизирующей работу всего устройства обработки информации. Известно устройство для формирования импульсов по фронту и спаду входного сигнала, содержащее D-триггер и схему исключающее ИЛИ 2, . Недостаток данного устройства - уэткая область применения вследствие того, что длительность формируемых выходных импульсов мала, так как она опрейёляё1гся только собственной задержкой переключения триггера, кроме того, выходные импульсы не привязаны к опорной тактовой частоте, синхронизирующей работу всего устройства обработки информации. С целью расширения функциональных возможностей, в устройство, содержащее Ь-триггер, введены второй Т)-триггер и два инвертора, причем D-входы обоих триггеров соединены С Тйиной входного сигнала, вход синхронизации второго триггера соединен с шиной тактовых импульсов и через первый инвертор - с входом синхронизации первого триггера, единичный выход которого соединен через второй инвертор г входом установки в второго триггера, единигчный выход йторого триггера подсоединен к входу установки в О первого триггера, нулевой выход которого пОдсОеданен к входу установки в О второго триггера. На фиг. 1 представлена схема устройства; на фиг. 2 - временная диаграмма его работы; на фиг. 3 - схема D -триггера, поясняющая принцип его работы. Устройство содержите-триггеры 1, 2, першр1й инвертор 3, второй инвертор 4,

шину v5 входных импульсов, шину 6тактовых импульсов, выходную шину 7. Еди1ничные выходы В -триггеров обозначены цифрами 8 и 9, а нулевые - 10 и 11 D -входы триггеров 1 и 2 соединены с шиной 5 входных импульсов. Шина тактовых импульсов соединена со входом С триггера 2 и через инвертор 3 со входом С триггера 1, единичный выход 8 кс:торого соединен через инвертор 4 со вхо дом ,-триггера 2. Единичный выход 9 триггера 2 соединен со входом R-тригге ра 1, нулевой выход Ю которого соединен со входом R-триггера 2. Нулевой выход 11 триггера 2 соединен с выходной шиной7. .В -триггер содёряшт информационный ti -вход, вход С синхронизации, вход S установки в 1 (состояние, при котором на единичном выходе Q установлен единичньгй логический уровень} вход R установки в О. Устройство работает следующим обраaoMi-; ,-,..- -..,,..-,--. Висх:одном состоянии на шине 5 присутствует нулевой логический уровень, н шину б поступают тактоетле импульсы. На выходе инвертора 3 формируются импульсы, инвертированные по отношению к импульсам, поступающим на шину 6. На единичных выходах 8, 9 триггеров присутствуют нулевые логические уровни (вследствие toro, что наТ)-входь1 этих триггеров поступает нулевой логический уровеньК На входах..5 и R триггера 2 присутствуют единичные логические уров ни На входе R-триггера 1 присутствует нулевой логический уровень, удерживающий триггер 1 в нулевом состоянии. Пусть в момент времени i (фиг. 2) на шине 6 присутствует тактовый импульс (единичный логический уровень), на шину 5 поступает единичный логический уровень. При этом состояние триггера 1 измениться не может, так как он блокирован нупеЕкым логическим уровнем, поступающим на его вход 1. Состояние триггера 2 также не изменяется, так как он может изменить свое состояние только по переднему фронту тактового импульса. При окончании тактового импульса (ф1гг. 2) состояние триггеров 1 и 2 по уже указанным причинам также: не изме няется. При поступлений на шину 6 следующе го тактового импульса t (фиг. 2) три гер 2 (ни его входе D присутствует ед

72О709

ничный логический уровень) переключается в единичное состояние и на его выходах 9 и Ji формируются соответственно единичный и нулевой логические уровни. Ешшичный логический уровень с выхода 9 триггера 2 поступает на вход триггера 1 в результате чего прекращается блокировка триггера 1, то есть триггер 1 подготовлен к работе. При окончании тактового импульса € (фиг. 2) на входе С триггера 1 формируется единичный логический уровень и триггер 1 (на его входе Ъ присутствует единичный логический уровень) переключается в единичное состояние. На выходе 10 триггера 1 и выходе инвертора 4 формируются нулевые логические уровни, поступающие на оба установочных входа § и R-тригге- ра 2. В результате на выходе 9 триггера 2 сохраняется, а на выходе 11 формируется единичный логический уровень. При поступлении следующих тактовых импульсов состояние устройства не изменяется - состояние триггера 1 соответствует состоянию его информационного D-входа, а триггер 2 блокирован нулевыми логическими уровнями,-поступающими на его входы S и R. В момент времени t (фиг. 2), когда на шине 6 присутствует тактовый им- v пульс, на шину 5 поступает нулевой логический уровень. Состояние уст{5ойства при этом не изменяется. При окончании тактового импульса t (фиг. 2) на входе С триггера 1 формируется единичный логический уровень и триггер 1 (на его входе D присутствует нулевой логический уровень) переключается в нулевое состояние. На его выходах 10 и 8 формируются соответственно единичный и нулевой логические уровни. В резул тате, на обоих установочных входах R и S-триггера 2 формируются еда- ничные логические уровни. Единичный логический уровень на входе 5-триггера 2 устанавливается позднее, чем на его входе R. Это объясняется, во-первых, собственной задержкой инвертора 4,и, в6-в то|эых, тем, что для триггеров, выполненных на схеме И-НЕ (см. фиг. 3), задержка переключения из единичного состояния в нулевое больше, чем. задержка переключения из нулевого состояния в единичное (t ). Вследствие того, что нулевой логический уровень снимается со пхода S (входа установки в ) триггера 2 позлнее, чем С его входа R, то тртгггер 2 устанавлпвеется в единичное состояние. На выходе 11 триггера 2 устанавливается нулевой логический уровень, а на выходе 9 г сох раняется единичный логический уровень. При поступлении на шину 6 очередног тактового импульса; (фиг. 2) триггер 2 (на его входе ti присутствует нулевой логический уровень) переключается в нулевое состояние и на его выходах 11 и формируются соответственно единичный и нулевой логические уровни. При поступлении последующих такто вых импульсов состояние устройства не изменяется. По фронту и спаду входного сигнала, поступающего на шину 5, на выходе 11 триггера 2 формируются импульсы, синхронные с тактчэвым сигналом и раьнйе ему по длительности. Формула изобретения Формирователь импульсов, содержащий t) -триггер, отличающийся тем, что, с целью расширения функшюнальных возможностей, в него введены второйD-триггер и два инвертора, причем D -входы обоих триггеров соединены с шиной входного сигнала, вход синхронизации второго триггера соединен с шиной тактовых импульсов и через первый инвертор - с входом сйнхронизайий netiвого триггера, единичный выход которогосоединен через второй инвертор с входом установки в второго триггера, единичный выход второго триггера подсоединен к входу установки в О первого триггера, нулевой выход-которого подсоединен к входу установки в О второго триггера. Источники информации, принятые во внимание при экспертизе . 1.Авторское свидетельство СССР № 455468, кл. Н 03 К 5/04, 1974. 2.Акцептованная заявка ФРГ № 2039732, кл. Н 03 К 5/156, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и диагностики цифровых устройств | 1987 |

|

SU1583914A2 |

| Устройство для контроля и диагностики цифровых устройств | 1988 |

|

SU1583886A2 |

| Устройство для временного разделения импульсных сигналов | 1983 |

|

SU1200401A1 |

| Формирователь дискретных сигналов | 1982 |

|

SU1115210A1 |

| Устройство для контроля и диагностики цифровых устройств | 1986 |

|

SU1499286A1 |

| Устройство для синхронизации импульсов | 1978 |

|

SU790213A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ПО ФРОНТУ И СРЕЗУ СИГНАЛОВ | 1987 |

|

SU1537106A1 |

| Устройство для синхронизации импульсов | 1978 |

|

SU748841A1 |

| Формирователь одиночного импульса | 1989 |

|

SU1621156A1 |

| Устройство для приема биимпульсных сигналов | 1990 |

|

SU1741282A2 |

Фи,2.-1

- Йеи5Ьг/.--«.-..-:.-Г.-.--.-:.

яёй г ГК;- /7 :;;Й5-7 : ..ii «Sa -;if «iJuf ;.:S,}

720709

Авторы

Даты

1980-03-05—Публикация

1978-02-16—Подача