Изобретение относится к радиоэлектронике, а конкретно к цифровым генераторам, предназначенным для использования в цифровых следящих системах корреляционной обработки сигналов, преимущественно сигналов спутниковых радионавигационных систем (СРНС) или спутниковых систем связи (ССС).

Особенностью цифровой корреляционной обработки сигналов СРНС или ССС является то, что выделение информации, содержащейся в обрабатываемом сигнале, производится с помощью замкнутых цифровых следящих систем, осуществляющих формирование копии обрабатываемого сигнала и последующее корреляционное сравнение копии с самим сигналом в процессе слежения за несущей и задержкой сигнала, см., например [1, с.269-271, рис.15.3], [2, часть I, с.82-85, рис. 9. 10], [3, с.24-31, рис.1.14 - 1.21]. Как правило, такие цифровые следящие системы содержат вычислители (цифровые процессоры), цифровые смесители, демодуляторы, накопители, а также управляемые вычислителем цифровые генераторы (цифровые синтезаторы), см., например [4]. Управляемые вычислителем цифровые генераторы, формирующие в цифровом виде значения фаз опорных колебаний, используемых в цифровых следящих системах корреляционной обработки сигналов (преимущественно сигналов СРНС или ССС), являются предметом рассмотрения в настоящей заявке.

Известно применение цифровых генераторов в качестве генераторов несущей и тактовой частоты кода в цифровых следящих системах, осуществляющих корреляционную обработку сигналов СРНС GPS ("Навстар") (США) и ГЛОНАСС (Россия).

Например, в известном интегрированном приемнике сигналов СРНС [5] каждый из каналов цифрового коррелятора содержит управляемый цифровой генератор несущей [5, фиг.4-5, блок 30], являющийся элементом цифровой следящей системы за несущей ("схемы слежения за несущей"). Цифровой генератор несущей формирует в цифровом виде текущие значения фазы несущей частоты опорного сигнала, используемые в цифровых смесителях в процессе "квадратурного перемножения" с сигналами, поступающими из радиочастотного преобразователя, для "снятия" несущей и переноса спектра обрабатываемого сигнала на нулевую частоту, на которой осуществляются последующие операции демодуляции и накопления. Управление цифровым генератором несущей осуществляется по сигналам вычислителя, входящим в состав интегрированного приемника, в частности от вычислителя поступают данные кода частоты несущей. Данные, поступающие от вычислителя, преобразуются в накапливающем сумматоре цифрового генератора несущей по определенному закону и запоминаются в выходном регистре, формируя цифровые сигналы, определяющие текущие значения фазы формируемого опорного сигнала. Кроме цифрового генератора несущей в интегрированном приемнике сигналов СРНС [5] каждый из каналов цифрового коррелятора содержит управляемый цифровой генератор тактовой частоты кода (цифровой генератор кода) [5, фиг.4-5, блок 32] , являющийся элементом цифровой следящей системы за задержкой кода ("схемы слежения за задержкой"). Цифровой генератор кода формирует в цифровом виде текущие значения фазы опорного тактового сигнала С/А кода (1,023 МГц для GPS и 0,511 МГц для ГЛОНАСС). Структура цифрового генератора кода аналогична структуре цифрового генератора несущей.

Основой рассмотренных управляемых цифровых генераторов, представленных в [5, фиг. 4-5, блоки 30, 32], является накапливающий сумматор, управляемый вычислителем. Использование вычислителя позволяет реализовать высокую точность формирования опорных сигналов, необходимых для работы цифровых следящих систем, что дает возможность осуществлять, в частности, высокоточные измерения временных задержек и доплеровских сдвигов частоты принимаемых сигналов СРНС.

Общие принципы построения цифровых генераторов на основе накапливающих сумматоров известны и достаточно широко представлены в источниках информации.

Например, в [2, часть I, с.89-91, рис.18] описана структурная схема цифрового генератора (синтезатора частот), используемого при формировании опорного сигнала несущей частоты в приемнике сигналов СРНС "Навстар". Основу этого цифрового генератора составляет 21-разрядный накапливающий сумматор, выполненный в виде последовательно соединенных 21-разрядного комбинационного сумматора, первый вход которого является входом "кода Доплера", и 21-разрядного регистра памяти, работающего с частотой дискретизации fs = 5,115 МГц, выход которого соединен с вторым входом комбинационного сумматора. В таком цифровом генераторе реализуется известный метод прямого цифрового синтеза частоты, основанный на накоплении приращений фазы с помощью накапливающего сумматора. По этому же принципу и с использованием 32-разрядного накапливающего сумматора выполнен управляемый цифровой генератор кода приемника сигналов СРНС "Навстар", описанный в [2, часть II, с.72-73, рис.36].

Рассмотренные цифровые генераторы, выполненные на основе накапливающего сумматора и реализующие метод прямого цифрового синтеза частоты, формируют в цифровом виде текущие значения фазы опорных сигналов. При необходимости, на основе этих цифровых сигналов, характеризующих текущие значения фазы, формируется аналоговый сигнал, например, с помощью преобразователя кодов, реализующего "таблицу синусов (косинусов)", и цифроаналогового преобразователя.

Среди цифровых генераторов, предназначенных для использования в цифровых следящих системах корреляционной обработки сигналов, реализующих метод прямого цифрового синтеза, наиболее близким к заявляемому цифровому генератору по своему выполнению является цифровой генератор, представленный в [6, с. 90-92, рис.34], который выбран в качестве прототипа.

Цифровой генератор для цифровых следящих систем корреляционной обработки сигналов, выбранный в качестве прототипа, выполнен в виде накопительного модуля, содержащего последовательно соединенные К-разрядные регистр кода частоты и накапливающий сумматор, работающий с частотой дискретизации fs. Накапливающий сумматор выполнен в виде последовательно соединенных К-разрядных комбинационного сумматора, первый вход которого является входом накапливающего сумматора, и регистра-накопителя (регистра фазы), выход разрядов которого подключен к второму входу комбинационного сумматора. Информационный вход регистра кода частоты образует управляющий вход, а выход разрядов регистра фазы - выход цифрового генератора, принятого в качестве прототипа.

Цифровой генератор, выбранный в качестве прототипа, формирует на своем выходе цифровые сигналы, представляющие собой результаты накоплений текущей фазы. Эти сигналы используются при осуществлении корреляционной обработки, например, в "схемах слежения за несущей", измеряющих доплеровский сдвиг, или в "схемах слежения за задержкой", измеряющих сдвиг опорного кода относительно кода обрабатываемого сигнала [6, с. 87-90, рис.33].

Цифровой генератор, выбранный в качестве прототипа, реализует метод прямого цифрового синтеза частоты с накоплением текущей фазы. Осуществляется это следующим образом. На информационный вход накапливающего сумматора, т.е. на первый вход входящего в его состав комбинационного сумматора, с выхода регистра кода частоты поступает управляющий сигнал в виде К-разрядного числа N, которое пропорционально заданному приращению текущей фазы в каждом такте сигнала дискретизации частоты fs. Управляющий сигнал вырабатывается вычислителем, например, в процессе работы "схемы слежения за несущей" или "схемы слежения за задержкой". В накапливающем сумматоре на второй вход комбинационного сумматора с частотой fs поступает К- разрядное число, определяющее значение текущей фазы, накопленное в регистре фазы к данному такту. Результат суммирования этих чисел отсылается обратно в регистр фазы. Таким образом, на выходе накапливающего сумматора с частотой fs формируются текущие значения фазы, что геометрически интерпретируется (в системе координат "фаза - время") ступенчатой линией. Наклон этой линии определяет скорость приращения фазы и, следовательно, частоту синтезируемого сигнала. Наклон линии, а значит и частота синтезируемого сигнала может изменяться путем изменения числа N. Это весьма удобно для осуществления непосредственного управления генератором от вычислителя, например, при формировании доплеровского сдвига частоты.

Требования к числу разрядов (К) накапливающего сумматора устанавливаются исходя из требуемого дискрета установки частоты (приращения фазы), определяемого конкретными условиями корреляционной обработки сигнала. Требования к частоте дискретизации (fs) устанавливаются исходя из спектра обрабатываемого сигнала. Как показывает практика, при корреляционной обработке сигналов СРНС (ССС) цифровой генератор рассматриваемой структуры должен иметь высокочастотный (десятки мегагерц частота дискретизации) и одновременно высокоразрядный (десятки разрядов) накапливающий сумматор. Однако генераторы, использующие такие высокочастотные и одновременно высокоразрядные накапливающие сумматоры, характеризуются повышенным уровнем энергопотребления, что может представлять проблему, в частности, для портативной аппаратуры, работающей от автономного батарейного питания.

Технической задачей, на решение которой направлено заявляемое изобретение, является создание цифрового генератора, реализующего метод прямого цифрового синтеза с накоплением текущей фазы, который в заданных условиях применения для цифровых следящих систем корреляционной обработки сигналов типа сигналов СРНС (ССС) позволяет снизить уровень энергопотребления.

Задача решается за счет предложенного изменения структуры цифрового генератора, а именно за счет использования в нем двух накопительных модулей - высокочастотного накопительного модуля, работающего на заданной частоте дискретизации fs1 и использующего при этом накапливающий сумматор с уменьшенным количеством разрядов (например, меньше десяти), и низкочастотного модуля, работающего на пониженной частоте дискретизации и использующего накапливающий сумматор с количеством разрядов, определяемым из условия обеспечения заданной точности формирования частоты выходного сигнала (например, несколько десятков разрядов). Требуемая характеристика накопления текущей фазы синтезируемого сигнала обеспечивается при этом за счет суммирования значений фаз обоих накопительных модулей. Предложенная структура, основанная на использовании двух накопительных модулей - высокочастотного низкоразрядного и низкочастотного высокоразрядного, позволяет в заявляемом генераторе уменьшить энергопотребление по сравнению с генератором традиционной структуры, в котором используется один накопительный модуль - высокочастотный и одновременно высокоразрядный.

Сущность изобретения заключается в том, что в цифровой генератор для цифровых следящих систем корреляционной обработки сигналов, содержащий первый накопительный модуль, выполненный в виде последовательно соединенных регистра первого кода частоты, информационный вход которого является первым управляющим входом цифрового генератора, и накапливающего сумматора, работающего с частотой дискретизации fs1, выполненного в виде последовательно соединенных комбинационного сумматора, первый вход которого является информационным входом данного накапливающего сумматора, и регистра фазы, выход разрядов которого подключен в данном накапливающем сумматоре к второму входу комбинационного сумматора, введен второй накопительный модуль, выполненный в виде последовательно соединенных регистра второго кода частоты, информационный вход которого образует второй управляющий вход цифрового генератора, и накапливающего сумматора, работающего с частотой дискретизации fs2 = fs1/k, где k - целое число больше единицы, выполненного в виде последовательно соединенных комбинационного сумматора, первый вход которого является информационным входом этого накапливающего сумматора, и регистра фазы, выход разрядов которого подключен в этом накапливающем сумматоре к второму входу комбинационного сумматора, при этом указанные элементы первого накопительного модуля выполнены К1-разрядными, а указанные элементы второго накопительного модуля - К2-разрядными, причем К2 > K1, в цифровой генератор также введены соединенные последовательно К1-разрядные выходной комбинационный сумматор и работающий с частотой дискретизации fs1 регистр суммарной фазы, выход разрядов которого образует первый выход цифрового генератора, при этом первый вход выходного комбинационного сумматора соединен с выходом разрядов регистра фазы накапливающего сумматора первого накопительного модуля, а второй вход - с выходом K1 старших разрядов регистра фазы накапливающего сумматора второго накопительного модуля, в котором выход М младших разрядов регистра фазы, где М = К2 - K1, образует второй выход цифрового генератора.

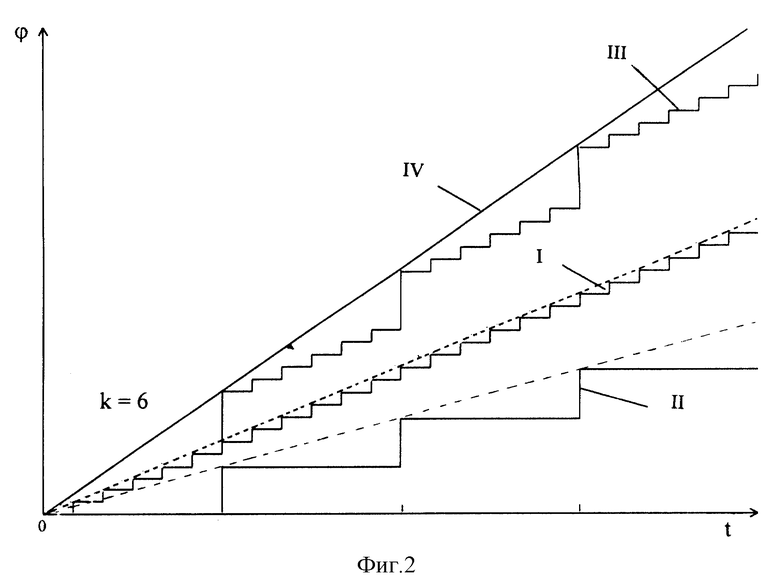

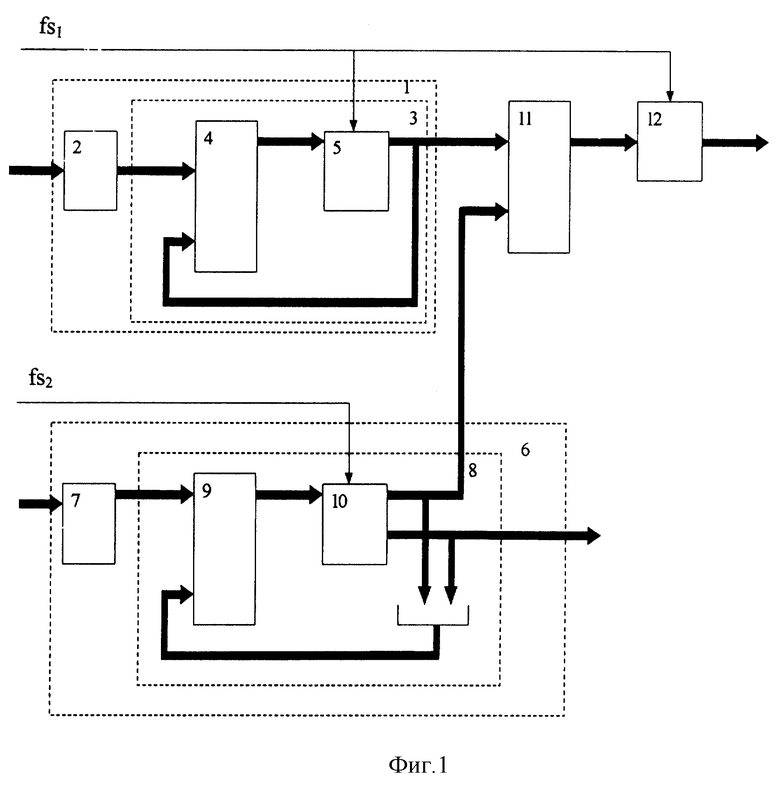

Сущность изобретения, его реализуемость и возможность промышленного применения поясняются представленной на фиг.1 структурной схемой заявляемого цифрового генератора, а также представленными на фиг.2 графиками, иллюстрирующими процессы формирования значений фаз в заявляемом генераторе.

Заявляемый цифровой генератор для цифровых следящих систем корреляционной обработки сигналов содержит, см. фиг 1, первый накопительный модуль 1, выполненный в виде последовательно соединенных регистра 2 первого кода частоты, информационный вход которого является первым управляющим входом цифрового генератора, и накапливающего сумматора 3, работающего с частотой дискретизации fs1, выполненного в виде последовательно соединенных комбинационного сумматора 4, первый вход которого является информационным входом накапливающего сумматора 3, и регистра фазы 5, выход разрядов которого подключен в накапливающем сумматоре 3 к второму входу комбинационного сумматора 4.

Заявляемый цифровой генератор содержит также второй накопительный модуль 6, выполненный в виде последовательно соединенных регистра 7 второго кода частоты, информационный вход которого образует второй управляющий вход цифрового генератора, и накапливающего сумматора 8, работающего с частотой дискретизации fs2, выполненного в виде последовательно соединенных комбинационного сумматора 9, первый вход которого является информационным входом накапливающего сумматора 8, и регистра фазы 10, выход разрядов которого подключен в накапливающем сумматоре 8 к второму входу комбинационного сумматора 9.

Элементы первого накопительного модуля 1 (регистр 2 первого кода частоты, комбинационный сумматор 4, регистр фазы 5) выполнены K1-разрядными, а элементы второго накопительного модуля 6 (регистр 7 второго кода частоты, комбинационный сумматор 9, регистр фазы 10) выполнены К2-разрядными, причем К2 > K1. Например, при реализации цифрового генератора несущей значения K1 и К2 могут быть выбраны в соотношении К2 = 25, K1 = 5, а в случае реализации генератора кода - в соотношении К2 = 23. K1= 2.

Частота дискретизации fs2 связана с частотой дискретизации fs1 выражением fs2 = fs1/k, где k - целое число больше единицы. Например, для случая, представленного на фиг. 2, k = 6, для случая рассматриваемого ниже примера оценки энергопотребления k = 8.

Исходя из указанных разрядностей и частот дискретизации первый накопительный модуль 1 можно условно охарактеризовать как высокочастотный низкоразрядный модуль, а второй накопительный модуль 6 - как низкочастотный высокоразрядный модуль.

Заявляемый цифровой генератор содержит также соединенные последовательно К1-разрядные выходной комбинационный сумматор 11 и регистр суммарной фазы 12, работающий с частотой дискретизации fs1.

Первый и второй входы выходного комбинационного сумматора 11 соединены соответственно с выходом K1 разрядов регистра фазы 5 накапливающего сумматора 3 первого накопительного модуля 1 и с выходом K1 старших разрядов регистра фазы 10 накапливающего сумматора 8 второго накопительного модуля 6.

Выход K1 разрядов регистра суммарной фазы 12 образует первый выход заявляемого цифрового генератора, а выход М = К2 - K1 младших разрядов регистра фазы 10 накапливающего сумматора 8 второго накопительного модуля 6 образует второй выход заявляемого цифрового генератора.

В заявляемом цифровом генераторе первый сигнал дискретизации частоты fs1 поступает на тактовый вход регистра фазы 5 накапливающего сумматора 3 первого накопительного модуля 1, а также на тактовый вход регистра суммарной фазы 12. Второй сигнал дискретизации частоты fs2 поступает на тактовый вход регистра фазы 10 накапливающего сумматора 8 второго накопительного модуля 6. Первый и второй сигналы дискретизации синхронны, что обеспечивается формированием второго сигнала дискретизации из первого путем деления частоты fs1 в k раз.

В практических схемах регистр 2 первого кода частоты и регистр 7 второго кода частоты помимо информационных входов имеют также входы записи (на фиг. 1 не показаны), по которым осуществляется запись входных данных в эти регистры. Также в практических схемах регистры 2, 5, 7, 10, 12 могут иметь входы обнуления (на фиг.1 не показаны), на которые в начальный момент работы может подаваться обнуляющий сигнал, устанавливающий регистры в начальное (нулевое) состояние. Вопросы записи данных и обнуления регистров в рамках настоящей заявки не рассматриваются как общеизвестные и не относящиеся к сущности заявляемого изобретения.

Элементы, входящие в состав заявляемого цифрового генератора, являются известными элементами цифровой техники. Общая структура накапливающих сумматоров 3, 8 известна, например, из [3, с. 50-51, рис.2.13], Комбинационные сумматоры 4, 9, 11 могут быть выполнены по схеме комбинационного сумматора с последовательным переносом, описанной, например, в [7, с. 523-536, рис.6.96, 6.97] , что является предпочтительным с точки зрения уменьшения энергопотребления, или по схеме комбинационного сумматора с параллельным переносом, описанной, например, в [7, с.523-536, рис.6.100]. Регистры 2, 5, 7, 10, 12 могут быть выполнены в виде регистров памяти на основе триггеров (например, D-триггеров), обеспечивающих запись, хранение и считывание данных в параллельном двоичном коде, см., например [7, с.348-354, рис.5.85].

Заявляемый цифровой генератор работает следующим образом.

На первый управляющий вход заявляемого цифрового генератора поступает K1-разрядное число N1, пропорциональное заданному приращению Δϕ1 текущей фазы в накапливающем сумматоре 3 первого (высокочастотного низкоразрядного) накопительного модуля 1 в каждом такте сигнала дискретизации частоты fs1. Число N1 устанавливается вычислителем (на фиг.1 не показан), например, исходя из условий функционирования "схемы слежения за несущей" или "схемы слежения за задержкой". Число N1 поступает в виде цифрового сигнала на информационный вход регистра 2 первого кода частоты, где записывается по соответствующему сигналу записи. С выхода регистра 2 число N1 поступает на первый вход комбинационного сумматора 4. На второй вход комбинационного сумматора 4 с частотой fs1 поступает К1-разрядное число, определяющее значение текущей фазы, накопленное в регистре фазы 5 к данному такту. Результат суммирования этих чисел отсылается обратно в регистр фазы 5. Таким образом, на выходе накапливающего сумматора 3 с частотой fs1 формируются (в цифровом виде) текущие значения фазы ϕ1, что геометрически интерпретируется (в системе координат "фаза - время") ступенчатой функцией, представленной на фиг.2 кривой "I". Наклон кривой "I" определяет скорость приращения фазы и, следовательно, частоту f1 сигнала, синтезируемого накопительным модулем 1. Этот наклон, а значит и частота f1 может изменяться путем изменения числа N1. Значение фазы ϕ1, снимаемое с частотой fs1 с выхода регистра фазы 5 накапливающего сумматора 3 высокочастотного низкоразрядного накопительного модуля 1 (фиг.2, кривая "I"), поступает на первый вход выходного комбинационного сумматора 11.

На второй управляющий вход заявляемого цифрового генератора поступает К2-разрядное число N2, пропорциональное заданному приращению Δϕ2 текущей фазы в накапливающем сумматоре 8 второго (низкочастотного высокоразрядного) накопительного модуля 6 в каждом такте сигнала дискретизации частоты fs2. Число N2 устанавливается вычислителем (на фиг. 1 не показан) в соответствии с числом N1 исходя из условий функционирования "схемы слежения за несущей" или "схемы слежения за задержкой". Число N2 поступает в виде цифрового сигнала на информационный вход регистра 7 второго кода частоты, где записывается по соответствующему сигналу записи. С выхода регистра 7 число N2 поступает на первый вход комбинационного сумматора 9. На второй вход комбинационного сумматора 9 с частотой fs2 поступает К2-разрядное число, определяющее значение текущей фазы, накопленное в регистре фазы 10 к данному такту. Результат суммирования этих чисел отсылается обратно в регистр фазы 10. Таким образом, на выходе накапливающего сумматора 8 с частотой fs2 формируются (в цифровом виде) текущие значения фазы ϕ2, что геометрически интерпретируется (в системе координат "фаза - время") ступенчатой функцией, представленной на фиг. 2 кривой "II". Наклон кривой "II" определяет скорость приращения фазы и, следовательно, частоту fs сигнала, синтезируемого накопительным модулем 6. Этот наклон, а значит и частота f2 может изменяться при изменении числа N2.

Значение фазы ϕ2 (с точностью до K1 старших разрядов), снимаемое с выхода K1 старших разрядов регистра фазы 10 накапливающего сумматора 8 низкочастотного высокоразрядного накопительного модуля 6 (фиг.2, кривая "II"), поступает с частотой fs2 на второй вход выходного комбинационного сумматора 11, где складывается со значением фазы ϕ1, поступающим с частотой fs1 с выхода регистра фазы 5 накапливающего сумматора 3 высокочастотного низкоразрядного накопительного модуля 1 (фиг.2, ступенчатая кривая "I").

Результат суммирования фаз ϕ1+ ϕ2 = ϕΣ представлен на фиг.2 ступенчатой кривой "III". Этот результат записывается в регистр суммарной фазы 12, откуда с частотой fs1 поступает на первый выход заявляемого генератора.

Наклон ступенчатой кривой "III" определяет скорость приращения суммарной фазы ϕΣ и, следовательно, частоту fΣ сигнала, синтезируемого заявляемым генератором. Этот наклон, а значит и частота fΣ, изменяется при изменении любой из составляющих частей - кривых "I" и/или "II".

Сформированный таким образом на первом выходе заявляемого генератора цифровой сигнал в виде значений суммарной фазы ϕΣ далее может быть преобразован в аналоговый сигнал с помощью преобразователя кода, реализующего, например, таблицу синусов (косинусов) и выполненного на базе постоянного запоминающего устройства (ПЗУ), см., например [3, с.75-76, рис.3.12 ]. Для повышения точности такого преобразования, при необходимости, может использоваться сигнал, снимаемый с второго выхода генератора, т.е. с выхода М = К2 - K1 младших разрядов регистра фазы 10 накапливающего сумматора 8 второго накопительного модуля 6.

Из сравнения эталонной характеристики (фиг.2, прямая "IV") и реально получаемой характеристики (фиг.2, ступенчатая кривая "III") видно, что формируемые заявляемым генератором значения суммарной фазы ϕΣ, снимаемые с первого выхода заявляемого генератора, совпадают с эталонными значениями в моменты, соответствующие тактам сигнала дискретизации частоты fs2. В остальные моменты формируемые значения суммарной фазы отличаются от эталонных, причем это отличие носит систематический характер. Эта систематическая погрешность однозначно определяется соотношениями фаз первого и второго сигналов дискретизации, следовательно, легко может быть вычислена и затем учтена при работе цифровых следящим систем корреляционной обработки сигналов. В частности, учет систематической погрешности производится при осуществлении абсолютных фазовых измерений. В случаях, когда абсолютные фазовые измерения не осуществляются, сформированные заявляемым цифровым генератором значения суммарной фазы применяются без коррекции систематической погрешности.

Особенностью заявляемого генератора, в котором формирование выходных значений фазы ϕΣ осуществляется путем суммирования двух составляющих (высокочастотной ϕ1 и низкочастотной ϕ2), является очевидное ограничение, накладываемое на величину каждой из составляющих. Суть этого ограничения состоит в том, что для обеспечения однозначности в пределах фазовых циклов формируемых значений фазы ϕΣ, приращение суммарной фазы на каждом такте дискретизации не должно быть меньше нуля и больше 180o (π).С учетом этого ограничения выбираются конкретные соотношения между разрядностями K1, К2 накопительных сумматоров 3, 8 и величинами записываемых в них чисел N1, N2, а также выбирается нужная цикличность работы (периоды переполнения) накапливающих сумматоров 3, 8.

Таким образом, заявляемый цифровой генератор синтезирует выходной сигнал в виде цифровых значений суммарной фазы, формируемой с помощью двух накопительных модулей (высокочастотного низкоразрядного и низкочастотного высокоразрядного). Такое решение позволяет уменьшить потребляемую мощность по сравнению с генератором, выполненным традиционным образом с использованием одного (высокочастотного высокоразрядного) накопительного модуля.

Оценим возможный выигрыш по потребляемой мощности предлагаемого цифрового генератора по сравнению с генератором традиционной структуры на примере реализации цифрового генератора С/А кода сигналов СРНС GPS. Из условий осуществления корреляционной обработки примем, что генератор должен сформировать частоту в пять раз большую, чем частота С/А кода GPS (1,023 МГц), т.е. частоту Fr = 5 х 1,023 МГц = 5,115 МГц = (5 + 0,115) МГц. При этом требуемая частота дискретизации должна составлять fs1 = 20 МГц, а требуемый дискрет установки частоты - Δf = 1 Гц.

С учетом этих условий необходимая разрядность К генератора традиционной структуры, определяемая из формулы Δf = fs1/2K, составляет величину К = 25.

Заявляемый генератор в рассматриваемом случае выполняется следующим образом: накапливающий сумматор 3 высокочастотного низкоразрядного накопительного модуля 1 выполняется 2-разрядным (K1 = 2), работает с частой дискретизации fs1 = 20 МГц и синтезирует частоту f1 = 5МГц; накапливающий сумматор 8 низкочастотного высокоразрядного накопительного модуля 8 выполняется 23-разрядным (К2 = 23), работает с частотой дискретизации fs2 = fs1/8 = 2,5 МГц и синтезирует частоту f2 = 0,115 МГц.

Приблизительно энергопотребление (Р) цифрового генератора можно оценить с помощью эмпирической формулы

Р = Pg x Kg x F,

где Pg - потребление на один стандартный элемент (зависит от технологии);

Kg - число стандартных элементов, определяемое разрядностью;

F - частота работы, МГц.

В рассматриваемом случае как для традиционного, так и для заявляемого генераторов потребление на один стандартный элемент (Pg) при использовании одинаковой элементной базы является одним и тем же, что позволяет не учитывать его при сравнительной оценке энергопотребления генераторов.

С учетом этого упрощения потребление традиционного генератора (Р0) можно охарактеризовать как

Р0 = F х Kg = fs1 x (Ks0 +Kr0),

где Ks0 - разрядность комбинационного сумматора;

Кr0 - разрядность регистра фазы.

Потребление заявляемого генератора (Pi) оценивается как

P1 = F x Kg = fs1 x (Ks1 +Kr1) x 2 + fs2 x (Ks2 + Kr2),

где Ks1 - разрядность высокочастотных комбинационных сумматоров 4, 11;

Кr1 - разрядность высокочастотных регистров 5, 12;

Ks2 - разрядность низкочастотного комбинационного сумматора 9;

Kr2 - разрядность низкочастотного регистра фазы 10.

Примем, что потребление, приходящееся на один разряд сумматора и регистра фазы, реализованных, например, с использованием D-триггеров, примерно одинаково [8]. С учетом этого допущения потребление традиционного генератора (Р0) и потребление заявляемого генератора (P1) для целей сравнительной оценки можно записать следующим образом:

Р0 = fs1 x (Ks0 +Kr0) = fs1 х К х 2 = 20 х 25 х 2 = 1000;

P1 = fs1 x (Ks1 +Kr1) x 2 + fs2 x (Ks2 + Kr2) = fs1 x K1 x 4 + fs2 x K2 x 2 = =20 х 2 х 4 + 2,5 х 23 x 2 = 275.

Сравнивая значения P0 и P1 видно, что выигрыш по потребляемой мощности у предлагаемого цифрового генератора по сравнению с генератором традиционной структуры в условиях данного примера составляет более 3,6 раз. Реально выигрыш по потребляемой мощности выше, поскольку в генераторе традиционной структуры высокочастотный высокоразрядный комбинационный сумматор должен содержать дополнительные цепи параллельных переносов, не учитываемые в рассмотренном примере, что приводит к увеличению объема данного сумматора и, соответственно, потребляемой им мощности в несколько раз. Для заявляемого генератора таких цепей нет, поскольку комбинационный сумматор 4 первого накопительного модуля 1 имеет мало разрядов, а комбинационный сумматор 9 второго накопительного модуля 6 работает на достаточно низкой частоте, которая позволяет применение сумматоров с последовательным переносом.

Из рассмотренного видно, что заявляемый цифровой генератор для цифровых следящих систем корреляционной обработки сигналов, реализующий метод прямого цифрового синтеза с накоплением текущей фазы, технически осуществим, промышленно реализуем и решает поставленную техническую задачу по снижению уровня энергопотребления. Указанные положительные особенности заявляемого цифрового генератора обуславливают перспективы по его использованию, например, в портативной многоканальной аппаратуре потребителей сигналов СРНС (ССС), в том числе работающей от батарейного питания.

Источники информации

1. Варакин Л. Е. Системы связи с щумоподобными сигналами. М., Радио и связь, 1985.

2. Волынкин А.И, Кудрявцев И.В., Мищенко И.Н., Шебшаевич B.C. Аппаратура подтребителей СРНС "Настар", часть I, II. Зарубежная радиоэлектроника, 1983, 4, 1983, с.70-91, 5, с.59-83.

3. Цифровые радиоприемные системы: Справочник /М.И, Жодзишский, Р.Б. Мазепа, Е.П. Овсянников и др. / Под ред. М.И. Жодзишского, М., Радио и связь, 1990.

4. Патент РФ 2090902 (С1), кл. G 01 S 5/14, опубл.20.09.97.

5. Патент РФ 2146378 (С1), кл. G 01 S 5/14, опубл. 10.04.2000.

6. Бортовые устройства спутниковой радионавигации / И.В. Кудрявцев, И.Н. Мищенко, А.И. Волынкин и др.; под ред. B.C. Шебшаевича. М., Транспорт, 1988.

7. Г. И. Пухальский, Т Я. Новосельцева. Цифровые устройства. - Политехника. Санкт-Петербург, 1996.

8. Каталог элементов фирмы "Самсунг" - "STD 80/STDM80 0.5 m 5V/3.3V Standard Cell Library Data Book, 1996, Samsung Electronics Co., Ltd."о

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2000 |

|

RU2178894C1 |

| РАДИОЭЛЕКТРОННЫЙ БЛОК | 2001 |

|

RU2194375C1 |

| РАДИОЭЛЕКТРОННЫЙ БЛОК | 2001 |

|

RU2188522C1 |

| РАДИОЭЛЕКТРОННЫЙ БЛОК | 2001 |

|

RU2199839C1 |

| РАДИОЭЛЕКТРОННЫЙ БЛОК | 2001 |

|

RU2192108C1 |

| БЛОК ПРИЕМНИКА СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2001 |

|

RU2190941C1 |

| РАДИОЭЛЕКТРОННЫЙ БЛОК | 2000 |

|

RU2175821C1 |

| БАЗОВЫЙ КОНСТРУКТИВНЫЙ БЛОК ДЛЯ РАДИОЭЛЕКТРОННЫХ ПРИБОРОВ | 2000 |

|

RU2173037C1 |

| РАДИОЭЛЕКТРОННЫЙ БЛОК | 2000 |

|

RU2172080C1 |

| РАДИОЭЛЕКТРОННЫЙ БЛОК | 2000 |

|

RU2172081C1 |

Изобретение относится к радиоэлектронике, а конкретно к цифровым генераторам, предназначенным для использования в цифровых следящих системах корреляционной обработки сигналов, преимущественно сигналов спутниковых радионавигационных систем или спутниковых систем связи. Техническим результатом является снижение уровня энергопотребления. Устройство содержит регистр частоты, два комбинационных сумматора и два регистра фазы, выполненные низкоразрядными и работающие с высокой частотой дискретизации, и регистр кода частоты, сумматор и регистр фазы, выполненные высокоразрядными и работающие с низкой частотой дискретизации. 2 ил.

Цифровой генератор для цифровых следящих систем корреляционной обработки сигналов, содержащий первый накопительный модуль, выполненный в виде последовательно соединенных регистра первого кода частоты, информационный вход которого является первым управляющим входом цифрового генератора, и накапливающего сумматора, работающего с частотой дискретизации fs1, выполненного в виде последовательно соединенных комбинационного сумматора, первый вход которого является информационным входом данного накапливающего сумматора, и регистра фазы, выход разрядов которого подключен в данном накапливающем сумматоре к второму входу комбинационного сумматора, отличающийся тем, что введен второй накопительный модуль, выполненный в виде последовательно соединенных регистра второго кода частоты, информационный вход которого образует второй управляющий вход цифрового генератора, и накапливающего сумматора, работающего с частотой дискретизации fs2 = fs1/k, где k - целое число больше единицы, выполненного в виде последовательно соединенных комбинационного сумматора, первый вход которого является информационным входом этого накапливающего сумматора, и регистра фазы, выход разрядов которого подключен в этом накапливающем сумматоре к второму входу комбинационного сумматора, при этом указанные элементы первого накопительного модуля выполнены К1-разрядными, а указанные элементы второго накопительного модуля - К2-разрядными, причем K2>K1, в цифровой генератор также введены соединенные последовательно К1-разрядные выходной комбинационный сумматор и работающий с частотой дискретизации fs1 регистр суммарной фазы, выход разрядов которого образует первый выход цифрового генератора, при этом первый вход выходного комбинационного сумматора соединен с выходом разрядов регистра фазы накапливающего сумматора первого накопительного модуля, а второй вход - с выходом K1 старших разрядов регистра фазы накапливающего сумматора второго накопительного модуля, в котором выход М младших разрядов регистра фазы, где М = К2-K1, образует второй выход цифрового генератора.

| Бортовые устройства спутниковой радионавигации | |||

| / Под ред | |||

| В.С.ШЕБШАЕВИЧА | |||

| - М.: Транспорт, 1988, с | |||

| Пожарный двухцилиндровый насос | 0 |

|

SU90A1 |

| ЦИФРОВОЙ ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ | 1995 |

|

RU2090902C1 |

| ИНТЕГРИРОВАННЫЙ ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1999 |

|

RU2146378C1 |

| Способ фиксации зеленого чайного листа | 1973 |

|

SU460862A1 |

| US 4410954 A, 18.10.1983 | |||

| US 5084681 A, 28.01.1992 | |||

| US 5399984 A, 21.03.1995. | |||

Авторы

Даты

2002-02-27—Публикация

2000-09-25—Подача