Изобретение относится к технической кибернетике и может быть использовано в системах управления объектами с запаздыванием по состоянию нейтрального типа, причем параметры объекта - неизвестные постоянные или медленно меняющиеся во времени величины.

Наиболее близким техническим решением к предлагаемому является адаптивная система управления /1/, содержащая первый блок задания коэффициентов, блок запаздывания, второй блок задания коэффициентов, первый блок суммирования, первый умножитель, первый интегратор, второй умножитель, второй блок суммирования, третий умножитель, второй интегратор, четвертый умножитель, третий блок суммирования, объект регулирования, выходы которого связаны с соответствующими входами первого блока задания коэффициентов и соответствующими входами блока запаздывания, выходы первого блока задания коэффициентов подключены к соответствующим входам первого блока суммирования, выход которого соединен с первым и вторым входами первого умножителя, входом второго умножителя, входом третьего умножителя, выход первого умножителя связан с входом первого интегратора, выход которого подключен ко второму входу второго умножителя, выходы блока запаздывания соединены с соответствующими входами второго блока задания коэффициентов, выходы которого связаны с соответствующими входами второго блока суммирования, выход которого подключен ко второму входу третьего умножителя и к входу четвертого умножителя, выход третьего умножителя соединен с входом второго интегратора, выход которого связан с вторым входом четвертого умножителя, выход которого подключен ко второму входу третьего блока суммирования, второй вход которого связан с выходом второго умножителя, а выход подключен ко входу объекта регулирования.

Недостатком этой системы являются, во-первых, узкие функциональные возможности системы, так как система не может работать с объектами, обладающими запаздыванием нейтрального типа, и, во-вторых, необходимость выбора элементов числового вектора настройки параметров регулятора в условиях априорной неопределенности, как правило, представляет собой сложную задачу. В такой ситуации выбор целесообразнее заменить специальной настройкой параметров регулятора, что является в ряде случаев единственно возможным подходом к построению систем управления, устойчиво работоспособных в условиях априорной неопределенности.

Целью изобретения является расширение функциональных возможностей системы.

Поставленная цель достигается тем, что, вводя в систему второй блок запаздывания, первые умножители, первые блоки вычисления модуля, первые интеграторы, вторые умножители, третьи умножители, вторые блоки вычисления модуля, вторые интеграторы, четвертые умножители, четвертый блок суммирования, блок дифференцирования, получают в системе новую функцию, которая заключается в том, что теперь система может работать с объектами, обладающими запаздыванием нейтрального типа, и элементы числового вектора настройки параметров регулятора будут настраиваться, что обеспечивает условие нормального функционирования системы.

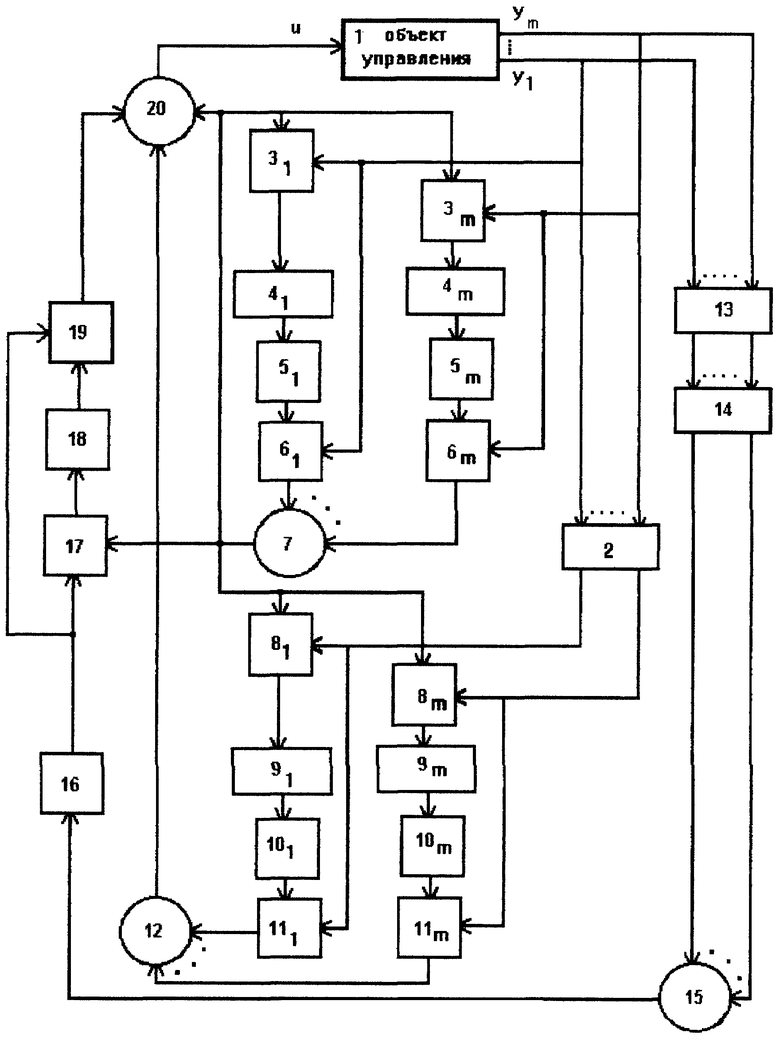

На чертеже представлена блок-схема предлагаемой системы управления.

Система содержит объект управления 1, первый блок запаздывания 2, первые умножители 3i (i= 1, m), первые блоки вычисления модуля 4i (i=1,m), первые интеграторы 5i (i=1,m), вторые умножители 6i (i=1,m), первый блок суммирования 7, третьи умножители 8i (i=1,m), вторые блоки вычисления модуля 9i (i=1, m), вторые интеграторы 10i (i=1,m), четвертые умножители 11i (i=1,m), второй блок суммирования 12, второй блок запаздывания 13, блок задания коэффициентов 14, третий блок суммирования 15, блок дифференцирования 16, пятый умножитель 17, третий интегратор 18, шестой умножитель 19, четвертый блок суммирования 20.

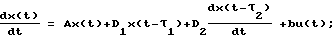

Динамика процессов в объекте управления описывается уравнениями состояния и выхода

y(t)=LTx(t),

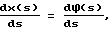

x(s) = ϕ(s),

s∈{-τ,0},

τ = max{τ1,τ2},

где x - n-мерный вектор состояния;

y - m-мерный вектор выходных измеряемых координат;

u - скалярное управляющее воздействие;

ϕ(s) - начальная вектор-функция;

τ1>0, τ2>0 - постоянные запаздывания;

A, D1, D2, L, b - матрицы и вектор размерностей (n•n), (n•n), (n•n), (m•n), (n•1) соответственно, зависящие от вектора неизвестных параметров ξ∈Θ где Θ - известное множество возможных значений вектора ξ.

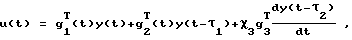

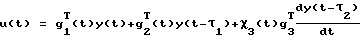

К объекту подключен регулятор

где g1,g2,χ3 - настраиваемые параметры регулятора, векторы и скаляр соответственно;

g3 - числовой вектор.

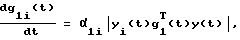

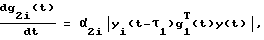

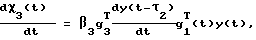

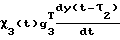

Параметры регулятора настраиваются в соответствии с алгоритмами адаптации

α1i,α2i,β3 = const>0,

Выходы объекта управления 1 связаны с соответствующими входами первых 3i (i= 1, m) и вторых 6i умножителей и с соответствующими входами первого блока запаздывания 2 и второго блока запаздывания 13, выход каждого первого умножителя 3i через последовательно соединенные соответствующие первые блоки вычисления модуля 4i и первые 5i интеграторы соединены с входом соответствующего второго умножителя 6i, выходы вторых умножителей 6i подключены к входам первого блока суммирования 7, выход которого подключен ко вторым входам первых умножителей 3i (i=1,m), ко вторым входам третьих 8i умножителей, ко второму входу пятого умножителя 17 и к первому входу четвертого блока суммирования 20, первые входы каждого третьего умножителя 8i соединены с выходами первого блока 2 запаздывания, выходы каждого третьего 8i умножителя соединены со входами соответствующих вторых блоков вычисления модуля 9i (i= 1, m), выходы которых связаны с соответствующими входами вторых интеграторов 10i (i= 1, m), выходы которых соединены со входами каждого соответствующего четвертого умножителя 11i (i= 1,m), вторые входы четвертых умножителей 11i связаны с выходами первого блока 2 запаздывания, выходы четвертых умножителей 11i соединены с входами второго блока суммирования 12, выход которого соединен со вторым входом четвертого блока суммирования 20, вход третьего блока суммирования 15 соединен с выходом блока задания коэффициентов 14, входы блока задания коэффициентов 14 соединены с выходами второго блока 13 запаздывания, выход третьего блока суммирования 15 связан с входом блока 16 дифференцирования, выход которого соединен со вторым входом шестого умножителя 19 и первым входом пятого умножителя 17, выход пятого умножителя 17 через последовательно соединенные третий интегратор 18 и шестой умножитель 19 связан с третьим входом четвертого блока суммирования 20, выход которого соединен с входом объекта 1 управления.

Система функционирует следующим образом.

Сигналы с выходов объекта управления 1 поступают одновременно на соответствующие входы первого блока запаздывания 2 и второго блока запаздывания 13. Сигнал с выхода первого блока суммирования 7 поступает на вторые входы каждого первого умножителя 3i (i=1,m). На первые входы каждого первого умножителя 3i поступают соответствующие сигналы у, с выхода объекта управления 1. С выходов каждого первого 3i умножителя сигналы g1ууi поступают на входы соответствующих первых блоков вычисления модуля 4i (i=1,m), где вычисляются их абсолютные значения. С выходов первых блоков вычисления модуля 4i сигналы |g1yyi| поступают на соответствующие входы первых интеграторов 5i (i=1,m), где интегрируются. Сигналы g1i с выходов первых интеграторов поступают на первые входы каждого соответствующего второго умножителя 6i (i=1,m). На вторые входы вторых умножителей 6i поступают соответствующие сигналы yi с выходов объекта управления 1. С выходов вторых умножителей 6i сигналы поступают на входы первого блока суммирования 7, где складываются между собой. Сигнал с выхода первого блока суммирования 7 g1y поступает на вторые входы каждого третьего умножителя 8i (i=1,m), на второй вход пятого умножителя 17 и на первый вход четвертого блока суммирования 20. В первом блоке 2 запаздывания происходит задержка сигнала yi на время τ1. На первые входы каждого третьего умножителя 8i поступают соответствующие сигналы yi(t-τ1) с выходов первого блока 2 запаздывания. С выходов каждого третьего 8i умножителя сигналы g1(t)y(t)yi(t-τ1) поступают на соответствующие входы вторых блоков вычисления модуля 9i (i= 1, m), где вычисляются их абсолютные значения. С выходов вторых блоков вычисления модуля 9i сигналы |g1(t)y(t)yi(t-τ1| поступают на соответствующие входы вторых интеграторов 10i (i=1,m). Сигналы g2i с выходов вторых интеграторов 10i поступают на первые входы каждого четвертого умножителя 11i (i=1,m). На вторые входы четвертых умножителей 11i поступают соответствующие сигналы yi(t-τ1) с выходов первого блока 2 запаздывания. С выходов четвертых умножителей 11i сигналы поступают на входы второго блока суммирования 12, где складываются между собой. Сигнал с выхода второго блока суммирования 12 g2(t)y(t-τ1) поступает на второй вход четвертого блока суммирования 20. Во втором блоке 13 запаздывания происходит задержка сигнала yi на время τ2. Сигналы yi(t-τ2) с выхода второго блока 13 запаздывания поступают на соответствующие входы блока 14 задания коэффициентов, где происходит умножение сигнала yi(t-τ2) на коэффициент g3i. Сигналы g3iyi(t-τ2) с выходов блока 14 задания коэффициентов поступают на соответствующие входы третьего блока суммирования 15, где складываются. Сигнал g3y(t-τ2) с выхода третьего блока суммирования 15 поступает на вход блока 16 дифференцирования, где дифференцируется. Сигнал  с выхода блока 16 дифференцирования поступает на второй вход шестого умножителя 19 и на первый вход пятого умножителя 17. Сигнал

с выхода блока 16 дифференцирования поступает на второй вход шестого умножителя 19 и на первый вход пятого умножителя 17. Сигнал  с выхода пятого умножителя 17 поступает на вход третьего интегратора 18, где интегрируется. Сигнал с выхода третьего интегратора 18 поступает на первый вход шестого умножителя 19, где умножается на сигнал с выхода блока 16 дифференцирования. Сигнал

с выхода пятого умножителя 17 поступает на вход третьего интегратора 18, где интегрируется. Сигнал с выхода третьего интегратора 18 поступает на первый вход шестого умножителя 19, где умножается на сигнал с выхода блока 16 дифференцирования. Сигнал  с выхода шестого умножителя 19 поступает на третий вход четвертого блока суммирования 20. В четвертом блоке суммирования 20 происходит сложение всех сигналов, поступающих на входы этого блока. Сигнал (сигнал управления)

с выхода шестого умножителя 19 поступает на третий вход четвертого блока суммирования 20. В четвертом блоке суммирования 20 происходит сложение всех сигналов, поступающих на входы этого блока. Сигнал (сигнал управления)  c выхода четвертого блока суммирования 20 поступает на вход объекта 1 управления. Данное устройство может быть реализовано промышленным способом на основе стандартной элементной базы.

c выхода четвертого блока суммирования 20 поступает на вход объекта 1 управления. Данное устройство может быть реализовано промышленным способом на основе стандартной элементной базы.

ИСТОЧНИК ИНФОРМАЦИИ

1. Авторское свидетельство СССР 1105860, кл.G 05 B 13/02, 1984 (прототип).

Изобретение относится к технической кибернетике и может быть использовано в системах управления объектами с запаздыванием по состоянию нейтрального типа. Технический результат заключается в расширении функциональных возможностей системы. Устройство содержит объект управления, блок задания коэффициентов, второй блок запаздывания, третий блок суммирования, четвертый блок суммирования, пятый умножитель, третий интегратор, шестой умножитель, первый блок запаздывания, первые умножители, первые блоки вычисления модуля, первые интеграторы, вторые умножители, третьи умножители, вторые блоки вычисления модуля, вторые интеграторы, четвертые умножители, первый блок суммирования, второй блок суммирования, блок дифференцирования. 1 ил.

Адаптивная система управления для объектов с запаздыванием нейтрального типа, содержащая объект управления, блок задания коэффициентов, второй блок запаздывания, выходы объекта управления соединены с соответствующими входами второго блока запаздывания, выходы второго блока запаздывания соединены с входами блока задания коэффициентов, третий блок суммирования, четвертый блок суммирования, входы третьего блока суммирования соединены с соответствующими выходами блока задания коэффициентов, пятый умножитель, выход пятого умножителя через третий интегратор связан с первым входом шестого умножителя, выход которого подключен к третьему входу четвертого блока суммирования, выход которого подключен к входу объекта управления, отличающаяся тем, что в систему введены первый блок запаздывания, первые умножители, первые блоки вычисления модуля, первые интеграторы, вторые умножители, третьи умножители, вторые блоки вычисления модуля, вторые интеграторы, четвертые умножители, первый блок суммирования, второй блок суммирования, блок дифференцирования, выходы объекта управления соединены с соответствующими входами первых и вторых умножителей и с соответствующими входами первого блока запаздывания, выход каждого первого умножителя через последовательно соединенные соответствующие первые блоки вычисления модуля и первые интеграторы соединен с соответствующими входами вторых умножителей, выходы вторых умножителей подключены к входам первого блока суммирования, выход которого подключен ко вторым входам первых умножителей, ко вторым входам третьих умножителей, ко второму входу пятого умножителя и к первому входу четвертого блока суммирования, выходы первого блока запаздывания соединены с соответствующими входами третьих и четвертых умножителей, выход каждого третьего умножителя через последовательно соединенные соответствующие вторые блоки вычисления модуля и вторые интеграторы соединен с соответствующим входом четвертого умножителя, выходы четвертых умножителей подключены к входам второго блока суммирования, выход которого подключен к второму входу четвертого блока суммирования, вход блока дифференцирования соединен с выходом третьего блока суммирования, выход блока дифференцирования соединен с вторым входом шестого умножителя и первым входом пятого умножителя.

| Самонастраивающаяся система управления | 1982 |

|

SU1105860A1 |

| АДАПТИВНАЯ СИСТЕМА УПРАВЛЕНИЯ ДЛЯ ОБЪЕКТОВ С ЗАПАЗДЫВАНИЕМ | 1998 |

|

RU2130636C1 |

| СПОСОБ ИЗМЕРЕНИЯ ПЛОТНОСТИ ЭЛЕКТРИЧЕСКОГО ТОКА В ЭЛЕКТРОЛИТИЧЕСКОЙ ЯЧЕЙКЕ | 0 |

|

SU180669A1 |

| WO 9712300 A1, 03.04.1997. | |||

Авторы

Даты

2002-05-10—Публикация

2000-06-13—Подача