Изобретение относится к области информационно-измерительной и вычислительной техники и предназначено для подсчета выбросов или провалов напряжения, длительность превышения которыми различных уровней анализа больше заданных критических значений, также определения суммарного времени отказов электрооборудования при нестационарном напряжении в электрических сетях.

Известен детектор колебаний напряжения [1], содержащий входной преобразователь переменного напряжения в постоянное, к выходу которого подключен самопишущий прибор или шлейфовый осциллограф.

Недостатками аналога являются большие затраты средств на носитель регистрации изменений напряжения, а также значительная трудоемкость и большие затраты времени на обработку регистрограмм.

Наиболее близким техническим решением к предлагаемому является регистратор импульсных помех [2], содержащий преобразователь переменного напряжения в постоянное, информационный ключ, время-амплитудный пребразователь, два амплитудно-временных преобразователя, два аналого-цифровых преобразователя, регистр счетчиков, электронные часы, триггер, три элемента задержки, три кнопки управления, цифро-печатающую машину (перфоратор).

Недостатками прототипа являются громоздкость, низкое быстродействие, значительная трудоемкость и большие затраты времени на обработку перфолент, а также невозможность определения суммарного времени отказов электрооборудования.

Технические задачи, решаемые изобретением - упрощение счетчика, повышение удобства эксплуатации и расширение функциональных возможностей.

Указанные технические задачи решаются благодаря тому, что в регистратор импульсных помех, содержащий преобразователь переменного напряжения в постоянное, вход которого подключен ко входному зажиму устройства, SR-триггер, дополнительно введены блок вычитания, инвертор, переключатель, источник опорных напряжений, генератор прямоугольных импульсов, одновибратор, первый и второй счетчики, элемент И, первый и второй n-входовые (где n - число уровней анализа модуля амплитуды выбросов или провалов напряжения) элементы ИЛИ, n компараторов, n делителей частоты с переменным коэффициентом деления, n задатчиков кода коэффициента деления частоты, n D-триггеров, причем в каждом i-м (где i=1, ..., n) канале вход опорного напряжения компаратора подключен к i-му выходу источника опорных напряжений, а инверсный выход соединен со входом установки нуля делителя частоты с переменным коэффициентом деления, вход кода коэффициента деления частоты которого подключен к выходу задатчика кода коэффициента деления частоты, а выход соединен со входом синхронизации D-триггера, инверсный выход которого соединен с i-м входом первого элемента ИЛИ, выход которого через одновибратор соединен с объединенными тактовым входом первого счетчика и входом установки единицы SR-триггера, прямой выход которого соединен с первым входом элемента И, выход которого соединен с тактовым входом второго счетчика, а второй вход подключен к выходу генератора прямоугольных импульсов, соединенному с объединенными между собой тактовыми входами всех n делителей частоты с переменным коэффициентом деления, выход преобразователя переменного напряжения в постоянное соединен со входом уменьшаемого блока вычитания, вход вычитаемого которого подключен к (n+1)-му выходу источника опорных напряжений, а выход соединен со входом инвертора и первым зажимом переключателя, второй зажим которого подключен к выходу инвертора, а общий зажим соединен с объединенными между собой информационными входами компараторов всех каналов, прямые выходы которых через второй элемент ИЛИ соединены со входом установки нуля SR-триггера и объединенными между собой входами установки единицы D-триггеров всех каналов, информационные входы которых объединены между собой и соединены с шиной нулевого потенциала; блок вычитания содержит операционный усилитель, выход которого является выходом блока вычитания и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через первый входной резистор подключен ко входу вычитаемого блока вычитания, вход уменьшаемого которого через второй входной резистор соединен с неинвертирующим входом операционного усилителя, который соединен с шиной нулевого потенциала через дополнительный резистор; инвертор содержит операционный усилитель, выход которого является выходом инвертора и через резистор обратной связи соединен с инвертирующим входом операционного усилителя, который через входной резистор подключен ко входу инвертора, неинвертирующий вход операционного усилителя соединен с шиной нулевого потенциала.

Существенными отличиями предлагаемого технического решения являются использование новых элементов (блока вычитания, инвертора, переключателя, источника опорных напряжений, генератора прямоугольных импульсов, одновибратора, первого и второго счетчиков, элемента И, первого и второго n-входовых элементов ИЛИ, n компараторов, n делителей частоты с переменным коэффициентом деления, n задатчиков кода коэффициента деления частоты, n D-триггеров) и организация новых связей между ними. Эти существенные отличия обеспечивают достижение положительного эффекта - упрощения счетчика, повышения удобства его эксплуатации и расширения функциональных возможностей.

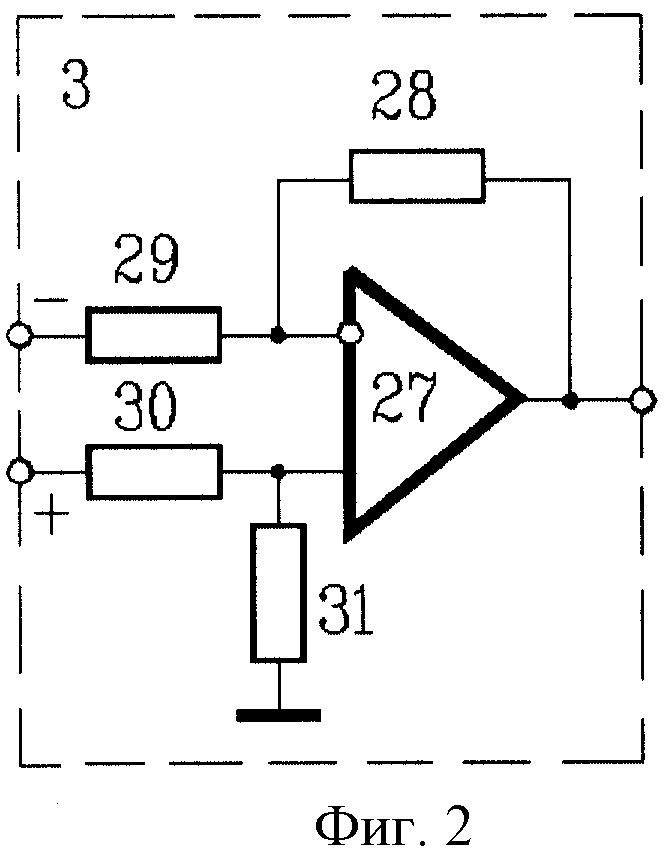

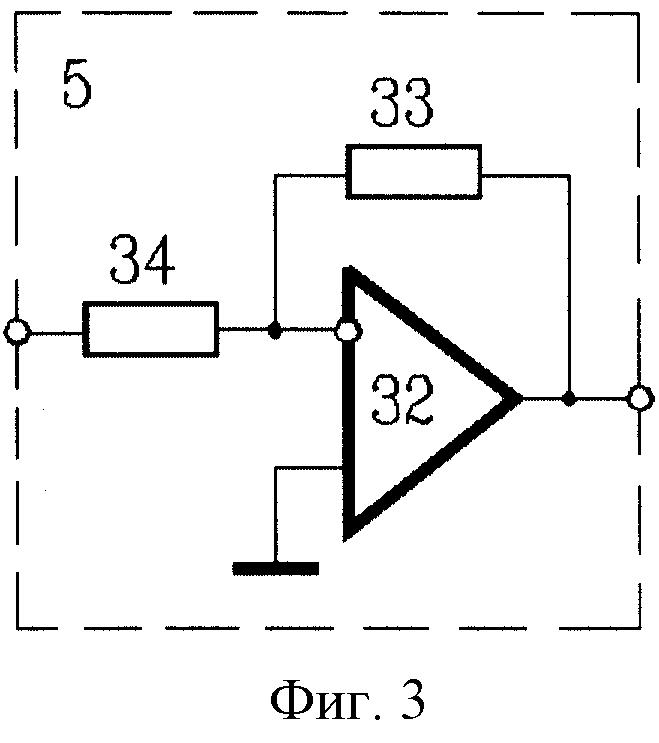

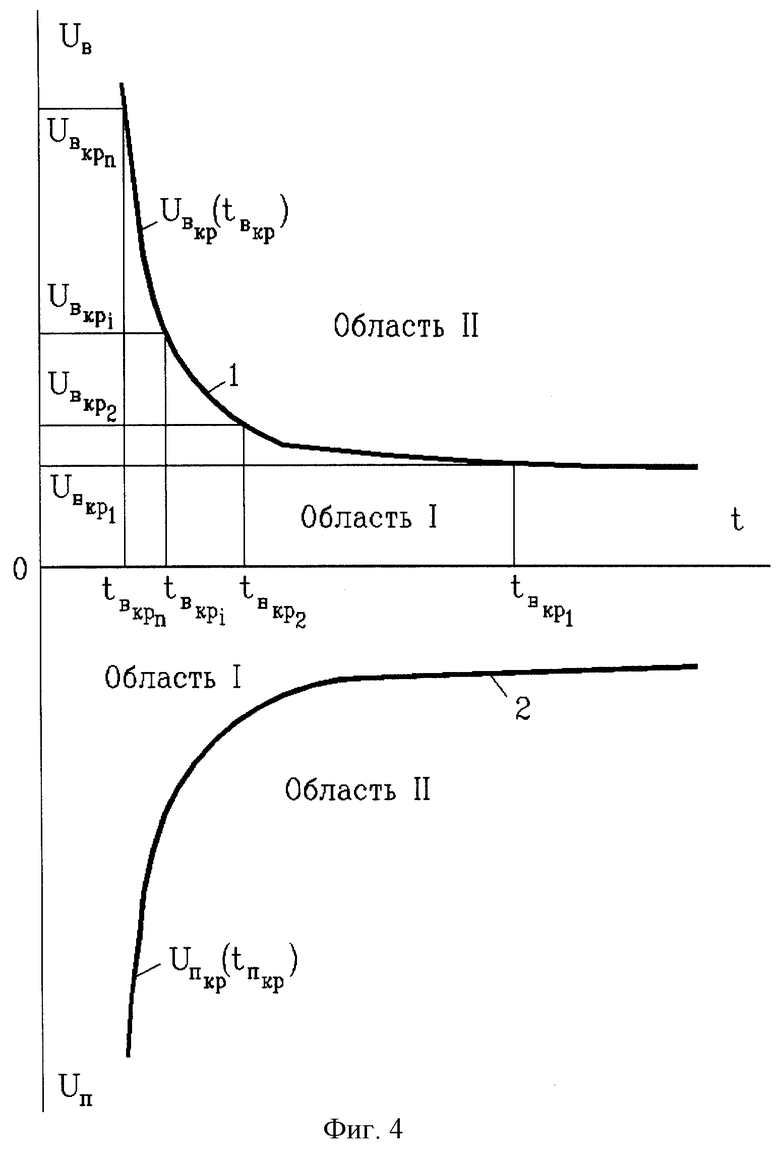

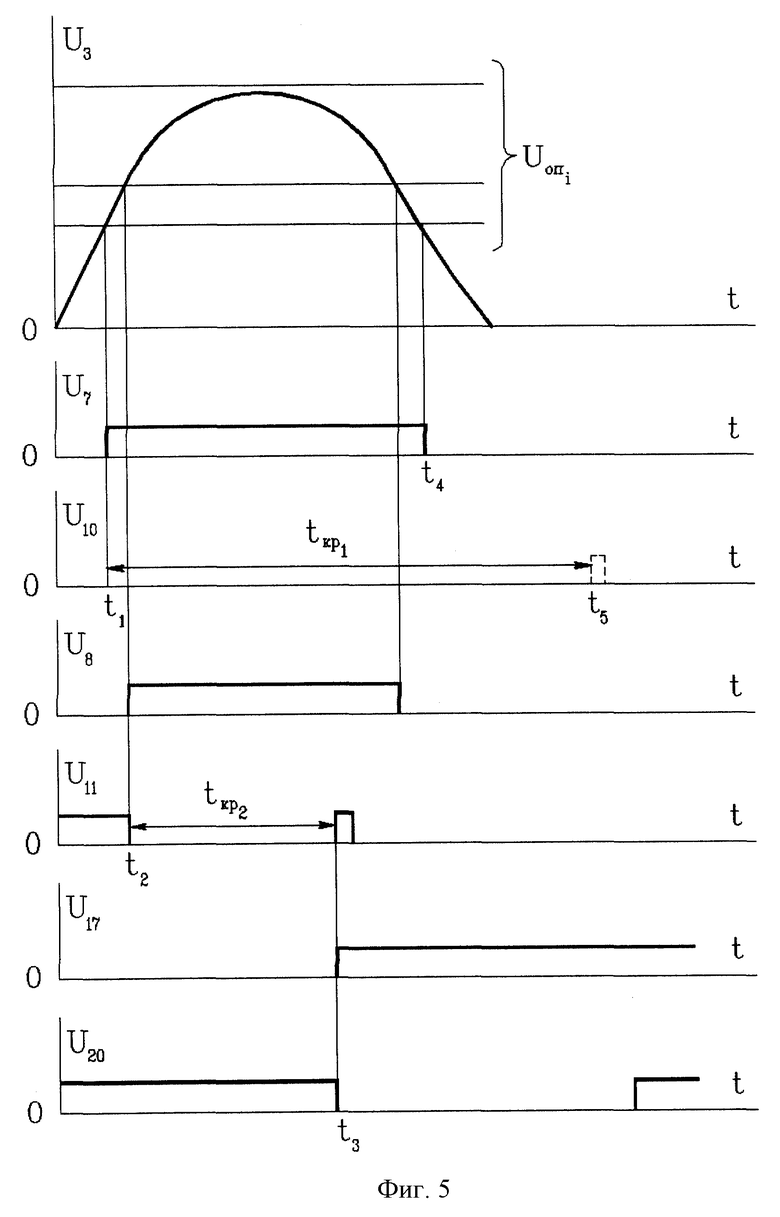

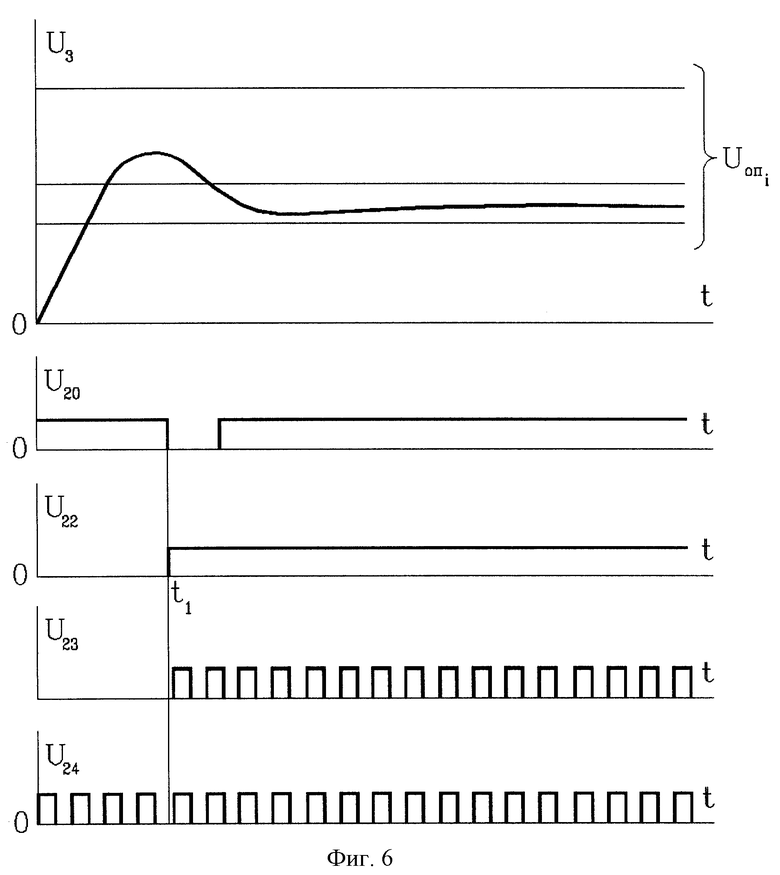

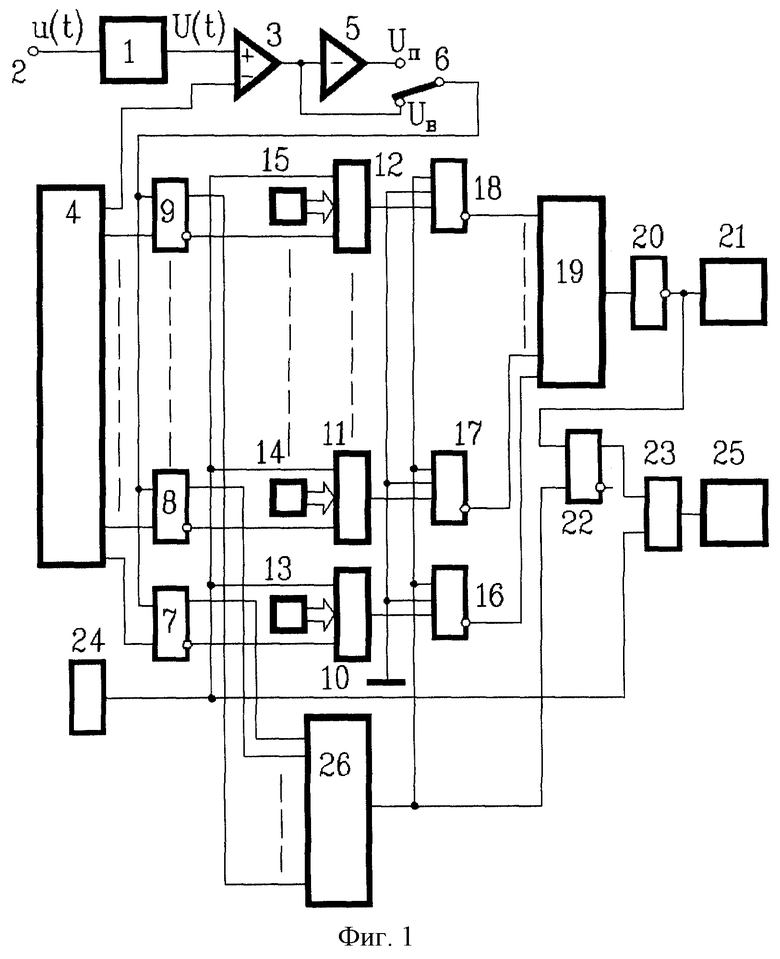

На фиг.1 представлена схема счетчика, на фиг. 2 и 3 - варианты реализации схем блока вычитания и инвертора, на фиг.4 - граничные кривые зависимостей амплитуды выбросов и провалов напряжения от длительности, разделяющие области их допустимых и критических значений, на фиг.5 - графики изменений напряжения на элементах схемы счетчика при стационарном, на фиг.6 - при нестационарном напряжении.

Счетчик содержит преобразователь 1 переменного напряжения в постоянное (ППНП), вход которого подключен ко входному зажиму 2 счетчика, а выход соединен со входом уменьшаемого блока 3 вычитания (БВ), вход вычитаемого которого подключен к (n+1)-му выходу источника 4 опорных напряжений (ИОН), а выход соединен со входом инвертора 5 и первым зажимом переключателя 6, второй зажим которого подключен к выходу инвертора 5, а общий зажим соединен с объединенными между собой информационными входами n (где n - число уровней анализа модуля амплитуды выбросов или провалов напряжения) компараторов 7-9 всех каналов, n делителей 10-12 частоты с переменным коэффициентом деления (ДЧ), n задатчиков 13-15 кода коэффициента деления частоты (ЗК), n D-триггеров 16-18, причем в каждом i-м (где i = 1, ..., n), например, втором, канале вход опорного напряжения компаратора 8 подключен к i-му (в рассматриваемом случае ко второму) выходу ИОН 4, а инверсный выход соединен со входом установки нуля ДЧ 11, вход кода коэффициента деления частоты которого подключен к выходу ЗК 14, а выход соединен со входом синхронизации D-триггера 17, инверсные выходы D-триггеров 16-18 всех каналов соединены со входами первого элемента ИЛИ 19, выход которого через одновибратор 20 соединен с объединенными тактовым входом первого счетчика 21 и входом установки единицы SR-триггера 22, прямой выход которого соединен с первым входом элемента И 23, второй вход которого подключен к выходу генератора 24 прямоугольных импульсов (ГПИ), а выход соединен с тактовым входом второго счетчика 25, прямые выходы n компараторов 7-9 всех каналов через второй элемент ИЛИ 26 соединены со входом установки нуля SR-триггера 22 и объединенными между собой входами установки единицы n D-триггеров 16-18 всех каналов, информационные входы которых объединены между собой и соединены с шиной нулевого потенциала, выход ГПИ 24 соединен с объединенными между собой тактовыми входами n ДЧ 10-12 всех каналов.

Блок 3 вычитания (фиг.2) содержит операционный уилитель (ОУ) 27, выход которого является выходом БВ 3, который через резистор 28 обратной связи соединен с инвертирующим входом ОУ 27 и через первый входной резистор 29 подключен ко входу вычитаемого БВ 3, вход уменьшаемого которого через второй входной резистор 30 соединен с неинвертирующим входом ОУ 27, который через дополнительный резистор 31 соединен с шиной нулевого потенциала.

Инвертор 5 (фиг.3) содержит ОУ 32, выход которого является выходом инвертора 5, который через резистор 33 обратной связи соединен с инвертирующим входом ОУ 32, который через входной резистор 34 подключен ко входу инвертора 5, неинвертирующий вход ОУ 32 соединен с шиной нулевого потенциала.

Исследования, проведенные в [3-6], показывают, что отказ электрооборудования (ЭО) происходит в том случае, если превышаются параметры двух характеристик выбросов (или провалов) напряжения: амплитуда (у провала - глубина) и длительность превышения уровня. На фиг.4 приведены граничные зависимости Uкр (tкр) критических значений уровня напряжения Uкр от критической допустимой длительности его превышения tкр (см. кривые 1 и 2 на фиг.4, соответственно, для выбросов и провалов напряжения), разделяющие квадранты Uв0t и Uп0t (квадранты значений параметров, соответственно, выбросов и провалов напряжения) на области I и II, соответственно, работоспособного и неработоспособного состояния ЭО.

Рассмотрим работу счетчика при стационарном напряжении на примере анализа и фиксации выброса напряжения, изображенного на фиг.5 (см. напряжение U3). В этом случае переключатель 6 находится в нижнем положении.

Уровни срабатывания Uопi компараторов 7-9, которые задаются группой из n нижних выходов ИОН 4, соответствуют критическим уровням напряжения Uвкрi, взятым на перегибе кривой 1 на фиг. 4:

Uоп1=Uвкр1; Uоп2=Uвкр2; Uопi=Uвкрi; Uопn=Uвкрn.

Каждому критическому уровню анализа Uвкрi выброса напряжения соответствует критическая длительность tвкрi (см. фиг.4) его превышения.

Контроль длительности выбросов напряжения осуществляется с помощью ДЧ 10-12, имеющих переменный коэффициент деления частоты входных импульсов. Значение коэффициентов Кi деления частоты для каждого ДЧ 10-12 задается задатчиками кода 13-15 в двоичном коде пропорциональным критической длительности tвкрi

К13=f24tвкр1;

К14=f24tвкр2;

К15=f24tвкрn,

где f24 - частота следования импульсов ГПИ 24.

Напряжение на (n+1)-м выходе ИОН 4 соответствует номинальному напряжению сети Uн.

Счетчик работает следующим образом.

Преобразователь 1 осуществляет преобразование переменного напряжения сети u(t) в постоянное напряжение, пропорциональное действующему значению контролируемого напряжения U(t).

Напряжение с выхода ППНП 1 поступает на вход уменьшаемого БВ 3, ко входу вычитаемого которого приложено номинальное напряжение сети Uн с выхода ИОН 4. В результате на выходе БВ 3 н появляется напряжение (см. фиг.5):

U3=U(t)-Uн. (1)

Это напряжение без изменений через переключатель 6 (который находится в нижнем положении) подается на объединенные информационные входы компараторов 7-9.

В процессе нарастания напряжение U3 в момент времени t1 на фиг.5 превышает уровень срабатывания компаратора 7 первого канала Uоп1, который в этом случает срабатывает - напряжение на его инверсном выходе спадает до нуля. При нулевом напряжении на входе установки нуля ДЧ 10 последний переходит в динамический режим подсчета импульсов с выхода ГПИ 24. Поскольку критическая длительность выброса tвкр1 имеет довольно большое значение (см. фиг. 4) и, соответственно, коэффициент К13=f24tвкр1 деления частоты на выходе ЗК 13 также достаточно велик, то очередной импульс на выходе ДЧ 10 мог бы появиться в момент времени t5. Однако этот импульс не появляется, поскольку в момент времени t4 компаратор 7 уже отпускает, и единичное напряжение с его инверсного выхода при этом приводит в нулевое состояние все многостабильные элементы ДЧ 10.

При дальнейшем нарастании напряжение U3 превышает уровень срабатывания компаратора 8 второго канала Uоп2 (в момент времени t2 на фиг.5), который своим нулевым напряжением инверсного выхода разрешает ДЧ 11 динамический режим подсчета импульсов ГПИ 24.

В момент времени t3 (через время tвкр2 после момента t2) на выходе ДЧ 11 появляется выходной импульс, по переднему фронту которого в D-триггер 17 вписывается "ноль". На инверсном выходе D-триггера 17 при этом появляется единичное напряжение, которое, проходя через элемент ИЛИ 19, запускает одновибратор 20, выходной импульс которого увеличивает содержимое счетчика 21 на единицу.

Таким образом после соответствующей идентификации засчитывается выброс напряжения с критическими параметрами.

В момент времени t4 отпускает компаратор 7 первого канала, напряжение на его прямом выходе спадает до нуля, в результате чего исчезает последняя "единица" со входа элемента ИЛИ 26 - выходное нулевое напряжение последнего возвращает в исходное единичное состояние покоя D-триггеры 16-18.

Схема счетчика приведена в исходное состояние покоя до прихода и идентификации следующего выброса напряжения.

При анализе провалов напряжения переключатель 6 переводится в верхнее положение. В этом случае на объединенные информационные входы компараторов 7-9 подается напряжение

U5= - [U(t)-Uн]. (2)

В остальном при анализе провалов напряжения работа счетчика аналогична описанной выше при анализе выбросов.

Рассмотрим работу счетчика при нестационарном напряжении на примере анализа и фиксации выброса напряжения, изображенного на фиг.6 (см. напряжение U3).

При нестационарном напряжении в сети длительное время имеют место большие отклонения напряжения. В этом случае также длительное время могут быть превышены уровни срабатывания части компараторов 7-9. В такой ситуации происходит отказ ЭО без восстановления работоспособного состояния на длительное время.

Учет суммарного времени отказов ЭО выполняется счетчиком 25 следующим образом.

При идентификации выброса напряжения на фиг.6 в момент времени t1 на выходе одновибратора 20 появляется отрицательный импульс напряжения, который переводит в единичное состояние SR-триггер 22. Напряжение с прямого выхода последнего прикладывается к первому входу элемента И 23, который при этом начинает пропускать импульсы с выхода ГПИ 24. Счетчиком 25 подсчитывается количество N импульсов ГПИ 24, по которому может быть определено суммарное время Тот пребывания ЭО в отказавшем состоянии:

где Тот - суммарное время отказов электрооборудования за время контроля (сутки, неделя, месяц и т.д.), выраженное в секундах;

N - показания счетчика 22;

f - частота ГПИ 24, Гц.

Преимуществами предлагаемого технического решения по сравнению с известными являются упрощение счетчика, повышение удобства его эксплуатации и расширение функциональных возможностей. Схема счетчика проста и легко реализуется на интегральных микросхемах отечественного производства.

Источники информации

1. Ахалкаци В. Г., Церетели К.О., Блеткин Н.П. Детектор колебаний напряжения//Сообщение АН ГССР. Электромеханика 64.-1971.-N2.

2. Корнеев Б.А., Самуйтис В.П. Регистратор импульсных помех // Помехи в цифровой технике: Сб. материалов науч.-техн. конф. /Под ред. И.С. Гурвича. - Вильнюс: Респ. ин-т науч.-техн. информации и пропаганды, 1969. С. 136-138 (прототип).

3. Тэндон М. Л. Применение имитаторов помех для выявления схем, чувствительных к сетевым помехам //Электроника. - 1966. -N 5.-С. 33-38.

4. Ермаков В.Ф., Черепов В.И. Метод автоматического определения критических значений характеристик резкопеременного изменения напряжения для одиночных электроприемников // Повышение эффективности электроснабжения сельскохозяйственных потребителей: Тез. докл. Краевой науч.-техн. конф. молодых ученых и специалистов. - Краснодар: КПИ, 1983.-С. 46-48.

5. Гурвич И.С. Защита ЭВМ от внешних помех. - М.: Энергоатомиздат, 1984, 224 с.

6. Ермаков В. Ф. , Черепов В.И. Экспериментальное исследование влияния провалов напряжения питающей сети на работу электроприемников //Изв. вузов. Сев.-Кавк. регион. Техн. науки.-1997.-N 1.-С. 38-41.

Изобретение относится к области информационно-измерительной и вычислительной техники и предназначено для подсчета выбросов или провалов напряжения, длительность превышения которыми различных уровней анализа больше заданных критических значений, а также определения суммарного времени отказов электрооборудования при нестационарном напряжении в электрических сетях. Техническим результатом является упрощение счетчика, повышение удобства его эксплуатации и расширение функциональных возможностей. Технический результат достигается за счет того, что счетчик содержит преобразователь переменного напряжения в постоянное, блок вычитания, источник опорных напряжений, инвертор, переключатель, n (где n - число уровней анализа модуля амплитуды выбросов или провалов напряжения) компараторов, n делителей частоты с переменным коэффициентом деления, n задатчиков кода коэффициента деления частоты, n D-триггеров, одновибратор, элемент И, два элемента ИЛИ, два счетчика, SR-триггер, генератор прямоугольных импульсов. 2 з.п. ф-лы, 6 ил.

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| US 5636372 A, 03.06.1997. | |||

Авторы

Даты

2002-10-20—Публикация

2001-02-27—Подача