Изобретение относится к области радиотехники и может быть использовано для передачи дискретной информации в условиях воздействия мощной узкополосной или широкополосной частотно-модулированной помехи.

Как известно, в системах связи, использующих сложные сигналы [Варакин Л. Е. Системы связи с шумоподобными сигналами. - М.: Радио и связь, 1985, стр. 7, стр. 192], выигрыш в отношении сигнал/помеха пропорционален базе сигнала.

Однако, во-первых, при недостаточно больших базах применяемых сигналов и мощных помехах этот выигрыш может оказаться недостаточным. Во-вторых, при мощных помехах начинает сказываться нелинейность приемника, в результате чего могут возникать интермодуляционные помехи, структура которых аналогична структуре полезного сигнала, поэтому их подавление не зависит от базы сигнала.

Для подавления мощных ЧМ помех предложено применять так называемые компенсаторы [Теория обнаружения сигналов/Под ред. П.А. Бакута. - М.: Радио и связь, 1984, стр. 294-297, 322-325; "Радиотехника", 1984, 8, стр. 33-35].

При этом в приемнике выход компенсатора соединяется с демодулятором сигнала, оптимальным при гауссовской помехе.

Наиболее близкой к предлагаемой аппаратуре связи можно считать типовую "Аппаратуру для передачи дискретной информации" по а.с. 300946, СССР, Н 03 С 3/40, 1971, приемник которой дополнен типовым "Подавителем помех" (заявка Великобритании 2227907, Н 04 В 1/10, 1979).

Функциональная схема прототипа приведена на фиг.1а и 1б.

Обозначения на фиг.1а:

1 - генератор несущей и тактовой частот;

2 и 4 - первый и второй генераторы псевдослучайных последовательностей (ГПСП);

3 - блок фазирования;

5, 7 и 8 - первый, второй и третий перемножители;

6 - фазовращатель на 90o;

9 - сумматор;

Обозначения на фиг.1б:

1 - подавитель помех;

2 - полосовой амплитудный ограничитель;

3 и 17 - первый и второй фазовые детекторы;

4 - блок фильтрации;

5 - регулируемый усилитель;

6 - вычитатель;

7 - коммутатор;

8 - демодулятор;

9 и 10 - первый и второй перемножители;

11 и 12 - первый и второй генераторы псевдослучайных последовательностей (ГПСП);

13 и 14 - первый и второй полосовые фильтры;

15 - генератор тактовой частоты;

16 - фазовращатель на 90o;

18 - блок синхронизации.

Устройство-прототип имеет следующие функциональные связи.

Передатчик (фиг.1а) содержит генератор несущей и тактовой частот 1, первый выход которого через фазовращатель на 90o 6 соединен со вторым входом первого перемножителя 5, а через второй перемножитель 7 - со вторым входом третьего перемножителя 8, выход которого соединен со вторым входом сумматора 9, первый вход которого соединен с выходом первого перемножителя 5, первый вход которого соединен с выходом первого генератора ПСП 2, первый вход которого соединен со вторым выходом генератора несущей и тактовой частот 1 и с первым входом второго генератора ПСП 4, выход которого соединен с первым входом третьего перемножителя 8; первый и второй выходы блока фазирования 3 соединены со вторыми входами первого 2 и второго 4 генераторов ПСП; кроме того, второй вход второго перемножителя 7 является информационным входом передатчика, а выход сумматора 9 является выходом передатчика.

Приемник (фиг. 1б) содержит подавитель помех 1 и демодулятор 8. Подавитель помех 1 состоит из последовательно соединенных полосового амплитудного ограничителя 2, вход которого является входом приемника, первого фазового детектора 3, блока фильтрации 4 и регулируемого усилителя 5, выход которого соединен со вторым входом вычитателя 6, первый вход которого соединен со входом приемника и со вторым входом коммутатора 7, а выход вычитателя 6 соединен со вторым входом первого фазового детектора 3 и с первым входом коммутатора 7; кроме того, первый вход регулируемого усилителя 5 соединен с выходом полосового амплитудного ограничителя 2. Демодулятор 8 состоит из последовательно соединенных первого перемножителя 9, первого полосового фильтра 13 и фазовращателя на 90o 16, выход которого соединен с первым входом второго фазового детектора 17; последовательно соединенных второго перемножителя 10, второго полосового фильтра 14 и второго фазового детектора 17, выход которого является выходом приемника; третий вход коммутатора 7 является входом команды переключения режимов работы приемника, а выход коммутатора 7 соединен с первым входом первого перемножителя 9, с первым входом второго перемножителя 10 и со входом блока синхронизации 18, второй выход которого соединен со вторыми входами первого 11 и второго 12 генераторов псевдослучайных последовательностей, выходы которых соединены со вторыми входами первого 9 и второго 10 перемножителей соответственно; при этом первый выход блока синхронизации 18 соединен со входом генератора тактовой частоты 15, выход которого соединен с первыми входами первого 11 и второго 12 генераторов псевдослучайных последовательностей.

Работа устройства-прототипа происходит следующим образом.

В передатчике блоки 2 и 4 вырабатывают бинарные псевдослучайные последовательности с элементами +1 и -1, начала которых задаются блоком 3. В блоках 5 и 7 эти ПСП манипулируют фазу высокочастотных колебаний.

На входе блока 5 образуется первый бинарный сложный фазоманипулированный сигнал (СФМнС), манипулированный ПСП блока 2 со значениями фаз 90o и 270o.

На выходе блока 7 образуется второй бинарный СФМнС со значениями фаз 0o и 180o, манипулированный, помимо ПСП блока 4, еще и сигналом информации в блоке 7. В результате на выходе блока 9 формируется 4-х фазный СФМнС, представляющий сумму находящихся в квадратуре первого бинарного периодического СФМнС, манипулированного ПСП блока 2, и второго бинарного СФМнС, манипулированного ПСП блока 4 и сигналом бинарной информации.

Демодулятор 8 представляет типовой приемник 4-х фазного СФМнС.

В режиме синхронизации ПСП, вырабатываемые блоками 2 и 4, совпадают с соответствующими манипулирующими ПСП входных бинарных квадратурных СФМнС.

На выходе блока 9 выделяется несущая первого бинарного СФМнС, которая после фильтрации в блоке 13 и сдвига фазы на 90o поступает на первый вход блока 17 в качестве опорного колебания.

На выходе блока 10 выделяется несущее колебание второго бинарного СФМнС, манипулированное сигналом информации, которое после фильтрации в блоке 14 поступает на второй вход блока 17, на выходе которого выделяется сигнал информации.

Блок 1 осуществляет нелинейное подавление мощной синусоидальной или ЧМ помехи, при наличии которой он через блок 7 подключается к входу блока 8. При отсутствии помехи блок 8 подключается непосредственно к входу приемника.

Наличие мощной помехи определяется некоторыми внешними устройствами, которые управляют блоком 7 с входа 3.

Рассмотрим процесс подавления мощной синусоидальной помехи в блоке 1.

Смесь синусоидального сигнала AссosWct и помехи Aпcos(Wпt+ϕ), АП>АС,

Ucм(t)=AcсosWct+Aпcos(Wпt+ϕ)

представлена на фиг.2.

Вектор сигнала  вращается относительно вектора помехи

вращается относительно вектора помехи  с угловой скоростью

с угловой скоростью

ΔW=WC-WП=2πFб,

где Fб - частота биений.

Результирующее напряжение в виде вектора  имеет угловую и амплитудную модуляцию. Амплитудную модуляцию можно рассматривать как результат биений между сигналом и помехой. Максимумы огибающей соответствуют моментам времени, когда векторы сигнала и помехи синфазны, минимумы - когда противофазны, среднее значение примерно соответствует ортогональности векторов.

имеет угловую и амплитудную модуляцию. Амплитудную модуляцию можно рассматривать как результат биений между сигналом и помехой. Максимумы огибающей соответствуют моментам времени, когда векторы сигнала и помехи синфазны, минимумы - когда противофазны, среднее значение примерно соответствует ортогональности векторов.

При синусоидальных сигнале и помехе форма огибающей смеси также близка к синусоидальной (фиг. 2а), при скачке фазы сигнала на Δϕ синусоида огибающей смеси также испытывает скачок фазы на Δϕ (фиг.2б).

Таким образом, изменение фазы сигнала относительно фазы помехи однозначно отражается изменением фазы синусоиды огибающей.

Частота этой синусоиды 2πFб = 2π|fп-fc|, а амплитуда равна амплитуде сигнала.

Блок 2 на фиг.1б снимает амплитудную модуляцию смеси, а блок 5 доводит амплитуду ограниченной смеси до среднего значения, в результате чего на выходе блока 6 выделяется разность между неограниченной и ограниченной по амплитуде входной смесью. Эту разность можно представить как произведение ограниченной по амплитуде смеси на переменную составляющую огибающей смеси или как сумму полезного сигнала и интермодуляционной помехи 3-го порядка.

Блок 3 выполняет синхронное детектирование сигнала с выхода блока 6.

Цепочка из блоков 3 и 4 вырабатывает напряжение, регулирующее амплитуду смеси на выходе блока 5 до тех пор, пока не осуществится подавление постоянной составляющей напряжения на выходе блока 3.

Таким образом, блок 1 устраняет составляющую с частотой помехи fп и повышает отношение сигнал/помеха.

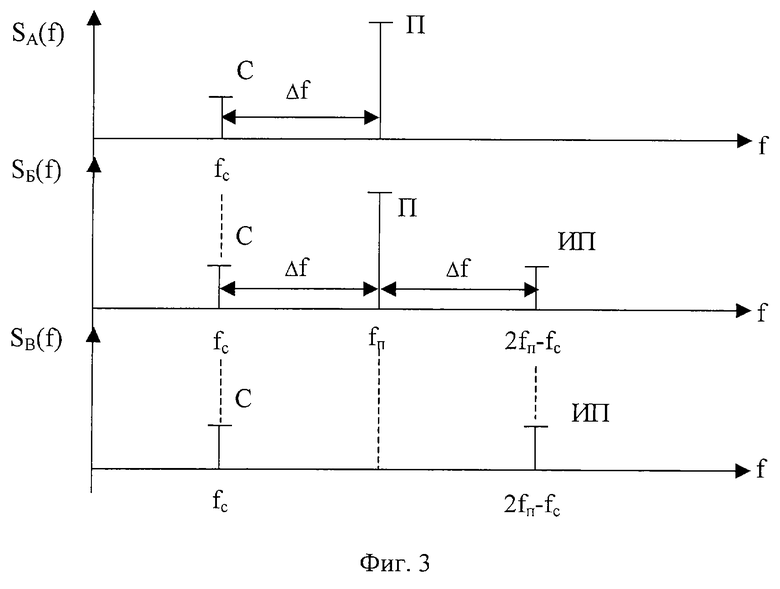

Эпюры в спектральной области (SА(f), SБ(f), SB(f)) в некоторых точках (А, Б, В) схемы блока 1 (фиг.1б) приведены на фиг.3.

Интермодуляционная помеха ИП имеет ту же структуру и амплитуду, что и полезный сигнал С, следовательно, в блоках 9 и 10 с нее снимается фазовая манипуляция ПСП. Если частота интермодуляционной помехи не попадает в полосу пропускания блоков 13 и 14, то она не проходит на выход и не оказывает мешающего влияния на прием полезного сигнала.

Однако, если частота интермодуляционной помехи 2fп-fc попадает в полосу пропускания блоков 13 и 14, выходной сигнал блока 17 будет искажен за счет биений между сигналами и интермодуляционными помехами на его входах, что является недостатком аппаратуры-прототипа.

Для устранения указанного недостатка в аппаратуру для передачи дискретной информации, устойчивую к воздействию мощной ЧМ помехи, содержащую в передатчике генератор несущей и тактовой частот, второй выход которого соединен с первыми входами первого и второго генераторов псевдослучайных последовательностей, вторые входы которых соединены с первым и вторым выходами блока фазирования соответственно, первый, второй и третий перемножители, сумматор, первый вход которого соединен с выходом первого перемножителя, а выход сумматора является выходом передатчика, и фазовращатель на 90o, вход которого соединен с первым выходом генератора несущей и тактовой частот и первым входом второго перемножителя, второй вход которого является информационным входом передатчика, а выход второго перемножителя через третий перемножитель соединен со вторым входом сумматора; содержащую в приемнике подавитель помех, состоящий из полосового амплитудного ограничителя, вход которого, являющийся входом приемника, соединен со вторым входом первого коммутатора и с первым входом вычитателя, второй вход которого через регулируемый усилитель соединен с выходом полосового амплитудного ограничителя и с первым входом фазового детектора, второй вход которого соединен с выходом вычитателя, а выход фазового детектора через блок фильтрации соединен с первым входом регулируемого усилителя; выход первого коммутатора соединен с первыми входами первого и второго перемножителей и блока синхронизации, второй выход которого соединен со вторыми входами первого и второго генераторов псевдослучайных последовательностей, первые входы которых соединены с выходом генератора тактовой частоты, вход которого соединен с первым выходом блока синхронизации, а также из фазовращателя на 90o и полосового фильтра, в передатчик введены формирователь импульсов коммутации, инвертор, первый и второй ключи и четвертый перемножитель, первый вход которого соединен с выходом фазовращателя на 90o; второй вход четвертого перемножителя соединен со вторым входом второго перемножителя, а выход четвертого перемножителя соединен со вторым входом первого перемножителя, первый вход которого соединен с выходом первого ключа, первый вход которого соединен с выходом первого генератора псевдослучайных последовательностей, а второй вход первого ключа соединен с выходом формирователя импульсов коммутации и через инвертор - со вторым входом второго ключа, первый вход которого соединен с выходом второго генератора псевдослучайных последовательностей, а выход второго ключа соединен с первым входом третьего перемножителя, причем первый вход формирователя импульсов коммутации соединен со вторым выходом генератора несущей и тактовой частот, а второй вход формирователя импульсов коммутации соединен с третьим выходом блока фазирования; в приемник введены второй и третий коммутаторы, первый, второй, третий и четвертый смесители, опорный генератор, сумматор, первый и второй ключи, инвертор, блок выделения информации и формирователь импульсов коммутации, первый вход которого соединен с выходом генератора тактовой частоты и с четвертым входом блока синхронизации, второй вход которого соединен со вторым входом третьего смесителя и с выходом второго коммутатора, третий вход которого соединен с третьим входом первого коммутатора, являющегося входом команды переключения режимов работы приемника, и с третьим входом третьего коммутатора, первый вход которого соединен с выходом второго смесителя, первый вход которого соединен с первым входом фазового детектора и с первым входом первого смесителя, второй вход которого соединен с выходом опорного генератора, со вторым входом второго коммутатора и со входом фазовращателя на 90o, выход которого соединен со вторым входом второго смесителя и со вторым входом третьего коммутатора, выход которого соединен с третьим входом блока синхронизации и со вторым входом четвертого смесителя, первый вход которого соединен с выходом второго перемножителя, а выход четвертого смесителя соединен со вторым входом сумматора, первый вход которого соединен с выходом третьего смесителя, первый вход которого соединен с выходом первого перемножителя, второй вход которого соединен с выходом первого ключа, второй вход которого соединен с выходом формирователя импульсов коммутации и через инвертор - со вторым входом второго ключа, выход которого соединен со вторым входом второго перемножителя; а также, второй вход формирователя импульсов коммутации соединен со вторыми входами первого и второго генераторов псевдослучайных последовательностей и со вторым выходом блока синхронизации, при этом выход первого генератора псевдослучайных последовательностей соединен с первым входом первого ключа; выход первого смесителя соединен с первым входом первого коммутатора; кроме того, выход сумматора через полосовой фильтр соединен со входом блока выделения информации, выход которого является выходом приемника.

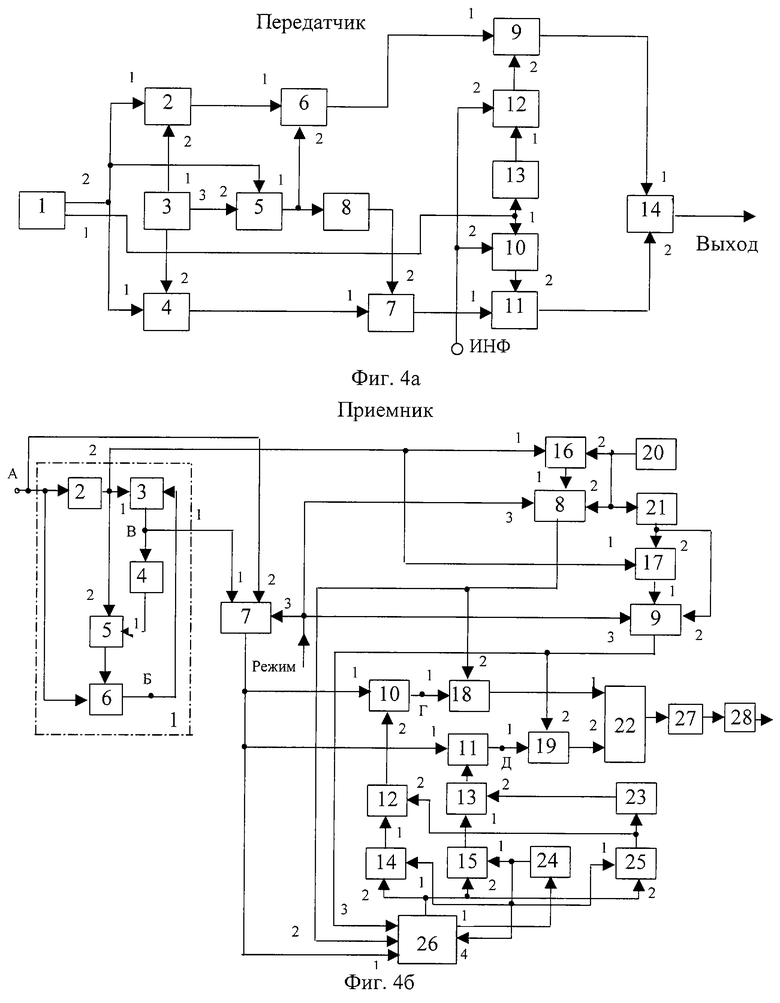

Структурная схема предлагаемого устройства приведена на фиг.4а и б.

Обозначения на фиг.4а:

1 - генератор несущей и тактовой частот;

2 и 4 - первый и второй генераторы псевдослучайных последовательностей (ГПСП);

3 - блок фазирования;

5 - формирователь импульсов коммутации (ФИК);

6 и 7 - первый и второй ключи;

8 - инвертор;

9÷12 - первый ... четвертый перемножители;

13 - фазовращатель на 90o;

14 - сумматор;

Обозначения на фиг.4б:

1 - подавитель помех;

2 - полосовой амплитудный ограничитель;

3 - фазовый детектор;

4 - блок фильтрации (интегратор);

5 - регулируемый усилитель;

6 - вычитатель;

7, 8 и 9 - первый, второй и третий коммутаторы;

10 и 11 - первый и второй перемножители;

12 и 13 - первый и второй ключи;

14 и 15 - первый и второй генераторы псевдослучайных последовательностей (ГПСП);

16÷19 - первый ... четвертый смесители;

20 - опорный генератор;

21 - фазовращатель на 90o;

22 - сумматор;

23 - инвертор;

24 - генератор тактовой частоты;

25 - формирователь импульсов коммутации (ФИК);

26 - блок синхронизации;

27 - полосовой фильтр;

28 - блок выделения информации.

Предлагаемое устройство содержит передатчик (фиг.4а), состоящий из генератора несущей и тактовой частот 1, второй выход которого соединен с первым выходом ФИК 5 и с первыми входами первого 2 и второго 4 генераторов псевдослучайных последовательностей, вторые входы которых соединены с первым и вторым выходами блока фазирования 3, выход которого через ФИК 5 соединен со входом инвертора 8 и со вторым входом первого ключа 6, первый вход которого соединен с выходом первого ГПСП 2, а выход первого ключа 6 через первый перемножитель 9 присоединен к первому входу сумматора 14; выход инвертора 8 соединен со вторым входом второго ключа 7, первый вход которого соединен с выходом второго ГПСП 4, а выход второго ключа 7 через третий перемножитель 11 присоединен к второму входу сумматора 14, выход которого является выходом передатчика. Второй информационный вход передатчика соединен со вторыми входами второго перемножителя 10 и четвертого перемножителя 12, выход которого соединен со вторым входом первого перемножителя 9, а первый вход четвертого перемножителя 12 через последовательно соединенные фазовращатель на 90o 13 и второй перемножитель 10 соединен со вторым входом третьего перемножителя 11, при этом первый вход второго перемножителя 10 соединен с первым выходом генератора несущей и тактовой частот 1.

Приемник (фиг. 4б) содержит подавитель помех 1, состоящий из последовательно соединенных полосового амплитудного ограничителя 2, вход которого является входом приемника, фазового детектора 3, выход которого через блок фильтрации 4 соединен с первым входом регулируемого усилителя 5, выход которого соединен со вторым входом вычитателя 6, выход которого соединен со вторым входом фазового детектора 3, первый вход которого соединен с первым входом первого смесителя 16 и первым входом второго смесителя 17; а также, вход полосового амплитудного ограничителя 2 соединен с первым входом вычитателя 6 и со вторым входом первого коммутатора 7, первый вход которого соединен со входом блока фильтрации 4; кроме того, второй вход регулируемого усилителя 5 соединен со входом фазового детектора 3. Выход первого коммутатора 7 соединен с первым входом блока синхронизации 26 и с первыми входами второго перемножителя 11 и первого перемножителя 10, выход которого через третий смеситель 18 соединен с первым входом сумматора 22, второй вход которого через четвертый смеситель 19 соединен с выходом второго перемножителя 11, второй вход которого через второй ключ 13 соединен с выходом второго ГПСП 15, второй вход которого соединен со вторым входом ФИК 25, со вторым выходом блока синхронизации 26 и со вторым входом первого ГПСП 14, выход которого через первый ключ 12 соединен со вторым входом первого перемножителя 10. Третий вход первого коммутатора 7, являющийся входом команды переключения режимов работы приемника, соединен с третьим входом третьего коммутатора 9 и с третьим входом второго коммутатора 8, выход которого соединен со вторым входом третьего смесителя 18 и со вторым входом блока синхронизации 26, третий вход которого соединен со вторым входом четвертого смесителя 19 и с выходом третьего коммутатора 9, второй вход которого соединен со вторым входом второго смесителя 17 и с выходом фазовращателя на 90o 21, вход которого соединен с выходом опорного генератора 20 и со вторыми входами первого смесителя 16 и второго коммутатора 8, второй вход которого соединен с выходом первого смесителя 16; выход второго смесителя 17 соединен с первым входом третьего коммутатора 9. Первый выход блока синхронизации 26 через генератор тактовой частоты 24 соединен с первыми входами второго ГПСП 15 и первого ГПСП 14, с четвертым входом блока синхронизации 26 и первым входом ФИК 25, выход которого соединен со вторым входом первого ключа 12 и через инвертор 23 - со вторым входом второго ключа 13. Кроме того, выход сумматора 22 через полосовой фильтр 27 соединен со входом блока выделения информации 28, выход которого является выходом приемника.

Работа предлагаемой аппаратуры происходит следующим образом.

В передатчике формирование первого и второго бинарных СФМнС, составляющих 4-х фазный СФМнС осуществляется так же, как и в передатчике-прототипе, за исключением:

1. оба сигнала манипулированы по фазе одним и тем же сигналом информации, для чего введен блок 12;

2. временные отрезки каждого из составляющих бинарных СФМнС поступают на входы блока 14 поочередно при открывании соответствующих блоков 6 или 7, которые управляются блоком 5.

В приемнике блок 1 работает так же, как и в приемнике-прототипе, однако выходное напряжение снимается не с выхода блока 6, а с выхода фазового блока 3, т.е. после демодуляции. В блоках 10 и 11 поочередно снимается манипуляция с соответствующих сигналов, причем очередность осуществляется путем отпирания и запирания блоков 12 и 13, которые управляются импульсами с блока 25. На выходах блоков 12 и 13 формируются 3-х уровневые ПСП, элементы которых принимают значения ±1 и 0.

В результате на выходах перемножителей 10 и 11 выделяются отрезки огибающих биений между помехой и первьм и вторым бинарными СФМнС.

Т. к. несущие колебания сдвинуты относительно друг друга на 90o, то и огибающие биений также сдвинуты на 90o. Если изменяется частота помехи, соответственно изменяется и частота огибающей биений. Скачки фазы на 180o, обусловленные манипуляцией информационного сигнала, при этом сохраняются. Для осуществления фильтрации желательно преобразовать биения так, чтобы их частота стала постоянной. С этой целью биения смешиваются с соответствующими опорными колебаниями в 18 и 19. Квадратурные опорные колебания формируются в блоках 16 и 17. Чтобы получить частотную модуляцию опорных колебаний, аналогичную частотной модуляции биений, в блоках 16 и 17 смешиваются сигнал с выхода блока 2, практически пропорциональный помехе, и сигнал блока 20 с частотой foг.

На выходах блоков 16 и 17 формируются квадратурные опорные колебания с частотой fог-fп.

Обозначим сигнал с выхода блока 16 как sin А, тогда сигнал с выхода блока 17 будет cos A.

На первые входы блоков 18 и 19 поступают огибающие биений с частотой fб = |fп-fc|.

Обозначим сигнал на первом входе блока 18 через sin В, тогда сигнал на первом входе блока 19 будет cos В.

Сигнал на выходе блока 18 запишется как

а на выходе блока 19

Очевидно, на выходе блока 22 выделится сигнал нижней боковой полосы cos(A-В) с постоянной (не зависящей от fп) частотой foг-fc. На эту частоту настроен блок 27.

Опорные колебания на вторых входах блоков 18 и 19 имеют малые скачки фазы ψ, обусловленные информационным сигналом (фиг.2). Колебания на первых входах этих блоков под воздействием информационного сигнала меняют знак на противоположный. Следовательно, и суммарный сигнал cos(A-В) под действием информационного сигнала будет испытывать скачки фазы на 180o. В результате на выходе блока 27 получается синусоидальный сигнал с постоянной частотой foг-fc, манипулированный бинарным сигналом информации. Этот информационный сигнал выделяется в типовом блоке выделения информации 28.

Таким образом, мешающее влияние интермодуляционной помехи устраняется даже в случае, когда fп=fc.

Эпюры напряжений (UА(t), UБ(t), UВ(t), UГ(t), UД(t)) в разных точках (А, Б, В, Г, Д) схемы на фиг.4б для случая, когда период импульсов коммутации равен четверти периода биений, а длительность импульса коммутации равна длительности одного элемента СФМнС, при одинаковых на данном отрезке манипулирующих последовательностях 1 0 1 0 синфазного (I) и квадратурного (Q) сигналов приведены на фиг.5.

Очевидно, квадратурный канал в предлагаемом устройстве служит для получения огибающей биений, сдвинутой на 90o относительно огибающей синфазного канала.

Для этой цели можно было бы использовать фазовращатель на 90o. Однако его трудно реализовать для сверхнизких частот.

Все элементы функциональной схемы на фиг.4а и б являются типовыми и описаны в соответствующей литературе, например, в книге "Радиоприемные устройства" /Под ред. А.П. Жуковского. - М.: Высшая школа, 1989, стр. 123, рис. 7.1, стр. 140, рис. 7.27, стр. 142, рис. 7.29.

Генераторы ПСП могут быть выполнены на основе типовой схемы, приведенной, например, в книге Варакина Л.Е. "Системы связи с шумоподобными сигналами". - М.: Радио и связь, 1985, стр. 54, рис. 3.17.

Формирователь импульсов коммутации может быть выполнен на счетном триггере с установочным входом.

Блок выделения информации 28 для простого (без расширяющей спектр ПСП) бинарного сигнала может быть выполнен, например по типовой схеме Костаса [Лиджсей В. Системы синхронизации в связи и управлении: Пер. с англ. /Под ред. Ю. Н. Бакаева и М.В. Капранова, - М.: Сов. радио, 1978, стр. 102, рис. 3.13] или по схеме дифференциально-когерентного демодулятора [Спилкер Дж. Цифровая спутниковая связь: Пер. с англ. /Под ред. В.В. Макарова. - М.: Связь, 1979, стр. 300, рис. 11.28].

Блок синхронизации 26 может быть выполнен по схеме, приведенной в книге Варакина Л. Е. "Системы связи с шумоподобными сигналами". - М.: Радио и связь, 1985, стр. 30, рис. 17.5. В качестве примера на фиг.6 приведена одна из возможных его схем.

На фиг.6 введены следующие обозначения:

КК 1÷КК 5 - корреляционные каналы;

11 и 12 - первый и второй перемножители;

21 и 22 - первый и второй смесители;

31 I÷33 I - первый...третий ключи синфазного (I) канала;

31 Q÷33 Q - первый...третий ключи квадратурного (Q) канала;

41 и 42 - первый и второй генераторы ПСП;

5 - дешифратор;

6 - сумматор;

7 - полосовой фильтр;

8 - инвертор;

9 - формирователь импульсов коммутации;

10 - ключ;

11 - амплитудный детектор;

12 - генератор тактовой частоты;

13 - интегратор;

14 - блок управления;

15 - решающая схема;

16 - вычитатель;

17 - фильтр петли.

Три верхних корреляционных канала (фиг.6) осуществляют поиск СФМнС по задержке. Генераторами ПСП 41 и 42 и ключами 31 I÷33 I формируются трехуровневые ПСП I1÷I3 для каналов I, а генераторами ПСП 41 и 42 и ключами 31 Q÷33 Q - трехуровневые ПСП Q1÷QI3 для каналов Q. Опорные колебания SI и SQ подаются одновременно во все корреляционные каналы КК 1÷КК 5 с коммутаторов 8 и 9 (фиг.4б).

Решающая схема 15 (фиг.6) вырабатывает импульсы запирания ключа 10 до тех пор, пока не будет обнаружен максимум автокорреляционной функции ПСП, соответствующий максимуму напряжения на выходе интегратора 13 одного из корреляционных каналов КК 1÷КК 3.

Генераторы ПСП 41 и 42, корреляционные каналы КК 4 и КК 5 и вычитатель 16 образуют временной дискриминатор, а генератор тактовой частоты 12, блок управления 14 и фильтр петли 17 образуют генератор, управляемый напряжением (ГУН). Схема слежения за задержкой осуществляет тактовую синхронизацию. Импульс, формируемый на выходе дешифратора 5, задает начальное состояние генераторов ПСП 41 и 42 и формирователя импульсов коммутации 9.

Элементы блока синхронизации 16 на фиг.6, входящие в приемник на фиг.4б, изображены пунктиром.

Изобретение относится к области радиотехники и может быть использовано для передачи дискретной информации в условиях воздействия мощной узкополосной или широкополосной частотно-модулированной помехи. Технический результат - повышение помехоустойчивости аппаратуры при передаче дискретной информации за счет устранения влияния интермодуляционной помехи. Аппаратура содержит приемник и передатчик. В передатчик введены формирователь импульсов коммутации, инвертор, два ключа и четвертый перемножитель. При этом в передатчике формируется четырехфазный сложный фазоманипулированный сигнал путем поочередной передачи синфазного и квадратурного бинарного сигналов, манипулированных по фазе одним и тем же информационным сигналом. В приемник введены два коммутатора, четыре смесителя, опорный генератор, сумматор, два ключа, инвертор, формирователь импульсов коммутации и блок выделения информации, что позволяет осуществить нелинейное подавление мощной помехи, отличающееся устранением влияния образующейся при этом интермодуляционной помехи 3-го порядка. Для этого колебание огибающей смеси с разностной частотой сигнала и помехи преобразуется в колебание с постоянной частотой, манипулированное по фазе информационным сигналом. Это позволяет устранить влияние интермодуляционной помехи в приемнике, что повышает помехоустойчивость аппаратуры. 6 ил.

Аппаратура для передачи дискретной информации, устойчивая к воздействию мощной ЧМ-помехи, содержащая в передатчике генератор несущей и тактовой частот, второй выход которого соединен с первыми входами первого и второго генераторов псевдослучайных последовательностей, вторые входы которых соединены с первым и вторым выходами блока фазирования соответственно, первый, второй и третий перемножители, сумматор, первый вход которого соединен с выходом первого перемножителя, а выход сумматора является выходом передатчика, и фазовращатель на 90o, вход которого соединен с первым выходом генератора несущей и тактовой частот и первым входом второго перемножителя, второй вход которого является информационным входом передатчика, а выход второго перемножителя через третий перемножитель соединен со вторым входом сумматора, содержащая в приемнике подавитель помех, состоящий из полосового амплитудного ограничителя, вход которого, являющийся входом приемника, соединен со вторым входом первого коммутатора и с первым входом вычитателя, второй вход которого через регулируемый усилитель соединен с выходом полосового амплитудного ограничителя и с первым входом фазового детектора, второй вход которого соединен с выходом вычитателя, а выход фазового детектора через блок фильтрации соединен с первым входом регулируемого усилителя, выход первого коммутатора соединен с первыми входами первого и второго перемножителей и блока синхронизации, второй выход которого соединен со вторыми входами первого и второго генераторов псевдослучайных последовательностей, первые входы которых соединены с выходом генератора тактовой частоты, вход которого соединен с первым выходом блока синхронизации, а также из фазовращателя на 90o и полосового фильтра, отличающаяся тем, что в передатчик введены формирователь импульсов коммутации, инвертор, первый и второй ключи и четвертый перемножитель, первый вход которого соединен с выходом фазовращателя на 90o; второй вход четвертого перемножителя соединен со вторым входом второго перемножителя, а выход четвертого перемножителя соединен со вторым входом первого перемножителя, первый вход которого соединен с выходом первого ключа, первый вход которого соединен с выходом первого генератора псевдослучайных последовательностей, а второй вход первого ключа соединен с выходом формирователя импульсов коммутации и через инвертор - со вторым входом второго ключа, первый вход которого соединен с выходом второго генератора псевдослучайных последовательностей, а выход второго ключа соединен с первым входом третьего перемножителя, причем первый вход формирователя импульсов коммутации соединен со вторым выходом генератора несущей и тактовой частот, а второй вход формирователя импульсов коммутации соединен с третьим выходом блока фазирования; в приемник введены второй и третий коммутаторы, первый, второй, третий и четвертый смесители, опорный генератор, сумматор, первый и второй ключи, инвертор, блок выделения информации и формирователь импульсов коммутации, первый вход которого соединен с выходом генератора тактовой частоты и с четвертым входом блока синхронизации, второй вход которого соединен со вторым входом третьего смесителя и с выходом второго коммутатора, третий вход которого соединен с третьим входом первого коммутатора, являющегося входом команды переключения режимов работы приемника, и с третьим входом третьего коммутатора, первый вход которого соединен с выходом второго смесителя, первый вход которого соединен с первым входом фазового детектора и с первым входом первого смесителя, второй вход которого соединен с выходом опорного генератора, со вторым входом второго коммутатора и со входом фазовращателя на 90o, выход которого соединен со вторым входом второго смесителя и со вторым входом третьего коммутатора, выход которого соединен с третьим входом блока синхронизации и со вторым входом четвертого смесителя, первый вход которого соединен с выходом второго перемножителя, а выход четвертого смесителя соединен со вторым входом сумматора, первый вход которого соединен с выходом третьего смесителя, первый вход которого соединен с выходом первого перемножителя, второй вход которого соединен с выходом первого ключа, второй вход которого соединен с выходом формирователя импульсов коммутации и через инвертор - со вторым входом второго ключа, выход которого соединен со вторым входом второго перемножителя, а также второй вход формирователя импульсов коммутации соединен со вторыми входами первого и второго генераторов псевдослучайных последовательностей и со вторым выходом блока синхронизации, при этом выход первого генератора псевдослучайных последовательностей соединен с первым входом первого ключа; выход первого смесителя соединен с первым входом первого коммутатора; кроме того, выход сумматора через полосовой фильтр соединен со входом блока выделения информации, выход которого является выходом приемника.

| 0 |

|

SU300946A1 | |

| 1992 |

|

RU2001528C1 | |

| СИСТЕМА СВЯЗИ С ШИРОКОПОЛОСНЫМИ СИГНАЛАМИ | 1995 |

|

RU2115236C1 |

| Теория обнаружения сигналов./Под ред | |||

| Бакута П.А | |||

| - М.: Радио и связь, 1984, с | |||

| ДИФФЕРЕНЦИАЛЬНАЯ ТЕРМИОННАЯ ЛАМПА | 1920 |

|

SU294A1 |

Авторы

Даты

2003-05-27—Публикация

2001-09-20—Подача