Изобретение относится к электротехнике и может быть использовано в устройствах релейной защиты в качестве реле направления мощности.

Известно устройство, содержащее последовательно соединенные генератор тактовых импульсов, двоичный счетчик, дешифратор, формирователь импульсов и исполнительный элемент, выполненный в виде транзистора [1].

Недостатком устройства являются относительно узкие функциональные возможности, не позволяющие использовать его в качестве реле направления мощности.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее последовательно соединенные промежуточный преобразователь напряжения, блок фиксации положительных значений сигнала, первый интегратор, сумматор, пороговый блок и исполнительный элемент, а также последовательно соединенные промежуточный преобразователь тока, блок фиксации отрицательных значений сигнала, первый вход которого соединен со вторым входом блока фиксации положительных значений сигнала, а второй вход соединен с первым входом блока фиксации положительных значений сигнала, и второй интегратор, выход которого соединен со вторым входом сумматора [2].

Недостатком наиболее близкого технического решения является относительно низкая точность в условиях возможных изменений частоты входного сигнала.

Действительно, в основу его работы положен принцип сравнения фаз двух сигналов - напряжения и тока от защищаемого объекта. Параметры устройства должны быть настроены на заданное время совпадения однополярных мгновенных значений этих сигналов. Однако заданное время настройки существенно зависит от частоты сигнала и при изменениях частоты даже в небольших пределах точность работы устройства резко снижается.

Техническим результатом изобретения является повышение точности.

Этот технический результат достигается тем, что в устройство, содержащее промежуточный трансформатор напряжения, промежуточный трансформатор тока и последовательно соединенные двухпороговый компаратор и исполнительный элемент, введены первый пороговый блок с нулевым пороговым уровнем, вход которого соединен с выходом промежуточного трансформатора напряжения, второй пороговый блок с нулевым пороговым уровнем, вход которого соединен с выходом промежуточного трансформатора тока, первый элемент И, первый и второй входы которого соединены с выходами "больше" первого и второго упомянутых пороговых блоков, соответственно, второй элемент И, первый и второй входы которого соединены с выходами "меньше" первого и второго пороговых блоков, соответственно, реверсивный счетчик, вход сложения которого соединен с выходом первого элемента И, вход вычитания соединен с выходом второго элемента И, а выход - соединен с информационным входом двухпорогового компаратора, последовательно соединенные одновибратор, вход которого соединен со входом пуска реле, и генератор тактовых импульсов, выход которого соединен с третьими входами первого и второго элементов И, последовательно соединенные третий элемент И, первый вход которого соединен с выходом генератора тактовых импульсов, первый счетчик, первый регистр памяти, выход которого соединен с первым входом сумматора, выход которого соединен со входом блока определения порогов, первый и второй выходы которого соединены, соответственно, с первым и вторым входами установки пороговых уровней двухпорогового компаратора, последовательно соединенные четвертый элемент И, первый вход которого соединен с выходом генератора тактовых импульсов, второй счетчик и второй регистр памяти, выход которого соединен со вторым входом сумматора, первый формирователь импульсов по заднему фронту сигналов на его входе, вход которого соединен с выходом "больше" упомянутого первого порогового блока и со вторым входом четвертого элемента И, второй формирователь импульсов по заднему фронту импульсов на его входе, вход которого соединен с выходом "больше" упомянутого второго порогового блока и со вторым входом третьего элемента И, первый элемент ИЛИ, первый вход которого соединен с выходом упомянутого первого формирователя импульсов и с входом управления записью первого регистра памяти, а выход - соединен с входом установки в ноль первого счетчика, второй элемент ИЛИ, первый вход которого соединен с выходом второго упомянутого формирователя импульсов и с входом управления записью второго регистра памяти, второй вход - соединен со вторым входом первого элемента ИЛИ, с установочным входом реверсивного счетчика и с выходом одновибратора, а выход - соединен с входом установки в ноль второго счетчика. Кроме того, двухпороговый компаратор содержит первый и второй пороговые элементы, информационные входы которых объединены и являются информационным входом двухпорогового компаратора, а входы установки пороговых уровней первого и второго пороговых элементов являются, соответственно, входами установки первого и второго пороговых уровней двухпорогового компаратора, а также элемент ИЛИ, первый и второй входы которого соединены с выходом, соответственно первого и второго пороговых элементов, а выход - является выходом двухпорогового компаратора. Кроме того, входы установки в ноль первого и второго счетчиков соединены с выходами соответствующего первого и второго элементов ИЛИ через соответствующие элементы задержки. Кроме того, управление записью информации в первый и второй регистры памяти осуществляется по передним фронтам импульсов упомянутых первого и второго формирователей импульсов, соответственно, а установка в ноль первого и второго счетчиков - по задним фронтам этих же импульсов. Кроме того, исполнительный элемент выполнен в виде реле с замыкающим контактом, обмотка которого непосредственно или через усилитель соединена с выходом двухпорогового компаратора.

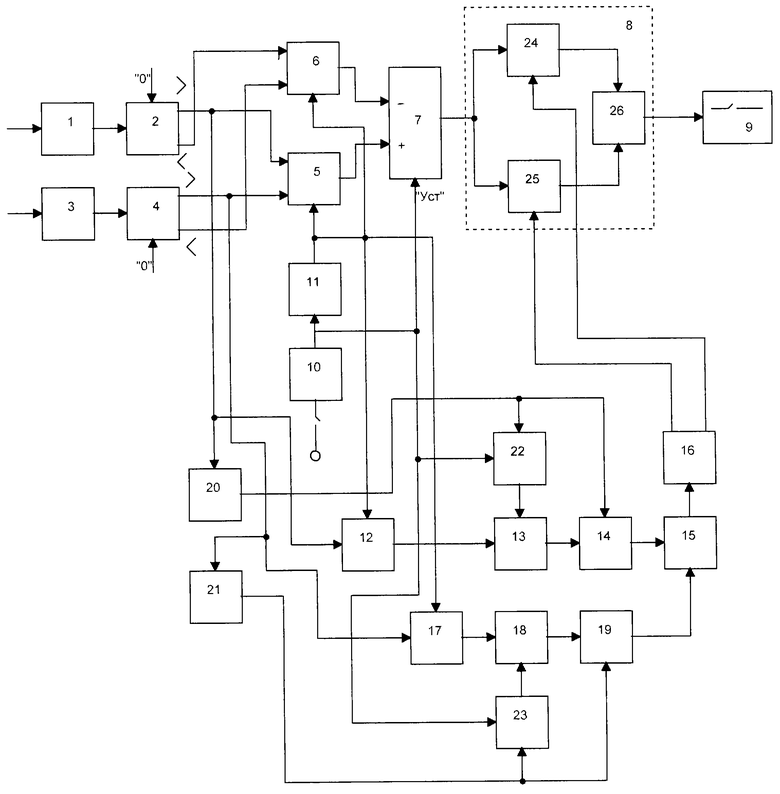

На чертеже представлена электрическая структурная схема реле направления мощности.

Реле направления мощности содержит последовательно соединенные промежуточный трансформатор 1 напряжения и первый пороговый блок 2 с нулевым пороговым уровнем, последовательно соединенные промежуточный трансформатор 3 тока и второй пороговый блок 4 с нулевым пороговым уровнем, первый элемент И 5, первый и второй входы которого соединены с выходами "больше" первого 2 и второго 4 пороговых блоков с нулевым пороговым уровнем, соответственно, второй элемент И 6, первый и второй входы которого соединены с выходами "меньше" первого 2 и второго 4 пороговых блоков, соответственно, реверсивный счетчик 7, вход суммирования которого соединен с выходом первого элемента И 5, а вход вычитания - соединен с выходом второго элемента И 6, двухпороговый компаратор 8, информационный вход которого соединен с выходом реверсивного счетчика 7, исполнительный элемент 9, вход которого соединен с выходом двухпорогового компаратора 8, последовательно соединенные одновибратор 10 и генератор тактовых импульсов (ГТИ) 11, выход которого соединен с третьими входами первого 5 и второго 6 элементов И, последовательно соединенные третий элемент И 12, первый счетчик 13, первый регистр 14 памяти, сумматор 15 и блок 16 определения порогов, первый и второй выходы которого соединены, соответственно, с входами установки первого и второго пороговых уровней двухпорогового компаратора, последовательно соединенные четвертый элемент И 17, первый вход которого соединен с первым входом третьего элемента И 12 и с выходом генератора 11 тактовых импульсов, второй счетчик 18 и второй регистр 19 памяти, выход которого соединен со вторым входом сумматора 15, первый формирователь 20 импульсов по заднему фронту сигнала на его входе, вход которого соединен с выходом "больше" первого порогового блока 2 с нулевым пороговым уровнем и со вторым входом третьего элемента И 12, второй формирователь 21 импульсов по заднему фронту сигнала на его входе, вход которого соединен с выходом "больше" второго порогового блока 4 с нулевым пороговым уровнем и со вторым входом четвертого элемента И 17, первый элемент ИЛИ 22, первый вход которого соединен с выходом первого формирователя 20 импульсов и с управляющим входом первого регистра 14 памяти, а выход - соединен с входом установки в ноль первого счетчика 13, второй элемент ИЛИ 23, первый вход которого соединен с выходом второго формирователя 21 импульсов и с управляющим входом второго регистра 19 памяти, второй вход - соединен со вторым входом первого элемента ИЛИ 22, с установочным входом реверсивного счетчика 7 и с выходом одновибратора 10, а выход - соединен с входом установки в ноль второго счетчика 18.

Двухпороговый компаратор 8 содержит первый 24 и второй 25 пороговые элементы, информационные входы которых объединены и являются информационным входом порогового блока 8, а входы установки пороговых уровней первого 24 и второго 25 пороговых элементов являются, соответственно, первым и вторым входами установки первого и второго пороговых уровней двухпорогового компаратора 8, а также элемент ИЛИ 26, первый и второй входы которого соединены с выходом, соответственно первого 24 и второго 25 пороговых элементов, а выход - является выходом порогового блока 8.

Промежуточные трансформаторы 1 и 3 могут иметь ту же конструкцию, что и в прототипе, первый 2 и второй 4 пороговые блоки с нулевым пороговым уровнем, а также первый 24 и второй 25 пороговые элементы могут быть выполнены в виде компараторов. Блок 16 может быть выполнен в виде двух постоянных запоминающих устройств, входы которых объединены и являются входом блока, а выходы являются его выходами. Исполнительный элемент 9 может быть выполнен в виде обмотки реле с замыкающим контактом, которая через усилитель или непосредственно соединена с выходом двухпорогового компаратора 8. Первый 20 и второй 21 формирователи импульсов формируют одиночный импульс при переходе входного сигнала с уровня логической единицы на уровень логического нуля. Остальные элементы устройства являются стандартными элементами цифровой техники. Цепи питания на чертежах опущены, как несущественные.

Работает реле направления мощности следующим образом.

В основу его работы положен принцип сравнения фаз двух сигналов - напряжения и тока от защищаемого объекта. Параметры устройства должны быть настроены на заданное время совпадения однополярных мгновенных значений этих сигналов. Так, например, сдвигу фаз, равному девяносто градусов, соответствует время совпадения в четверть периодов промышленной частоты.

При включении устройства питание подается на все его элементы, в том числе, на вход одновибратора 10, который вырабатывает одиночный импульс, поступающий на вход запуска ГТИ 11, через первый 22 и второй 23 элементы ИЛИ - на входы установки в ноль первого 13 и второго 18 счетчиков, а также на вход установки в начальное состояние реверсивного счетчика 7 и первого 14 и второго 19 регистров памяти, в которых устанавливается код, соответствующий номинальной частоте входного сигнала.

На вход промежуточного трансформатора 1 поступает входной сигнал напряжения, поэтому на выходе "больше" первого порогового блока 2 с нулевым пороговым уровнем формируется последовательность прямоугольных импульсов, длительность которых соответствует положительному полупериоду и функционально связана с частотой входного сигнала, а на выходе "меньше" - формируется последовательность прямоугольных импульсов, длительность которых соответствует половине отрицательного полупериода. Аналогично на вход промежуточного трансформатора 3 поступает входной сигнал тока, поэтому на выходе "больше" второго порогового блока 4 (с нулевым пороговым уровнем) формируется последовательность прямоугольных импульсов, длительность которых соответствует положительному полупериоду, а на выходе "меньше" - отрицательному полупериоду. Через первый элемент И 5 на суммирующий вход реверсивного счетчика 4 поступают импульсы ГТИ 9, число которых пропорционально совпадению интервалов положительных значений напряжения и тока входного сигнала. Через второй элемент И 6 на вычитающий вход реверсивного счетчика 4 поступают импульсы ГТИ 9, число которых пропорционально совпадению интервалов отрицательных значений напряжения и тока входного сигнала. Выходной код реверсивного счетчика 7 сравнивается в двухпороговом компараторе 8 с предельно допустимым значением верхнего порога Uп+ (в первом пороговом элементе 24) и с предельно допустимым значением нижнего порога Uп- (во втором пороговом элементе 25). При выходе за эти уровни на вход исполнительного элемента 9 через элемент ИЛИ 26 с выхода первого 24 или второго 25 пороговых элементов подается уровень логической единицы, что приводит к срабатыванию исполнительного элемента 9.

Кроме того, в течение сигнала с уровнем логической единицы через третий элемент И 12 на вход первого счетчика 13 поступают импульсы ГТИ 11, что позволяет сформировать в первом счетчике 13 код длительности импульса, функционально связанного с частотой напряжения. В моменты окончания этих импульсов на выходе первого формирователя 20 импульсов формируется короткий импульс, по которому содержимое первого счетчика 13 переписывается в первый регистр 14 памяти, после чего содержимое первого счетчика 13 обнуляется. Последнее обеспечивается либо работой первого регистра 14 и входа установки в ноль первого счетчика 13 по разным фронтам импульса с выхода первого формирователя 20, либо включением элемента задержки на входе установки в ноль первого счетчика 13. Аналогично, в течение сигнала с уровнем логической единицы через четвертый элемент И 17 на вход второго счетчика 18 поступают импульсы ГТИ 11, что позволяет сформировать во втором счетчике 18 код длительности импульса, функционально связанного с частотой тока в цепи. В моменты окончания этих импульсов на выходе второго формирователя 21 импульсов формируется короткий импульс, по которому содержимое второго счетчика 18 переписывается во второй регистр 19 памяти, после чего содержимое второго счетчика 18 обнуляется. Последнее обеспечивается либо работой второго регистра 19 памяти и входа установки в ноль второго счетчика 18 по разным фронтам импульса с выхода второго формирователя 21, либо включением элемента задержки на входе установки в ноль второго счетчика. Коды первого 14 и второго 19 регистров памяти взевешенно с коэффициентами 0,5 суммируются в сумматоре 15, поэтому на его выходе формируется сигнал, пропорциональный усредненной по цепям напряжения и тока длительности половине периода входного сигнала, функционально связанной с частотой входного сигнала. В блоке 16 определения порогов производится уточнение значений верхнего и нижнего допустимых пороговых уровней Uп+ и Uп-, которые используются в качестве опорных уровней для первого 24 и второго 25 пороговых элементов в двухпороговом компараторе 8.

Таким образом, предложенное устройство обладает более высокой точностью, поскольку в нем предусмотрена подстройка величин порогов срабатывания первого порогового блока в соответствии с текущей частотой входного сигнала.

Источники информации

1. Электротехнический справочник, в 4-х томах, т.2. Электротехнические изделия и устройства. Под общей редакцией В.Г. Герасимова и др. - М.: Издательство МЭИ, 1998 г., с. 390, рис. 35.10.

2. Чернобровов Н.В., Семенов В.А. Релейная защита энергетических систем. - М.: Энергоатомиздат, 1998, с. 122, рис. 2.70.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЛЕ НАПРАВЛЕНИЯ МОЩНОСТИ | 2002 |

|

RU2205466C1 |

| РЕЛЕ ЧАСТОТЫ | 2002 |

|

RU2208864C1 |

| РЕЛЕ ЧАСТОТЫ | 2002 |

|

RU2208865C1 |

| ДИФФЕРЕНЦИАЛЬНОЕ РЕЛЕ | 2003 |

|

RU2248655C1 |

| РЕЛЕ СТАТИЧЕСКОЕ МОЩНОСТИ | 2002 |

|

RU2216813C1 |

| РЕЛЕ РАЗНОСТИ ФАЗ | 2003 |

|

RU2248640C2 |

| РЕЛЕ СИНХРОНИЗАЦИИ | 2003 |

|

RU2233501C1 |

| РЕЛЕ ТОКА | 2003 |

|

RU2248653C2 |

| РЕЛЕ ЧАСТОТЫ | 2003 |

|

RU2248639C2 |

| ЭЛЕКТРОННОЕ РЕЛЕ СКОРОСТИ ИЗМЕНЕНИЯ ЧАСТОТЫ | 2002 |

|

RU2208802C1 |

Изобретение относится к области электротехники и может быть использовано в качестве реле направления мощности. Реле направления мощности содержит промежуточный трансформатор напряжения, промежуточный трансформатор тока и последовательно соединенные двухпороговый компаратор и исполнительный элемент, а также первый и второй пороговые блоки с нулевым пороговым уровнем, первый и второй элементы И, реверсивный счетчик, вход сложения которого соединен с выходом первого элемента И, вход вычитания - с выходом второго элемента И, а выход соединен с информационным входом двухпорогового компаратора, последовательно соединенные одновибратор и генератор тактовых импульсов, две последовательные цепи, каждая из которых содержит элемент И, счетчик и регистр памяти, а также первый формирователь импульсов по заднему фронту сигналов на его входе, вход которого соединен с выходом "больше" упомянутого первого порогового блока, второй формирователь импульсов по заднему фронту импульсов на его входе, вход которого соединен с выходом "больше" упомянутого второго порогового блока, и первый и второй элементы ИЛИ. Устройство обладает высокой точностью, поскольку в нем предусмотрена подстройка величин порогов срабатывания двухпорогового компаратора в соответствии с текущей частотой входного сигнала. Технический результат - повышение точности. 4 з. п.ф-лы, 1 ил.

| RU 2058658 C1, 20.04.1996 | |||

| СИНХРОННЫЙ ДЕТЕКТОР | 1997 |

|

RU2124804C1 |

| Турбобур | 1958 |

|

SU121732A1 |

Авторы

Даты

2003-07-10—Публикация

2002-02-19—Подача