Изобретение относится к области радиотехники, в частности к радиоприемным устройствам, и может быть использовано в устройствах цифровой обработки радиосигналов для оценки фазы высокочастотного заполнения с одновременным выделением огибающей узкополосных сигналов.

Известны цифровые детекторы огибающей сигнала (см., например, "Цифровой пиковый детектор" по А. С. СССР N 1118926, "Синхронный детектор" по А.С. СССР N 1272470, "Синхронный детектор" по А.С. СССР N 1706005 и др. В известных устройствах решается только задача получения значений огибающей узкополосных сигналов в цифровой форме.

Однако, в современных цифровых радиоприемных системах, реализующих адаптивную обработку сигналов, способных адаптивно менять режим и вид работы, осуществляющих, например, обработку полезного сигнала с компенсацией помех, сведений только об огибающей или только о фазе сигнала недостаточно. Для вынесения окончательного решения о принятом сигнале в них часто необходимо одновременно использовать и ту и другую информацию.

Недостаточные функциональные возможности известных синхронных детекторов обусловливают их узкую область применения. В радиоприемных системах они могут использоваться только при построении схем, реализующих некогерентный прием по огибающей. Их возможностей недостаточно для осуществления квадратурной обработки, обработки с компенсацией помех и т.д.

Наиболее близким по своей технической сущности к заявляемому является синхронный детектор по А.С. СССР N 1706005, кл. H 03 D 3/02, 3/18, 1989 г., который выбран в качестве прототипа.

Устройство прототип содержит аналого-цифровой преобразователь последовательного приближения (АЦП) и компаратор, сигнальные входы которых объединены и служат сигнальным входом устройства, последовательно соединенные первый RS-триггер, S-вход которого является входом "Запуск" устройства, первый элемент И и инвертор, последовательно соединенные генератор тактовых импульсов (ГТИ), счетчик, дешифратор, второй RS-триггер и второй элемент И, выход которого соединен с тактовым входом АЦП, а второй вход объединен со счетным входом счетчика и подключен к выходу ГТИ, причем вход R счетчика соединен с выходом инвертора, управляющий вход V счетчика соединен с выходом первого RS-триггера и входом "Запуск" АЦП, выход которого "Готовность данных" подключен к R-входу первого RS-триггера, а выход компаратора соединен с первым входом первого элемента И, кроме того АЦП имеет выход "А" отсчетов огибающей амплитуды входного сигнала в цифровой форме, являющийся выходом устройства.

Достоинствами устройства-прототипа в сравнении с указанными аналогами является наличие в его составе узлов, формирующих напряжения, на основе которых может решаться задача измерения фазы.

Недостатком устройства прототипа является узкая область его применения.

Целью изобретения является расширение области применения синхронного детектора за счет обеспечения возможности измерения в нем фазы входного сигнала с одновременным выделением его огибающей.

Поставленная цель достигается тем, что в известном синхронном детекторе, содержащем аналого-цифровой преобразователь последовательного приближения и компаратор, сигнальные входы которых объединены и служат сигнальным входом устройства, последовательно соединенные первый RS- триггер, S-вход которого является входом "Запуск" устройства, первый элемент И и инвертор, последовательно соединенные генератор тактовых импульсов, счетчик, дешифратор, второй RS-триггер и второй элемент И, выход которого соединен с тактовым входом аналого-цифрового преобразователя, а второй вход объединен со счетным входом счетчика и подключен к выходу генератора тактовых импульсов, причем вход R счетчика соединен с выходом инвертора, управляющий вход V счетчика соединен с выходом первого RS-триггера и входом "Запуск" аналого-цифрового преобразователя, выход которого "Готовность данных" подключен к R-входу первого RS-триггера, а выход компаратора соединен с первым входом первого элемента И, кроме того аналого-цифровой преобразователь последовательного приближения имеет выход "А" отсчетов огибающей амплитуды входного сигнала в цифровой форме, дополнительно введены блок согласования, синтезатор частоты, умножитель частоты и блок измерения фазы, выход которого является цифровым выходом "ϕ" значения фазы, причем первый вход блока согласования соединен с входом "Запуск" детектора, второй вход соединен с выходом компаратора, выходы "Пуск" и "Начало измерения ϕ" подключены к одноименным входам блока измерения фазы, вход которого "Опорная частота" соединен с выходом синтезатора частоты, а вход "Счетные импульсы" - с выходом умножителя частоты, входы синтезатора частоты и умножителя частоты объединены и подключены к выходу генератора тактовых импульсов.

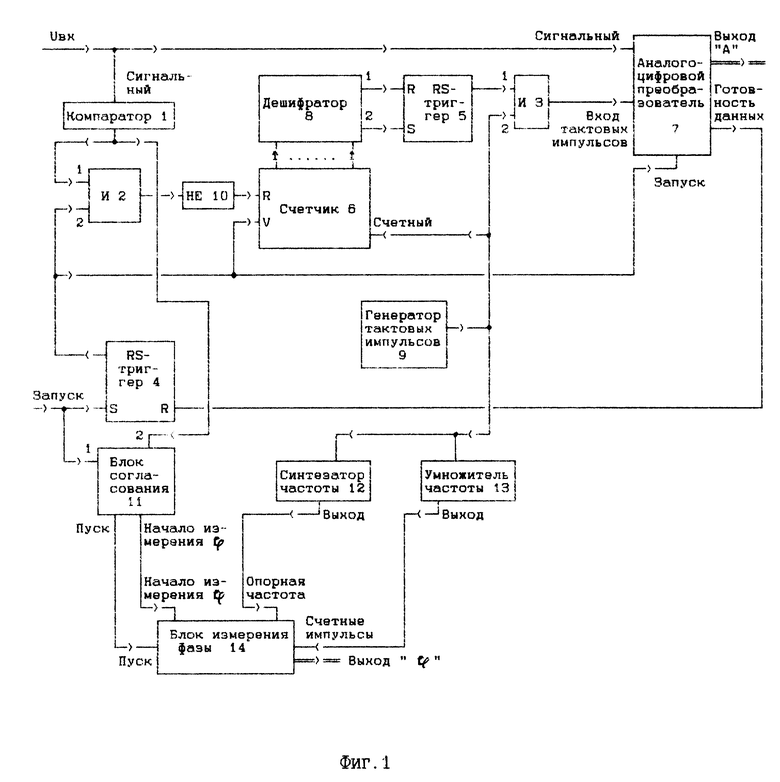

Существо предложения по расширению области возможного применения по сравнению с прототипом основывается на одновременном выполнении измерений амплитуды и фазы входного сигнала и формирование результатов измерений в цифровом виде. Заявляемое устройство поясняется чертежами

Фиг. 1 - Схема заявляемого устройства.

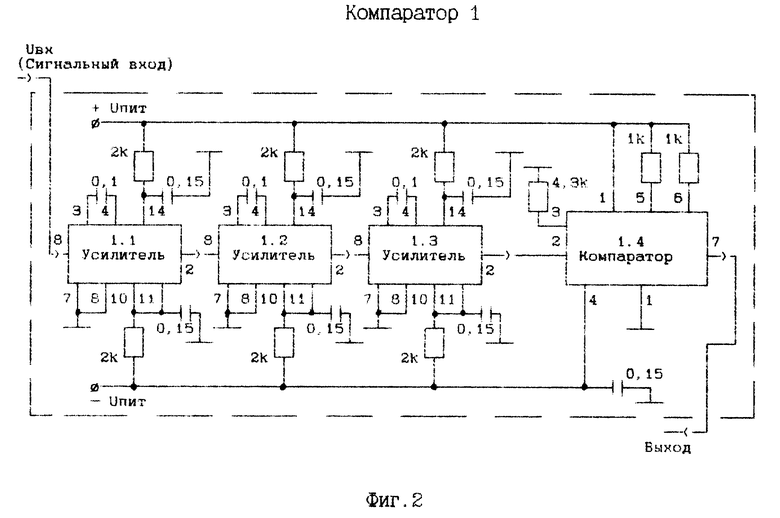

Фиг. 2 - Компаратор 1.

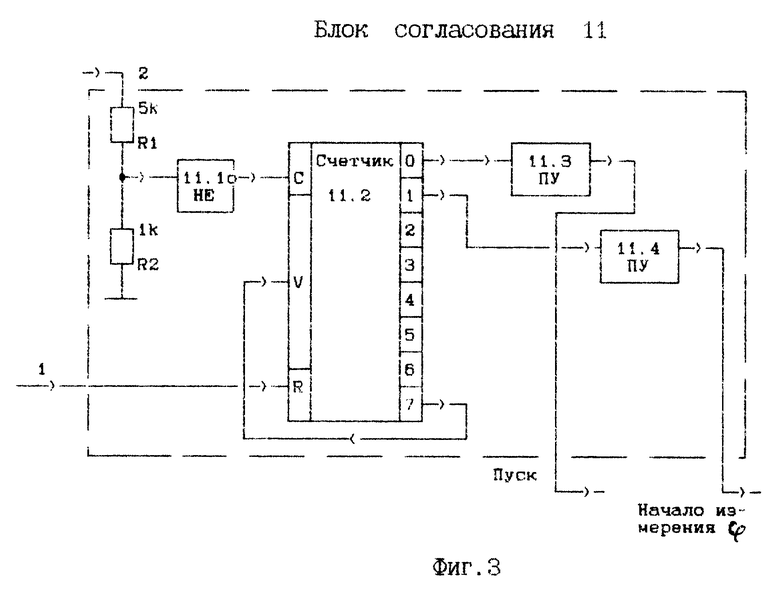

Фиг. 3 - Блок согласования 11.

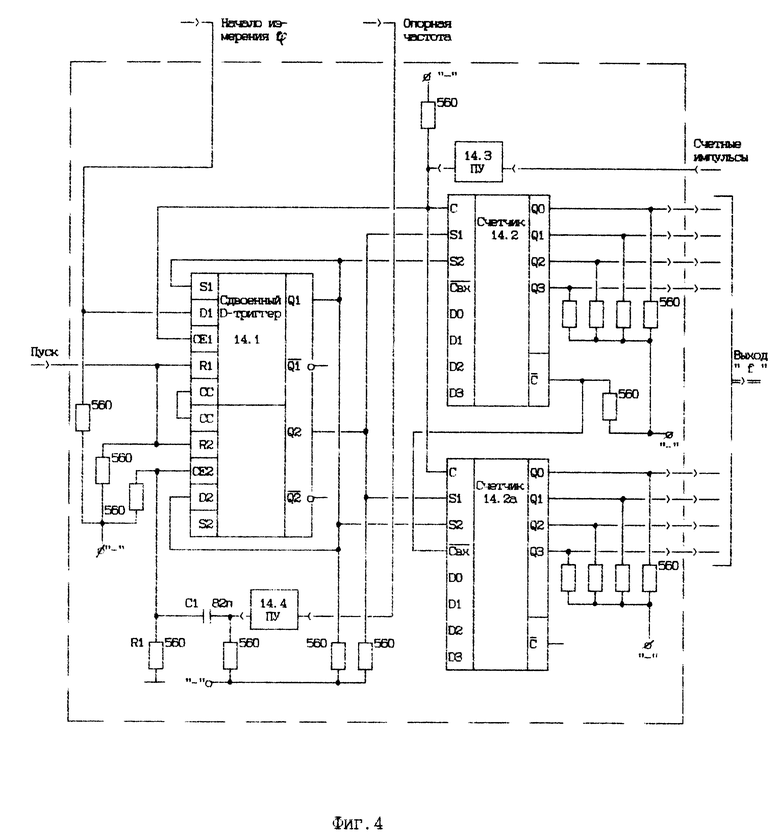

Фиг. 4 - Блок измерения фазы 14.

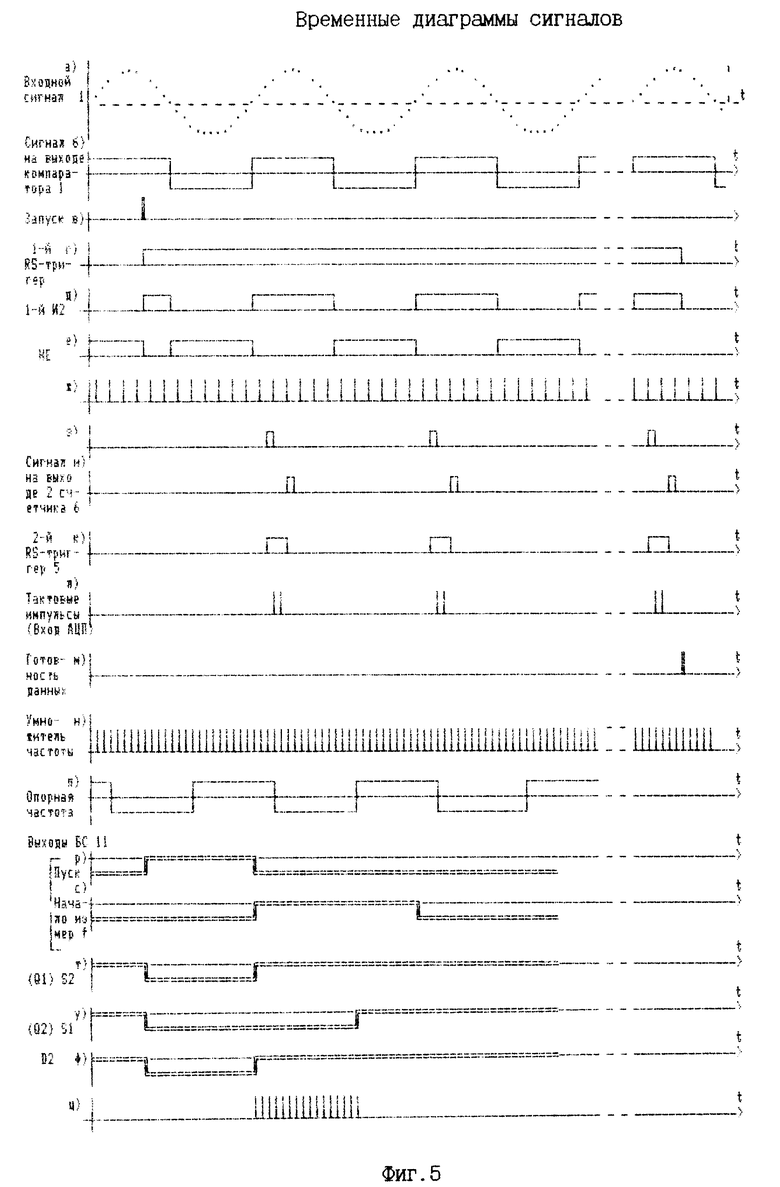

Фиг. 5 - Временные диаграммы сигналов, поясняющие принцип работы заявляемого устройства.

Синхронный детектор, показанный на фиг. 1, содержит компаратор 1, первый логический элемент И 2, второй логический элемент И 3, первый RS-триггер 4, второй RS-триггер 5, счетчик 6, аналого-цифровой преобразователь последовательного приближения (АЦП) 7, дешифратор 8, генератор тактовых импульсов (ГТИ) 9, инвертор 10, блок согласования 11, синтезатор частот (СЧ) 12, умножитель частоты (УЧ) 13, блок измерения фазы (БИФ) 14. Сигнальные входы компаратора 1 и АЦП 7 объединены и служат сигнальным входом устройства. Выход компаратора 1 соединен с первым входом первого элемента И 2 и вторым входом блока согласования 11, выходы которого "Пуск" и "Начало измерения ϕ" подключены к одноименным входам БИФ 14. Второй вход первого элемента И 2 соединен с входом V (управляющим входом) счетчика 6, входом "Запуск" АЦП 7 и подключен к выходу первого RS-триггера 4, R-вход (обнуляющий вход) которого соединен с выходом "Готовность данных" АЦП 7. Выход элемента И 2 через инвертор 10 соединен с обнуляющим R-входом счетчика 6, выходы которого подключены к дешифратору 8. Счетный вход счетчика 6 соединен с вторым входом второго элемента И 3, входом умножителя 13, входом синтезатора частоты 12 и подключен к выходу ГТИ 9. Первый и второй выходы дешифратора 8 соединены с S и R входами второго RS-триггера 5 соответственно. Выход RS-триггера 5 подключен к первому входу второго элемента И 3. Выход второго элемента И 3 соединен с входом тактовых импульсов (вх.ТИ) АЦП 7. Выход СЧ 12 подключен к входу "Опорная частота" БИФ 14. Выход умножителя частоты 13 соединен с входом счетных импульсов БИФ 14. Информационный выход АЦП 7 является выходом "А" синхронного детектора, на котором формируется цифровое значение амплитуды входного сигнала. Вход S первого RS-триггера 4 и вход "Пуск" блока согласования 11 объединены и являются входом "Запуск" синхронного детектора. Выход БИФ 14 является выходом "ϕ" синхронного детектора, на котором формируются цифровые значения фазы входного сигнала.

На фиг. 2 показана схема компаратора 1, предназначенного для выделения моментов пересечения входным сигналом нулевого уровня. Схема содержит последовательно соединенные 3 усилители 1.1 - 1.3 и собственно компаратор 1.4. Вход первого усилителя 1.1 является входом компаратора 1. Выход компаратора 1.4 является выходом блока 1. Усилители 1.1-1.3 могут быть выполнены на интегральных микросхемах 435УН1 с дифференциальным входом, которые хорошо работают в качестве усилителей-ограничителей, см., например, книгу "Функциональные устройства на интегральных микросхемах дифференциального усиления". Под ред. В.3. Найдерова.- М.: Сов. радио, 1977, с. 37. Компаратор 1.4 обеспечивает наиболее резкое переключение уровня выходного напряжения за счет весьма высокой скорости нарастания выходного сигнала и очень малого времени восстановления, что обеспечивает хорошее совпадение фронтов напряжения на выходе компаратора с положением пересечения входным сигналом нулевого уровня. Компараторы описаны, например, в книге "Аналоговые и цифровые интегральные микросхемы". Справочное пособие. Под ред. С.В. Якубовского. - 2-е изд. перераб. и доп. - М.: Радио и связь, 1985, на стр. 305-307. Схема использованного компаратора 521 САЗ показана в названной книге на стр. 311 рис. 6.30.

Схемы логических элементов И 2, 3, RS-триггеры 4, 5 и инвертора 10 известны и описаны, см., например, в книге Шило B.Л. "Популярные цифровые микросхемы" Справочник - М. : Радио и связь, 1987, на стр. 34-44, стр. 74 и стр. 26-27 соответственно.

Счетчик 6 и дешифратор 8 предназначены для формирования выходных импульсов, положение которых на временной оси совпадает с положением амплитуды колебания входного сигнала. Такие счетчики и дешифраторы известны, описаны, например, в упомянутой выше книге Шило В. Л. на стр. 239-240. На рис. 2.40 показана схема подобного счетчика с дешифратором. Счетчик 6 и дешифратор 8, в частности, могут быть реализованы на микросхеме 564ИЕ9.

Аналого-цифровой преобразователь последовательного приближения 7 предназначен для формирования в цифровом коде значения амплитуды входного сигнала. Подобные АЦП известны, описаны, например, в книге "Аналоговые и цифровые интегральные микросхемы". Справочное пособие. Под ред. С.В. Якубовского. - 2-е издание перераб. и дополненное, М.: Радио и связь, 1982, на стр. 361-363. На рис. 6.88 показана схема такого АЦП. АЦП 7, в частности, может быть реализован на интегральной микросхеме К1108ПВ1.

ГТИ 9 предназначен для выработки опорных тактовых импульсов, на основе которых формируются сигналы, обеспечивающие управление во времени работой блоков заявляемого устройства. В качестве ГТИ 9 могут быть использованы опорные генераторы. Схемы опорных генераторов известны и описаны, например, в книге Павлова К. М. "Радиоприемные устройства магистральной КБ связи". Учебное пособие для техникумов связи. М.: Связь, 1980, стр. 83-84, на рис. 2.30 показана и описана функциональная схема широко распространенного опорного генератора "Гиацинт".

Блок согласования 11 предназначен для согласования сигналов по уровням и во времени в блоке измерения фазы 14 с сигналами, формируемыми в других блоках синхронного детектора. Схема блока согласования 11 показана на фиг. 3. Схема включает: делитель напряжения на сопротивлениях R1 и R2, инвертор 11.1, счетчик 11.2 и два преобразователя уровней 11.3 и 11.4. Средняя точка сопротивлений делителя на R1 и R2 соединена со входом инвертора 11.1, выход которого подключен к входу "С" (счетному входу) счетчика 11.2. Выходы "0" и "1" счетчика 11.2 подключены к входам ПУ 11.3 и ПУ 11.4 соответственно. Выход ПУ 11.3 является выходом "Пуск" блока согласования 11, а выход ПУ 11.4 - с выходом "Начало измерения ϕ". R-вход (обнуляющий вход) счетчика 11.2 является первым входом блока согласования 11. Вход делителя на сопротивлениях R1 и R2 является вторым входом блока согласования 11. Все эти устройства описаны в упомянутой выше книге Шило B.Л, в частности, преобразователи уровней представлены на стр. 304-305 данной книги.

Синтезатор частоты (СЧ) 12 предназначен для формирования двухуровневого опорного сигнала с частотой, равной частоте входного сигнала. Для обеспечения хорошего совпадения частоты опорного сигнала с частотой входного необходим синтезатор частот с мелким шагом сетки частот. Такие синтезаторы описаны, например, в книге "Цифровые радиоприемные системы". Справочник. Под ред. М.И. Жодзижского. - М.: Радио и связь, 1990, стр. 71-74, а на рис. 3.7 стр. 72 показана функциональная схема, по которой, в частности, может быть построен СЧ 11. Синтезатор частоты, построенный по вышеназванной схеме, изготовлен Российским институтом мощного радиостроения, децимальный номер принципиальной схемы EP2 329.008 Э3. Разряды кодового слова (целая часть и дробная часть), управляющего частотой выходного сигнала синтезатора, формируются непосредственно в синтезаторе. Для этого соответствующие разряды кодового слова присоединяются к источнику напряжения, формирующего уровни логических нуля и единицы.

Умножитель частоты 13 предназначен для формирования счетных импульсов, используемых в блоке измерения фазы 14 для оценки рассогласования входного колебания и опорного. Умножители частоты известны, они описаны, например, в книге "Функциональные устройства на интегральных микросхемах дифференциального усиления". Под ред. В. З. Найдерова.- М.: Сов. радио, 1977, стр. 61-66. В частности, умножитель частоты 13 может быть реализован по схеме, показанной на рис. 3.6 стр. 65 вышеназванной книги.

Блок измерения фазы (БИФ) 14 показан на фиг. 4 и предназначен для измерения в цифровом коде временного промежутка между моментами пересечения нулевого уровня положительным фронтом входного сигнала и опорного сигнала. БИФ 14 содержит сдвоенный D-триггер 14.1, счетчики 14.2 и 14.2а, два преобразователя уровней 14.3 и 14.4. Выход ПУ 14.4 через дифференциальную цепь C1, R1 соединен с тактовым входом СЕ2 D-триггера 14.1, информационный вход D2 и управляющий вход S1 которого соединены с собственным выходом Q1, а также с управляющими входами S2 счетчиков 14.2 и 14.2а. Выход Q2 D-триггера 14.1 подключен к управляющим входам S1 счетчиков 14.2 и 14.2а, счетные входы "С" которых объединены и подключены к выходу ПУ 14.3. Выход переноса "С" счетчика 14.2 соединен с входом Свх счетчика 14.2а. Обнуляющие входы R1 и R2 сдвоенного D-триггера 14.1 объединены и являются входом "Пуск" БИФ 14. Вход "Начало измерения ϕ" соединен с входом информационным входом D1 D-триггера 14.1. Вход ПУ 14.4 является входом "Опорная частота" БИФ 14. Вход ПУ 14.3 является входом "Счетные импульсы" БИФ 14. Выходы Q0, Q1, Q2, Q3 счетчиков 14.2, 14.2а образуют выход "ϕ" цифрового кода фазы. Для получения высокого быстродействия в схеме БИФ 14 наиболее целесообразно использовать микросхемы эмиттерно-связанной логики (ЭСЛ), требующие внешних нагрузочных резисторов, которые могут быть выбраны в широких пределах (300 Ом - 30 кОм), в схеме БИФ 14 эти сопротивления выбраны по 560 Ом. Такие схемы описаны в упоминавшейся уже книге Шило В.Л. на стр. 291-330, в частности сдвоенный D-триггер описан на стр. 309-310, рис. 3.19, счетчик на стр. 313-314, рис. 3.23 а), преобразователи уровней - на стр. 305 рис. 3.14.

Заявляемое устройство работает следующим образом.

Детектируемый сигнал, см. фиг. 5а, поступает на вход компаратора 1, где в результате усиления и ограничения входное синусоидальное колебание преобразуется в напряжение прямоугольной формы, см. фиг. 5б, которое поступает на первый вход первого логического элемента И 2 и второй вход блока согласования 11. Импульс запуска (см. фиг. 5в) поступает на S-вход первого RS-триггера 4 и первый вход блока согласования 11. При поступлении импульса запуска RS-триггер 4 срабатывает и на его выходе формируется потенциал, поступающий на второй вход первого элемента И 2, на вход управления (вход V) счетчика 6 и на вход "Запуск" АЦП 7, подготавливая работу блоков детектора, связанную с формированием отсчета амплитуды входного сигнала. Работа устройства в этой части в точности соответствует описанию синхронного детектора A.C. N 1706005 (см. описание изобретения и временные диаграммы на фиг. 5а - 5м).

Как указано в описании известного синхронного детектора, он предназначен для использования в устройствах обработки узкополосных сигналов, для которых характерно медленное по сравнению с периодом высокочастотного заполнения изменение огибающей и фазы. См., например, книгу И.О. Гоноровского "Радиотехнические цепи и сигналы". ч.II - М.: Советское радио, 1967, стр. 184-187. На интервале нескольких периодов колебания огибающая и фаза входного узкополосного сигнала практически не изменяются. Это позволяет получить приемлемую точность оценки фазы входного сигнала путем измерения временного промежутка между моментами пересечения нулевого уровня входным и опорным сигналами. Цифровые отсчеты фазы формируются путем непосредственного счета импульсов, которые могут быть пропущены за упомянутый выше временной промежуток на вход счетчика.

Выбор частоты следования счетных импульсов зависит от требуемой точности измерения фазы, частота счетных импульсов должна быть по крайней мере на порядок выше частоты входного колебания.

Положение пересечений входным сигналом нулевого уровня весьма точно задаются положениями фронтов сигнала на выходе компаратора 1.

В качестве опорного сигнала использован двухуровневый сигнал с выхода синтезатора частоты 12. Счетные импульсы имеют частоту 60 МГц и сформированы в умножителе частоты 13 путем умножения на 12 частоты опорного колебания с выхода ГТИ 9, равной 5 МГц. Для узкополосного сигнала, обрабатываемого на промежуточной частоте, например, 300 КГц, такое соотношение частоты счетных импульсов и частоты входного сигнала позволяет получить точность измерения фазы примерно 1,8o. Самое большое значение цифрового кода фазы - 11000111, которое соответствует 358,2o.

Сигнал "Запуск", поступающий на первый вход блока согласования 11, см. фиг. 3 и фиг. 5в, подается на обнуляющий вход R счетчика 11.2 и устанавливает его в исходное положение. При этом на нулевом выходе счетчика 11.2 формируется напряжение логической единицы, которое через преобразователь уровня 11.3 (от ТТЛ к ЭСЛ) передается на выход "Пуск" блока согласования 11 и далее на соответствующий вход "Пуск" блока измерения фазы 14, см. фиг. 5р.

Входной сигнал поступает на блок измерения фазы 14, пройдя компаратор 1 и блок согласования 11. Сигнал с выхода компаратора 1, сохраняющий полностью информацию о фазе входного сигнала (см. фиг .1 и фиг. 5б), поступает на второй вход блока согласования 11 (см. фиг. 3). В блоке согласования 11 входной сигнал поступает на делитель напряжения на сопротивлениях R1, R2 и далее через инвертор 11.1 - на счетный вход счетчика 11.2. Первый положительный фронт входного сигнала, который поступит после импульса "Запуск", переводит счетчик 11.2 в положение, при котором формируется сигнал на первом выходе счетчика (на нулевом выходе счетчика 11.2 сигнал при этом пропадает). Сигнал на первом выходе счетчика 11.2 несет в себе информацию о моменте пересечения нулевого уровня положительным фронтом входного сигнала. После преобразования уровня сигнала (во втором преобразователе 11.4) при полном сохранении информации о фазе этот сигнал поступает через выход "Начало измерения ϕ" блока 11 на одноименный вход блока измерения фазы 14.

Процесс формирования цифрового значения амплитуды в описываемом синхронном детекторе занимает несколько периодов колебаний входного сигнала (см. а. с. N 1706005). Измерение фазы осуществляется за время, не превышающее длительности одного периода входного сигнала. Благодаря элементам блока согласования 11 измерение фазы в блоке 14 происходит один раз после поступления на синхронный детектор импульса "Запуск", а не по каждому положительному фронту входного сигнала. После окончания действия импульса "Запуск" поступающие на счетный вход счетчика 11.2 импульсы, формируемые по положительному фронту входного сигнала, переводят счетчик последовательно в состояния, при которых выходное напряжение появляется на первом, втором, третьем,..., седьмом его выходах. Сигнал о начале измерения фазы формируется только при прохождении первого после импульса "Запуск" положительного фронта входного сигнала, а после прохождения седьмого (в нашем случае) положительного фронта счетчик 11.2 переводится в состояние, при котором счетные импульсы вообще не будут восприниматься им до тех пор, пока на обнуляющий вход R счетчика не поступит импульс сброса - новый импульс "Запуск". Таким образом, блок согласования 11 осуществляет согласование работы во времени, согласование по уровням осуществляется с помощью делителя напряжения и преобразователей уровня.

В БИФ 14 сигнал "Пуск" поступает на обнуляющие входы R1 и R2 сдвоенного D-триггера 14.1, последний при этом устанавливается в положение, когда на его обоих выходах Q1 и Q2 устанавливается уровень логической единицы (низкий уровень для ЭСЛ микросхем). Следовательно, такой же низкий уровень устанавливается на подключенных к выходам Q1 и Q2 D-триггера 14.1 управляющих входах S1 и S2 счетчиков 14.2 и 14.2а, см. фиг. 5т и 5у.

При низком уровне на обоих управляющих входах S1 и S2 счетчики 14.2 и 14.2а ставятся в режим предварительной установки, при котором в случае отсутствия низкого уровня на информационных входах D на выходах счетчиков устанавливается уровень логического нуля. Таким образом, БИФ 14 переводится в состояние предварительной установки. В этом состоянии первый положительный фронт входного сигнала, пересекающий нулевой уровень, фиксирует начало временного промежутка, с помощью которого измеряется фаза входного колебания. По первому положительному фронту сигнала с выхода компаратора 1, поступившему на второй вход блока согласования (БС) 11, переключается счетчик 11.2 (см. фиг. 3): напряжение логической единицы на нулевом выходе счетчика 11.2 снимается и устанавливается на его первом выходе, и как следствие, на выходе преобразователя уровня 11.4, то есть на выходе "Начало измерения ϕ" блока согласования 11, см. временную диаграмму на фиг. 5с. Сигнал "Начало измерения ϕ" (смена потенциала с низкого на высокий) с выхода БС 11 поступает на соответствующий вход БИФ 14, а в нем - на информационный вход D1 D-триггера 14.1 (см. фиг. 4). Работа БИФ 14 строго синхронизирована счетными импульсами, поступающими на его счетный вход от умножителя частоты 13. По первому положительному перепаду счетных импульсов, которые в БИФ 14 проходят через преобразователь уровня 14.3 и поступают на тактовый вход СЕ1 D-триггера, происходит перенос уровня с информационного входа D1 D-триггера на его выход Q1. На выходе Q1 устанавливается высокий уровень, этот же уровень устанавливается на информационном входе D2 D-триггера 14.1 и на управляющих входах S2 счетчиков 14.2 и 14.2а (см. фиг. 5т). При высоком уровне на S2 и низком уровне на S1 для счетчиков 14.2 и 14.2а устанавливается режим счета на увеличение.

Окончание временного промежутка измерения фазы фиксируется по первому моменту пересечения нулевого уровня положительным фронтом опорного напряжения (см. временную диаграмму фиг.5п), поступающего на вход "Опорная частота" БИФ 14 от СЧ 12.

Опорное напряжение прямоугольной формы, вырабатываемое СЧ 12 и поступающее на вход "Опорная частота" БИФ 14, после преобразования уровня в преобразователе 14.4 дифференцируется на цепи С1, R1. Импульс, формируемый по первому положительному перепаду опорного напряжения, поступает на вход тактовый вход СЕ2 D- триггера 14.1, по нему переносится на выход Q2 высокий уровень с информационного входа D2, который был установлен в момент начала времени измерения фазы. В результате на управляющих входах S1 счетчиков 14.2 и 14.2а также устанавливается высокий уровень, см. фиг. 5п и 5у. С этого момента прекращается работа счетчиков 14.2 и 14.2а, а на его выходах (Q0, Q1, Q2, Q3) сформировано 8-разрядное кодовое слово, соответствующее величине фазового сдвига входного сигнала по отношению к опорному.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1997 |

|

RU2115135C1 |

| ЧАСТОТНО-АДАПТИВНАЯ РАДИОЛИНИЯ ДЛЯ ПЕРЕДАЧИ СРЕДНЕСКОРОСТНЫХ ПОТОКОВ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1998 |

|

RU2142200C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1996 |

|

RU2114501C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2144267C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА СИГНАЛОВ РАДИОСТАНЦИЙ | 1998 |

|

RU2132111C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1998 |

|

RU2132567C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ ПОМЕХ | 1994 |

|

RU2097921C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

Изобретение относится к радиотехнике, а именно к технике радиосвязи, и предназначено для использования в составе устройств цифровой обработки сигналов при обработке узкополосных сигналов с компенсацией помех при приеме сигналов с фазоразностной модуляцией. В синхронный детектор, который содержит аналого-цифровой преобразователь (АЦП) (7), компаратор 1, RS-триггеры (4) и (5), элементы И (2) и (3), инвертор (10), генератор тактовых импульсов (9), счетчик (6), дешифратор (8), дополнительно введены блок согласования (11), синтезатор частоты (12), умножитель частоты (13) и блок измерения фазы (14). Сигнальные входы компаратора (1) и АЦД(7) объединены и являются сигнальным входом устройства. В блоках (1,...,8, 10, ... 13) производится обработка входного сигнала и формируются напряжения, управляющие работой устройства в целом. В блоках (7,14) соответственно оценивается огибающая и фаза входного сигнала, формируются результаты измерения в цифровом виде. Технический результат: расширение области применения синхронного детектора путем обеспечения возможности измерения в нем фазы входного сигнала с одновременным выделением его огибающей. 1 з.п. ф-лы, 5 ил.

| Синхронный детектор | 1989 |

|

SU1706005A1 |

| Елизаров А.С | |||

| Электрорадиоизмерения.-Минск, Высшая школа, 1986, с.156, рис.6, 13а, 6, 14б | |||

| Домрачев В.Г | |||

| и др | |||

| Схемотехника цифровых преобразователей перемещений: Справочное пособие.-М.: Энергоатомиздат, 1987, с.76, рис.5.2 | |||

| Кукуш В.Д | |||

| Электрорадиоизмерения.-М.: Радио и связь, 1985, с.215, рис.8.13 | |||

| Измерения в электронике: Справочник./Под ред | |||

| В.А.Кузнецова.-М.: Энергоатомиздат, 1987, с.330 | |||

| Цифровой фазометр | 1985 |

|

SU1278733A1 |

| Устройство счета фазовых циклов | 1986 |

|

SU1337819A1 |

Авторы

Даты

1999-01-10—Публикация

1997-02-24—Подача