Изобретение относится к технике защиты различных объектов от доступа посторонних лиц, в частности электронно-кодовым замком.

Известно устройство управления электронным замком (см. патент РФ 2057246 от 18.12.92 г., МПК: Е 05 В 47/00, "Электронный замок", А.Н.Юскаев, опубл. 27.03.96 г. , БИ 9), содержащее блок запрета, блок устранения дребезга, блок выдержки, коммутатор, блок счетчиков, блок эталонного кода, счетчик количества наборов ложного кода и элемент задержи. Вход блока устранения дребезга соединен с входной шиной устройства и входом блока защиты, выходом подключенного к первым входам блока счетчиков и счетчика количества наборов ложного кода, выход которого через элемент задержки подключен к первой выходной шине устройства, которая соединена со вторым входом счетчика количества наборов ложного кода. Выход блока устранения дребезга через блок выдержки подключен ко вторым входам блока счетчиков и блока запрета, третьим входом подключенного к выходу блока эталонного кода. Выход блока устранения дребезга соединен с первым входом коммутатора, первым выходом подключенного к третьему входу блока счетчиков, второй выход которого соединен с входом блока эталонного кода. Коммутатор вторым входом соединен с первым выходом блока счетчиков, а вторым выходом через блок переключения глубины кода - со второй выходной шиной устройства.

Недостатками устройства управления электронным замком являются:

а) ограниченность функциональных возможностей, обусловленная тем, что в случае отказа любого из элементов хранения символов ("1", "0") эталонного кода (контактных переключателей) замок нельзя открыть, поскольку его схемотехническим решением не предусмотрена возможность оперативной смены эталонного кода и открытия его запасным кодом (запасными кодами);

б) относительно низкая надежность, обусловленная сложностью схемотехнического решения отдельных функциональных узлов, например, блока счетчиков, являющейся следствием выбранного алгоритма работы, и наличием в его составе большого количества контактных переключателей (например, в блоке эталонного кода их количество равно количеству разрядов кода, в блоке переключения глубины кода их две), которым свойственны низкая надежность и ограниченность ресурса; при этом при увеличении секретности замка путем увеличения разрядов кодов количество указанных элементов увеличивается соответственно.

Наиболее близким по совокупности существенных признаков к заявляемому изобретению является выбранное в качестве прототипа устройство управления электронным замком (см. авт. свид. СССР 1612069 от 10.10.88 г., МКП: Е 05 В 49/00, 47/02, "Электронный замок", авторы - М.Я.Вертлиб и Ф.Г.Гордон, опубл. 07.12.90 г. , БИ 45), содержащее триггер, n-разрядный сдвиговый регистр, (n-1) кодирующих элементов, четыре элемента И, элемент ИЛИ-НЕ и инвертор. Прямой выход триггера соединен с информационным входом n-разрядного сдвигового регистра, прямые выходы с первого по (n-1)-й разряд которого соединены с первыми контактами соответствующих кодирующих элементов, и инверсные выходы соединены со вторыми контактами соответствующих кодирующих элементов, третьи контакты которых соединены с соответствующими входами первого элемента И. Первый вход второго элемента И соединен с первой входной шиной устройства, выход - с S-входом триггера, инверсный выход которого соединен со вторым входом второго элемента И, третий вход которого соединен с второй входной шиной устройства и первыми входами элемента ИЛИ-НЕ и третьего элемента И. Второй вход третьего элемента И подключен к третьей входной шине устройства и к второму входу элемента ИЛИ-НЕ. Выход третьего элемента И соединен с R-входами триггера и сдвигового регистра, выход элемента ИЛИ-НЕ соединен с входами синхронизации триггера и сдвигового регистра. Прямой выход n-го разряда сдвигового регистра соединен с n-м входом первого элемента И и первым входом четвертого элемента И. Выход первого элемента И соединен с первой выходной шиной устройства и через инвертор - со вторым входом четвертого элемента И, выход которого соединен со второй выходной шиной.

Из описания устройства управления электронным замком следует, что совокупность первого (многовходового) элемента И и (n-1) кодирующих элементов, подвижные контакты которых соединены с соответствующими входами первого элемента И, а неподвижные контакты - с прямыми и инверсными выходами соответствующих разрядов сдвигового регистра, является по сути блоком сравнения кодов и блоком памяти (эталонного кода замка), выходами соединенный с соответствующими входами блока сравнения кодов.

Недостатками устройства управления электронным замком являются:

а) низкая надежность, обусловленная наличием в его составе (n-1) кодирующих элементов (контактных переключателей), которым присущи низкая надежность, например, по сравнению с электронными коммутаторами, и ограниченность ресурса; при этом по мере увеличения количества разрядов сравниваемых кодов, например, для повышения секретности устройства, количество этих переключателей соответственно увеличивается, что ведет к дальнейшему снижению надежности устройства;

б) ограниченность функциональных возможностей, обусловленная тем, что устройство не обладает свойством, позволяющим оперативно открывать управляемое им исполнительное устройство замка в случае отказа хотя бы одного из кодирующих элементов, например, другим (запасным) кодом;

в) низкий уровень защищенности устройства от подбора кода посторонним лицом, поскольку устройство не имеет никакой активной защиты от подбора кода, кроме одной пассивной защиты - тревожной сигнализации;

г) определенное неудобство при эксплуатации, обусловленное необходимостью обязательной установки устройства в исходное состояние перед каждым набором кода.

Задачей, на решение которой направлено заявляемое изобретение, является создание более надежного, с расширенными функциональными возможностями, защищенного от подбора кода и удобного в эксплуатации устройства управления электронным замком, управляемого двоичным последовательным кодом.

Технический результат, заключающийся в повышении надежности, степени защищенности от подбора кодов, удобства эксплуатации и расширении функциональных возможностей устройства управления электронным замком, достигается тем, что в устройство управления электронным замком, содержащее две входные шины и две выходные шины, первая из которых соединена с первым выходом блока сравнения кодов, первая и вторая группы входов которого подключены к соответствующим выходам первого сдвигового регистра и блока памяти соответственно, введены второй сдвиговый регистр, мультиплексор, блок управления и счетчик, выходы разрядов которого, начиная с К-го, где К=1, 2,..., соединены с соответствующими адресными входами блока памяти и мультиплексора, выход которого соединен с информационным входом первого сдвигового регистра, информационные входы соединены с соответствующими выходами второго сдвигового регистра, информационный вход которого подключен к первой входной шине устройства, вторая входная шина которого соединена с первым входом блока управления, второй вход которого соединен с первой выходной шиной устройства, вторая выходная шина которого соединена со вторым выходом блока сравнения кодов и счетным входом счетчика, вход сброса которого соединен с первым выходом блока управления, второй выход которого соединен с тактовым входом блока сравнения кодов, третий и четвертый выходы соединены, соответственно, с входами сброса и тактовыми входами сдвиговых регистров.

Указанная совокупность признаков устройства позволяет:

а) повысить надежность устройства за счет исключения из его состава имеющих низкую надежность и ограниченный ресурс контактных кодирующих элементов (переключателей) и выполнения блока памяти в виде одного электронного ПЗУ, практически независимо от количества эталонных кодов и их разрядности;

б) расширить функциональные возможности устройства за счет нового свойства, позволяющего, при необходимости, использовать запасной эталонный код и разблокировать управляемое им исполнительное устройство соответствующим запасным кодом; способствует расширению функциональных возможностей устройства и возможность управления устройством двоичным последовательным кодом не только вручную от двух кнопочных переключателей, но и от автоматизированных систем;

в) повысить уровень защищенности устройства от подбора кода посторонним лицом за счет смены эталонного кода в случаях, когда количество попыток подбора кода превышает заданное;

г) повысить удобство эксплуатации устройства благодаря исключению необходимости установки его в исходное состояние перед каждым набором (вводом) кода за счет автоматической установки в исходное состояние при включении питания, после каждого цикла ввода кода и активного удержания в исходном состоянии между вводами кодов; способствует повышению удобства эксплуатации устройства и указанное выше расширение его функциональных возможностей, поскольку позволяет, при необходимости, оперативно разблокировать управляемое им исполнительное устройство в таких случаях, когда из-за отказа ячейки памяти в блоке памяти искажен хотя бы один символ эталонного кода или постоянный пользователь забыл какой-либо из символов кода.

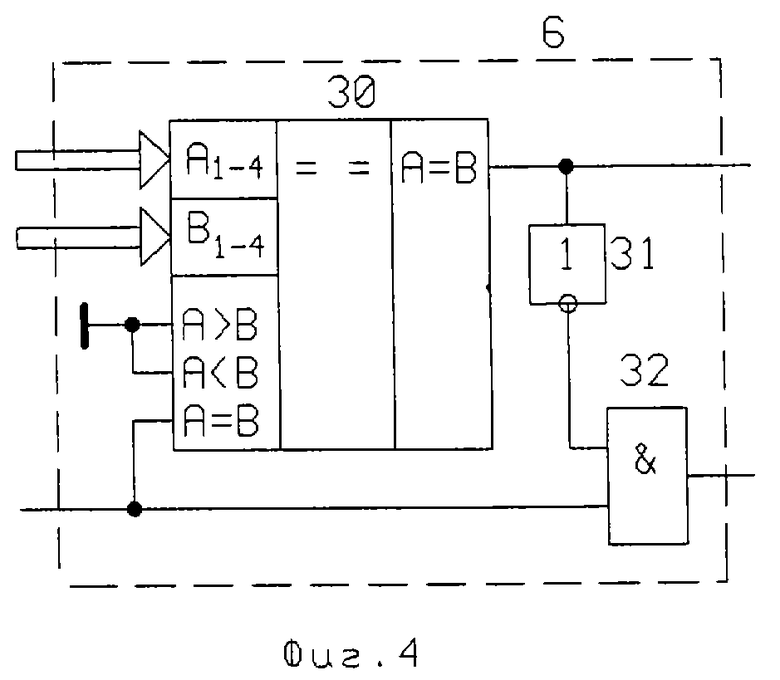

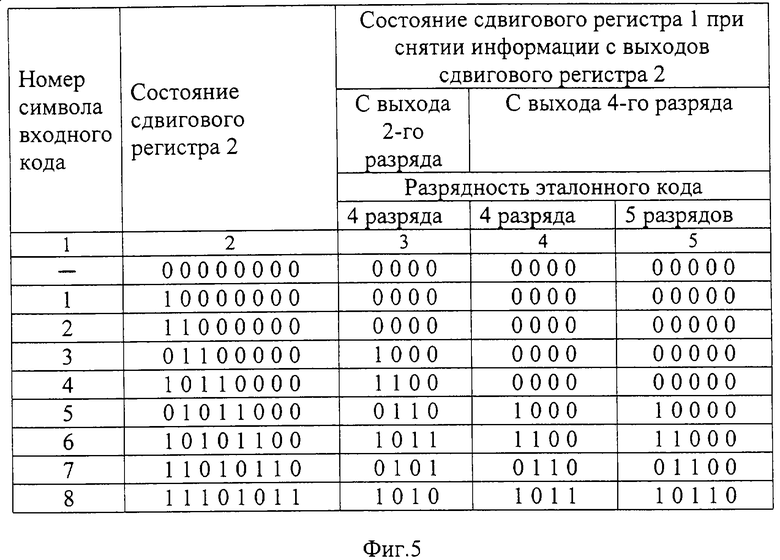

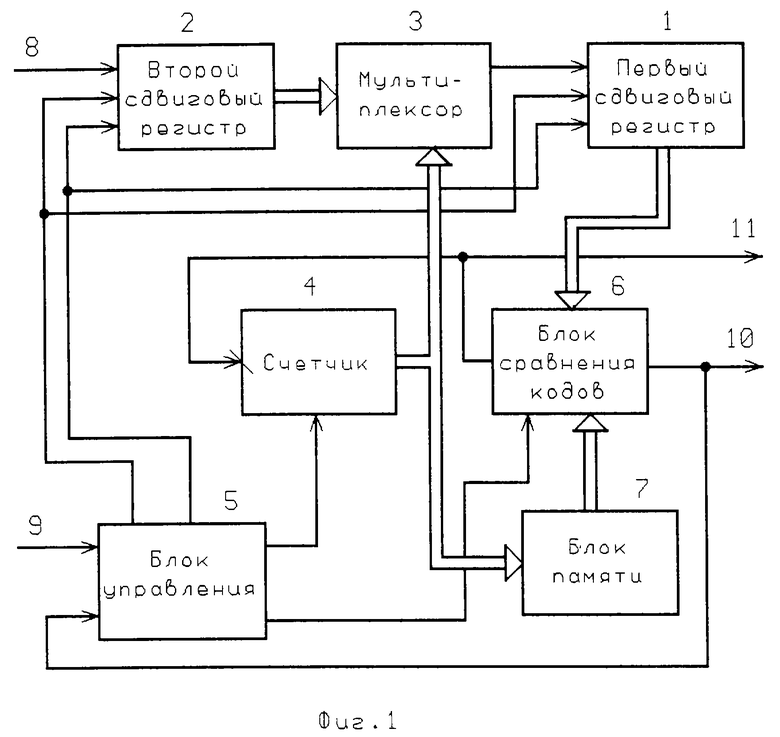

На фиг. 1 приведена структурная схема устройства управления электронным замком; на фиг.2-4 приведены возможные варианты электрических схем функциональных блоков и элементов устройства; на фиг.5 - состояния разрядов сдвиговых регистров в процессе ввода кода.

Устройство содержит (см. фиг.1) первый 1 и второй 2 сдвиговые регистры, мультиплексор 3, счетчик 4, блок 5 управления, блок 6 сравнения кодов и блок 7 памяти. Информационный вход сдвигового регистра 2 соединен с первой входной шиной 8 устройства. Второй вход блока 5 управления соединен с первым выходом блока 6 сравнения кодов, первый вход - со второй входной шиной 9 устройства, первый выход - с входом сброса счетчика 4, второй выход - с тактовым входом блока 6 сравнения кодов, третий и четвертый выходы соединены, соответственно, с входами сброса и тактовыми входами сдвиговых регистров 1, 2. Выходы сдвигового регистра 2 соединены с соответствующими информационными входами мультиплексора 3, выход которого соединен с информационным входом сдвигового регистра 1. Первая группа входов блока 6 сравнения кодов подключена к соответствующим выходам сдвигового регистра 1, вторая группа входов - к соответствующим выходам блока 7 памяти, первый выход соединен с первой выходной шиной 10 устройства, второй выход - со второй выходной шиной 11 устройства и счетным входом счетчика 4. Выходы разрядов счетчика 4, начиная с К-го, где К=1, 2,..., соединены с соответствующими адресными входами мультиплексора 3 и блока 7 памяти.

Сдвиговый регистр 2 предназначен для приема и хранения входного кода, сдвиговый регистр 1 - для приема и хранения части входного кода, сравниваемой с эталонным кодом. Эти сдвиговые регистры могут быть выполнены по любой из известных схем сдвиговых регистров с последовательным вводом и параллельным выводом информации (например, типа 564ИР2, 564ИР9, 533ИР8, 1564ИР8, включая их, при необходимости, последовательно). Количество разрядов сдвигового регистра 2 должно быть не менее количества разрядов входного кода, а у сдвигового регистра 1 - не менее количества разрядов эталонного кода и, по меньшей мере, на единицу меньше количества разрядов сдвигового регистра 2. Запись и сдвиг информации в обоих сдвиговых регистрах происходит по фронту тактовых импульсов. Символы "1", "0" кода поступают в устройство по входной шине 8, тактовые импульсы - по входной шине 9. При этом символ "1" кода представляет собой импульсный сигнал с уровнем логической единицы, сопровождаемый тактовым импульсом (также с уровнем логической единицы) по входной шине 9. Символ "0" кода поступает в устройство в виде напряжения с уровнем логического нуля, сопровождаемого тактовым импульсом по входной шине 9. Тактовые импульсы должны поступать с определенной задержкой относительно фронта символов 1 кода, необходимой для нормальной работы сдвиговых регистров 1 и 2.

Счетчик 4 предназначен для счета количества ошибок при вводе символов кода или неудачных попыток подбора кода посторонним лицом. Счетчик 4 выполнен в виде двоичного счетчика (например, может быть выполнен на счетчиках типа 564ИЕ10, 533ИЕ5, 533ИЕ10) или двоично-десятичного счетчика (например, типа 555ИЕ6, 1533ИЕ2), если количество ошибок на код не превышает десяти. Выходами счетчика 4 являются выходы его разрядов, начиная с К-го, где К зависит от количества допустимых ошибок при вводе каждого кода. Счетчик 4 переключается по срезу входных импульсов. Поэтому, если ошибки при вводе кодов вообще не допустимы, то К=1 и после первой же (и каждой) ошибки устройство переходит на второй (другой) эталонный код. Если же допустима одна ошибка (одна неудачная попытка подбора), то К=2 и после второй (каждой второй) ошибки устройство переходит на второй эталонный код. Если допустимы три ошибки на код (три попытки подбора кода), то К=3 и после четвертой (каждой четвертой) ошибки устройство переходит на третий эталонный код и т.д.

Блок 5 управления (см. фиг.2) содержит:

а) схему, активно удерживающую сдвиговые регистры 1 и 2 в исходном состоянии до ввода кода и после сравнения кодов, выполненную на резисторах 12, 13, 14, конденсаторе 15, диоде 16 и триггере Шмитта 17, инверсный выход которого является третьим выходом блока 5 управления;

б) схему, формирующую импульсные сигналы для сброса в исходное состояние счетчика 4, состоящую из формирователя импульса начального сброса при включении питания, выполненного на конденсаторе 18, резисторе 19, триггере Шмитта 20, элементе 21 ИЛИ, и формирователя короткого импульса по срезу сигнала "А=В", выполненного на триггере Шмитта 22, инверторе 23, резисторе 24 и конденсаторе 25; выход элемента 21 И является первым выходом блока 5 управления;

в) элемент 26 И, обеспечивающий выдачу на четвертый выход блока 5 управления тактовых импульсов только после снятия с входов сброса сдвиговых регистров 1 и 2 сигнала исходного состояния с уровнем логической единицы, запрещающего им прием и сдвиг информации (символов входного кода);

г) формирователь 27 импульсных сигналов опроса, выполненный (см. фиг.3) на двоичном счетчике 28 и элементе 29 И, выход которого является выходом формирователя 27 сигналов опроса и вторым выходом блока 5 управления.

На фиг.3 показан пример выполнения формирователя сигналов опроса для восьмиразрядного входного кода (восьмой тактовый импульс проходит на второй выход блока 5 управления в качестве опросного для блока 6 сравнения кодов). В качестве счетчика 28 могут быть использованы и другие типы счетчиков, переключение этого счетчика происходит по срезу тактовых импульсов.

Блок 6 сравнения кодов обеспечивает сравнение двух многоразрядных параллельных двоичных кодов, может быть выполнен на имеющихся в составе серий микросхем широкого применения цифровых компараторах (например, типа 564ИП2). На фиг. 4 показан пример выполнения блока 6 сравнения кодов для сравнения двух четырехразрядных двоичных кодов на схеме 30 сравнения типа 564ИП2, инверторе 31 и элементе 32 И. При количестве разрядов сравниваемых кодов больше, чем на схеме фиг. 4, указанного типа схемы сравнения включаются последовательно с использованием их входов расширения "А=В", "А>В" и "А<В", а сигнал опроса и младшие разряды сравниваемых кодов в этом случае подаются на соответствующие входы первой схемы сравнения, старшие разряды кодов - на входы второй схемы (последующих схем) сравнения.

Блок 7 памяти обеспечивает хранение эталонных кодов. Эталонный двоичный код выводится из блока 7 памяти параллельно путем изменения состояния счетчика 4. В качестве блока 7 памяти могут быть использованы выпускаемые в микросхемном исполнении ППЗУ (например, типов 541РТ1, М556РТ5, М1623РТ1) или РПЗУ (например, типов 558РР2, 573РФ2), в зависимости от количества разрядов эталонных кодов).

Устройство управления электронным замком (см. фиг.1) работает следующим образом.

В исходном состоянии на входных шинах 8 и 9 поддерживаются уровни логического нуля, на первом, втором и четвертом выходах блока 5 управления также уровни логического нуля, на третьем выходе - уровень логической единицы, которым сдвиговые регистры 1 и 2 активно удерживаются в исходном нулевом состоянии. Счетчик 4 также находится в исходном нулевом состоянии, в которое был установлен при включении питания импульсным сигналом с первого выхода блока 5 управления. На выходах сдвиговых регистров 1 и 2 - уровни логического нуля, на выходах блока 7 памяти первый эталонный код, на первом и втором выходах блока 6 сравнения кодов - уровни логического нуля. В указанное исходное состояние устройство само устанавливается при включении питания, которое сохраняется до подачи первого символа входного кода.

Рассмотрим работу устройства, принимая, что входные коды имеют восемь разрядов (символов), эталонные коды - четыре разряда, при этом входной код равен 11101011, первым поступает символ 1 справа, а на информационный вход сдвигового регистра 1 через мультиплексор 3 символы входного кода выдаются (в исходном состоянии счетчика 4) с выхода второго разряда сдвигового регистра 2. Принимаем также, что К=1, то есть ошибки при вводе кода или неудачные попытки подбора кода недопустимы, следовательно после первого же несовпадения кодов устройство должно переключится на новый эталонный код (и на соответствующий новый входной код).

При поступлении по входной шине 8 на информационный вход сдвигового регистра 2 первого символа ("1") кода от поступившего по входной шине 9 тактового импульса, "сопровождающего" каждый символ входного кода, быстро заряжается до уровня логической единицы через резистор 13 и диод 16 (см. фиг.2) конденсатор 15 блока 5 управления. При этом на третьем выходе блока 5 управления появляется и далее поддерживается (на время ввода всех символов входного кода, сравнения части входного кода с эталонным кодом и формирования результата сравнения этих кодов) уровень логического нуля, то есть снимается сигнал, активно удерживающий сдвиговые регистры 1 и 2 в исходном нулевом состоянии.

После этого на четвертом выходе блока 5 управления появляется с некоторой задержкой на элементе 26 И (см. фиг.2) первый тактовый импульс, по фронту которого в первый разряд сдвигового регистра 2 записывается первый символ ("1") кода и подтверждаются исходные нулевые состояния остальных разрядов сдвигового регистра 2 и всех разрядов сдвигового регистра 1. Следует отметить, что первый тактовый импульс на четвертом выходе блока 5 управления имеет несколько большую относительно символа "1" входного кода задержку, определяемую временем заряда конденсатора 15 до уровня логической единицы через резистор 13 и диод 16, чем остальные тактовые импульсы относительно соответствующих им символов "1" входного кода, для которых указанная задержка равна задержке переключения элемента 26 И, которая достаточна для обеспечения уверенной записи символов "1" кода в первый разряд сдвигового регистра 2. При необходимости, например, в случаях, когда паразитные емкости линий связи и монтажа заметно влияют на скорость распространения сигналов в устройстве, задержка тактовых импульсов в блоке 5 управления может быть увеличена включением элемента задержки (четного количества инверторов, RC-цепи с небольшой постоянной времени или просто конденсатора с небольшой емкостью) к выходу элемента 26 И.

Поступающие символы входного кода постепенно заполняют (по фронту тактовых импульсов) сдвиговые регистры 2 и 1. При этом на вход сдвигового регистра 1 символы входного кода через мультиплексор 3 начинают поступать не сразу, а только после того, когда первый символ кода в процессе сдвига кода в сдвиговом регистре 2 будет записан в разряд, который мультиплексором 3 в исходном состоянии счетчика 4 выбран для подачи части входного кода на вход сдвигового регистра 1 (для последующего сравнения этой части входного кода с эталонным кодом). Соответствующий символ входного кода переписывается в первый разряд сдвигового регистра 1 по фронту следующего тактового импульса, то есть при сдвиге его в сдвиговом регистре 2 в следующий разряд (в рассматриваемом нашем случае - в третий разряд).

В таблице (см. фиг.5) приведены состояния разрядов сдвигового регистра 2 (графа 2) и сдвигового регистра 1 (графа 3) в процессе ввода входного кода для рассматриваемого случая. Там же приведены состояния разрядов сдвигового регистра 1 еще для двух случаев, когда в исходном состоянии счетчика 4 для съема информации со сдвигового регистра 2 мультиплексором 3 выбран его четвертый разряд при четырехразрядном (графа 4) и пятиразрядном (графа 5) эталонных кодах.

Как видно из таблицы, в первом из рассматриваемых случаев (графа 3) после ввода в сдвиговый регистр 2 всех восьми разрядов входного кода 11101011 первые два символа (11) входного кода оказываются "вытолкнутыми" из сдвигового регистра 1, во втором случае (графа 4) в сдвиговом регистре 1 оказались записанными первые четыре символа (1011) входного кода, в третьем случае (графа 5) в сдвиговом регистре 1 оказываются записанными только первые четыре символа (1011) входного кода. Следовательно, в рассмотренных случаях в исходном состоянии устройства (счетчика 4) для сравнения с записанной в сдвиговый регистр 1 частью входного 8-разрядного кода из блока 7 памяти должны быть выставлены, соответственно, эталонные коды 1010, 1011, 10110.

После ввода в устройство (в сдвиговый регистр 2) всех восьми разрядов входного кода на втором выходе блока 5 управления появляется сигнал опроса, равный по длительности тактовому импульсу (восьмому), который поступает на тактовый вход блока 6 сравнения кодов и "разрешает" сравнение первого эталонного кода с частью входного кода, записанной в сдвиговый регистр 1.

Если сравниваемые коды совпадают, то на первом выходе блока 6 сравнения кодов появляется сигнал с уровнем логической единицы ("А=В"), который поступает по выходной шине 10 на соответствующее исполнительное устройство, а также поступает на второй вход блока 5 управления. По срезу этого сигнала блок 5 управления формирует короткий импульс, который через его первый выход подтверждает исходное состояние счетчика 4. После этого через заданное время, определяемое временем разряда конденсатора 15 (см. фиг.2) до уровня логического нуля через большое сопротивление резисторов 14 и 13, на третьем выходе блока 5 управления восстанавливается исходный уровень логической единицы, которым сбрасываются в исходные состояния и активно удерживаются в них сдвиговые регистры 1 и 2. Этим же сигналом в самом блоке 5 управления удерживается в исходном нулевом состоянии счетчик 28 формирователя 27 сигналов опроса. Таким образом, в случае совпадения кодов устройство формирует выходной сигнал "А=В" и автоматически возвращается в свое исходное состояние.

Если сравниваемые коды не совпадают, то по сигналу опроса в блоке 6 сравнения кодов формируется импульсный сигнал о неравенстве кодов ("А≠В") с уровнем логической единицы, который со второго выхода этого блока выдается по выходной шине 11 на тревожную сигнализацию, а также поступает на счетный вход счетчика 4. По срезу этого сигнала счетчик 4 принимает состояние, соответствующее числу 1, то есть триггер его первого разряда переключается в единичное состояние. А поскольку выходы всех разрядов счетчика 4 в рассматриваемом случае соединены с соответствующими адресными входами мультиплексора 3 и блока 7 памяти (так как было принято, что при вводе входного кода ошибки недопустимы), то изменяются коды на адресных входах блока 7 памяти и мультиплексора 3, поэтому блок 7 памяти выдает на свои выходы новый эталонный код, а мультиплексор 3 подключает информационный вход сдвигового регистра 1 к выходу другого разряда сдвигового регистра 2.

Через определенное время после формирования результата сравнения кодов (после разряда конденсатора 15 блока 5 управления через резисторы 14 и 13) на третьем выходе блока 5 управления восстанавливается исходный уровень логической единицы, который устанавливает сдвиговые регистры 1 и 2 в исходное состояние. После этого устройство снова готово к приему кода, но при этом счетчик 4 сохраняет свое состояние, соответствующее числу 1, а на выходах блока 7 памяти остается выставленным новый эталонный код.

Если после этого по входной шине 8 подать новый код и часть этого кода, оказавшаяся после восьмого тактового импульса в сдвиговом регистре 1, совпадает с новым эталонным кодом, то блок 6 сравнения кодов по сигналу опроса сформирует выходной сигнал "А=В". Этот сигнал по выходной шине 10 выдается на исполнительное устройство и одновременно поступает в блок 5 управления. Короткий импульс, сформированный в блоке 5 управления по срезу сигнала "А≠В", через первый выход этого блока, сбрасывает счетчик 4 в исходное состояние. При этом блок 7 памяти и мультиплексор 3 возвращаются в нулевые адреса, поэтому блок 7 памяти выставляет на свои выходы первый эталонный код, а мультиплексор 3 подключает информационный вход сдвигового регистра 1 к выходу этого разряда сдвигового регистра 2, к которому он был подключен в исходном состоянии счетчика 4. После разряда конденсатора 15 в блоке 5 управления устанавливаются в исходное состояние, как и в предыдущих случаях, и сдвиговые регистры 1 и 2. Следовательно, устройство оказывается в исходном состоянии.

В случае, если допустимое количество ошибок при вводе каждого нового кода принять равным одному, то есть, если после второй ошибки или неудачной попытки подбора кода устройство должно перейти на новый эталонный код и новый входной код, то с адресными входами мультиплексора 3 и блока 7 управления соединяются выходы всех разрядов счетчика 4, начиная со второго разряда. Тогда при первом несовпадении кодов устройство работает так же, как в рассматриваемом случае, а после второго несовпадения кодов изменяется состояние разряда счетчика 4, выход которого соединен с соответствующими адресными входами мультиплексора 3 и блока 7 памяти, поэтому устройство переключается на новый эталонный код и соответствующий ему новый входной код. Если при подаче этого нового кода сравниваемые коды совпадут, то устройство возвратится в исходное состояние. Если же и эти коды не совпадут, то после двух несовпадений устройство аналогично рассмотренным случаям снова переключится на очередной эталонный код. После первого же совпадения новых кодов устройство возвращается в исходное состояние.

Аналогично работает устройство и в случаях, когда с адресными входами блока 7 памяти и мультиплексора 3 соединяются выходы разрядов счетчика 4, начиная с третьего, четвертого и т.д. При этом при использовании выходов разрядов счетчика 4, начиная с третьего разряда, допустимое количество ошибок при вводе кода и попыток подбора на каждый новый код будет равно трем, и после четвертого несовпадения кодов устройство будет переключаться на следующий эталонный код. При использовании выходов разрядов счетчика 4, начиная с четвертого, допустимое количество ошибок при вводе кода будет равно семи, после восьмой неудачной попытки устройство переключится на новый эталонный код. Однако допущение такого большого количества ошибок или подбора кода вряд ли возможно практически.

Из описания работы устройства управления электронным замком видно, что оно обладает всеми функциональными возможностями прототипа, но имеет при этом повышенные надежность, степень защищенности от подбора кода, удобство в эксплуатации и расширенные функциональные возможности.

С целью подтверждения осуществимости заявленного объекта и достигнутого технического результата был собран и испытан макет заявляемого устройства управления электронным замком для восьмиразрядного входного кода и четырехразрядного эталонного кода. Макет был реализован на базе интегральных микросхем серии 564, РПЗУ 558РР2 и дискретных ЭРИ (резисторов, конденсаторов и диодов). Символы "1" и "0" кода и тактовые импульсы подавались на входы устройства с помощью двух кнопочных переключателей типа ПКн 105 с соответствующими схемами подавления дребезга. При этом на входную шину 8 устройства подавались символы "1" кода с выхода схемы подавления дребезга кнопки набора "1", а тактовые импульсы формировались сигналами с выходов схем подавления дребезга обеих кнопок по схеме ИЛИ, необходимая задержка тактовых импульсов обеспечивалась включением к выходу указанного элемента ИЛИ четного количества инверторов.

Проведенные испытания макета показали работоспособность заявляемого устройства управления электронным замком и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОННЫЙ ЗАМОК | 2002 |

|

RU2213191C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2003 |

|

RU2235178C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2003 |

|

RU2239037C1 |

| ЭЛЕКТРОННЫЙ ЗАМОК | 2002 |

|

RU2221921C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ КОДОВЫМ ЗАМКОМ | 2001 |

|

RU2195541C1 |

| ЭЛЕКТРОННЫЙ КОДОВЫЙ ЗАМОК | 2001 |

|

RU2215107C2 |

| ЭЛЕКТРОННЫЙ КОДОВЫЙ ЗАМОК | 2001 |

|

RU2191241C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КОДОВЫМ ЗАМКОМ | 2001 |

|

RU2191878C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМИ ЗАМКАМИ | 2001 |

|

RU2198276C1 |

| ЯЧЕЙКА ПАМЯТИ | 2001 |

|

RU2214037C2 |

Изобретение относится к технике защиты различных объектов от несанкционированного доступа, в частности к электронным кодовым замкам. Техническим результатом является повышение надежности, уровня защищенности от подбора кода и удобства эксплуатации и расширение функциональных возможностей. Технический результат достигается тем, что в устройство управления электронным замком, содержащее два сдвиговых регистра, мультиплексор, счетчик, блок управления, блок сравнения кодов, блок памяти, две входные шины и две выходные шины, введены сдвиговый регистр, мультиплексор, счетчик, блок управления и новые связи между функциональными блоками и элементами. 5 ил.

Устройство управления электронным замком, содержащее две входные шины и две выходные шины, первая из которых соединена с первым выходом блока сравнения кодов, первая и вторая группы входов которого подключены к соответствующим выходам первого сдвигового регистра и блока памяти соответственно, отличающееся тем, что введены второй сдвиговый регистр, мультиплексор, блок управления и счетчик, выходы разрядов которого, начиная с К-го, где К= 1,2, . . . , соединены с соответствующими адресными входами блока памяти и мультиплексора, выход которого соединен с информационным входом первого сдвигового регистра, информационные входы соединены с соответствующими выходами второго сдвигового регистра, информационный вход которого подключен к первой входной шине устройства, вторая входная шина которого соединена с первым входом блока управления, второй вход которого соединен с первой выходной шиной устройства, вторая выходная шина которого соединена со вторым выходом блока сравнения кодов и счетным входом счетчика, вход сброса которого соединен с первым выходом блока управления, второй выход которого соединен с тактовым входом блока сравнения кодов, третий и четвертый выходы соединены соответственно с входами сброса и тактовыми входами сдвиговых регистров.

| Электронный замок | 1988 |

|

SU1612069A1 |

| WO 9855717, 10.12.1998 | |||

| ЭЛЕКТРОННЫЙ КОДОВЫЙ ЗАМОК | 1999 |

|

RU2156851C1 |

| ЭЛЕКТРОННЫЙ ЗАМОК | 1992 |

|

RU2057246C1 |

| Устройство управления кодовым замком | 1986 |

|

SU1359429A1 |

| Электрический замок | 1984 |

|

SU1283340A1 |

| ЭЛЕКТРОННОЕ КОДОВОЕ УСТРОЙСТВО | 1993 |

|

RU2037046C1 |

| US 4967305 30.10.1990. | |||

Авторы

Даты

2003-08-10—Публикация

2002-06-21—Подача