Изобретение относится к области импульсной техники и может быть использовано в устройствах вычислительной техники и систем управления.

Известна ячейка памяти (см. а. с. СССР 1706362 от 02.04.90, МКИ H 03 K 3/037, "Триггерное устройство", Еремин А.Н., Шишкин Г.И., опубл. 28.08.97, Бюл. 24), содержащее D-триггер, первый, второй и третий элементы ИЛИ-НЕ, элемент И-НЕ, двунаправленный ключ, резистор и конденсатор. Один из выводов резистора через конденсатор подключен к общей шине. Первый и второй входы первого элемента ИЛИ-НЕ соединены соответственно с первым установочным входом устройства и выходом второго элемента ИЛИ-НЕ. Первый и второй входы второго элемента ИЛИ-НЕ соединены соответственно со вторым установочным входом устройства и прямым выходом D-триггера. Тактовый вход D-триггера соединен с выходом третьего элемента ИЛИ-НЕ, первый и второй входы которого соединены с первыми входами соответственно первого и второго элементов ИЛИ-НЕ. Выход двунаправленного ключа соединен с информационным входом D-триггера и другим выводом резистора, вход - с выходом первого элемента ИЛИ-НЕ, а управляющий вход - с выходом элемента И-НЕ. Первый и второй входы элемента И-НЕ соединены соответственно с выходом третьего элемента ИЛИ-НЕ и с дополнительным входом устройства.

Недостатком указанной ячейки памяти является малый объем хранимой информации.

Известна ячейка памяти (см. патент РФ 2042268 от 28.06.91, МКИ H 03 K 23/64, "Счетчик импульсов в коде Грея", Дикарев И.И., Шишкин Г.И., опубл. 20.08.95, Бюл. 23), содержащая разряды с нулевого по N-й, последовательные RC-цепи по числу разрядов, демультиплексор, два коммутатора и в каждом разряде асинхронный D-триггер и мультиплексор, содержащий два двунаправленных ключа и элемент ИЛИ-НЕ, входы которого являются адресными входами мультиплексора. В каждом разряде выходы двунаправленных ключей соединены с входом триггера и с соответствующим входом первого коммутатора, выход которого соединен с выходом второго коммутатора, входы которого соединены с первыми выводами соответствующих RC-цепей, вторые выводы которых соединены с общей шиной. Вход демультиплексора соединен с первой входной шиной, адресные входы - со второй входной шиной и с соответствующими адресными входами коммутаторов, а выходы - с первыми входами элементов ИЛИ-НЕ соответствующих разрядов, второй вход элемента ИЛИ-НЕ каждого разряда соединен с управляющим входом первого двунаправленного ключа и является входом разрешения записи информации, а выход соединен с управляющим входом второго двунаправленного ключа, вход которого соединен с прямым выходом триггера. Информация на второй входной шине изменяется при поступлении сигнала по первой входной шине. Вход первого двунаправленного ключа является информационным входом разряда ячейки памяти.

Ячейка памяти является наиболее близкой по технической сущности к заявленному устройству и взята в качестве прототипа.

Недостатком прототипа является сложность устройства.

Технической задачей является создание устройства, отличающегося простотой схемной реализации.

Ячейка памяти, содержащая коммутатор, N последовательных RC-цепей, первые выводы которых соединены с соответствующими входами коммутатора, а вторые выводы - с общей шиной, мультиплексор и асинхронный D-триггер, вход которого соединен с выходом коммутатора и с выходом мультиплексора, а выход - с его соответствующим входом, два других входа мультиплексора соединены с входной шиной. Новым является то, что дополнительно введены счетчик импульсов, два триггера, элемент ИЛИ-НЕ и формирователь коротких импульсов, первый вход которого соединен с S-входом первого триггера и с шиной считывания, второй вход - с S-входом второго триггера и с шиной записи, а выход - с R-входом счетчика, С-вход которого соединен с первым адресным входом мультиплексора и с управляющей шиной, а выходы - с соответствующими адресными входами коммутатора, выход старшего разряда счетчика соединен с R-входами триггеров, выход второго триггера соединен со вторым адресным входом мультиплексора, инверсный выход первого триггера соединен с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с инверсным выходом D-триггера, а выход - с выходной шиной.

Указанная совокупность признаков позволяет упростить схему.

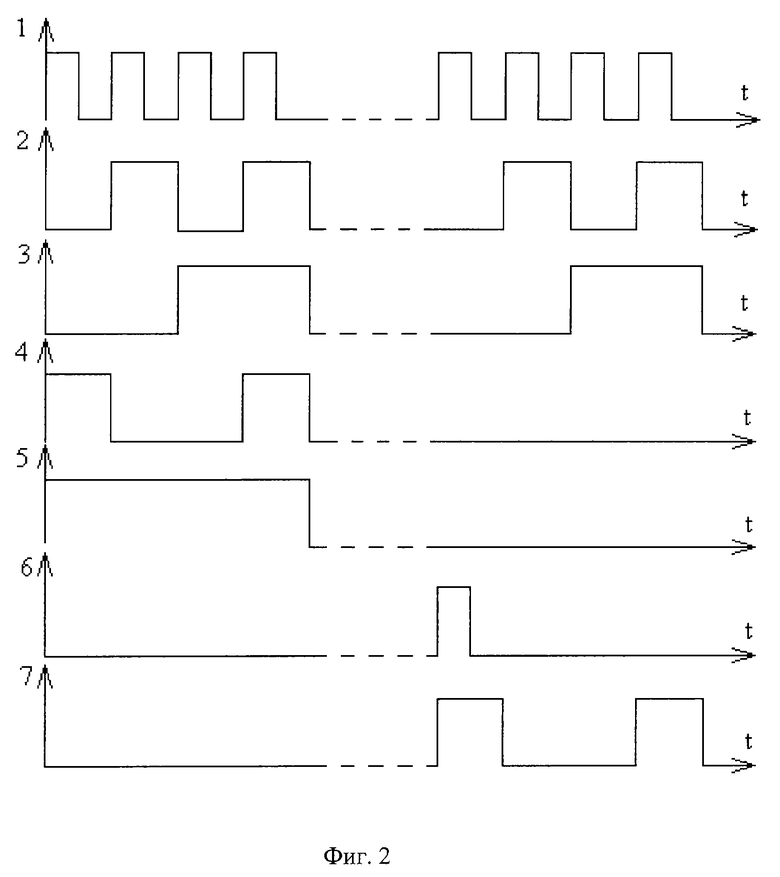

Принципиальная схема ячейки памяти приведена на фиг.1. На фиг.2 приведены временные диаграммы работы указанной ячейки памяти.

Ячейка памяти содержит 4 разряда (с нулевого по третий), входную "Вх", выходную "Вых" шины, шину считывания "Сч", шину записи "Зап", шину управления "Упр", мультиплексор 1, коммутатор 2, асинхронный D-триггер 3, состоящий из двух инверторов, два RS-триггера 4, 5, счетчик импульсов 6, формирователь коротких импульсов 7, элемент ИЛИ-НЕ 8, последовательные RC-цепи 9 (9-0. . .9-3), первые выводы которых соединены с соответствующими входами коммутатора 2, а вторые выводы - с общей шиной.

Входная шина соединена с входами Х2, Х3 мультиплексора 1, выход которого соединен с выходом коммутатора 2 и с входом D-триггера 3, выход которого соединен с входом Х0 мультиплексора 1, второй адресный вход которого соединен с прямым выходом RS-триггера 5, S-вход которого соединен с шиной записи и со вторым входом формирователя коротких импульсов 7, второй вход которого соединен с шиной считывания и с S-входом RS-триггера 4, R-входы триггеров соединены с выходом старшего разряда счетчика импульсов 6 и с адресным входом А2 коммутатора 2, адресный вход А1 которого соединен с выходом младшего разряда счетчика импульсов 6, С-вход которого соединен с шиной управления и с адресным входом А1 мультиплексора 1, R-вход счетчика импульсов 6 соединен с выходом формирователя коротких импульсов 7, выходная шина соединена с выходом элемента ИЛИ-НЕ 8, первый вход которого соединен с инверсным выходом D-триггера 3, а второй - с инверсным выходом RS-триггера 4.

Ячейка памяти работает следующим образом.

При включении напряжения питания на всех шинах устройства сигналы отсутствуют (сигнал логического "0"), каналы ХХ0 мультиплексора 1 и коммутатора 2 открыты, вход D-триггера 3 подключен к его выходу, RC-цепь 9-0 также подключена к входу D-триггера, остальные RC-цепи отключены. При подаче импульсов управления (диаграмма 1, фиг.2) счетчик импульсов 6 (диаграммы 2, 3, фиг.2) поочередно подключает RC-цепи 9 (9-0...9-3) к входу D-триггера и к выходу мультиплексора 1.

Запись информации в ячейку памяти происходит следующим образом. На шину "Зап" подается сигнал (диаграмма 5, фиг.2), который устанавливает прямой выход триггера 5 в состояние логической "1", также этот сигнал поступает на один из входов формирователя коротких импульсов, который формирует импульс, который поступает на вход сброса счетчика импульсов. Информация с входов Х2, Х3 мультиплексора 1 (диаграмма 4, фиг.2) поступает на вход коммутатора 2. Сигнал записи присутствует на шине "Зап" в течение всего цикла записи. Это необходимо для того, чтобы исключить действие помехи по шине "Зап".

Считывание информации происходит следующим образом.

На шину "Сч" поступает сигнал (диаграмма 6, фиг.2), который устанавливает инверсный выход RS-триггера 4 в состояние логического "0", сигнал с которого поступает на один из входов элемента ИЛИ-НЕ, на другой вход которого поступает сигнал с инверсного выхода D-триггера 3, вход которого поочередно подключается к одной из RC-цепей 9, в результате на выходной шине появляется информация, записанная в ячейке памяти (диаграмма 7, фиг.2). Сигнал считывания также подается на второй вход формирователя коротких импульсов, который выполняет также функцию "ИЛИ", в результате счетчик импульсов 6 обнуляется при поступлении сигналов записи или считывания.

Цикл записи и чтения заканчивается по окончании сигнала на выходе старшего разряда счетчика импульсов 6.

С целью подтверждения осуществимости заявляемой ячейки памяти и положительного эффекта, достигаемого от ее использования, изготовлен и испытан лабораторный образец, выполненный по схеме фиг.1.

В качестве элементной базы устройства выбрана КМОП серия 564. Формирователь коротких импульсов выполнен по схеме (см. Бирюков С.А. Цифровые устройства на МОП-интегральных микросхемах. - М.: Радио и связь, 1990, - 128с., с.58, рис. 105,б), вход которой подключен к выходу элемента ИЛИ-НЕ.

Проведенные испытания показали осуществимость предлагаемого изобретения и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ПАМЯТИ | 2002 |

|

RU2224356C2 |

| ЯЧЕЙКА ПАМЯТИ | 2002 |

|

RU2222100C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| ЭЛЕКТРОННЫЙ ЗАМОК | 2002 |

|

RU2213191C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207717C2 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ИЗМЕРЕНИЯ ВРЕМЕННЫХ ПАРАМЕТРОВ | 1999 |

|

RU2180450C2 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207718C1 |

| КОММУТАТОР ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 1995 |

|

RU2103716C1 |

| ПРОГРАММНЫЙ ТАЙМЕР | 2001 |

|

RU2215367C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМИ ЗАМКАМИ | 2001 |

|

RU2198276C1 |

Изобретение относится к области импульсной техники и может быть использовано в устройствах вычислительной техники и систем управления. Техническим результатом является увеличение объема записанной информации. Ячейка памяти содержит коммутатор, последовательные RC-цепи, три мультиплексора, асинхронный триггер, счетчик импульсов, два триггера, элемент ИЛИ-НЕ и формирователь коротких импульсов. 2 ил.

Ячейка памяти, содержащая коммутатор, N последовательных RC-цепей, первые выводы которых соединены с соответствующими входами коммутатора, а вторые выводы - с общей шиной, мультиплексор и асинхронный D-триггер, вход которого соединен с выходом мультиплексора, а выход - с его соответствующим входом, два других входа мультиплексора соединены с входной шиной, отличающаяся тем, что введены счетчик импульсов, два триггера, элемент ИЛИ-НЕ и формирователь коротких импульсов, первый вход которого соединен с S-входом первого триггера и с шиной считывания, второй вход - с S-входом второго триггера и с шиной записи, а выход - с R-входом счетчика импульсов, С-вход которого соединен с первым адресным входом мультиплексора и с управляющей шиной, а выходы - с соответствующими адресными входами коммутатора, выход которого соединен с выходом мультиплексора, выход старшего разряда счетчика соединен с R-входами триггеров, выход второго триггера соединен со вторым адресным входом мультиплексора, инверсный выход первого триггера соединен с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с инверсным выходом D-триггера, а выход - с выходной шиной.

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2042268C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1990 |

|

SU1706362A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО МАГАЗИННОГО ТИПА | 1991 |

|

RU2081459C1 |

| US 4805139 А, 14.02.1989 | |||

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1992 |

|

RU2030094C1 |

Авторы

Даты

2003-10-10—Публикация

2001-10-25—Подача